- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Память в вычислительных системах презентация

Содержание

- 1. Память в вычислительных системах

- 2. Характеристики запоминающих устройств Емкость. Разрядность. Способ доступа.

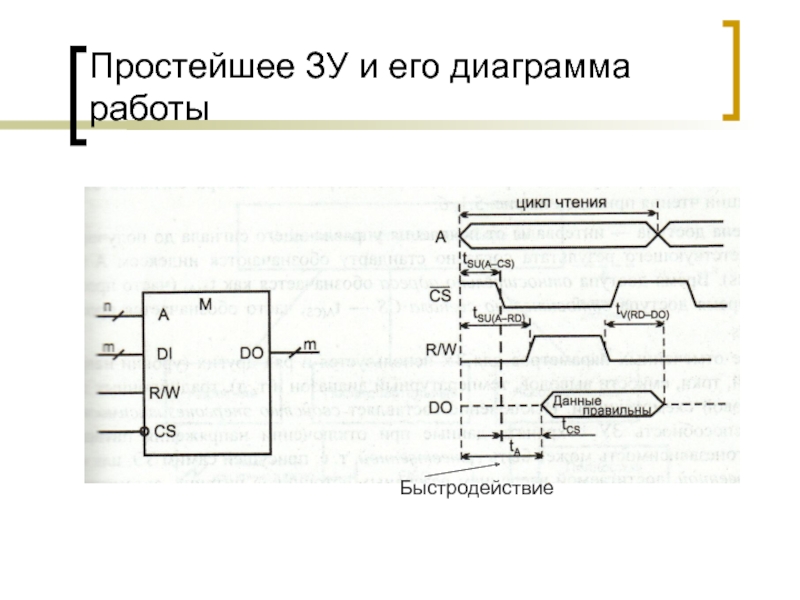

- 3. Простейшее ЗУ и его диаграмма работы Быстродействие

- 4. Иерархия ЗУ Прирост быстродействия ЗУ 9% в

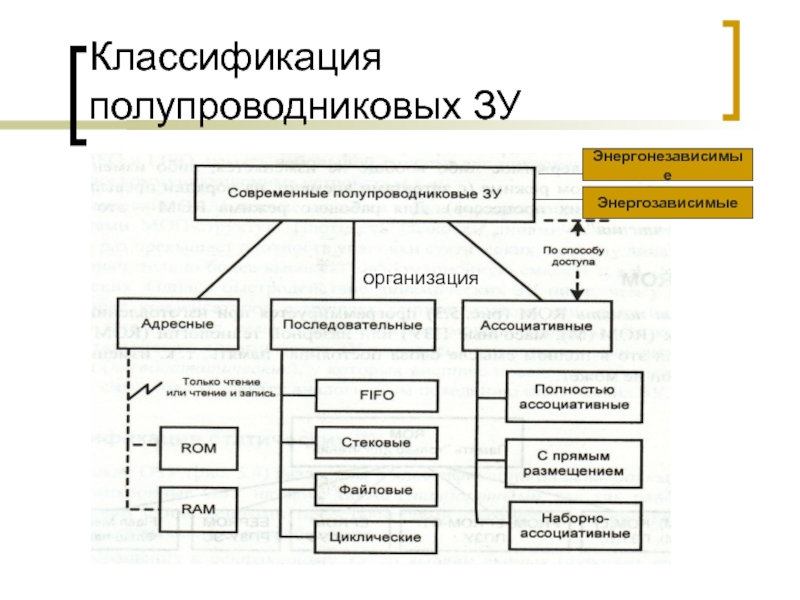

- 5. Классификация полупроводниковых ЗУ организация Энергонезависимые Энергозависимые

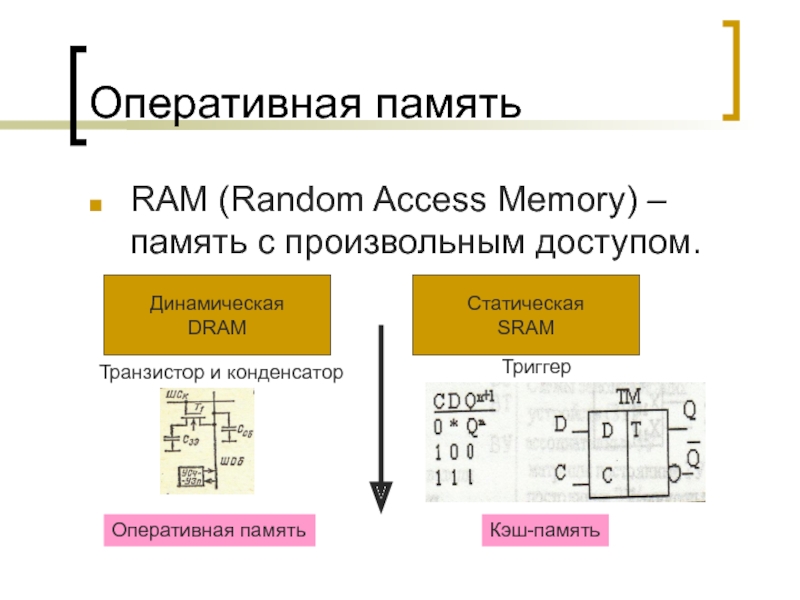

- 6. Оперативная память RAM (Random Access Memory) –

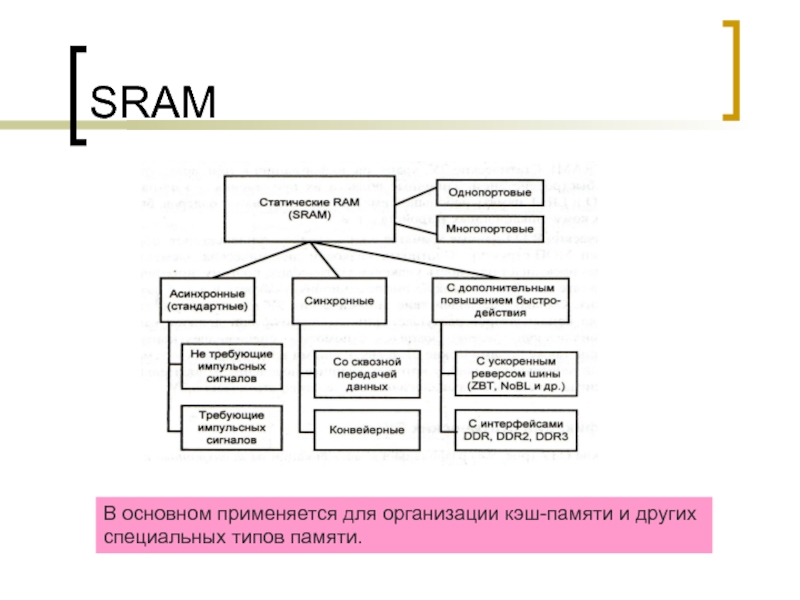

- 7. SRAM В основном применяется для организации кэш-памяти и других специальных типов памяти.

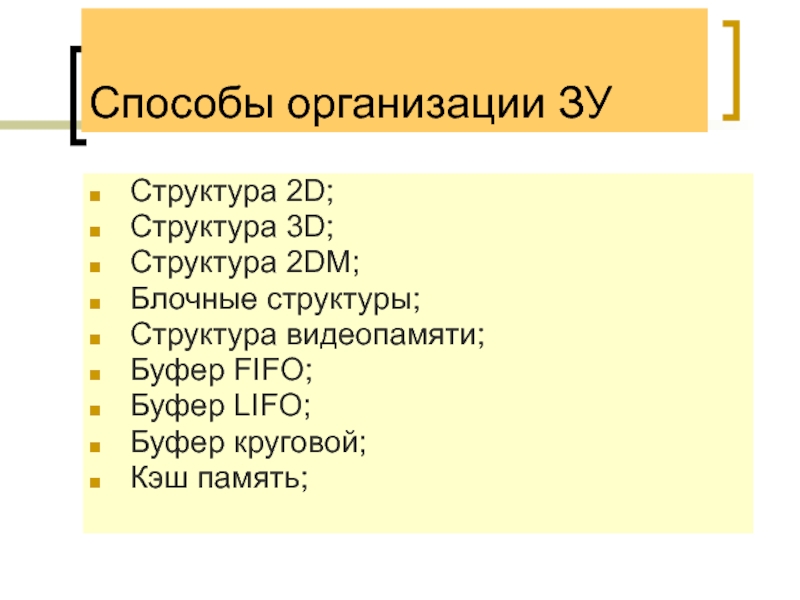

- 8. Способы организации ЗУ Структура 2D; Структура 3D;

- 9. Структура 2D ЗЭ образуют прямоугольную матрицу

- 10. Структура 3D Используется принцип двухкоординатной выборки. Применяется

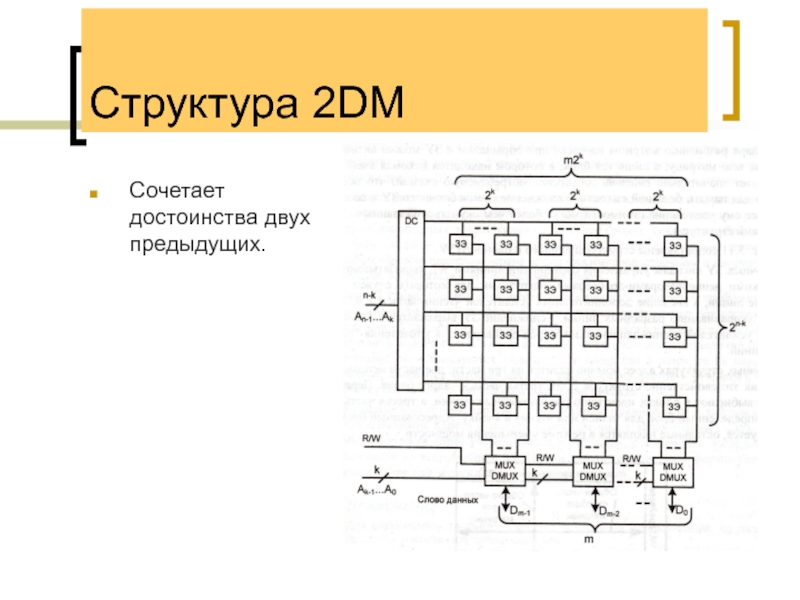

- 11. Структура 2DM Сочетает достоинства двух предыдущих.

- 12. Блочные структуры ЗУ С увеличением емкости матрицы

- 13. Блочная организация оперативной памяти Пока идет регенерация в одном банке, можно работать с другим банком.

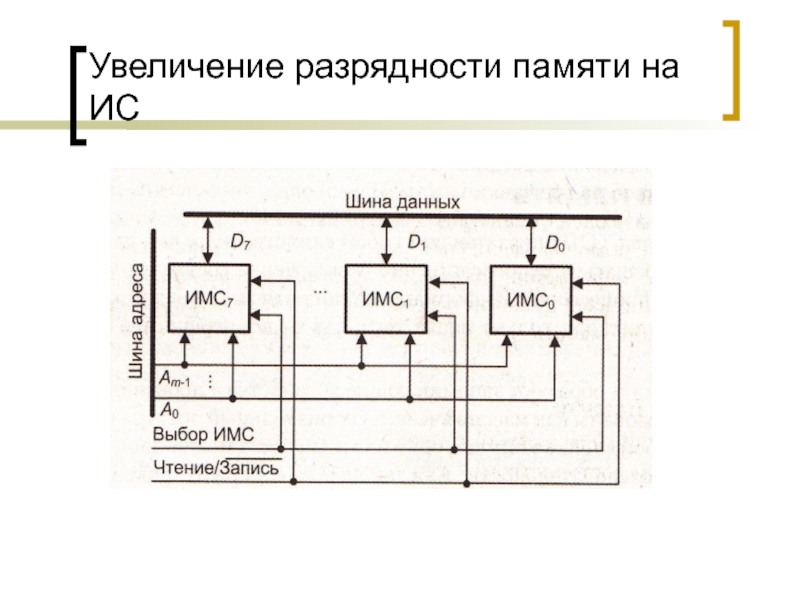

- 14. Увеличение разрядности памяти на ИС

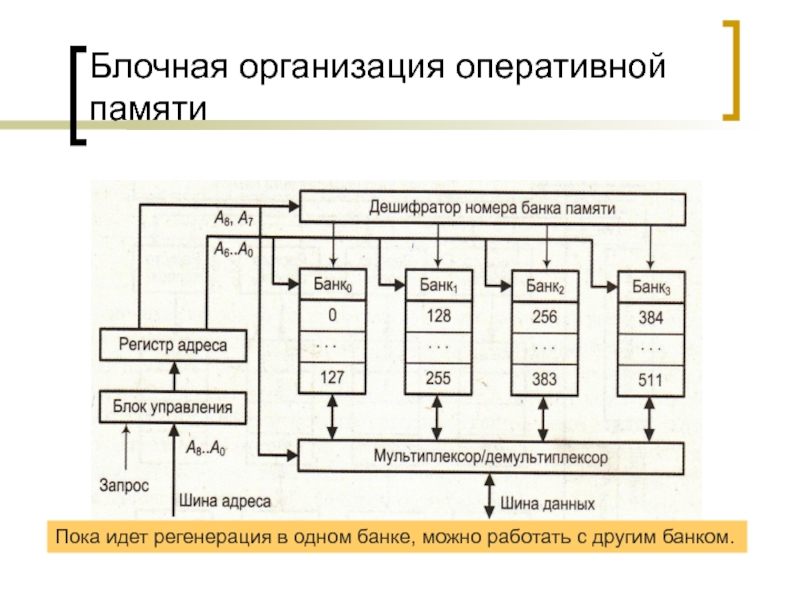

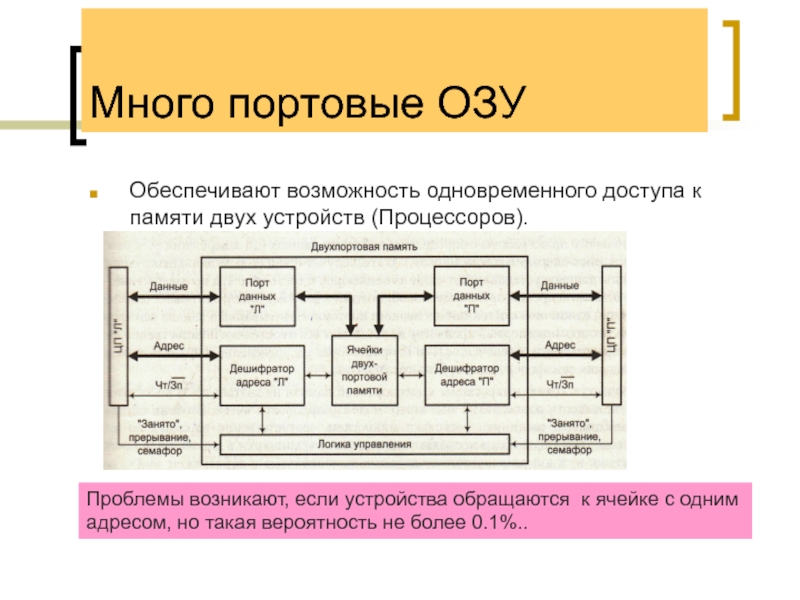

- 15. Много портовые ОЗУ Обеспечивают возможность одновременного доступа

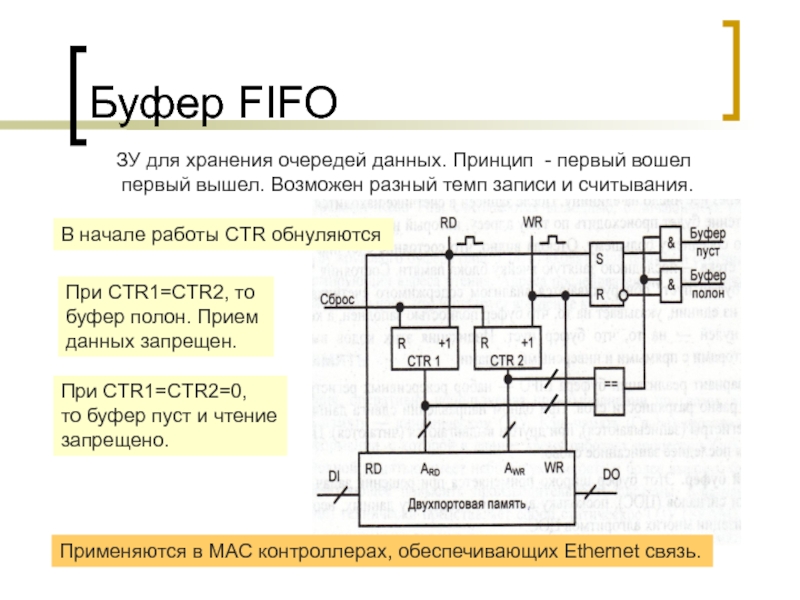

- 16. Буфер FIFO ЗУ для хранения очередей данных.

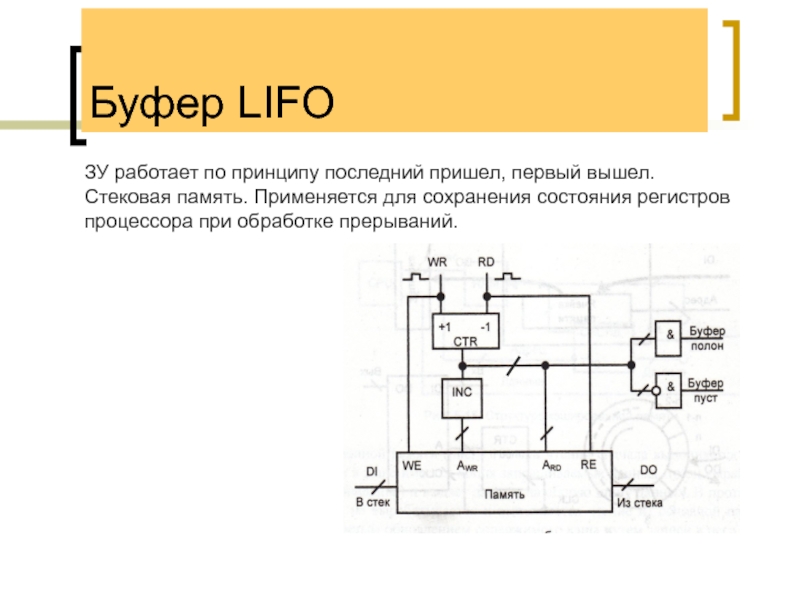

- 17. Буфер LIFO ЗУ работает по принципу последний

- 18. Круговой буфер Применяется при решении задач цифровой

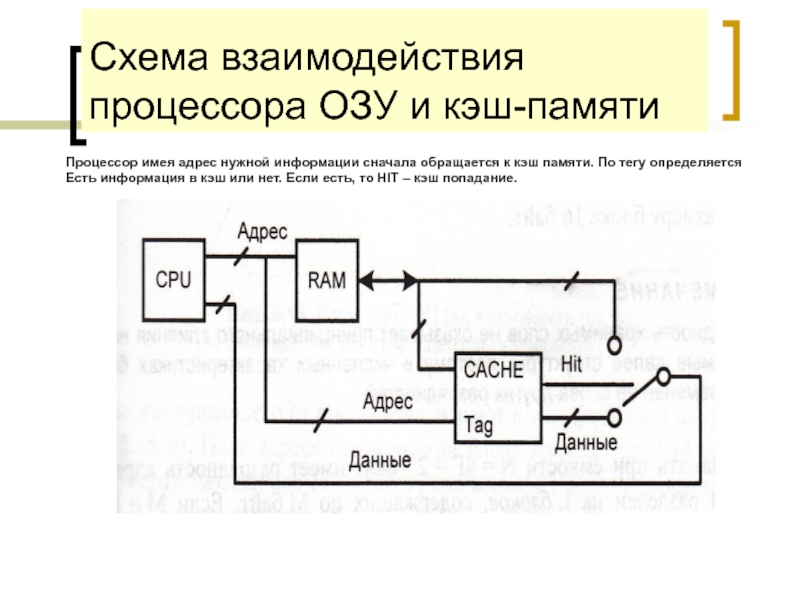

- 19. Схема взаимодействия процессора ОЗУ и кэш-памяти Процессор

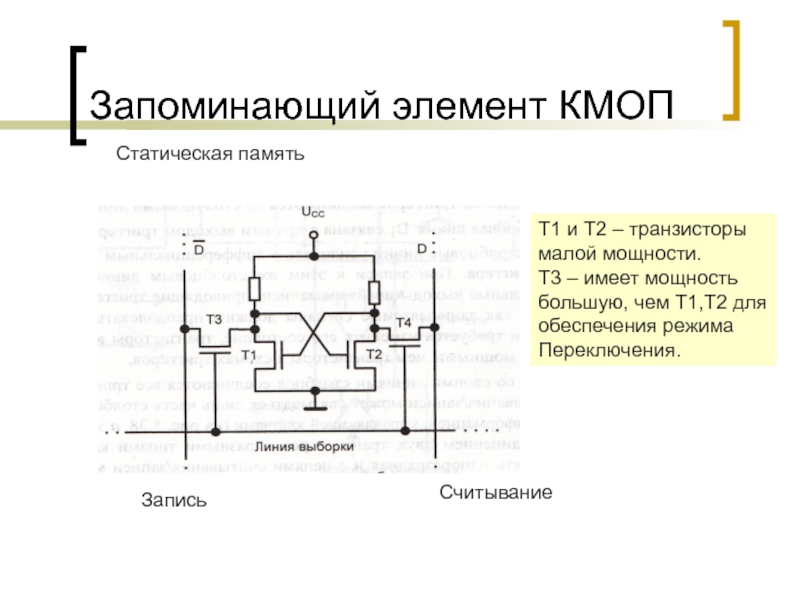

- 20. Запоминающий элемент КМОП Считывание Запись Т1 и

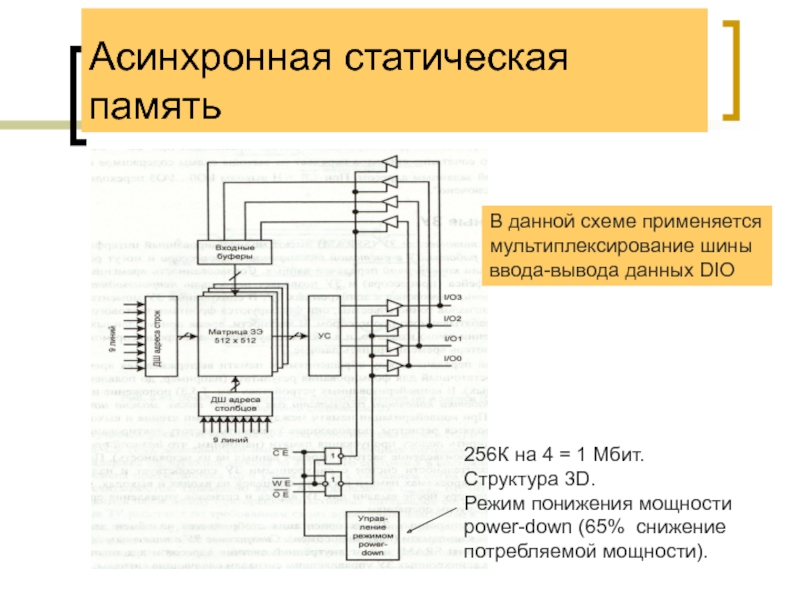

- 21. Асинхронная статическая память 256К на 4 =

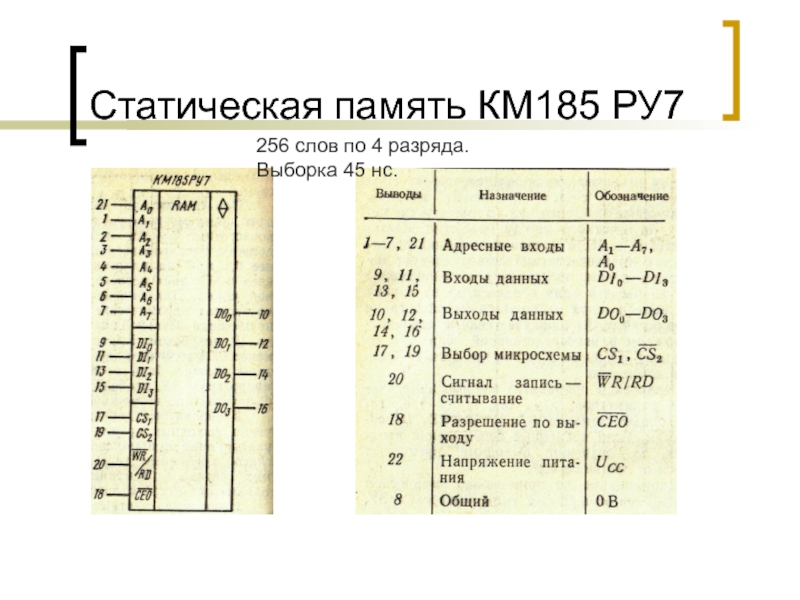

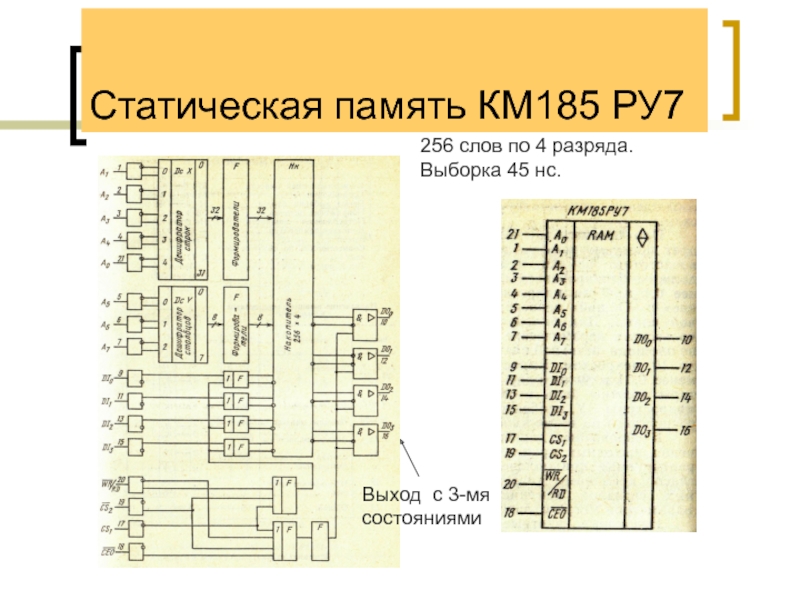

- 22. Статическая память КМ185 РУ7 256 слов по 4 разряда. Выборка 45 нс.

- 23. Статическая память КМ185 РУ7 256 слов по

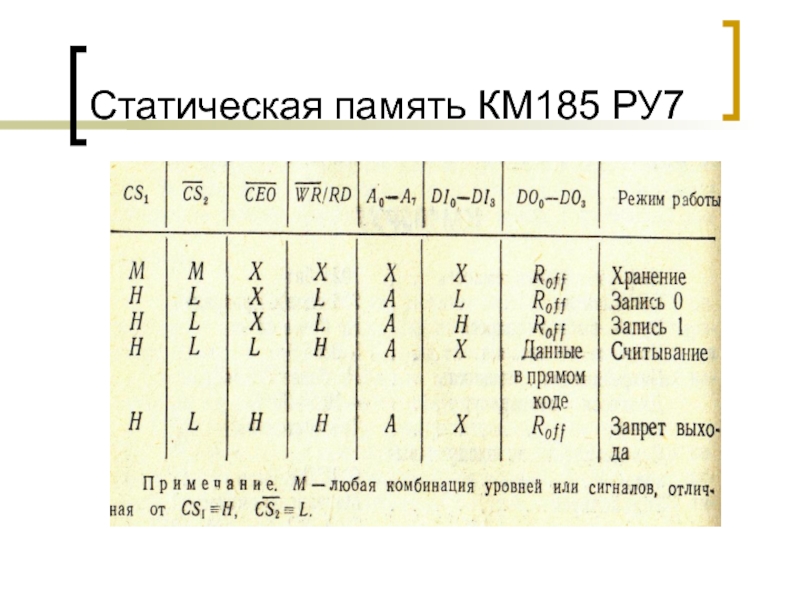

- 24. Статическая память КМ185 РУ7

- 25. Синхронная статическая память RG RG 9 си

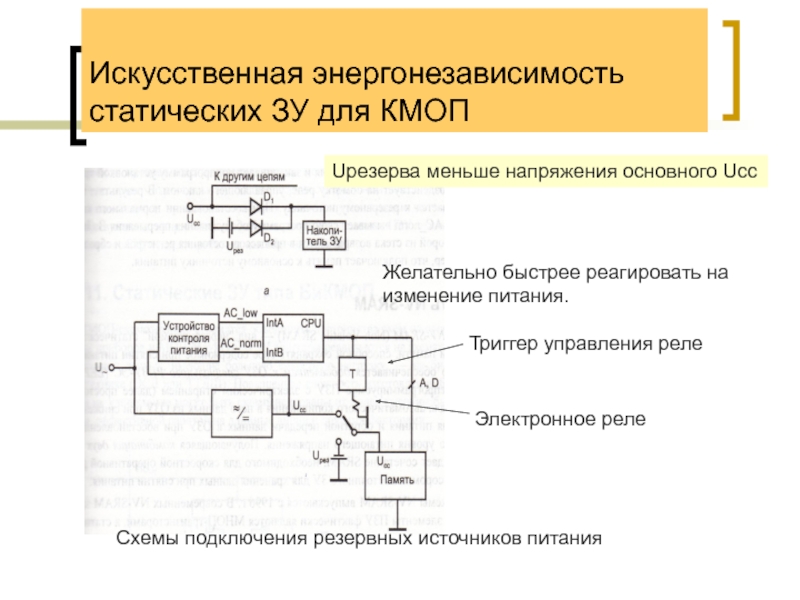

- 26. Искусственная энергонезависимость статических ЗУ для КМОП Схемы

- 27. Искусственная энергонезависимость статических ЗУ – NV-SRAM Выпускаются

- 28. Динамические ЗУ. Базовая структура запоминающей ячейки Позволяет

- 29. Особенности динамических ЗУ Поток обращений к динамическому

- 30. Считывание и запись в динамической ячейке памяти

- 31. Внешняя организация DRAM Мультиплексирование внешней шины часто

- 32. Организация микросхем динамической памяти OE output enable WE write enable CS chip select DIO

- 33. Структурная схема динамической памяти Блок регенерации RAS

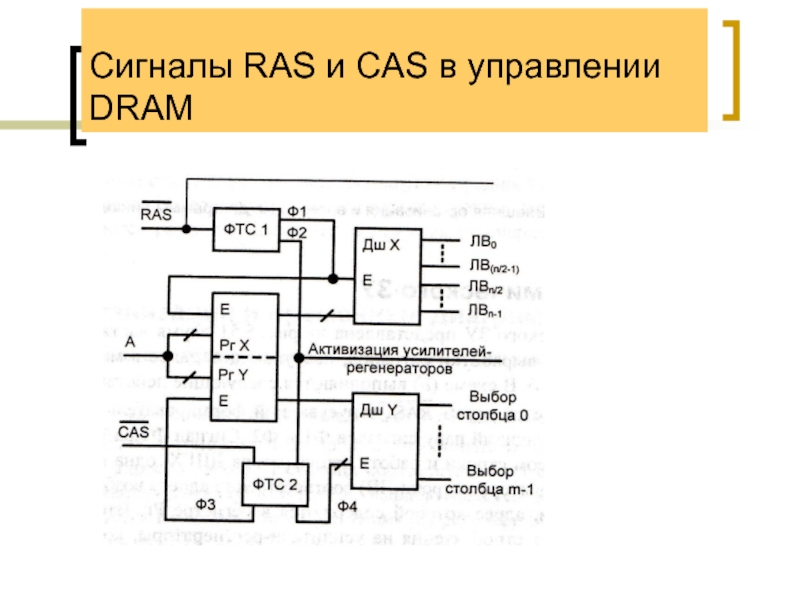

- 34. Сигналы RAS и CAS в управлении DRAM

- 35. Методы повышения быстродействия динамических ЗУ Быстрый

- 36. Эволюция оперативной памяти динамического типа FPM –

- 37. Асинхронная динамическая память FPM DRAM FPM –

- 38. Асинхронная динамическая память EDO DRAM EDO –

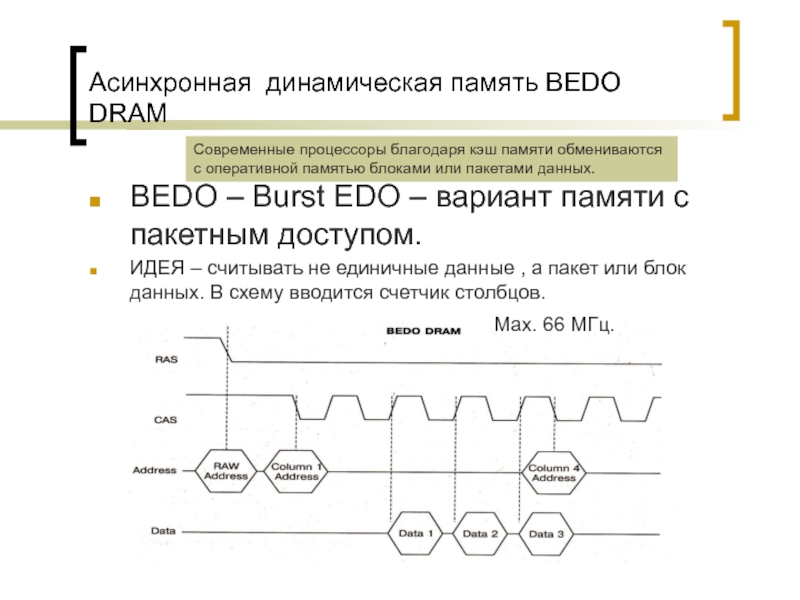

- 39. Асинхронная динамическая память BEDO DRAM BEDO –

- 40. Недостаток асинхронной динамической памяти Процессор ждет выполнение

- 41. Переход к синхронной динамической памяти. Особенности организации.

- 42. Синхронная динамическая память SDRAM Синхронизация входных и

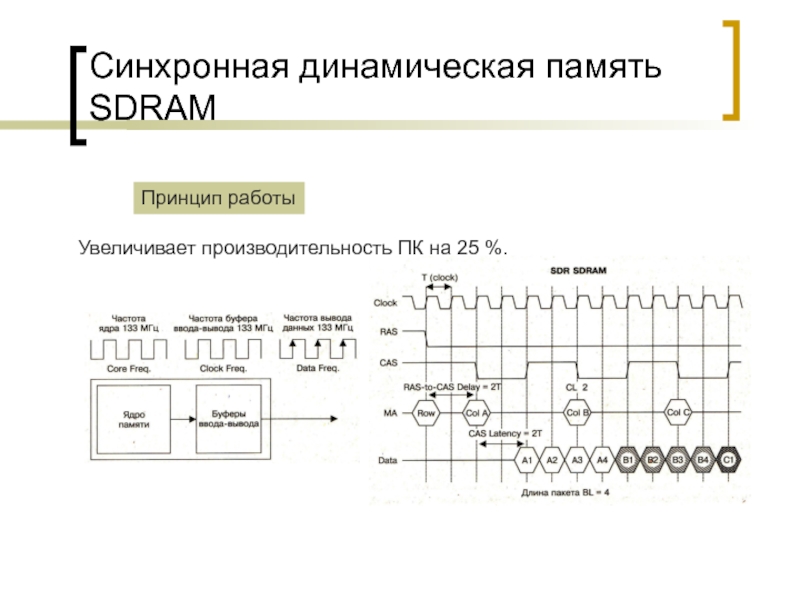

- 43. Синхронная динамическая память SDRAM Принцип работы Увеличивает производительность ПК на 25 %.

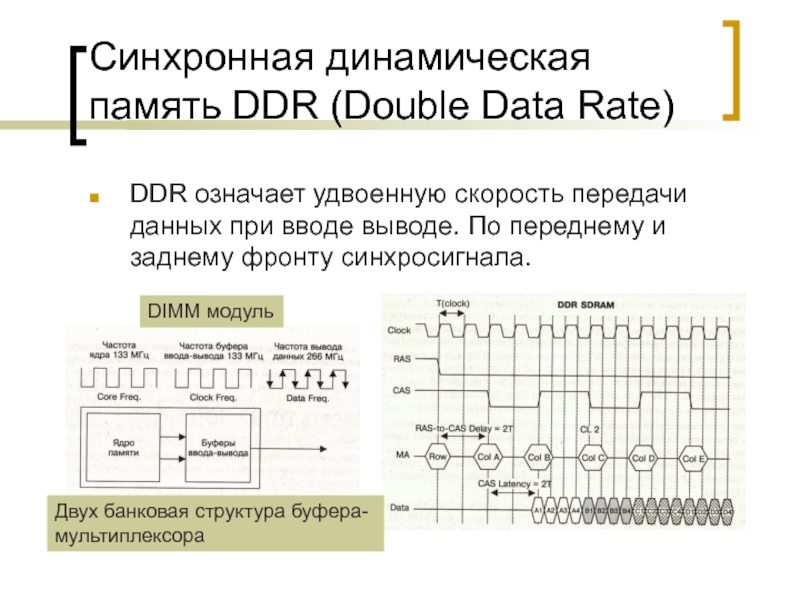

- 44. Синхронная динамическая память DDR (Double Data Rate)

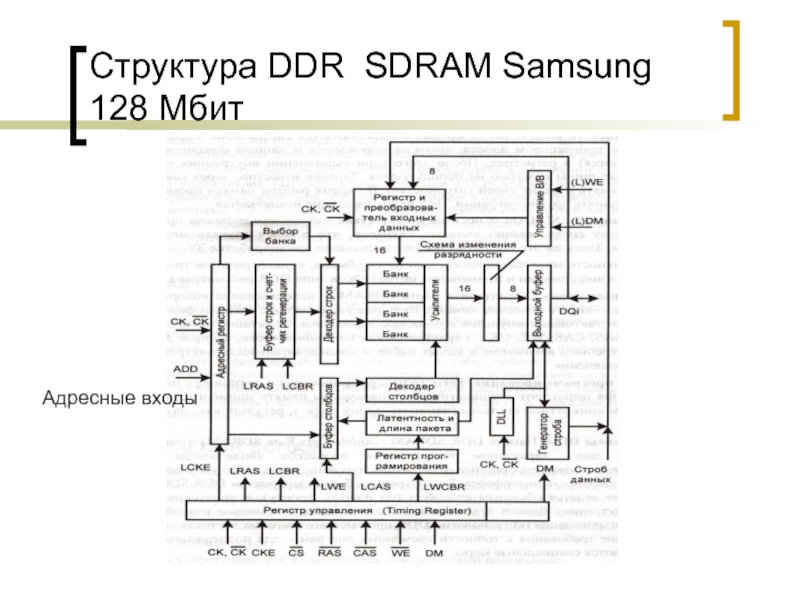

- 45. Структура DDR SDRAM Samsung 128 Мбит Адресные входы

- 46. Память DDR2 SDRAM За каждый такт работы

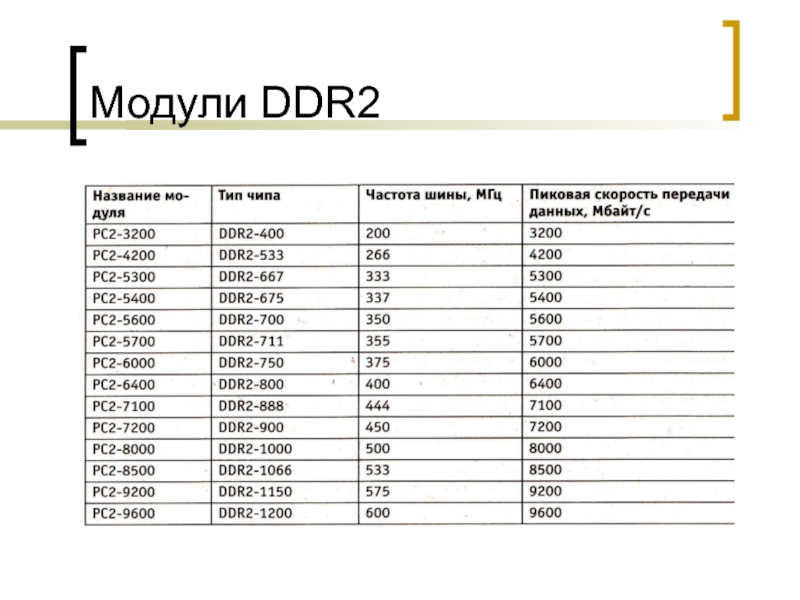

- 47. Модули DDR2

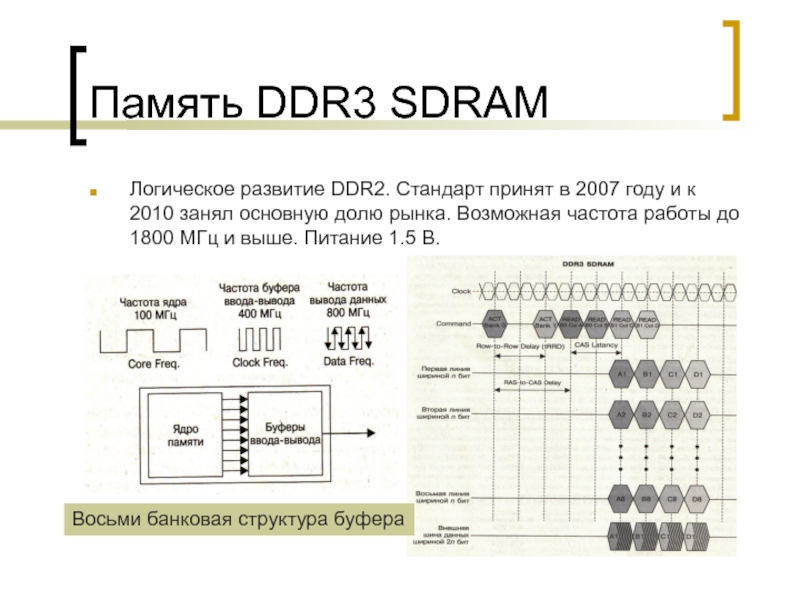

- 48. Память DDR3 SDRAM Логическое развитие DDR2. Стандарт

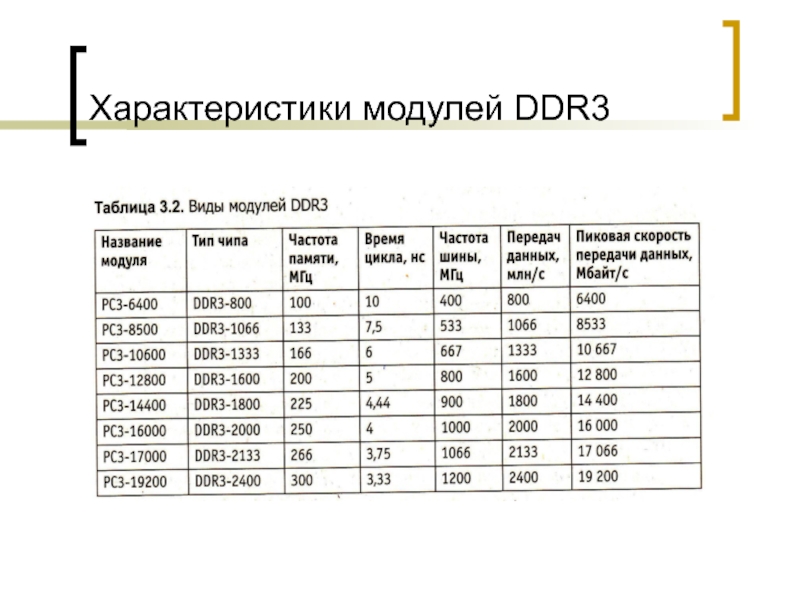

- 49. Характеристики модулей DDR3

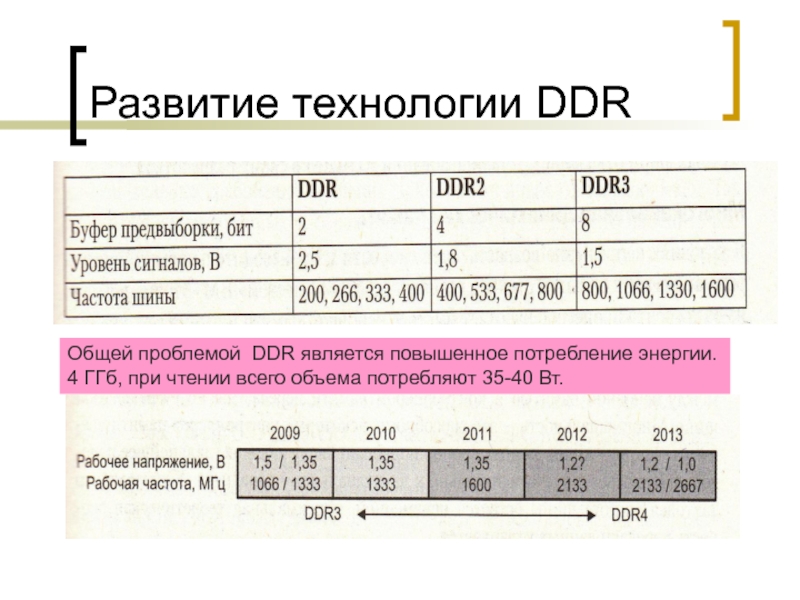

- 50. Развитие технологии DDR Общей проблемой DDR является

- 51. Rambus DRAM Применяется в графических и мультимедийных

- 52. RLDRAM (Reduced Latency DRAM) Идея – уменьшение

- 53. FCRAM (Fast Cycle RAM) Идея – сегментация

- 54. Перспективные ЗУ FRAM – ферроэлектрические. PFRAM –

- 55. Виды модулей оперативной памяти SIMM – (Single

- 56. Виды модулей оперативной памяти DIMM (Dual In-line

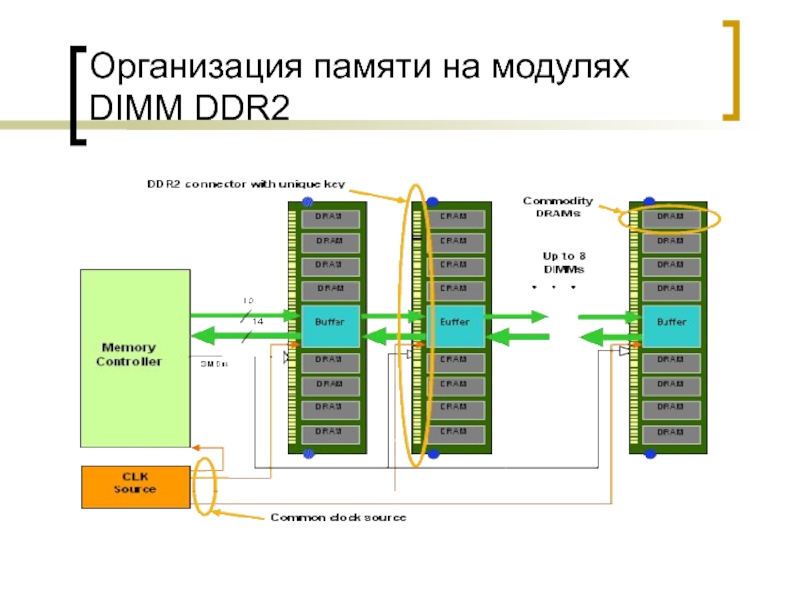

- 57. Организация памяти на модулях DIMM DDR2

- 58. Виды модулей оперативной памяти RIMM (Rambus In-line

- 59. Энергонезависимые ОЗУ Микросхемы BBSRAM (Battery-Back SRAM) –

Слайд 2Характеристики запоминающих устройств

Емкость.

Разрядность.

Способ доступа.

Физический тип или тип носителя.

Быстродействие.

Способ организации.

Стоимость.

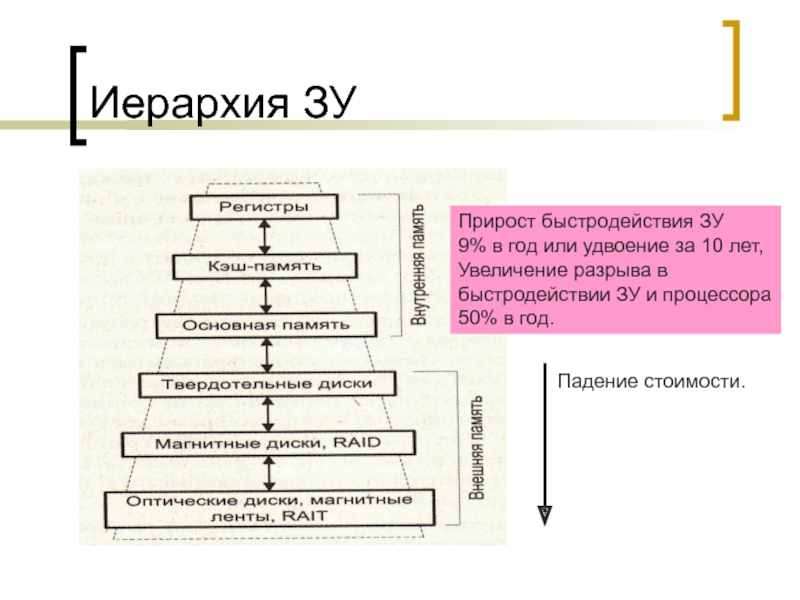

Слайд 4Иерархия ЗУ

Прирост быстродействия ЗУ

9% в год или удвоение за 10 лет,

Увеличение

быстродействии ЗУ и процессора

50% в год.

Падение стоимости.

Слайд 6Оперативная память

RAM (Random Access Memory) – память с произвольным доступом.

Динамическая

DRAM

Статическая

SRAM

Триггер

Транзистор и

Кэш-память

Оперативная память

Слайд 8Способы организации ЗУ

Структура 2D;

Структура 3D;

Структура 2DM;

Блочные структуры;

Структура видеопамяти;

Буфер FIFO;

Буфер LIFO;

Буфер круговой;

Кэш

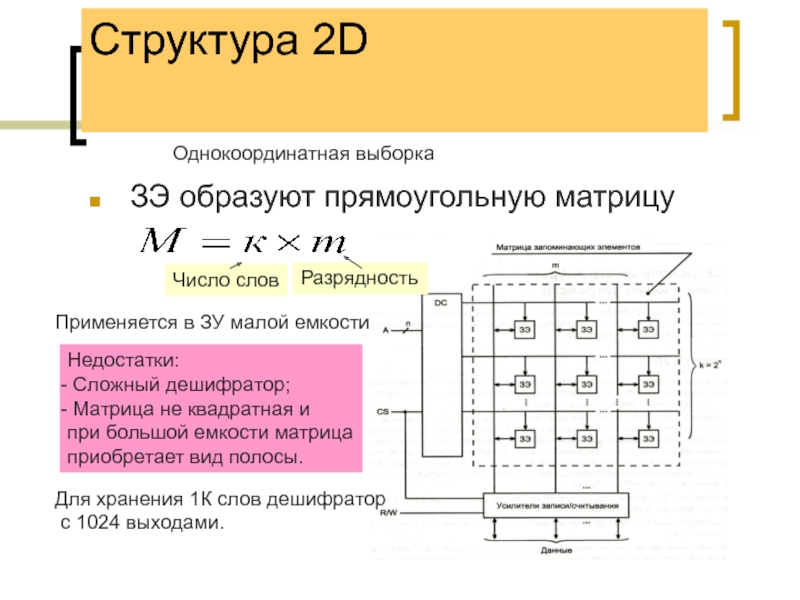

Слайд 9Структура 2D

ЗЭ образуют прямоугольную матрицу

Разрядность

Число слов

Применяется в ЗУ малой емкости

Недостатки:

Матрица не квадратная и

при большой емкости матрица

приобретает вид полосы.

Для хранения 1К слов дешифратор

с 1024 выходами.

Однокоординатная выборка

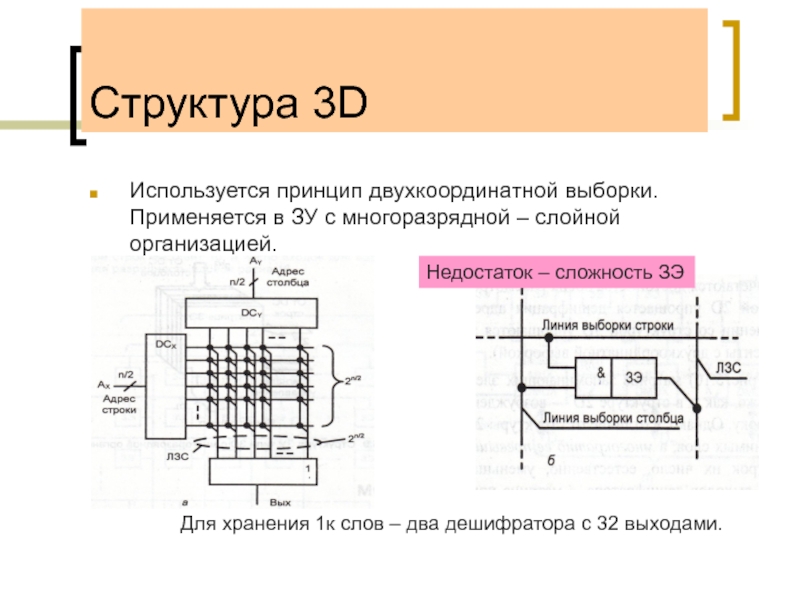

Слайд 10Структура 3D

Используется принцип двухкоординатной выборки. Применяется в ЗУ с многоразрядной –

Для хранения 1к слов – два дешифратора с 32 выходами.

Недостаток – сложность ЗЭ

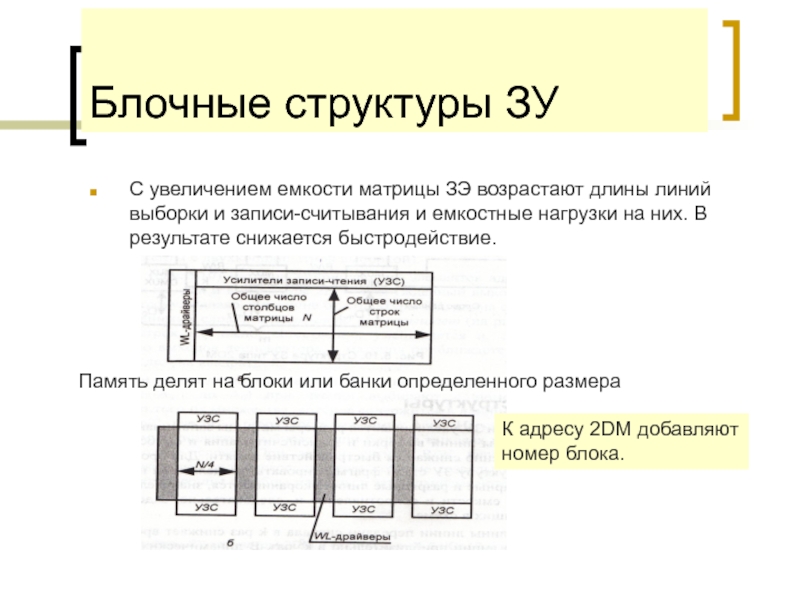

Слайд 12Блочные структуры ЗУ

С увеличением емкости матрицы ЗЭ возрастают длины линий выборки

К адресу 2DM добавляют

номер блока.

Память делят на блоки или банки определенного размера

Слайд 13Блочная организация оперативной памяти

Пока идет регенерация в одном банке, можно работать

Слайд 15Много портовые ОЗУ

Обеспечивают возможность одновременного доступа к памяти двух устройств (Процессоров).

Проблемы

адресом, но такая вероятность не более 0.1%..

Слайд 16Буфер FIFO

ЗУ для хранения очередей данных. Принцип - первый вошел

первый

В начале работы CTR обнуляются

При CTR1=CTR2, то

буфер полон. Прием

данных запрещен.

При CTR1=CTR2=0,

то буфер пуст и чтение

запрещено.

Применяются в МАС контроллерах, обеспечивающих Ethernet связь.

Слайд 17Буфер LIFO

ЗУ работает по принципу последний пришел, первый вышел.

Стековая память. Применяется

процессора при обработке прерываний.

Слайд 18Круговой буфер

Применяется при решении задач цифровой обработки сигналов,

обеспечивая задержку данных для

Работает по принципу – сначала чтение.

По нулевому адресу записываютcя

входные данные, из этой же

ячейки считываютcя выходные

в режиме Read First.

Слайд 19Схема взаимодействия процессора ОЗУ и кэш-памяти

Процессор имея адрес нужной информации сначала

Есть информация в кэш или нет. Если есть, то HIT – кэш попадание.

Слайд 20Запоминающий элемент КМОП

Считывание

Запись

Т1 и Т2 – транзисторы

малой мощности.

Т3 – имеет мощность

большую, чем Т1,Т2 для

обеспечения режима

Переключения.

Статическая память

Слайд 21Асинхронная статическая память

256К на 4 = 1 Мбит.

Структура 3D.

Режим понижения мощности

рower-down

потребляемой мощности).

В данной схеме применяется

мультиплексирование шины

ввода-вывода данных DIO

Слайд 25Синхронная статическая память

RG

RG

9

си

При добавлении выделенных регистров, работающих по переднему

фронту синхросигнала –

Слайд 26Искусственная энергонезависимость статических ЗУ для КМОП

Схемы подключения резервных источников питания

Uрезерва меньше

Желательно быстрее реагировать на

изменение питания.

Электронное реле

Триггер управления реле

Слайд 27Искусственная энергонезависимость статических ЗУ – NV-SRAM

Выпускаются с 1996 г.

Схема

Контроля

За питанием

Статическое

ЗУ

ПЗУ

Блок

U low

NV-SRAM – Non volatile SRAM

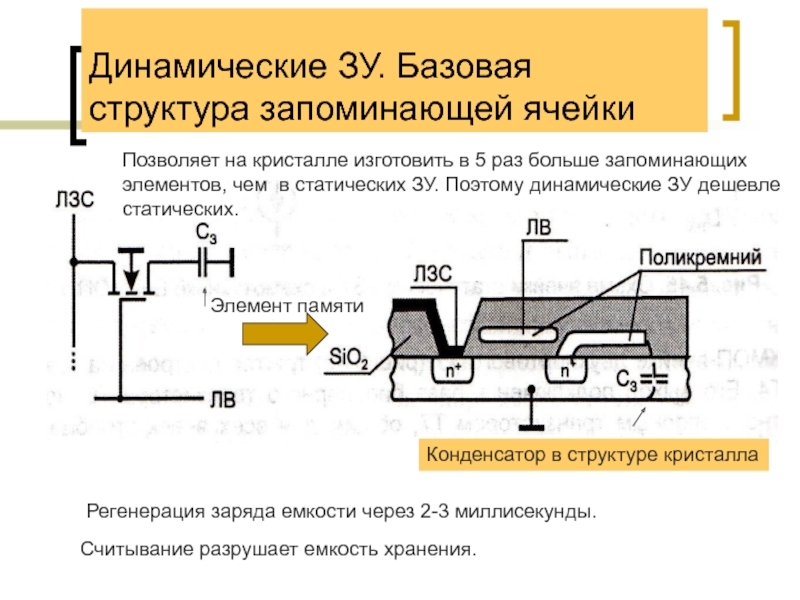

Слайд 28Динамические ЗУ. Базовая структура запоминающей ячейки

Позволяет на кристалле изготовить в 5

элементов, чем в статических ЗУ. Поэтому динамические ЗУ дешевле

статических.

Регенерация заряда емкости через 2-3 миллисекунды.

Считывание разрушает емкость хранения.

Элемент памяти

Конденсатор в структуре кристалла

Слайд 29Особенности динамических ЗУ

Поток обращений к динамическому ЗУ должен учитывать состояние в

Регенерация может быть циклической или после чтения.

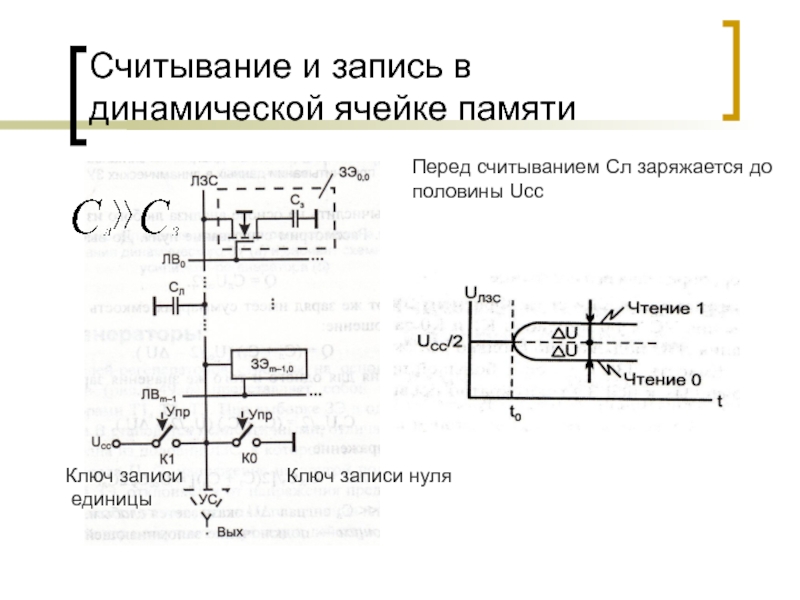

Слайд 30Считывание и запись в динамической ячейке памяти

Ключ записи нуля

Ключ записи

единицы

Перед

половины Uсс

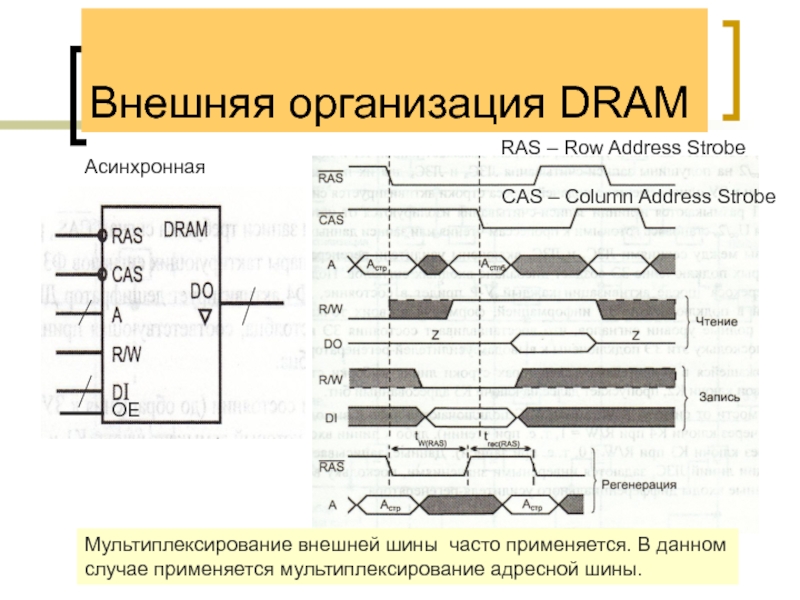

Слайд 31Внешняя организация DRAM

Мультиплексирование внешней шины часто применяется. В данном

случае применяется мультиплексирование

Асинхронная

RAS – Row Address Strobe

CAS – Column Address Strobe

ОЕ

Слайд 33Структурная схема динамической памяти

Блок

регенерации

RAS

RAW

Дешифратор

столбца

Дешифратор

строки

запись

чтение

Узп

Учт

Ядро

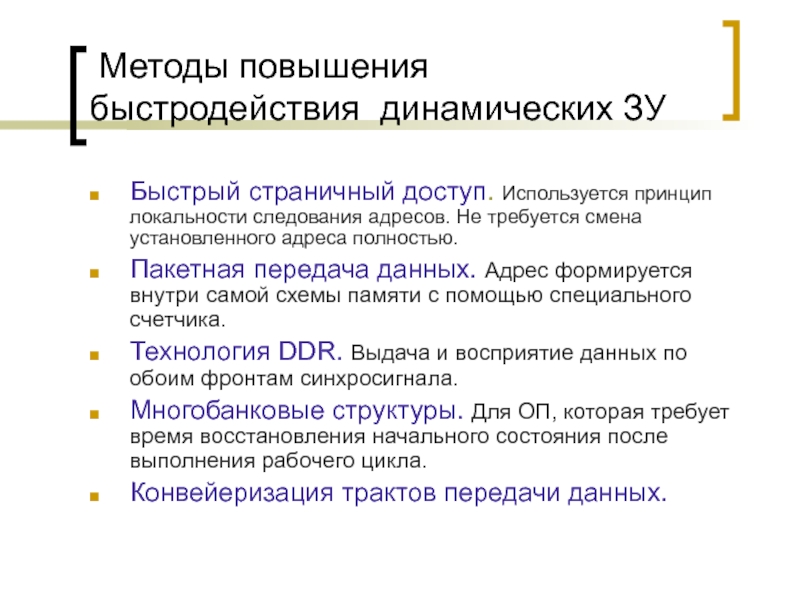

Слайд 35 Методы повышения быстродействия динамических ЗУ

Быстрый страничный доступ. Используется принцип локальности

Пакетная передача данных. Адрес формируется внутри самой схемы памяти с помощью специального счетчика.

Технология DDR. Выдача и восприятие данных по обоим фронтам синхросигнала.

Многобанковые структуры. Для ОП, которая требует время восстановления начального состояния после выполнения рабочего цикла.

Конвейеризация трактов передачи данных.

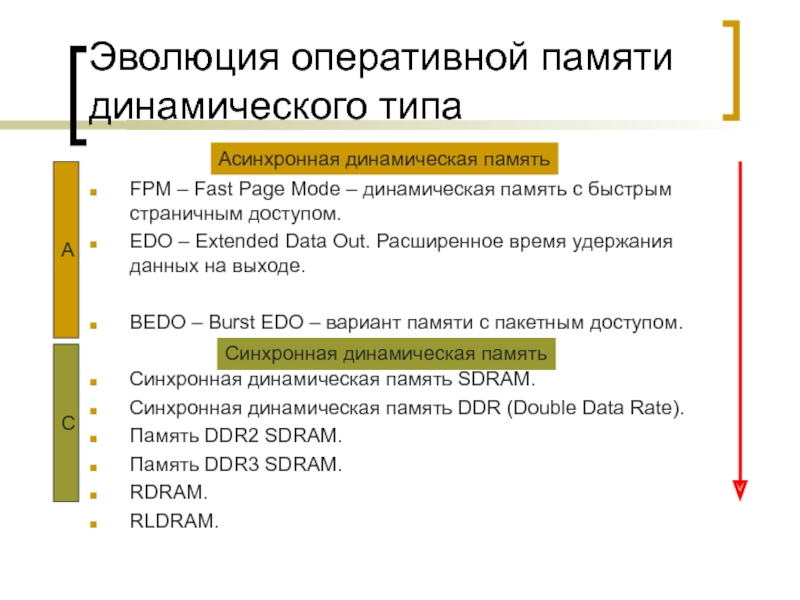

Слайд 36Эволюция оперативной памяти динамического типа

FPM – Fast Page Mode – динамическая

EDO – Extended Data Out. Расширенное время удержания данных на выходе.

BEDO – Burst EDO – вариант памяти с пакетным доступом.

Синхронная динамическая память SDRAM.

Синхронная динамическая память DDR (Double Data Rate).

Память DDR2 SDRAM.

Память DDR3 SDRAM.

RDRAM.

RLDRAM.

А

С

Синхронная динамическая память

Асинхронная динамическая память

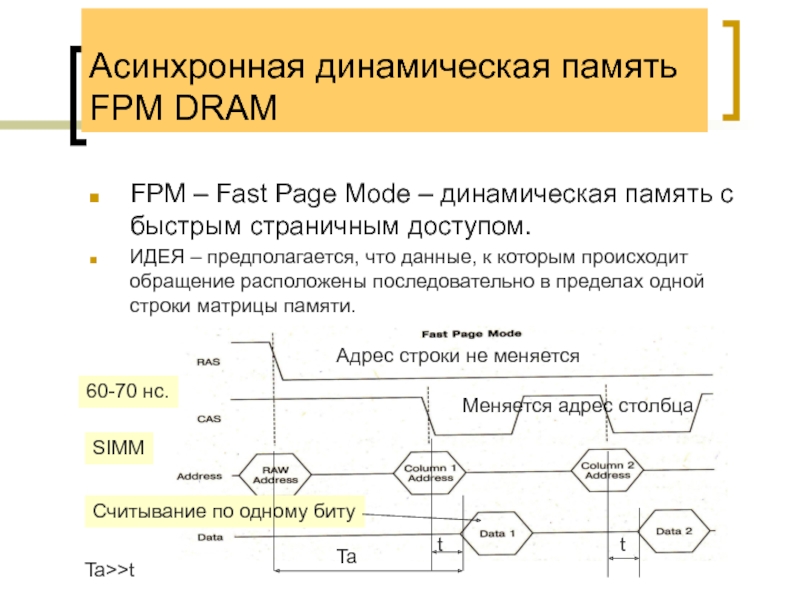

Слайд 37Асинхронная динамическая память FPM DRAM

FPM – Fast Page Mode – динамическая

ИДЕЯ – предполагается, что данные, к которым происходит обращение расположены последовательно в пределах одной строки матрицы памяти.

60-70 нс.

SIMM

Считывание по одному биту

Адрес строки не меняется

Меняется адрес столбца

Ta

t

t

Ta>>t

Слайд 38Асинхронная динамическая память EDO DRAM

EDO – Extended Data Out. Расширенное время

Идея – повторяет принцип FPM , но на выходе микросхемы памяти устанавливают регистры защелки, которые хранят выбранные данные до прихода следующих. При этом может выполнятся следующая выборка. Используется статический буфер для считывания данных.

На 15% эффективней FPM DRAM. Время обращения 45 нс.

Максимальная скорость по каналу процессор память 264 Мбайт\сек. Выпускалась в конструктивах SIMM и DIMM-

Слайд 39Асинхронная динамическая память BEDO DRAM

BEDO – Burst EDO – вариант памяти

ИДЕЯ – считывать не единичные данные , а пакет или блок данных. В схему вводится счетчик столбцов.

Мах. 66 МГц.

Современные процессоры благодаря кэш памяти обмениваются

с оперативной памятью блоками или пакетами данных.

Слайд 40Недостаток асинхронной динамической памяти

Процессор ждет выполнение операций с памятью. Других действий

Слайд 41Переход к синхронной динамической памяти. Особенности организации.

Увязка операций с тактирующими сигналами.

Буферизация

Многобанковые структуры.

Пакетный режим.

Конвейеризация тракта продвижения информации.

Слайд 42Синхронная динамическая память SDRAM

Синхронизация входных и выходных сигналов с тактами системного

Весь массив памяти делится на два банка. В одном происходит чтение, а в другом установка адреса - конвейер.

100-133 МГц

64 р –шина данных, за такт 8 байт

Слайд 43Синхронная динамическая память SDRAM

Принцип работы

Увеличивает производительность ПК на 25 %.

Слайд 44Синхронная динамическая память DDR (Double Data Rate)

DDR означает удвоенную скорость передачи

DIMM модуль

Двух банковая структура буфера-

мультиплексора

Слайд 46Память DDR2 SDRAM

За каждый такт работы ядра на шину данных выдается

Четырех банковая структура буфера

Слайд 48Память DDR3 SDRAM

Логическое развитие DDR2. Стандарт принят в 2007 году и

Восьми банковая структура буфера

Слайд 50Развитие технологии DDR

Общей проблемой DDR является повышенное потребление энергии.

4 ГГб, при

Слайд 51Rambus DRAM

Применяется в графических и мультимедийных приложениях – там где надо

Основное новшество – 16 разрядный интерфейс для пакетной передачи данных. В формате пакета содержится адрес и данные. Ближе к HTи PCIE.

Слайд 52RLDRAM (Reduced Latency DRAM)

Идея – уменьшение длительности полного цикла обращения к

Слайд 53FCRAM (Fast Cycle RAM)

Идея – сегментация ядра памяти и выполнение одновременной

Слайд 54Перспективные ЗУ

FRAM – ферроэлектрические.

PFRAM – полимерно-ферроэлектрические.

MRAM – магниторезистивные.

Использование в качестве элемента

конденсатор или остаточную намагниченность ферромагнитного

материала.

Слайд 55Виды модулей оперативной памяти

SIMM – (Single In-line Memory Module) - печатная

Слайд 56Виды модулей оперативной памяти

DIMM (Dual In-line Memory Module) – печатная плата

So-DIMM

Слайд 58Виды модулей оперативной памяти

RIMM (Rambus In-line Memory Module) – похожи на

Слайд 59Энергонезависимые ОЗУ

Микросхемы BBSRAM (Battery-Back SRAM) – обычные ОЗУ со встроенным литиевым

Микросхемы NVRAM (Non-Volatile RAM) – в одном корпусе статическое ОЗУ и перепрограммируемая ПЗУ.

Микросхемы FRAM (Ferroelectric RAM) – ферроэлектрическая память.

Их отличие от многократно программируемых ПЗУ заключается

в отсутствии предварительного этапа стирания, предваряющего запись.