- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Основы схемотехники ЭВМ презентация

Содержание

- 1. Основы схемотехники ЭВМ

- 2. 4096tb@gmail.com Тема

- 3. Лекция 1. Представление информации. Системы счисления. Формат

- 4. Лекция 2. Формат с плавающей запятой. Стандарт

- 5. Лекция 3. Логические основы ЭВМ. Минимизация. План

- 6. Лекция 4. Основы схемотехники ЭВМ. План лекции:

- 7. Логический элемент как физическое устройство Для описания

- 8. Логические (комбинационные) схемы Логическая схема (ЛС),

- 9. Логические элементы ИЛИ И НЕ И-НЕ

- 10. Логические элементы ИЛИ И НЕ И-НЕ

- 11. Пример реализации ЛФ («Сумматор» -суммирование чисел

- 12. Пример реализации ЛФ (Схема охранной сигнализации

- 13. Триггер Триггеры (англ. Trigger - защёлка,

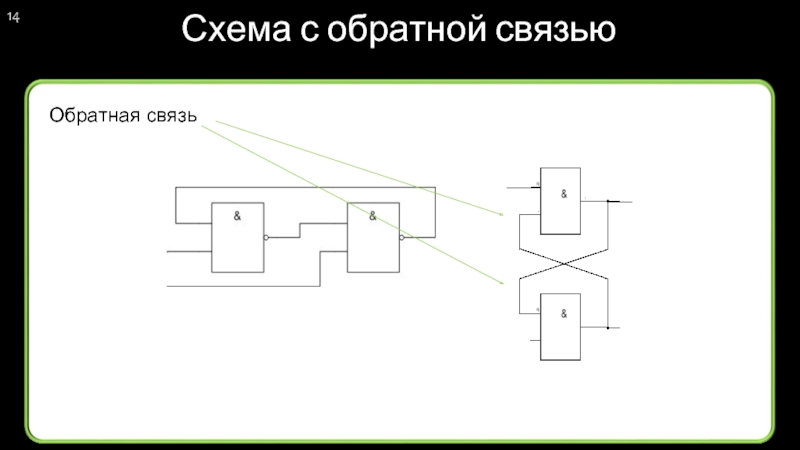

- 14. Схема с обратной связью Обратная связь

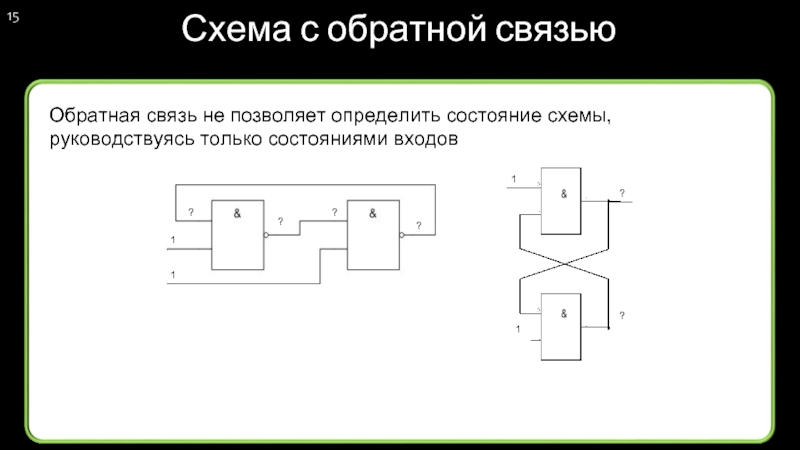

- 15. Схема с обратной связью 1 1 1

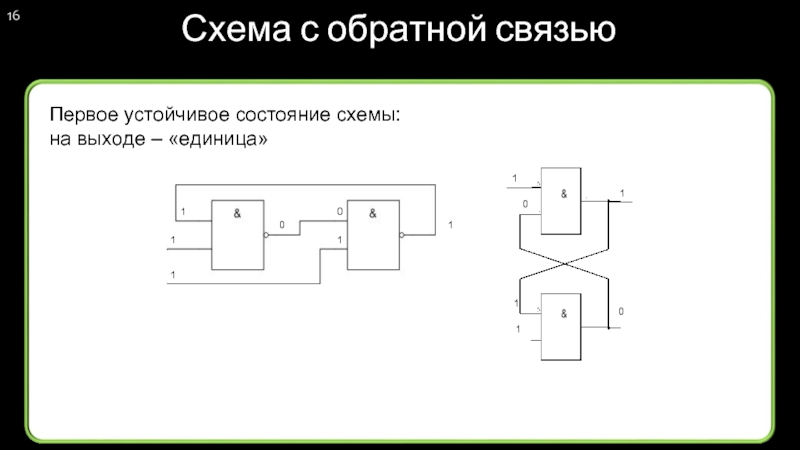

- 16. Схема с обратной связью 1 1 1

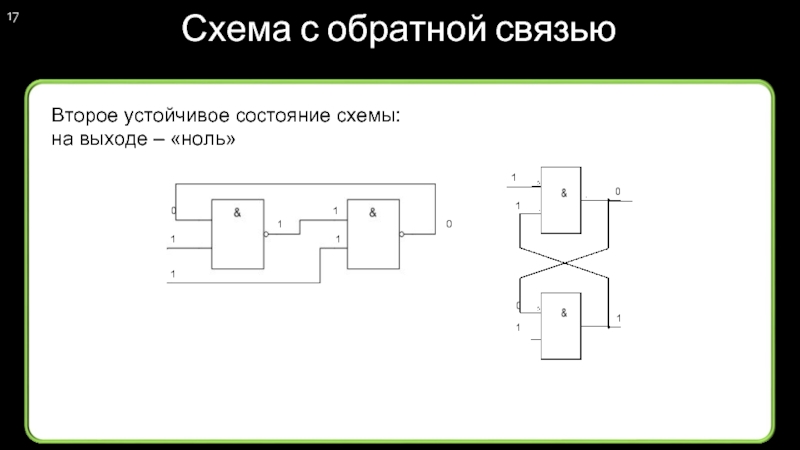

- 17. Схема с обратной связью 1 1 0

- 18. Схема с обратной связью 0 0 1

- 19. RS-триггер RS-триггер - это триггер с раздельной установкой состояний логического

- 20. RS-триггер – бистабильная ячейка Таблица переходов

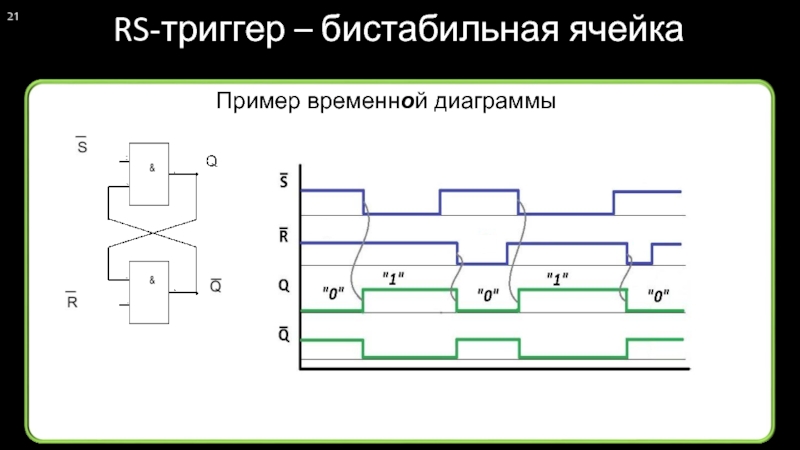

- 21. RS-триггер – бистабильная ячейка Пример временной диаграммы

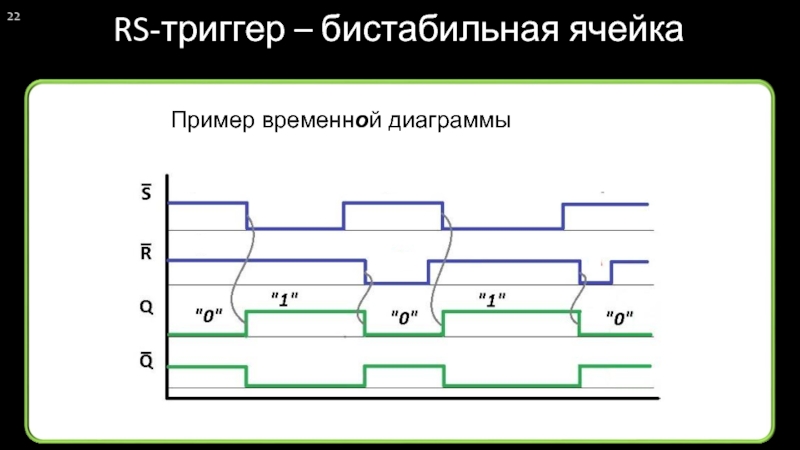

- 22. RS-триггер – бистабильная ячейка Пример временной диаграммы

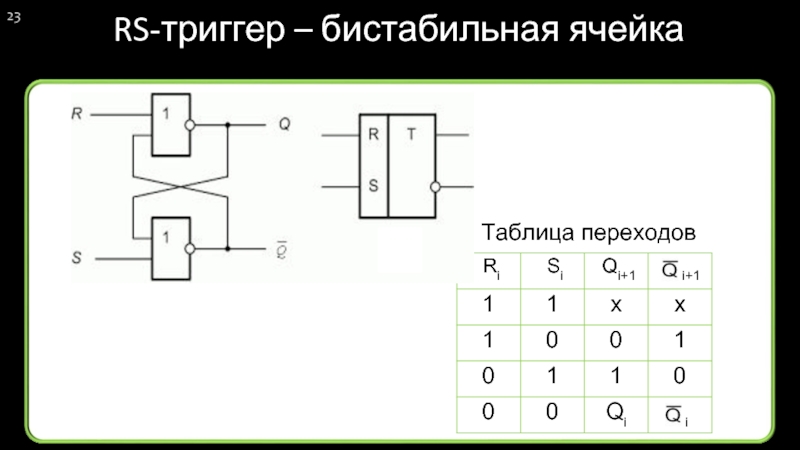

- 23. RS-триггер – бистабильная ячейка Таблица переходов

- 24. RS-триггер – бистабильная ячейка Таблица переходов С

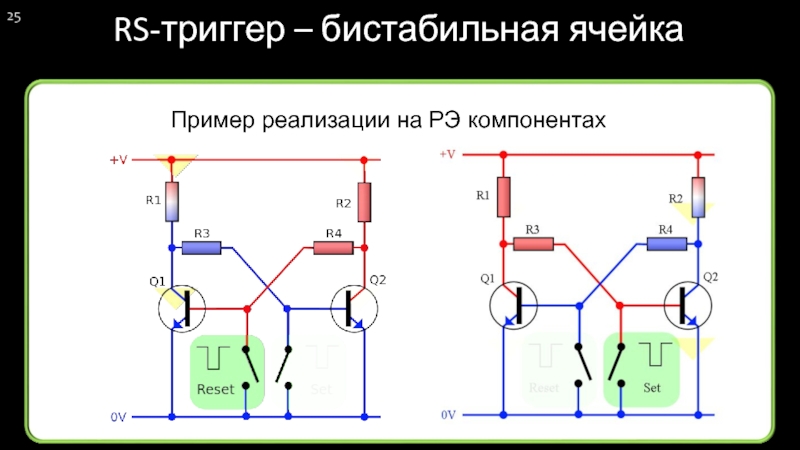

- 25. RS-триггер – бистабильная ячейка Пример реализации на РЭ компонентах

- 26. JK-триггер – бистабильная ячейка Таблица переходов Исключено

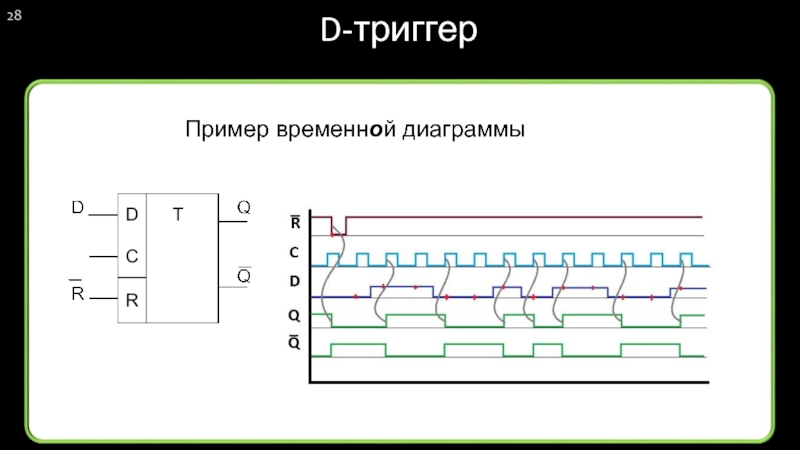

- 27. D-триггер (англ. Delay-задержка) Таблица переходов В

- 28. D-триггер Пример временной диаграммы

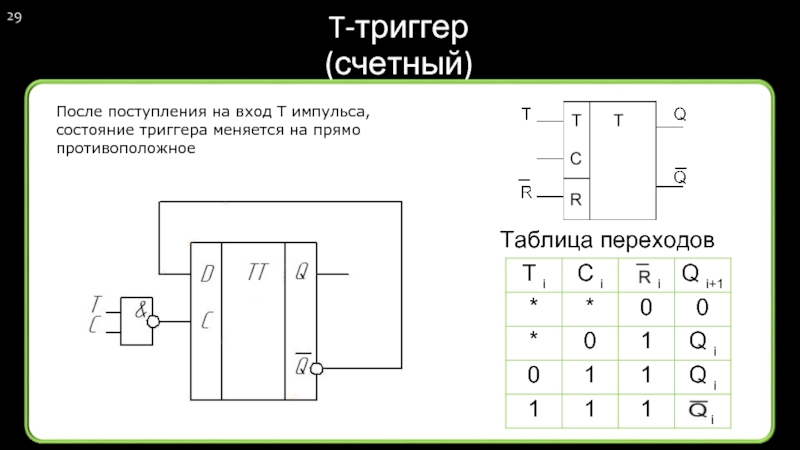

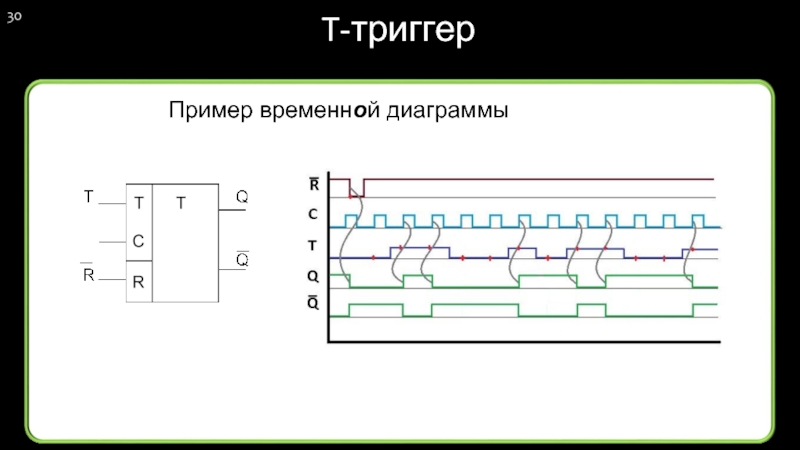

- 29. T-триггер (счетный) Таблица переходов После поступления на

- 30. T-триггер Пример временной диаграммы

- 31. Функциональные узлы ЭВМ Регистры Счетчики Шифраторы Дешифраторы Мультиплексоры Сумматоры АЛУ

- 32. Регистры Регистр — устройство, используемое для хранения

- 33. Регистры …

- 34. Счетчики C 0 1 2 3 На

- 35. Дешифраторы D2 D1 D0 0

- 36. Шифраторы m вых n вх Шифратор (англ.

- 37. Мультиплексоры S=0 ⇒ Y = A

- 38. Сумматоры Сумматор — устройство, преобразующее информационные сигналы

- 39. Сумматоры Комбинационный сумматор An-1 … A0 Bn-1

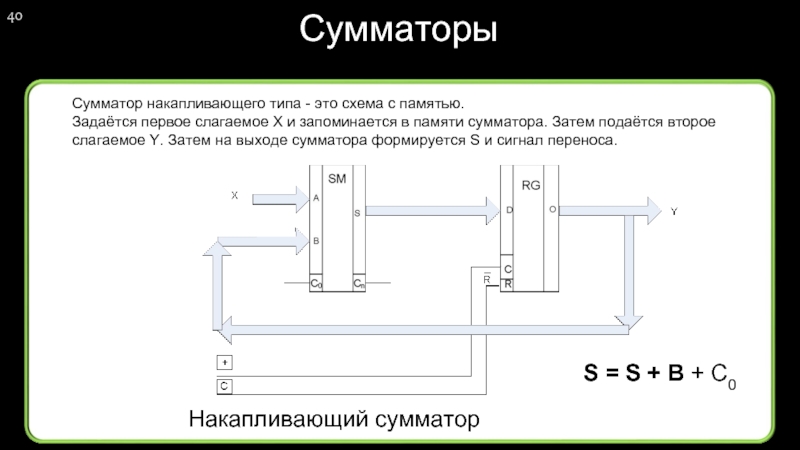

- 40. Сумматоры Накапливающий сумматор S = S +

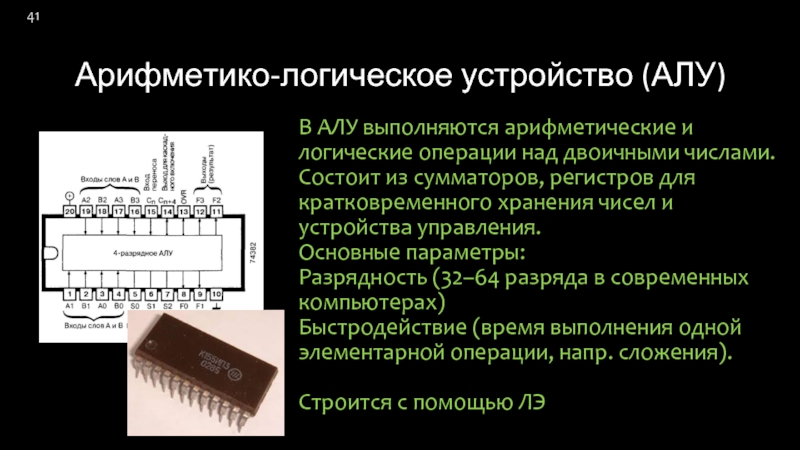

- 41. Арифметико-логическое устройство (АЛУ) В АЛУ выполняются арифметические

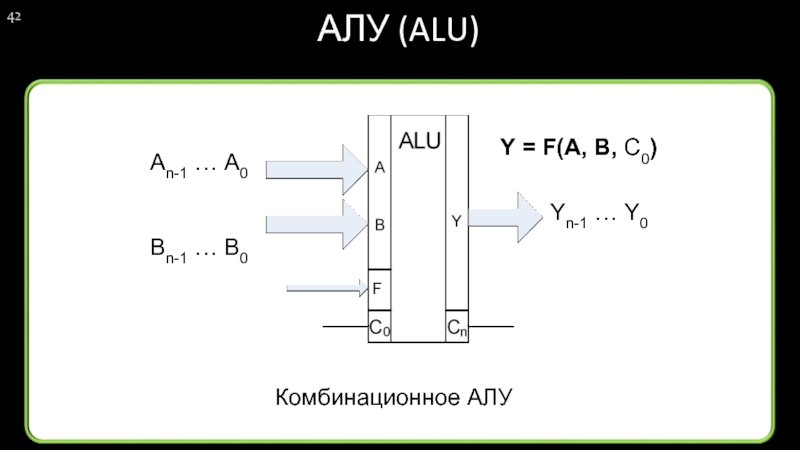

- 42. АЛУ (ALU) Комбинационное АЛУ An-1 … A0

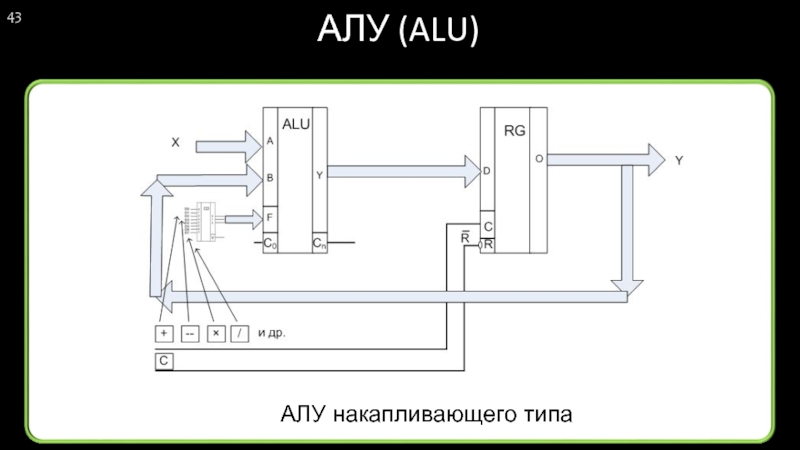

- 43. АЛУ (ALU) АЛУ накапливающего типа

- 44. Структура процессора

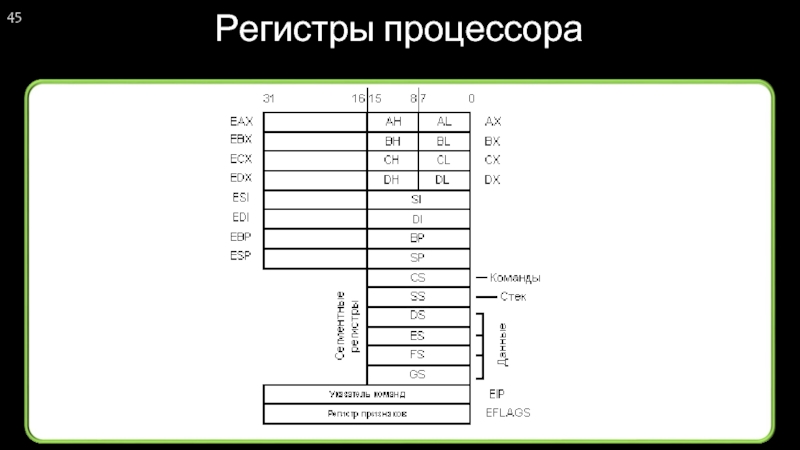

- 45. Регистры процессора

- 46. Регистр признаков (PSW) Cлово состояния процессора (ССП) англ. PSW — Processor Status Word

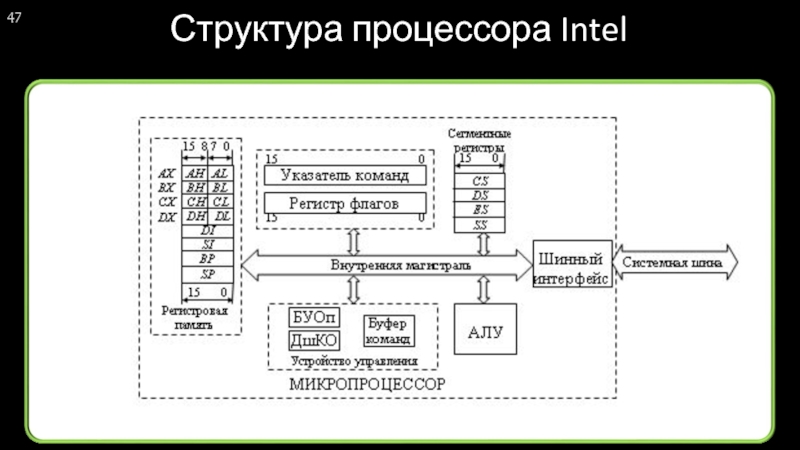

- 47. Структура процессора Intel

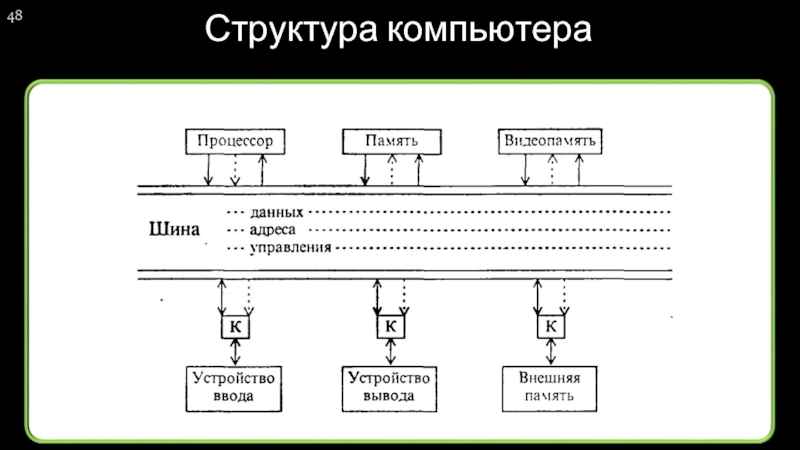

- 48. Структура компьютера

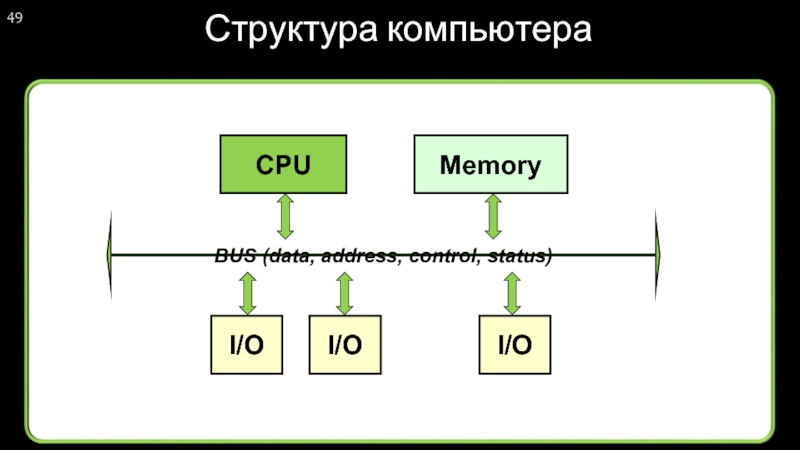

- 49. Структура компьютера

- 50. Основы схемотехники ЭВМ. ТСИС (Технические средства

Слайд 1Основы схемотехники ЭВМ.

Ковалевский Вячеслав Викторович

Лекция 4

(По материалам Мухаметова В.Н.)

2016

ТСИС

(Технические средства

Программное обеспечение информационных систем (1-40 01 73)

Гр. 6 0 3 2 5 , 6 0 3 2 6

Слайд 3Лекция 1. Представление информации. Системы счисления.

Формат с фиксированной запятой

План лекции:

История развития

Понятие информации.

Принцип программного управления.

Двоичная и шестнадцатеричная системы счисления.

Прямой и дополнительный код.

Арифметические действия в Формате ФЗ.

Переполнение.

Экзаменационные вопросы:

Информационная система. Информация. История развития компьютера.

Позиционные системы счисления. Перевод чисел из одной системы счисления в другую.

Арифметика ЭВМ. Представление чисел в форме с фиксированной точкой.

Сложение в формате с фиксированной точкой. Переполнение.

Операция вычитания с фиксированной точкой. Дополнительный код числа.

Слайд 4Лекция 2. Формат с плавающей запятой. Стандарт IEEE 754. Погрешности. Обратная

План лекции:

Формат чисел с плавающей запятой.

Стандарт IEEE 754.

Особенности операций в формате с плавающей запятой.

Переполнение порядков.

Точность вычислений.

Обратная польская запись.

Экзаменационные вопросы:

Представление чисел в форме с плавающей точкой. Мантисса и характеристика числа.

Нормализованные и денормализованные числа. Погрешность представления числа.

Арифметические операции в формате с плавающей точкой.

Стандарт IEEE 754.

Формат BCD. Представление текстовой информации. ASCII.

Слайд 5Лекция 3. Логические основы ЭВМ. Минимизация.

План лекции:

Понятия алгебры логики.

Аксиомы и законы

Логические функции: конъюнкция, дизъюнкция, инверсия и другие функции.

Преобразование логических выражений.

Логические элементы.

Логические (комбинационные) схемы.

Понятие о минимизации логических выражений.

Экзаменационные вопросы:

Алгебра логики. Переменные и константы алгебры логики.

Законы и аксиомы алгебры логики. Логические функции.

Конъюнкция. Дизъюнкция. Инверсия. Функционально полная система ЛФ. Функции И-НЕ, ИЛИ-НЕ, Исключающее ИЛИ.

Формы представления ЛФ. Таблица истинности. СДНФ и СКНФ. Переход от одной формы к другой.

Преобразование логических выражений. Склеивание. Минимизация логических выражений.

Слайд 6Лекция 4. Основы схемотехники ЭВМ.

План лекции:

Логический элемент как физическое устройство.

RS-триггер –

Понятие синхронизации.

Типы триггеров.

Узлы ЭВМ: регистры, счетчики, сумматоры, шифраторы и дешифраторы, мультиплексоры, АЛУ.

Экзаменационные вопросы:

Логический элемент. Логическая (комбинационная) схема. ЛЭ как физическое устройство.

Обратная связь. Бистабильная ячейка – триггер. RS-триггер, D-триггер, T-триггер.

Синхронный триггер. Понятие о синхронизации.

Узлы ЭВМ. Регистры. Счетчики. Сумматоры. Шифраторы и дешифраторы. Мультиплексоры. АЛУ.

Слайд 7Логический элемент как физическое устройство

Для описания функционирования цифровых схем используется алгебра

В основу алгебры логики положено понятие «событие», которое может наступить, либо не наступить. Наступившее событие считается истинным и выражается уровнем логической «1», не наступившее событие считается ложным и выражается уровнем логического «0».

На событие влияют переменные (аргументы), причем влияют по определенному закону (логическая функция).

Слайд 8Логические (комбинационные) схемы

Логическая схема (ЛС), или схема «без памяти», состоит

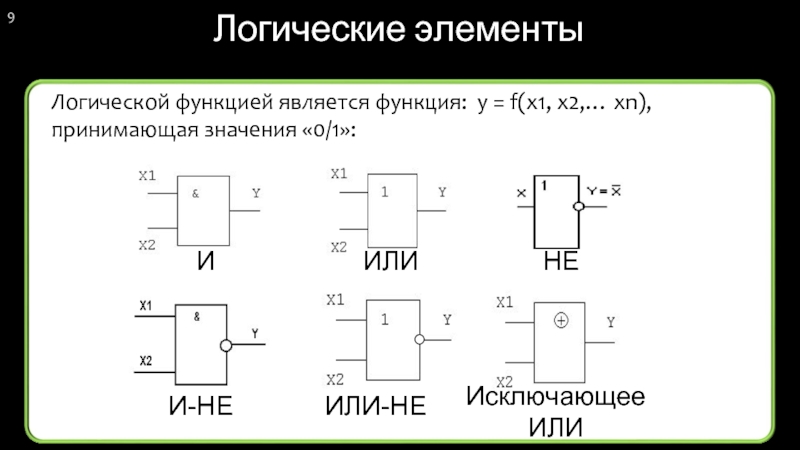

Слайд 9Логические элементы

ИЛИ

И

НЕ

И-НЕ

Логической функцией является функция: у = f(x1, x2,… xn), принимающая

ИЛИ-НЕ

Исключающее ИЛИ

Слайд 10Логические элементы

ИЛИ

И

НЕ

И-НЕ

ИЛИ-НЕ

Исключающее ИЛИ

Логической функцией является функция: у = f(x1, x2,… xn),

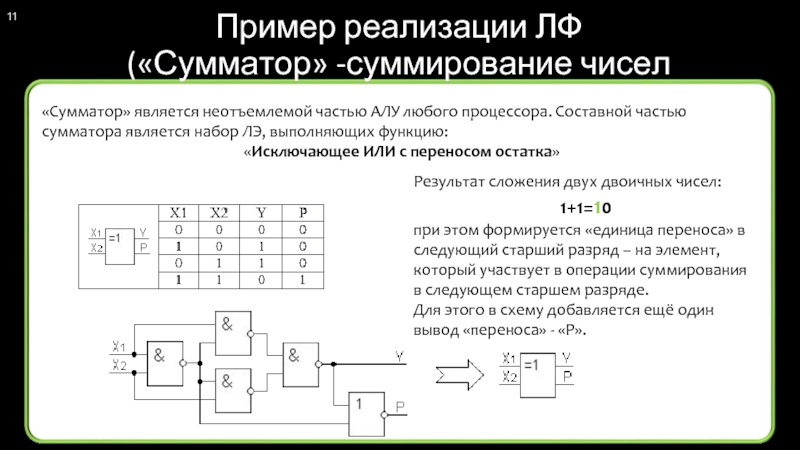

Слайд 11Пример реализации ЛФ

(«Сумматор» -суммирование чисел (2))

«Сумматор» является неотъемлемой частью АЛУ

«Исключающее ИЛИ с переносом остатка»

Результат сложения двух двоичных чисел:

1+1=10

при этом формируется «единица переноса» в следующий старший разряд – на элемент, который участвует в операции суммирования в следующем старшем разряде.

Для этого в схему добавляется ещё один вывод «переноса» - «Р».

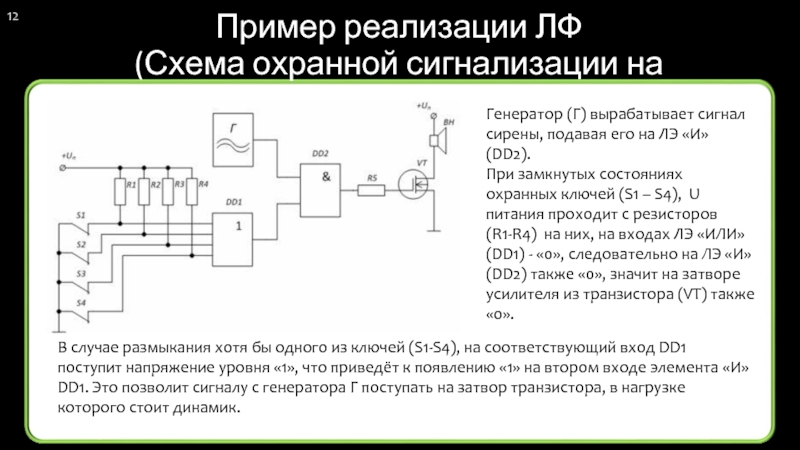

Слайд 12Пример реализации ЛФ

(Схема охранной сигнализации на ЛЭ)

Генератор (Г) вырабатывает сигнал

При замкнутых состояниях охранных ключей (S1 – S4), U питания проходит с резисторов (R1-R4) на них, на входах ЛЭ «ИЛИ» (DD1) - «0», следовательно на ЛЭ «И» (DD2) также «0», значит на затворе усилителя из транзистора (VT) также «0».

В случае размыкания хотя бы одного из ключей (S1-S4), на соответствующий вход DD1 поступит напряжение уровня «1», что приведёт к появлению «1» на втором входе элемента «И» DD1. Это позволит сигналу с генератора Г поступать на затвор транзистора, в нагрузке которого стоит динамик.

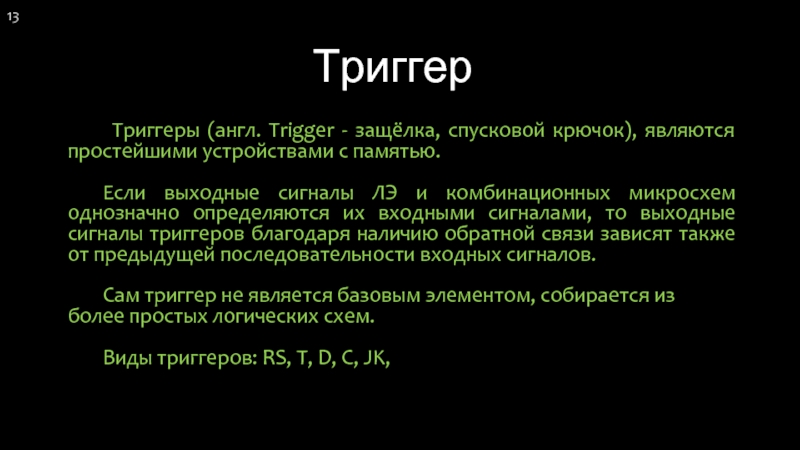

Слайд 13Триггер

Триггеры (англ. Trigger - защёлка, спусковой крючок), являются простейшими устройствами

Если выходные сигналы ЛЭ и комбинационных микросхем однозначно определяются их входными сигналами, то выходные сигналы триггеров благодаря наличию обратной связи зависят также от предыдущей последовательности входных сигналов.

Сам триггер не является базовым элементом, собирается из более простых логических схем.

Виды триггеров: RS, T, D, C, JK,

Слайд 15Схема с обратной связью

1

1

1

1

?

?

?

?

?

?

Обратная связь не позволяет определить состояние схемы, руководствуясь

Слайд 16Схема с обратной связью

1

1

1

1

1

1

0

1

0

1

0

1

0

Первое устойчивое состояние схемы:

на выходе – «единица»

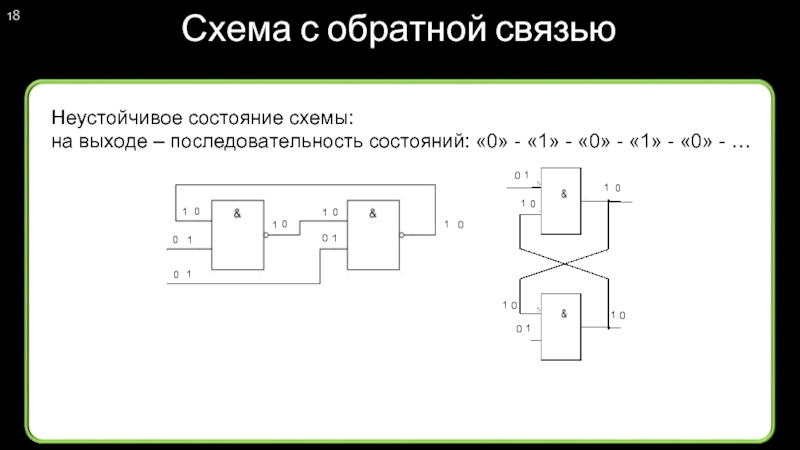

Слайд 18Схема с обратной связью

0

0

1

1

0

1

1

0

0

1

1

0

1

0

0

1

1

0

0

1

0

1

0

1

0

1

Неустойчивое состояние схемы:

на выходе – последовательность состояний:

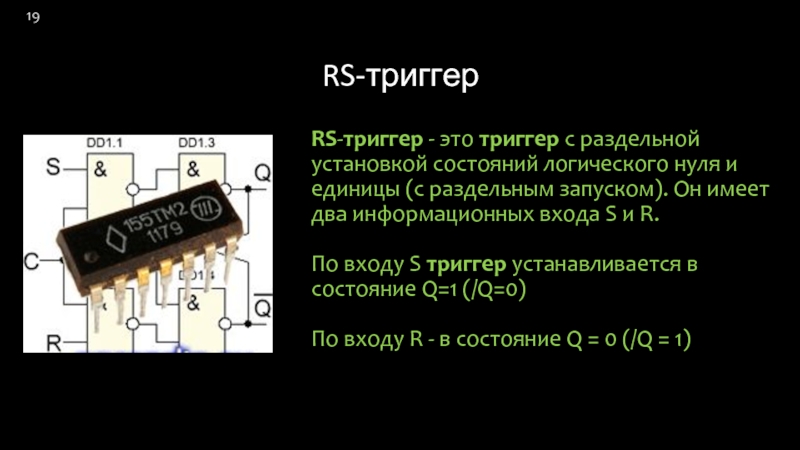

Слайд 19RS-триггер

RS-триггер - это триггер с раздельной установкой состояний логического нуля и единицы (с раздельным

По входу S триггер устанавливается в состояние Q=1 (/Q=0)

По входу R - в состояние Q = 0 (/Q = 1)

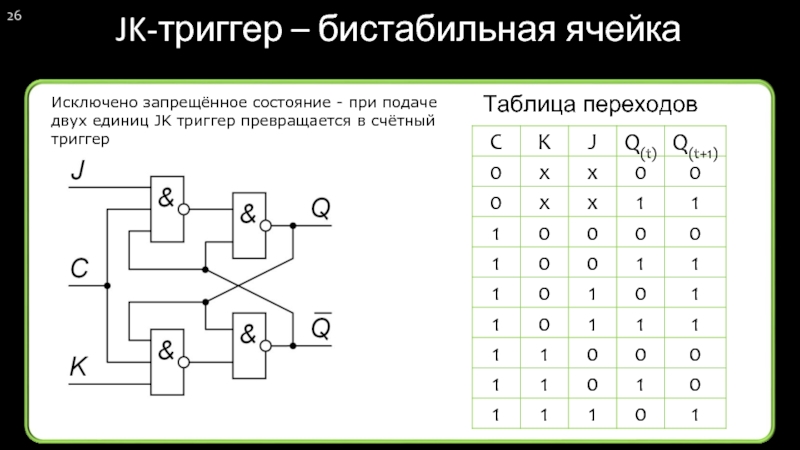

Слайд 26JK-триггер – бистабильная ячейка

Таблица переходов

Исключено запрещённое состояние - при подаче двух

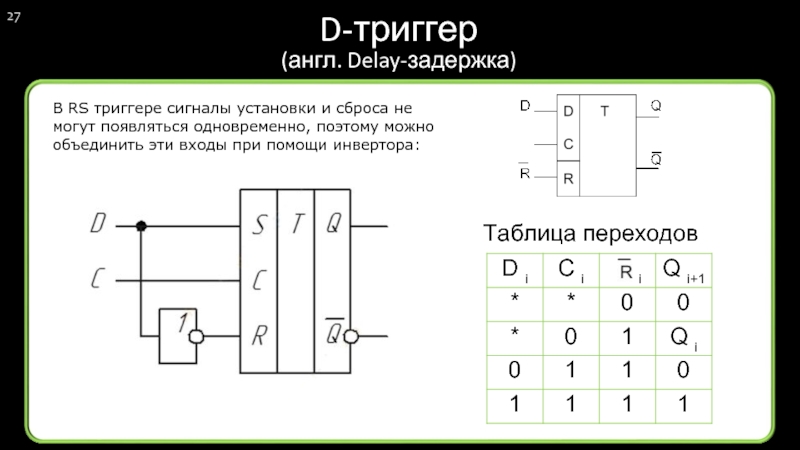

Слайд 27D-триггер

(англ. Delay-задержка)

Таблица переходов

В RS триггере сигналы установки и сброса не

Слайд 29T-триггер

(счетный)

Таблица переходов

После поступления на вход T импульса, состояние триггера меняется на

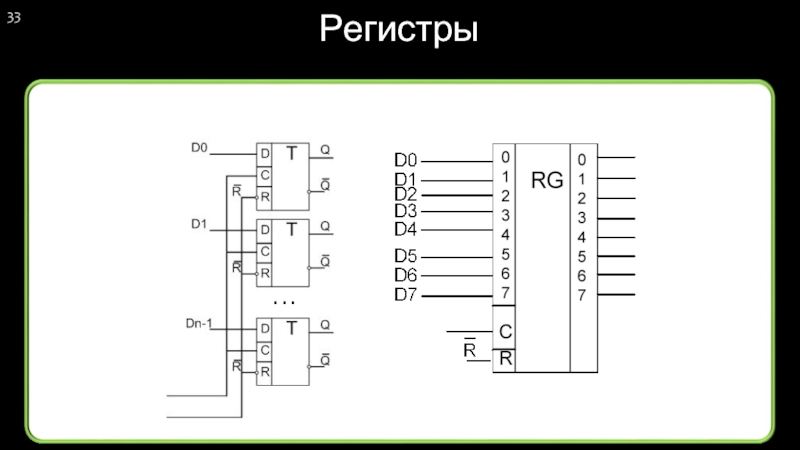

Слайд 32Регистры

Регистр — устройство, используемое для хранения n-разрядных двоичных данных и выполнения

Регистр представляет собой упорядоченный набор триггеров (обычно D) число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Основой построения регистров являются:

D-триггеры, RS-триггеры, JK-триггеры.

Слайд 34Счетчики

C

0

1

2

3

На выходах двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов.

Счётчики на

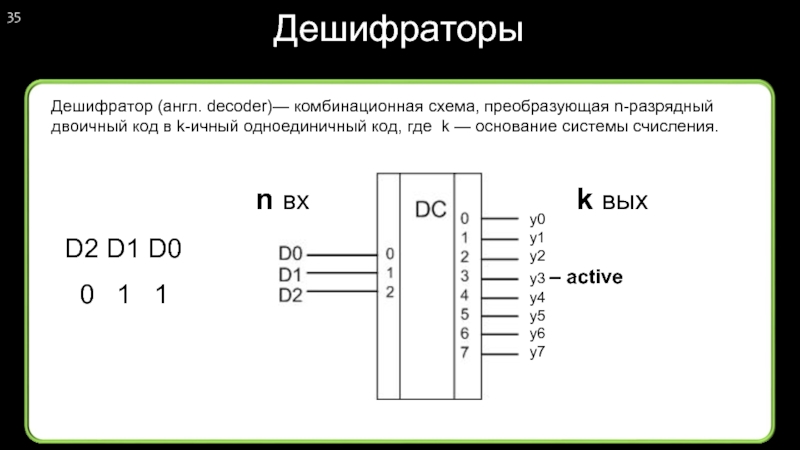

Слайд 35Дешифраторы

D2 D1 D0

0 1 1

y0

y1

y2

y3

n вх

k вых

Дешифратор (англ. decoder)— комбинационная схема, преобразующая n-разрядный двоичный код в k-ичный одноединичный код, где k — основание системы счисления.

Слайд 36Шифраторы

m вых

n вх

Шифратор (англ. encoder) - логическое устройство, выполняющее логическую функцию

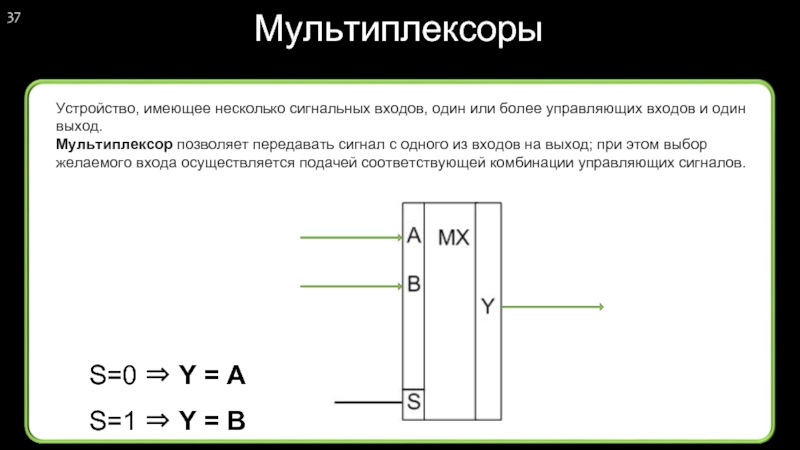

Слайд 37Мультиплексоры

S=0 ⇒ Y = A

S=1 ⇒ Y = B

Устройство, имеющее

Мультиплексор позволяет передавать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.

Слайд 38Сумматоры

Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал,

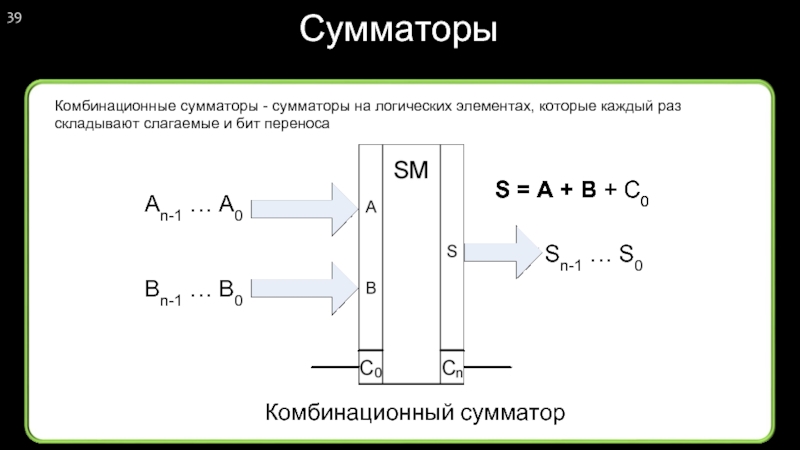

Слайд 39Сумматоры

Комбинационный сумматор

An-1 … A0

Bn-1 … B0

Sn-1 … S0

S = A +

S = A + B + C0

Комбинационные сумматоры - сумматоры на логических элементах, которые каждый раз складывают слагаемые и бит переноса

Слайд 40Сумматоры

Накапливающий сумматор

S = S + B + C0

Сумматор накапливающего типа -

Задаётся первое слагаемое X и запоминается в памяти сумматора. Затем подаётся второе слагаемое Y. Затем на выходе сумматора формируется S и сигнал переноса.

Слайд 41Арифметико-логическое устройство (АЛУ)

В АЛУ выполняются арифметические и логические операции над двоичными

Основные параметры:

Разрядность (32–64 разряда в современных компьютерах)

Быстродействие (время выполнения одной элементарной операции, напр. сложения).

Строится с помощью ЛЭ

Слайд 50Основы схемотехники ЭВМ.

ТСИС

(Технические средства информационных систем)

Программное обеспечение информационных систем (1-40

Ковалевский Вячеслав Викторович

Лекция 4

4096tb@gmail.com

Тема письма:

БГУИР. … .

https://www.dropbox.com/s/q8pkzresae3egb1/TCIC.Lec4.pps?dl=0

?