- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Вычислительные средства АСОИУ презентация

Содержание

- 1. Вычислительные средства АСОИУ

- 2. Основная учебная литература В.Л. Бройдо, О.П. Ильина.

- 3. Основная учебная литература К. Хамакер, Э. Вранешич,

- 4. Дополнительная учебная литература М. Гук, Аппаратные

- 5. Дополнительная учебная литература Столингс. Структурная организация

- 6. Неймановские принципы построения ЭВМ 1. Вся информация

- 7. Неймановские принципы построения ЭВМ 3. Слова размещаются

- 8. Неймановские принципы построения ЭВМ Управляющее слово называется машинной командой. Последовательность управляющих слов называется машинной программой.

- 9. Неймановские принципы построения ЭВМ 5. Выполнение вычислений

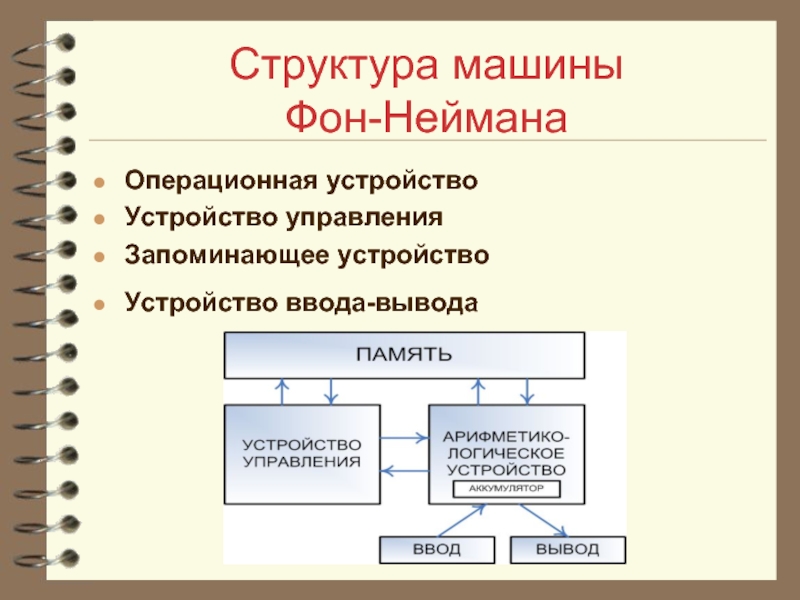

- 10. Структура машины Фон-Неймана Операционная устройство

- 11. Структурная организация современных ЭВМ ЭВМ- инженерная система

- 12. Структурная организация современных ЭВМ Совокупность связей двух

- 13. Типы интерфейсов Последовательный Параллельный Паралллельно-последовательный Типовой шинный интерфейс: ШУ-шина управления; ША-шина адреса; ШД-шина данных

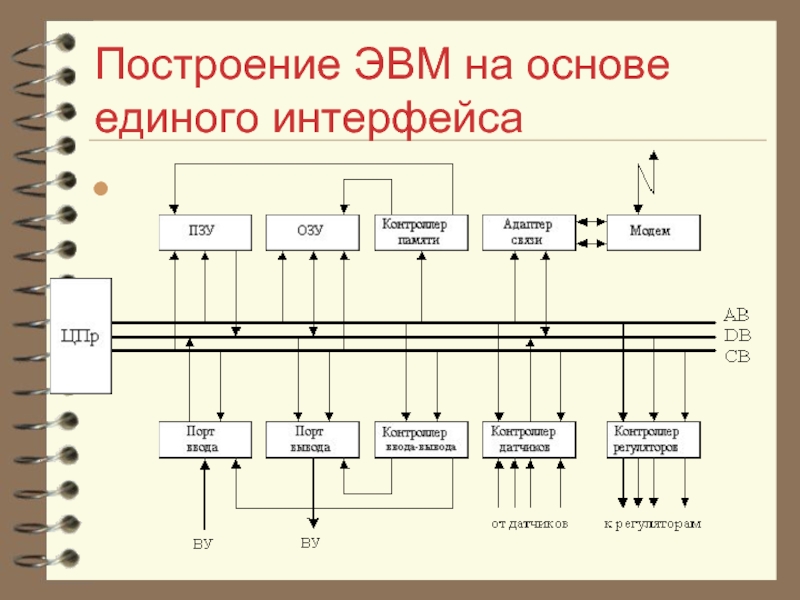

- 14. Построение ЭВМ на основе единого интерфейса

- 15. Основные характеристики ЭВМ 1. Операционные ресурсы: Способы

- 16. Основные характеристики ЭВМ 2. Ёмкость памяти и организация памяти.

- 17. Основные характеристики ЭВМ 3. Быстродействие. Основная характеристика быстродействия: V [оп/сек]; Длительность операции: Tоп=1/V [сек]

- 18. Основные характеристики ЭВМ 4. Производительность. Характеризует

- 19. Основные характеристики ЭВМ T задачи в мультипрограммном

- 20. Основные характеристики ЭВМ 5. Надёжность. Надёжность

- 21. Основные характеристики ЭВМ 6. Стоимость. На стоимость

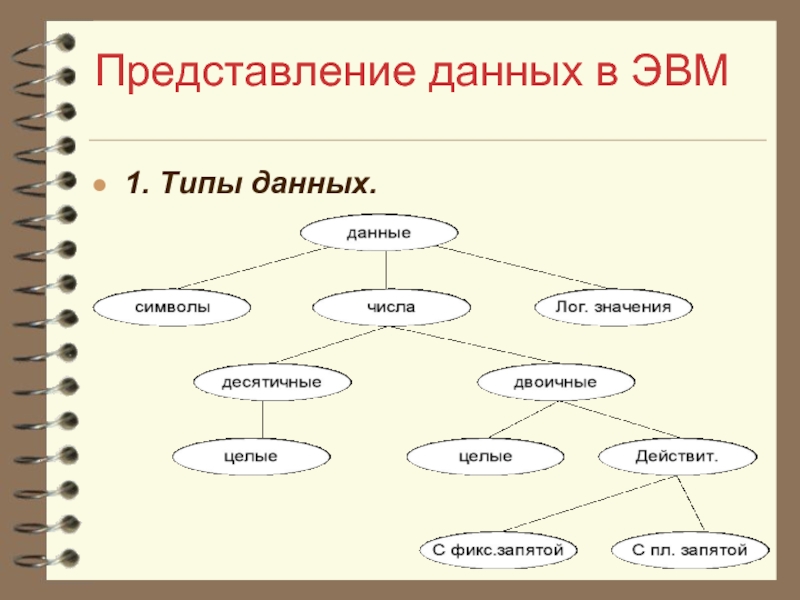

- 22. Представление данных в ЭВМ 1. Типы данных.

- 23. Представление данных в ЭВМ 2. Целые двоичные

- 24. Представление данных в ЭВМ 3. Двоичные числа с фиксированной запятой.

- 25. Представление данных в ЭВМ Особенности выполнения арифметических

- 26. Представление данных в ЭВМ В). Деление. А/В

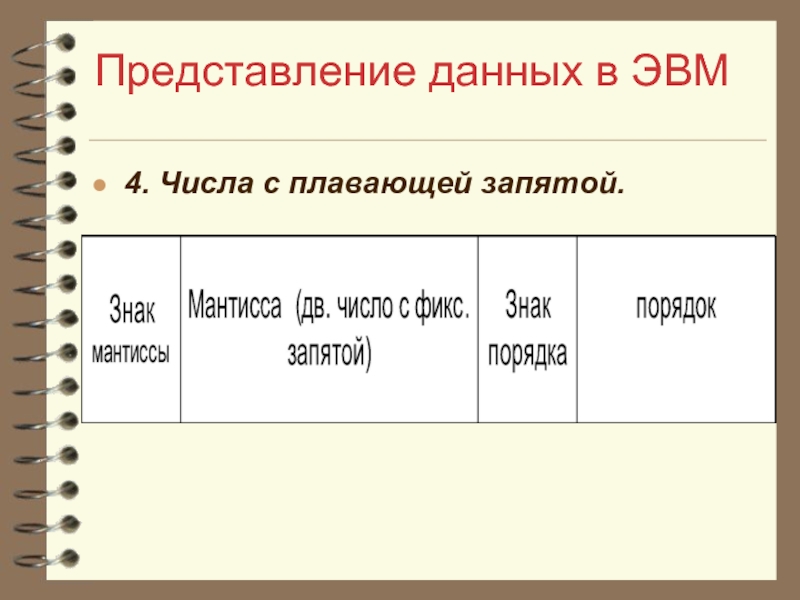

- 27. Представление данных в ЭВМ 4. Числа с плавающей запятой.

- 28. 4. Числа с плавающей запятой Структура числа:

- 29. 4. Числа с плавающей запятой Нормальная форма

- 30. 4. Числа с плавающей запятой Такая форма

- 31. 4. Числа с плавающей запятой Нормализованная форма,

- 32. 4. Числа с плавающей запятой Недостаток заключается

- 33. 4. Числа с плавающей запятой Так как

- 34. Cтандарт IEEE 754-1985 определяет: как представлять

- 36. Основные понятия в представлении чисел с плавающей

- 38. Представление данных в ЭВМ Z=плюс-минус М*d в

- 39. Представление данных в ЭВМ Из-за ограничений на

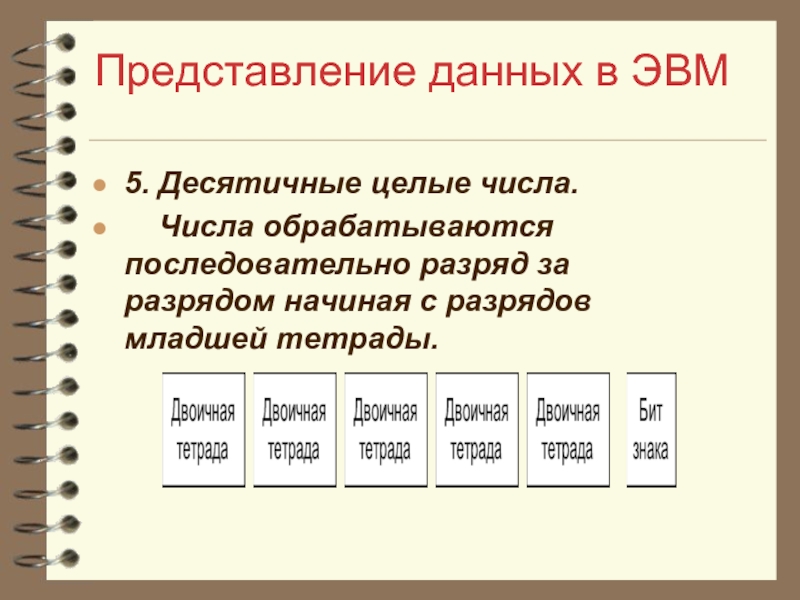

- 40. Представление данных в ЭВМ 5. Десятичные целые

- 41. Представление данных в ЭВМ 6. Строки символов.

- 42. Представление данных в ЭВМ 7. Логические значения.

- 43. Машинные операции 1. Свойства машинных операций:

- 44. Машинные операции Набор машинных операций характеризуется

- 45. Машинные операции 2. Классификация машинных операций. а)

- 46. Система команд ЭВМ По функциональному назначению в

- 47. Система команд ЭВМ Команды обработки данных (команды

- 48. Система команд ЭВМ Команды дополнительные (типа RESET, TEST,-).

- 49. Способы адресации Способ адресации – это

- 50. Способы адресации Способы формирования адресов ячеек памяти

- 51. Способы адресации Относительные способы формирования предполагают, что

- 52. Способы адресации Относительная адресация При относительной адресации

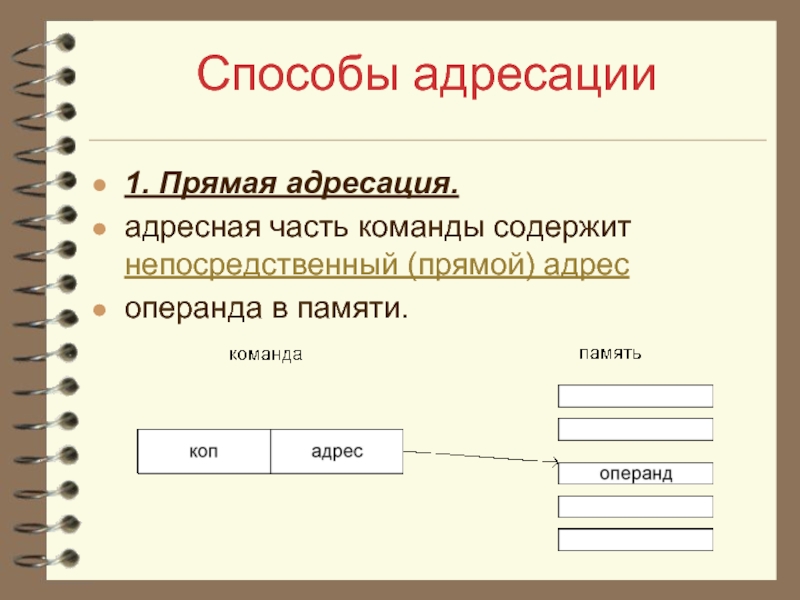

- 53. Способы адресации 1. Прямая адресация. адресная часть

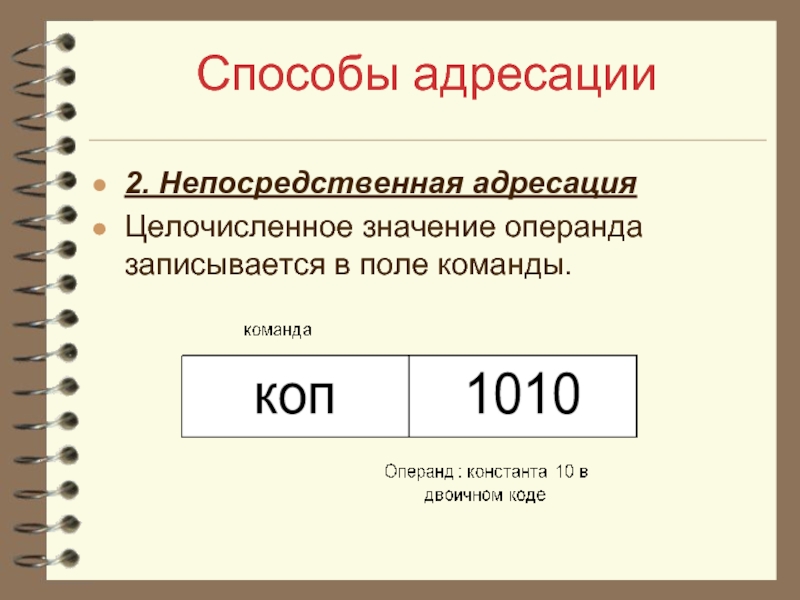

- 54. Способы адресации 2. Непосредственная адресация Целочисленное значение операнда записывается в поле команды.

- 55. Способы адресации 3. Косвенная адресация. Адресная часть

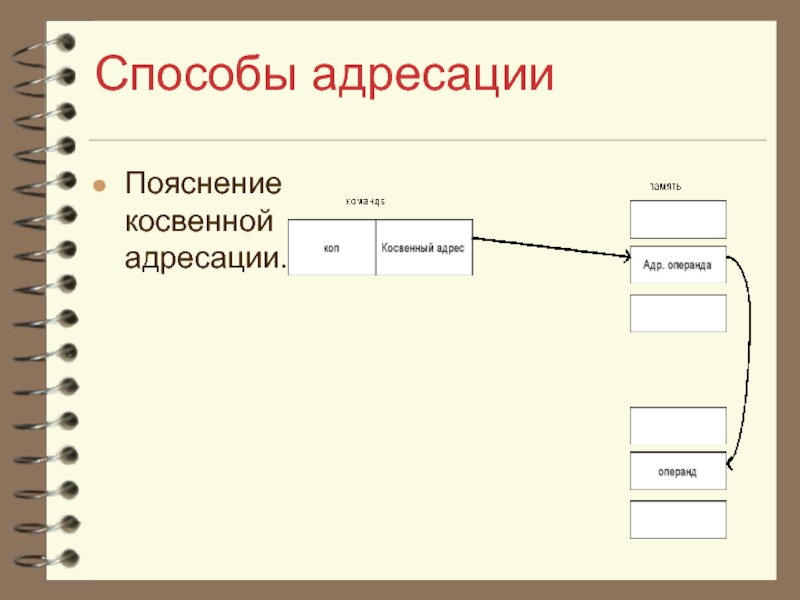

- 56. Способы адресации Пояснение косвенной адресации.

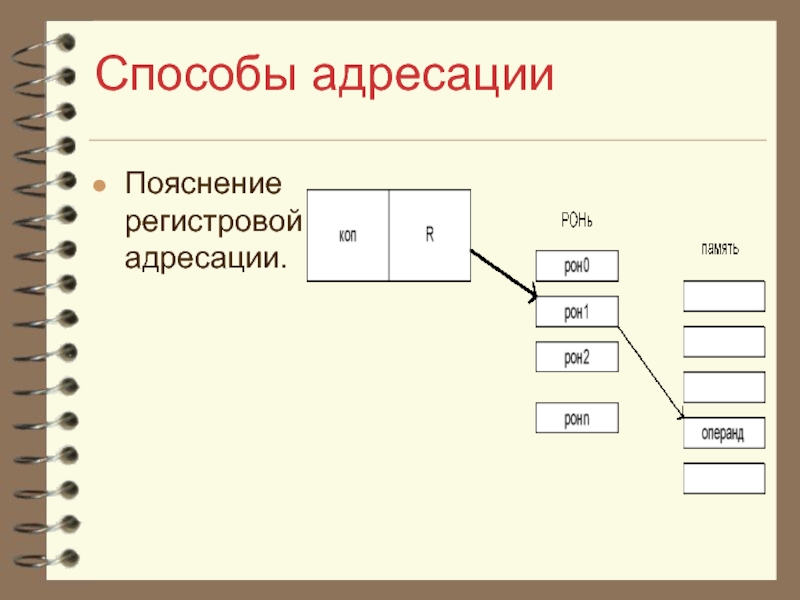

- 57. Способы адресации 4. Регистровая адресация. Применяется, когда

- 58. Способы адресации Пояснение регистровой адресации.

- 59. Способы адресации 5. Адресация с модификацией адресов.

- 60. Способы адресации Программирование циклов существенно упрощается, если

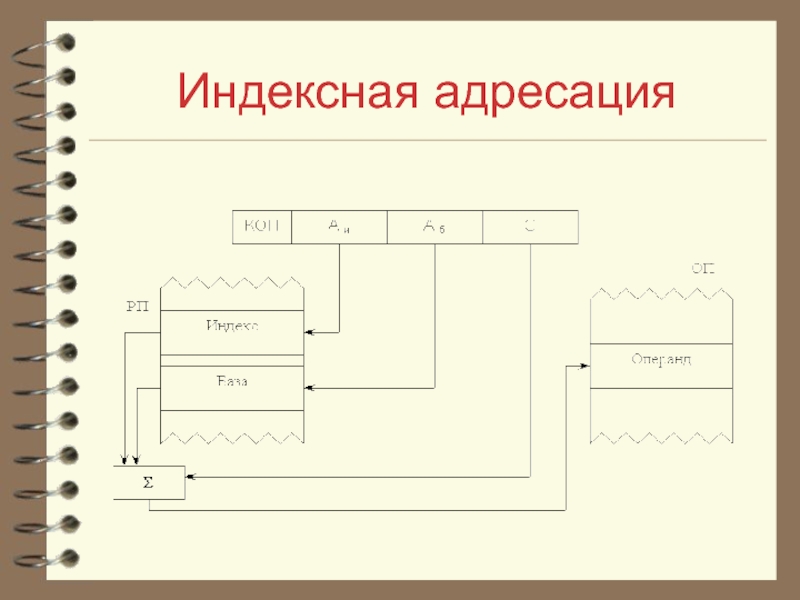

- 61. Способы адресации Индексная адресация Для работы программ

- 62. Индексная адресация

- 63. Индексная адресация Адрес i-того операнда в массиве

- 64. Способы адресации. 6. Прямая адресация с модификацией.

- 65. Способы адресации 7. Регистровая адресация с

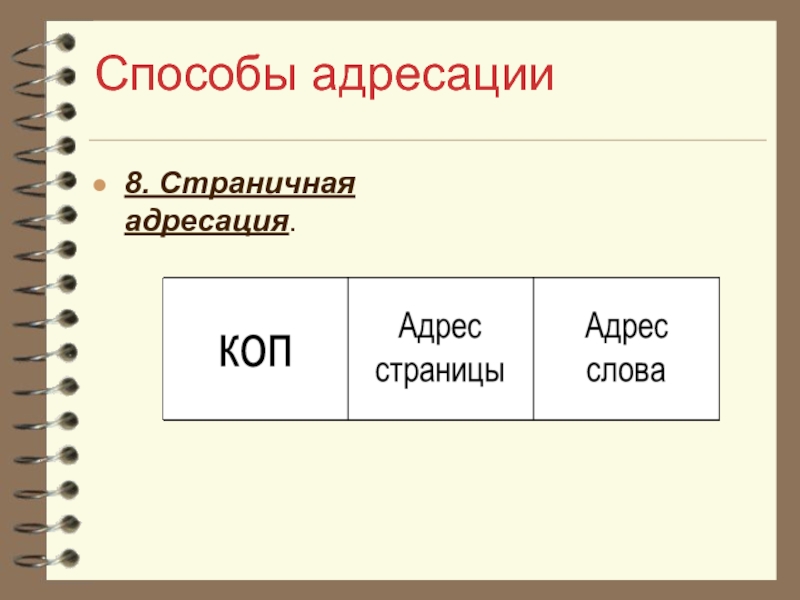

- 66. Способы адресации 8. Страничная адресация.

- 67. Способы адресации 9. Стековая адресация Стековая память

- 68. Способы адресации 9.Стековая адресация

- 69. 9.Стековая адресация Для чтения записи доступен

- 70. Исходные данные для проектирования ОУ F

- 71. Исходные данные для проектирования ОУ Задача проектирования-

- 72. Исходные данные для проектирования ОУ Формализованная микропрограмма

- 73. Исходные данные для проектирования ОУ Язык формализованного

- 74. ЯФМП ЯФМП состоит из описательной части (описание

- 75. ЯФМП 1. Описание слов:

- 76. ЯФМП Например, запись СчК(3:0) обозначает четырёхразрядный счётчик

- 77. ЯФМП 2. Описание массивов: М[m2:m1](n2:n1) где:

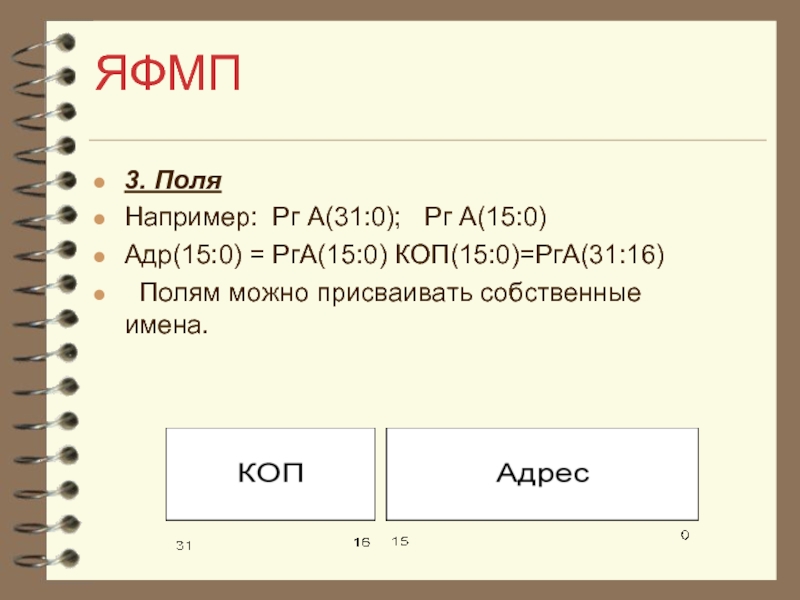

- 78. ЯФМП 3. Поля Например: Рг А(31:0);

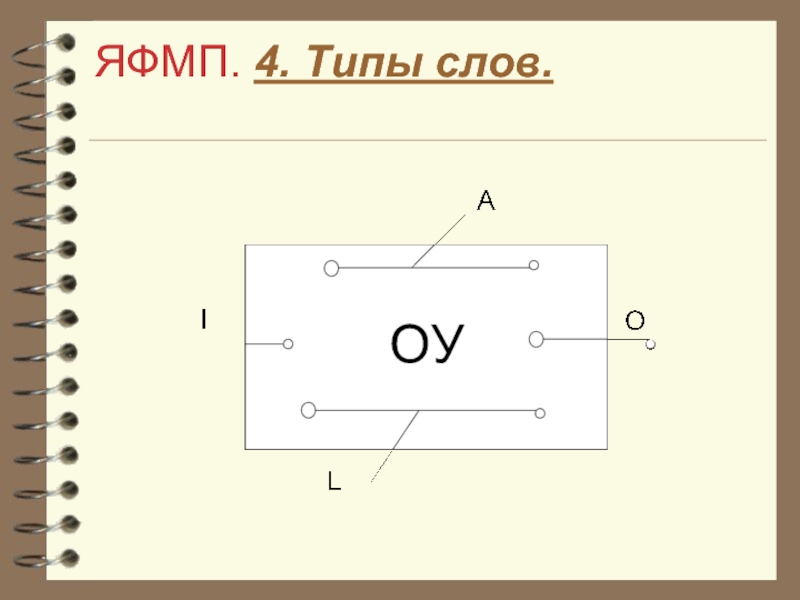

- 79. ЯФМП 4. Типы слов. Каждое

- 80. ЯФМП. 4. Типы слов.

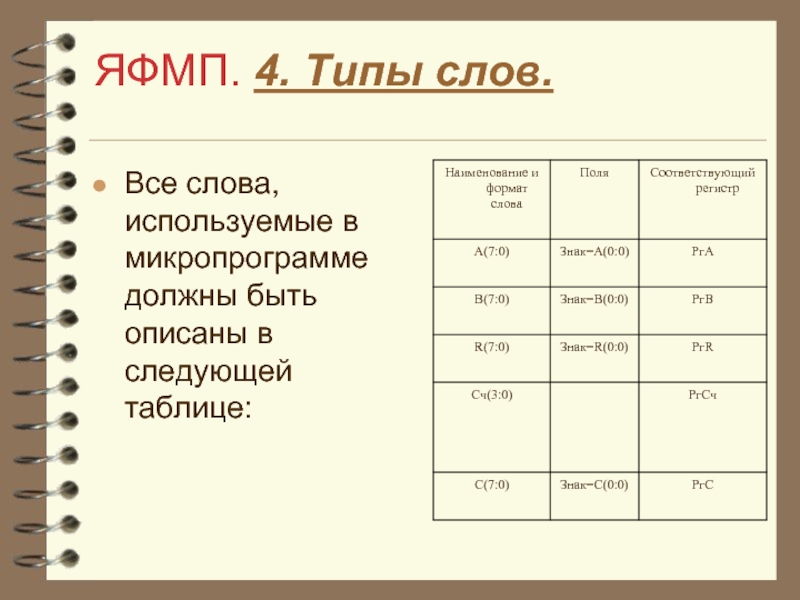

- 81. ЯФМП. 4. Типы слов. Все слова,

- 82. ЯФМП 5. Двоичные выражения. Описывают преобразования, выполняемые

- 83. 5. Двоичные выражения. В качестве ДВ

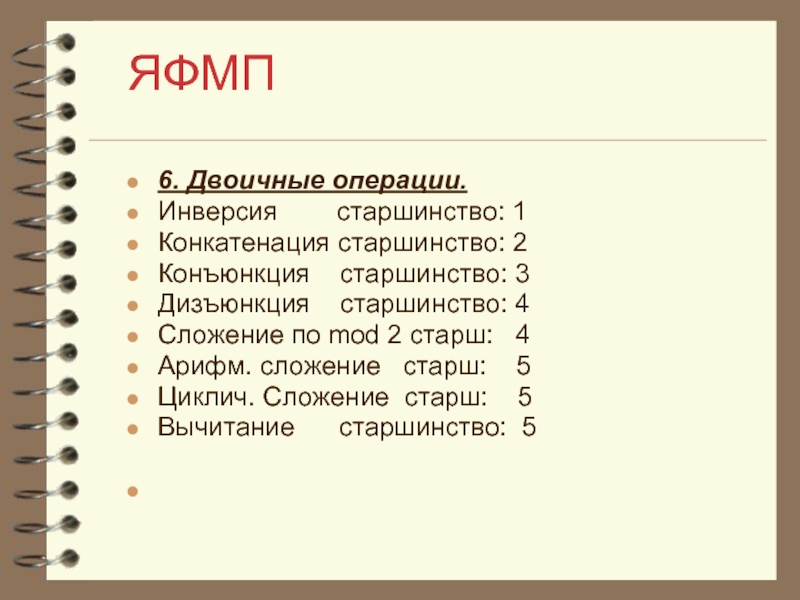

- 84. ЯФМП 6. Двоичные операции. Инверсия

- 85. Микрооперации Синтаксис записи микрооперации: := оператор присваивания.

- 86. Микрооперации Типовые микрооперации. Классификация. 1. Установка значения

- 87. Микрооперации Оператор присваивания в синтаксической записи: := Вся микрооперация выполняется за один машинный такт.

- 88. Микрооперации 4. Сдвиговые микрооперации. При сдвиге указывается

- 89. Микрооперации Синтаксис записи МО сдвига: RK

- 90. Микрооперации Типы сдвигов: - логический; - циклический; - арифметический.

- 91. Микрооперации Правила выполнения сдвигов: 1. При логическом

- 92. Микрооперации При арифметическом сдвиге выполняются следующие правила:

- 93. Микрооперации 5. Микрооперации счёта. Используются в

- 94. Микрооперации Совместимость микроопераций. Совместимыми называются микрооперации, которые

- 95. Микрооперации Функциональная совместимость определяется алгоритмом. Две МО

- 96. Микрооперации Структурная совместимость ограничивается аппаратурно. Две МО

- 97. Микрооперации Логические условия. Логические условия представляют из

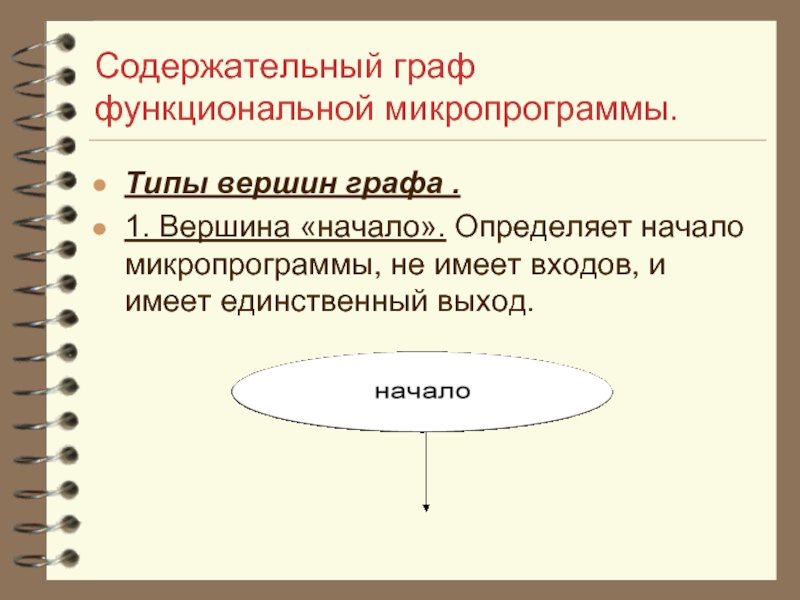

- 98. Содержательный граф функциональной микропрограммы. Для записи

- 99. Содержательный граф функциональной микропрограммы. Типы вершин графа

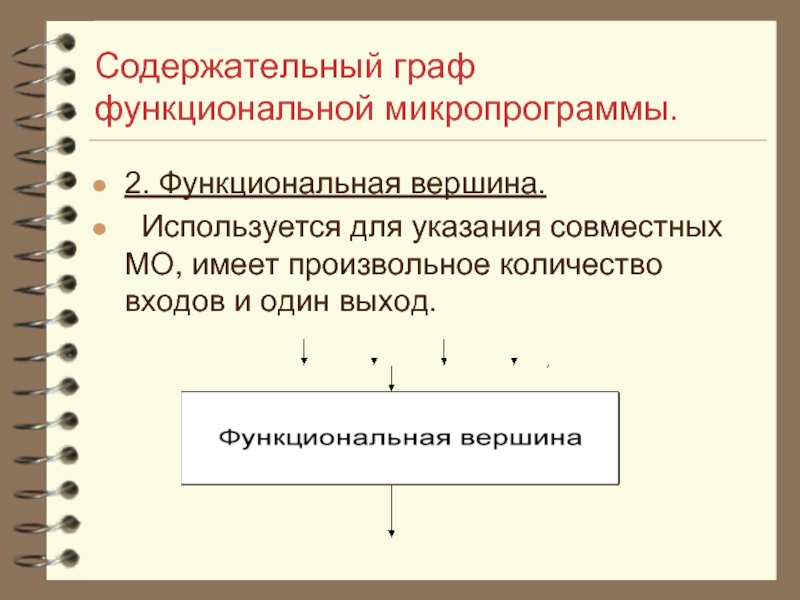

- 100. Содержательный граф функциональной микропрограммы. 2. Функциональная вершина.

- 101. Содержательный граф функциональной микропрограммы. 3. Условная вершина.

- 102. Содержательный граф функциональной микропрограммы. 4. Конечная вершина.

- 103. Содержательный граф функциональной микропрограммы. Граф должен быть

- 104. Содержательный граф функциональной микропрограммы. 2. В каждую

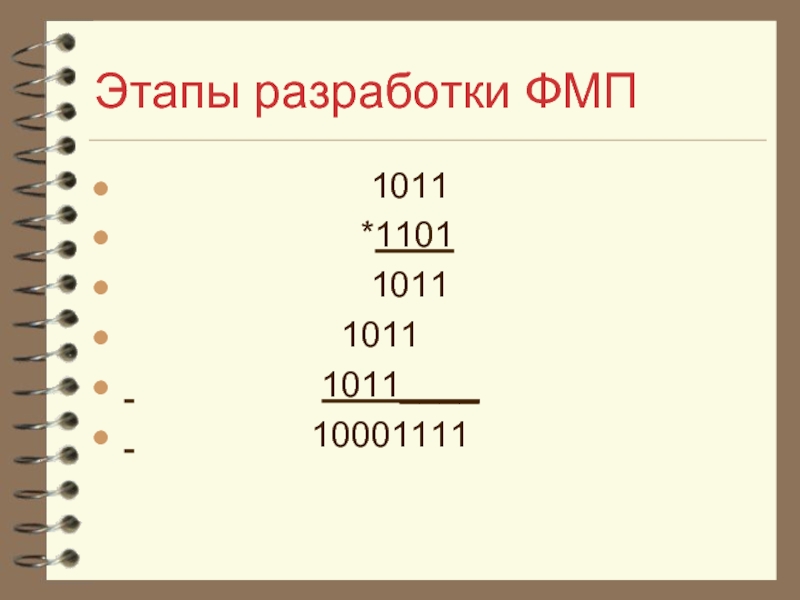

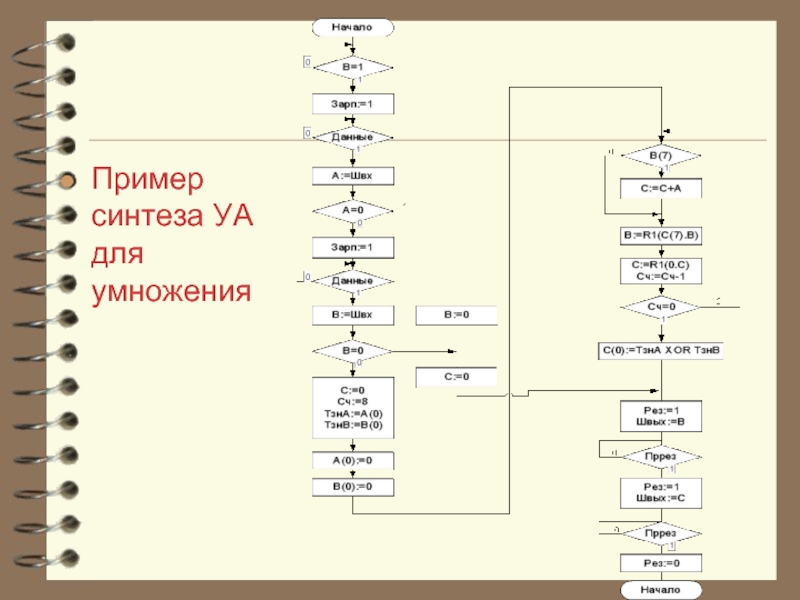

- 105. Этапы разработки ФМП Рассмотрим данные этапы на

- 106. Этапы разработки ФМП 3. Произведение занимает двойную

- 107. Этапы разработки ФМП

- 108. Этапы разработки ФМП Словесное описание алгоритма умножения.

- 109. Этапы разработки ФМП 2. Множимое располагается в

- 110. Этапы разработки ФМП 4. Производится сдвиг вправо

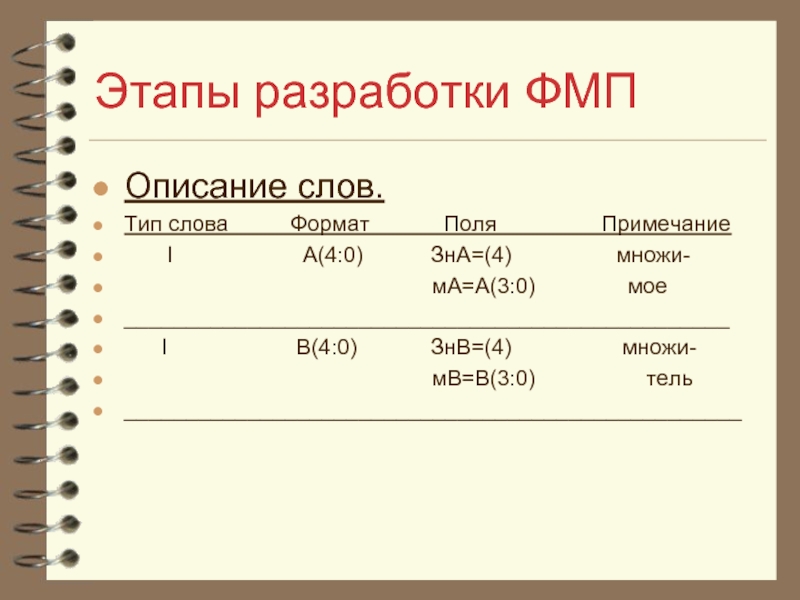

- 111. Этапы разработки ФМП Описание слов. Тип слова

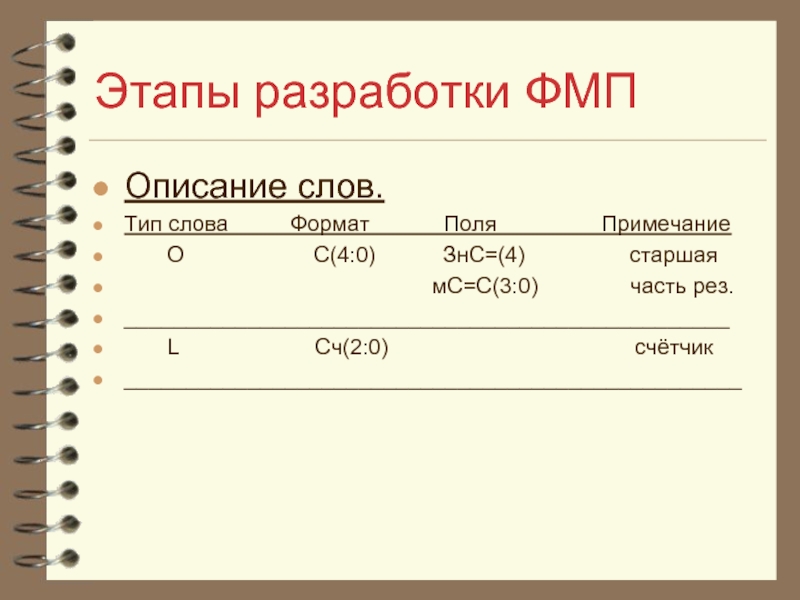

- 112. Этапы разработки ФМП Описание слов. Тип слова

- 113. Логическое проектирование операционного автомата (ОА)

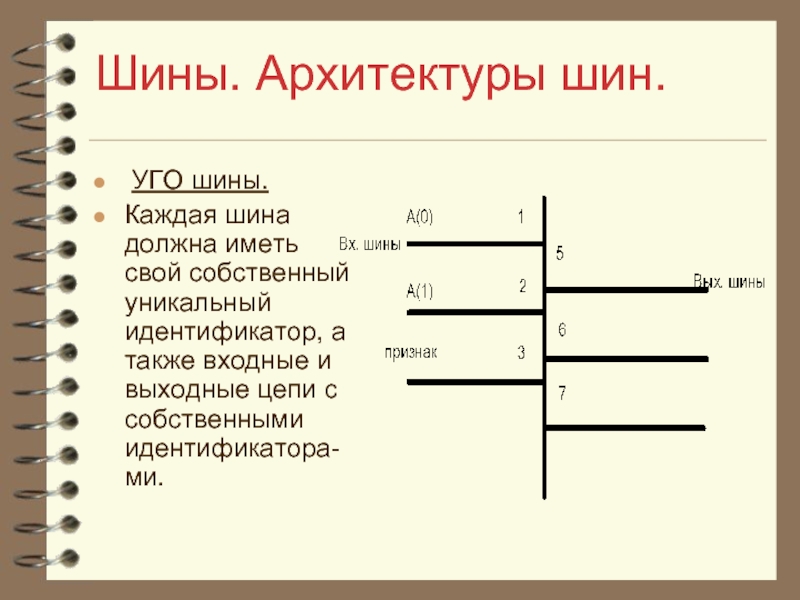

- 114. Шины. Архитектуры шин. УГО шины. Каждая

- 115. Шины. Архитектуры шин. Шины могут изгибаться, разветвляться,

- 116. Шины. Архитектуры шин. По шинам можно передавать

- 117. Порядок проектирования ОА 1. Описание ОА.

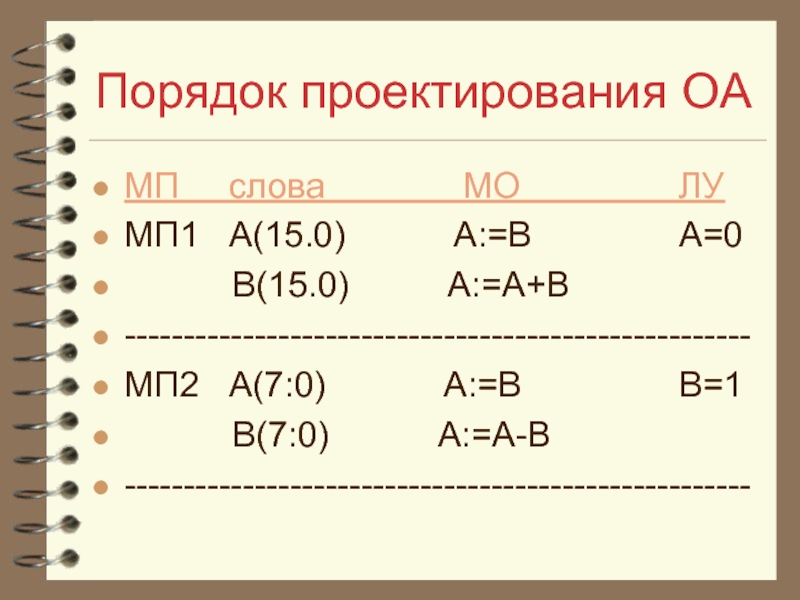

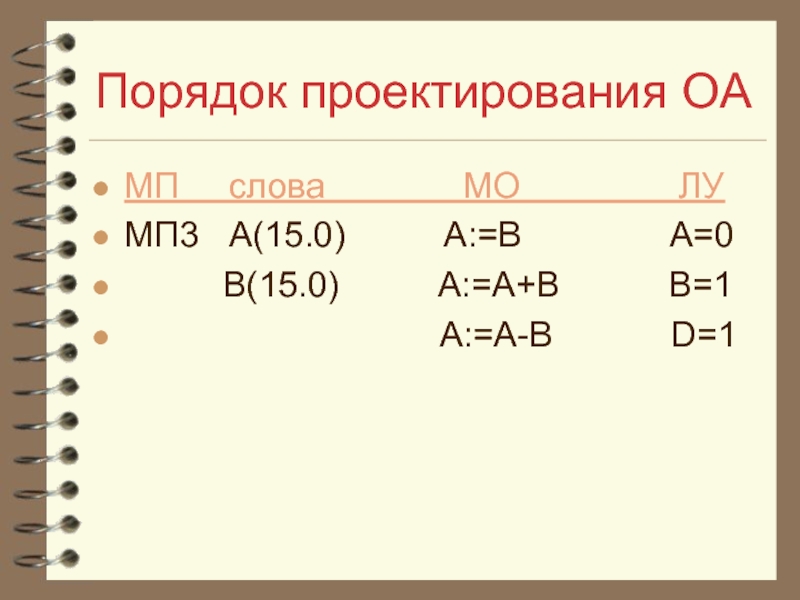

- 118. Порядок проектирования ОА МП слова

- 119. Порядок проектирования ОА МП слова

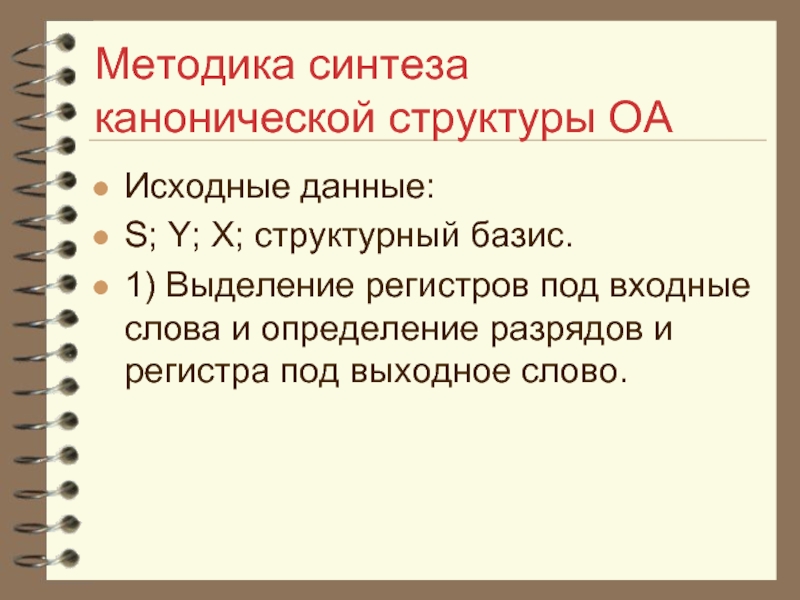

- 120. Методика синтеза канонической структуры ОА Исходные данные:

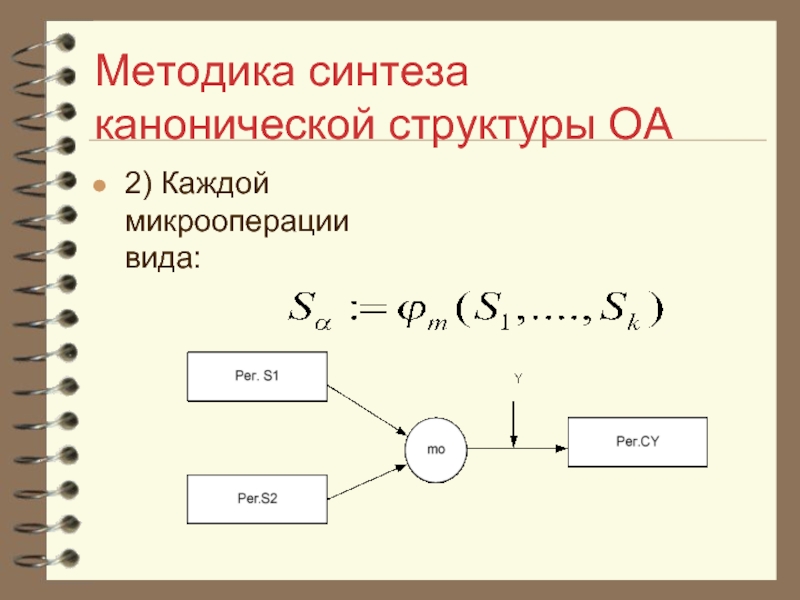

- 121. Методика синтеза канонической структуры ОА 2) Каждой микрооперации вида:

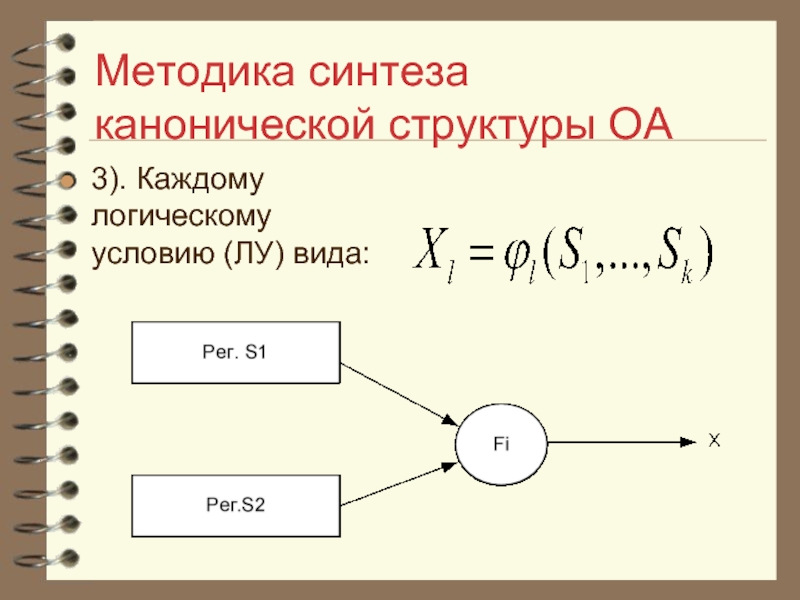

- 122. Методика синтеза канонической структуры ОА 3). Каждому логическому условию (ЛУ) вида:

- 123. Синтез ОА для блока умножения Составление алгоритма умножения

- 124. Синтез ОА для блока умножения Описание блока

- 125. Синтез канонической структуры блока умножения Рисунок структуры блока

- 126. Порядок работы ОА В ОА в каждом

- 127. Порядок работы ОА ОА работает по

- 128. Порядок работы ОА Длительность машинного такта: Tмт>ty+tmo+tлу

- 129. Характеристики ОА 1. Производительность (количество МО за такт). 2. Быстродействие (длительность такта). 3. Затраты оборудования.

- 130. Структурная организация ОА. Классификация структур автоматов: 1.I

- 131. Структурная организация ОА. 2. М –автоматы: в

- 132. Структурная организация ОА. 4. S - автоматы:

- 133. Структурная организация ОА.

- 134. Построение ОЭ на основе регистра Возможные операции

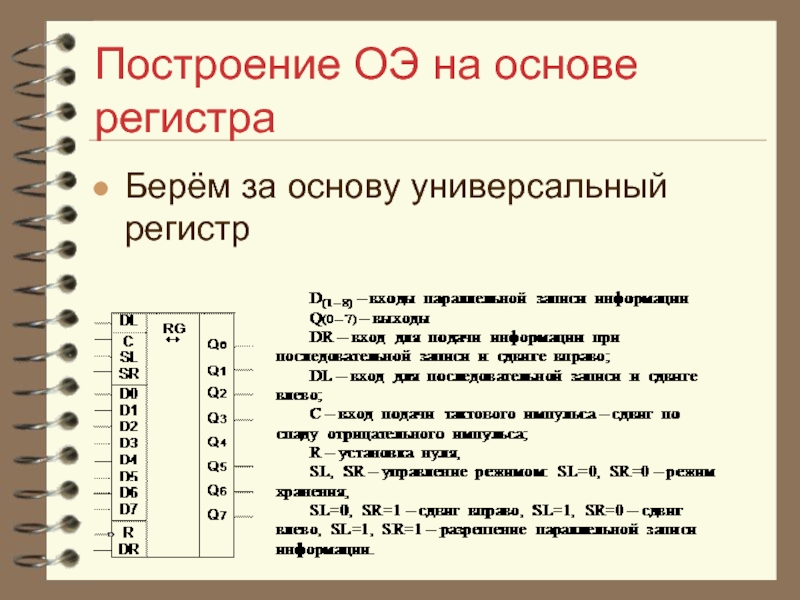

- 135. Построение ОЭ на основе регистра Берём за основу универсальный регистр

- 136. Таблица функций регистра

- 137. Таблица описания работы ОЭ

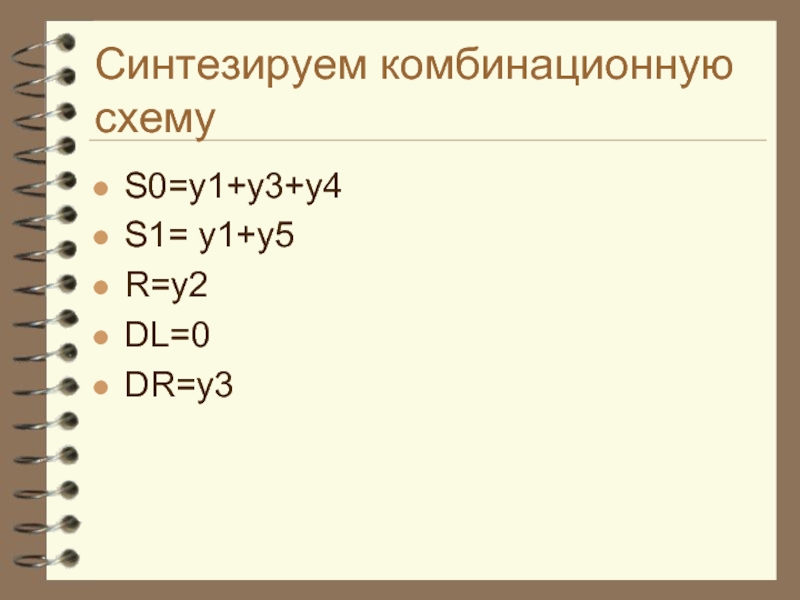

- 138. Синтезируем комбинационную схему S0=y1+y3+y4 S1= y1+y5 R=y2 DL=0 DR=y3

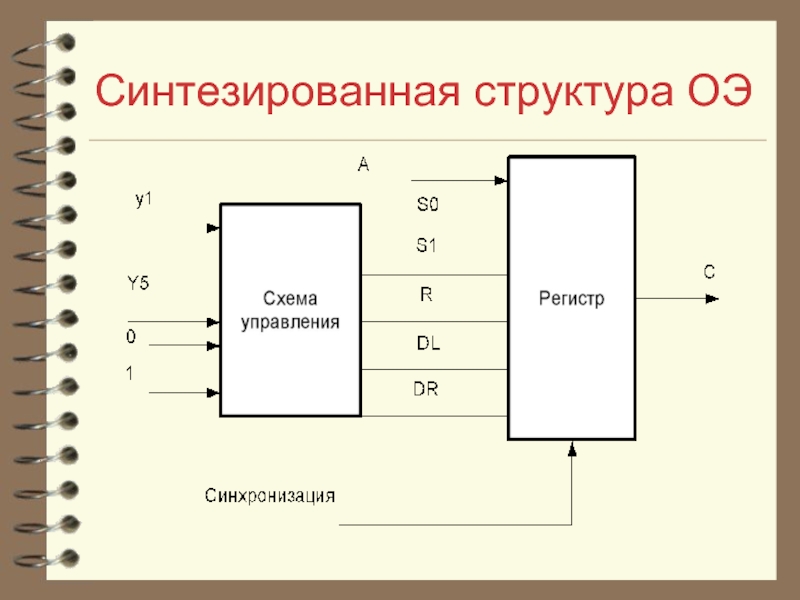

- 139. Синтезированная структура ОЭ

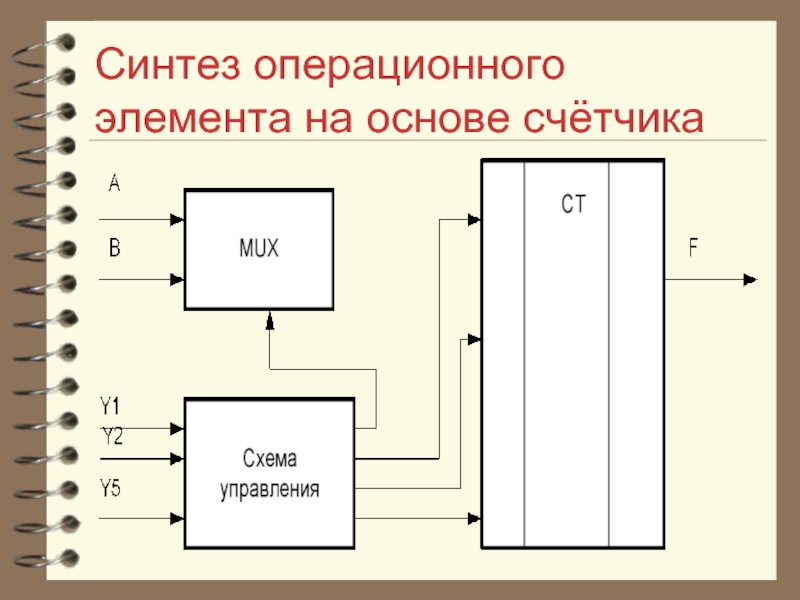

- 140. Синтез операционного элемента на основе счётчика Режимы счётчика

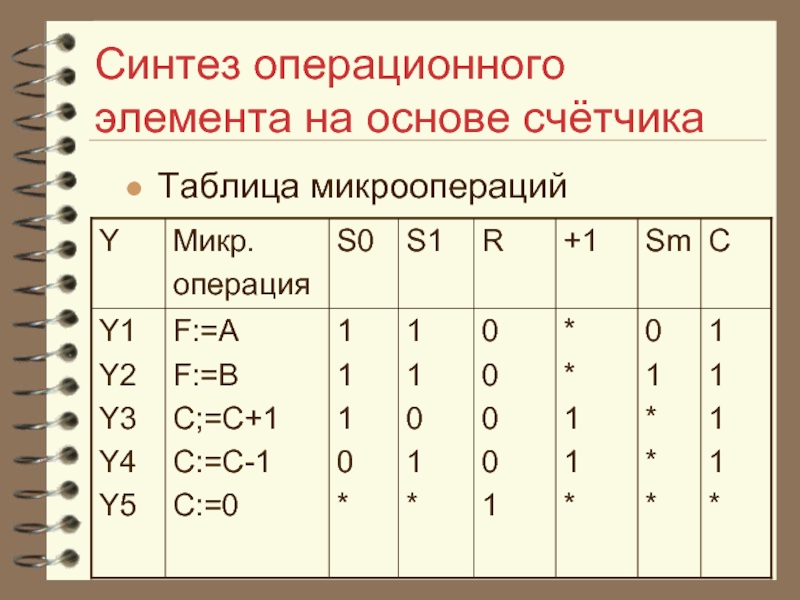

- 141. Синтез операционного элемента на основе счётчика Таблица микроопераций

- 142. Синтез операционного элемента на основе счётчика

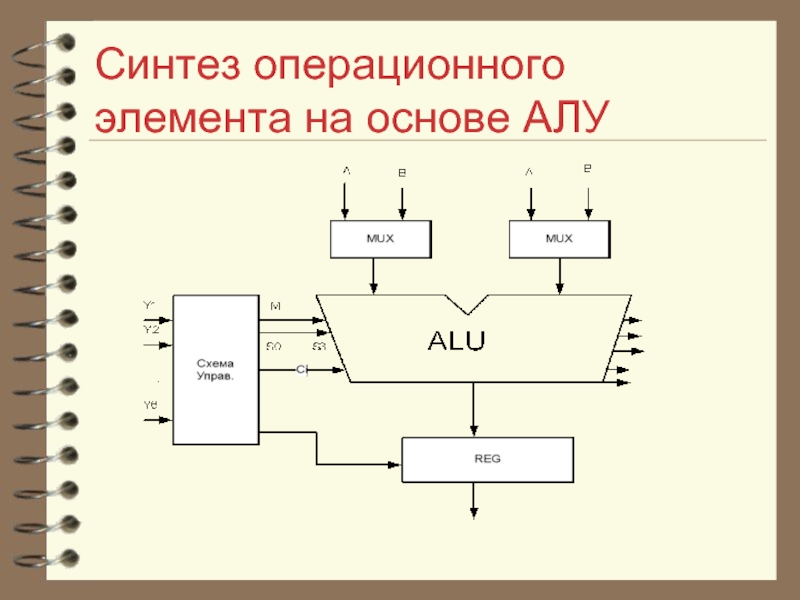

- 143. Синтез операционного элемента на основе АЛУ Интерфейс микросхемы АЛУ

- 144. Операции АЛУ Перечень выполняемых

- 145. Операции АЛУ

- 146. Соединение нескольких АЛУ

- 147. Соединение нескольких АЛУ

- 148. Синтез операционного элемента на основе АЛУ Перечень микроопераций: F=A+B F=A-B F=A+1 F=A-1 F=A&B F=A/\B

- 149. Синтез операционного элемента на основе АЛУ Таблица микроопераций для синтеза ОЭ

- 150. Синтез операционного элемента на основе АЛУ

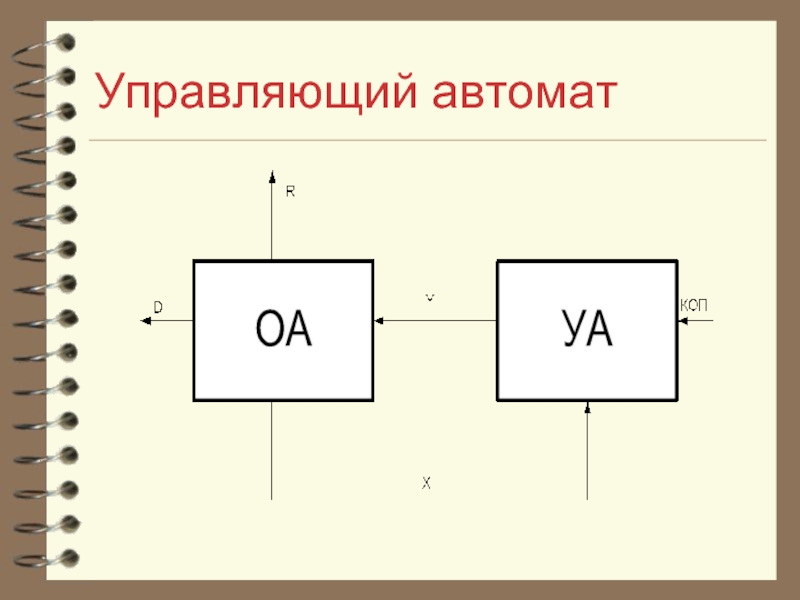

- 151. Управляющий автомат

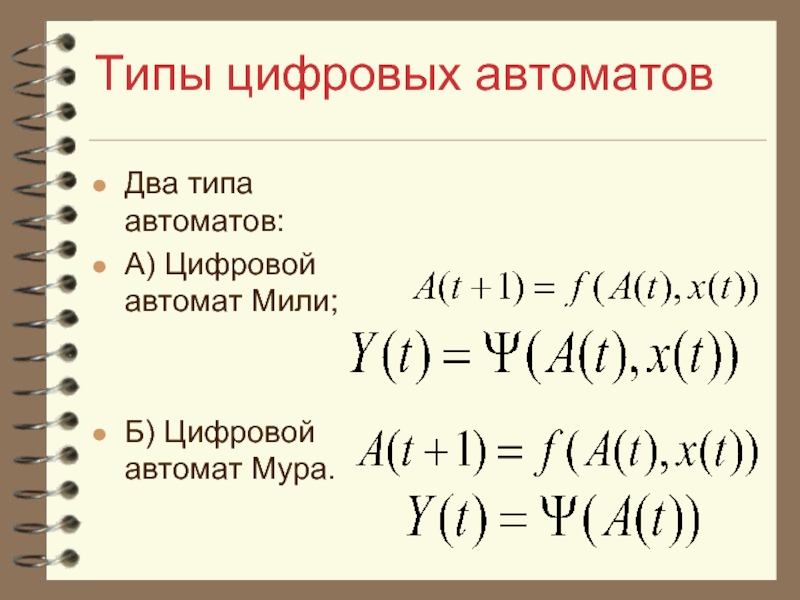

- 152. Типы цифровых автоматов Два типа автоматов: А)

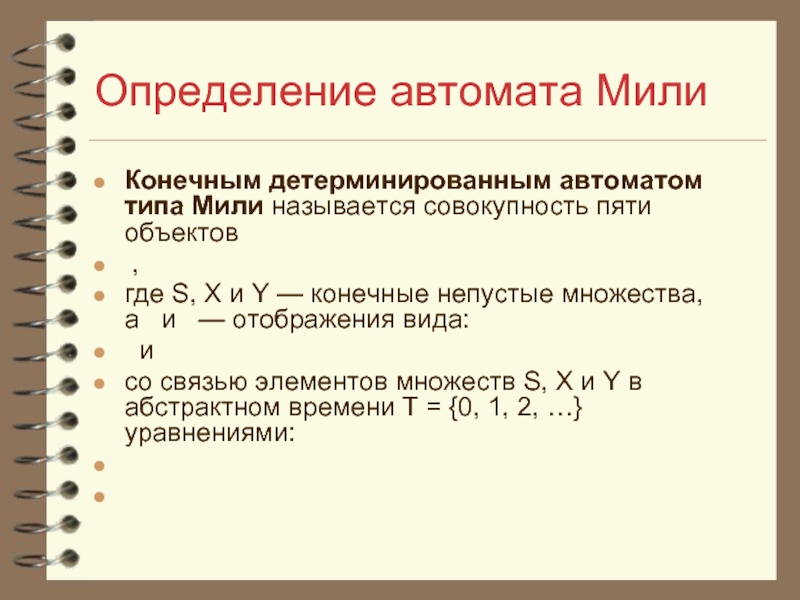

- 153. Определение автомата Мили Конечным детерминированным автоматом типа

- 154. Определение автомата Мили (Отображения и получили названия,

- 155. Цифровой автомат Мура Зависимость выходного сигнала только от

- 156. Цифровой автомат Мура Конечным детерминированным автоматом типа

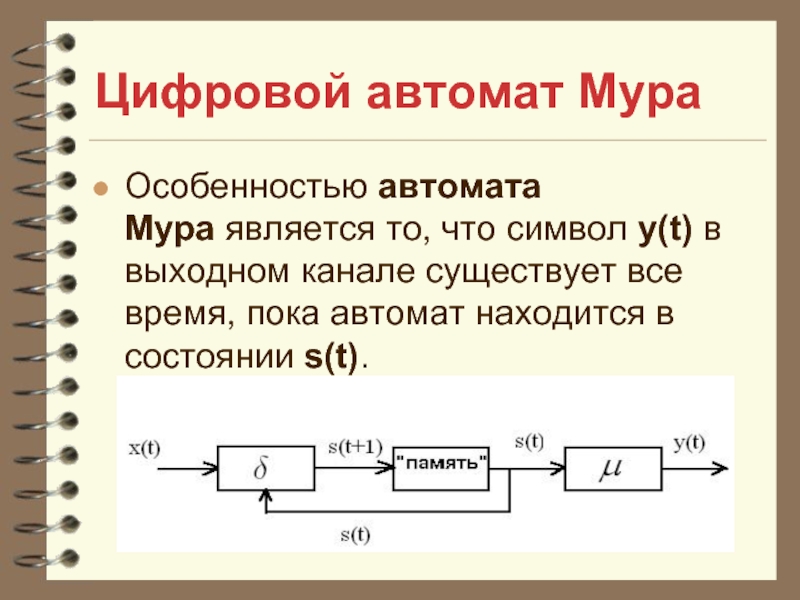

- 157. Цифровой автомат Мура Особенностью автомата Мура является то, что

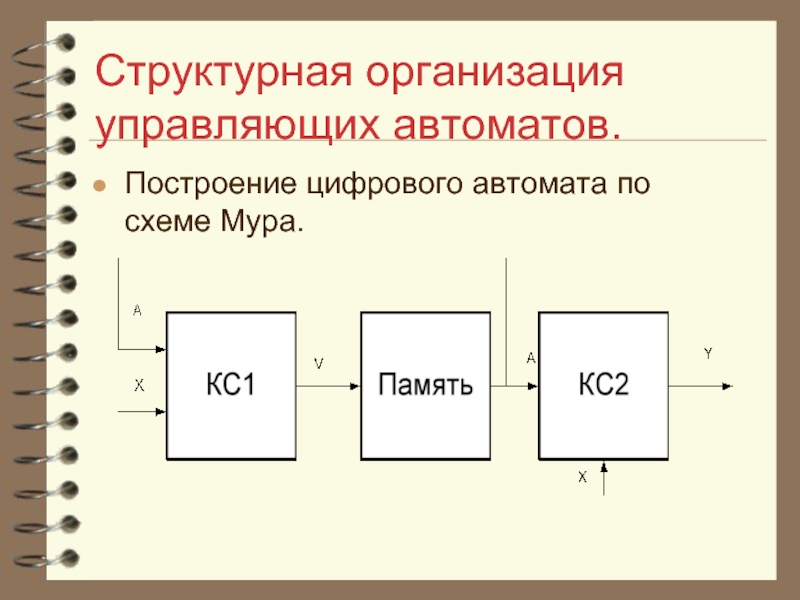

- 158. Структурная организация управляющих автоматов. Построение цифрового автомата по схеме Мура.

- 159. Построение цифрового автомата по схеме Мура.

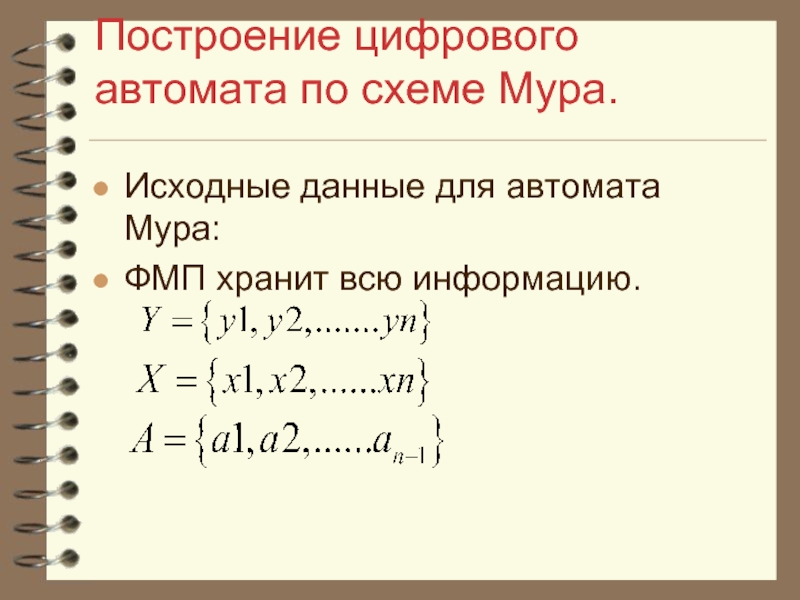

- 160. Построение цифрового автомата по схеме Мура.

- 161. Построение цифрового автомата по схеме Мура Формализуем

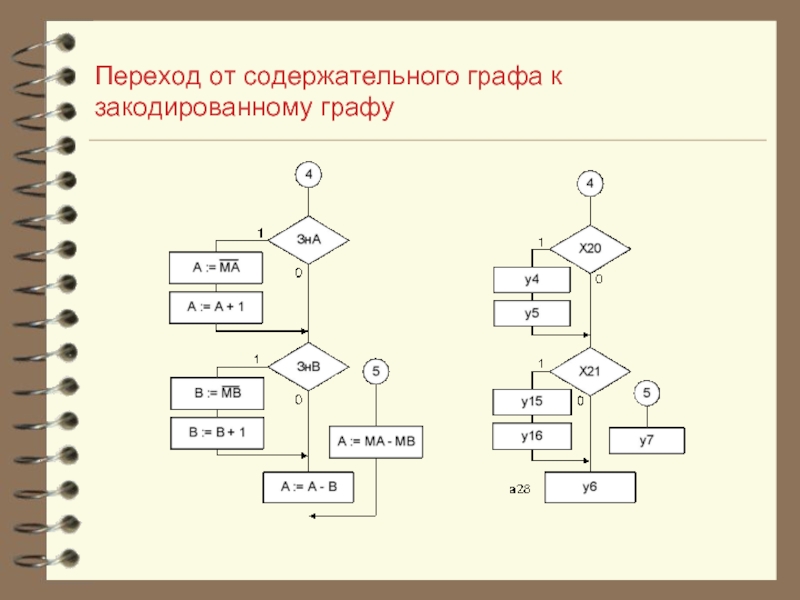

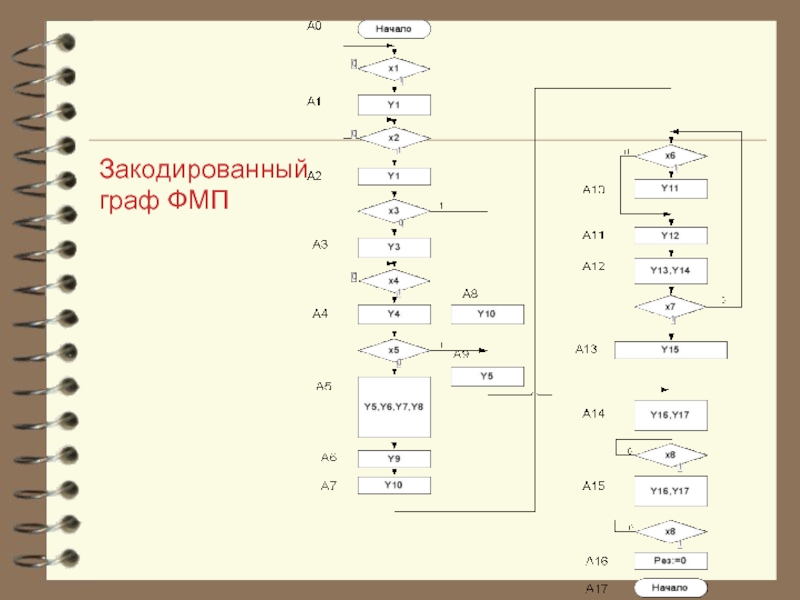

- 162. Переход от содержательного графа к закодированному графу

- 163. Этапы синтеза УА 1. Построение таблицы микроопераций

- 164. Этапы синтеза УА 4. Построение графа автомата

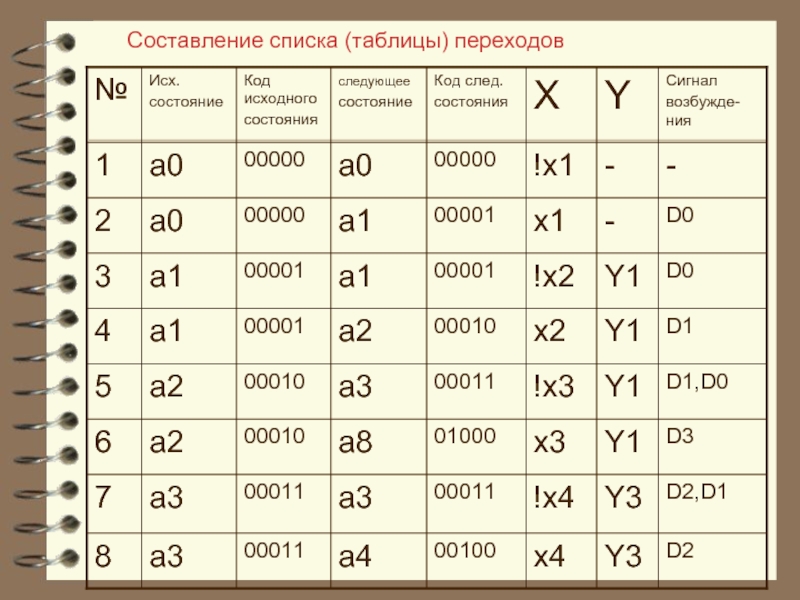

- 165. Этапы синтеза УА 5. Построение списка переходов

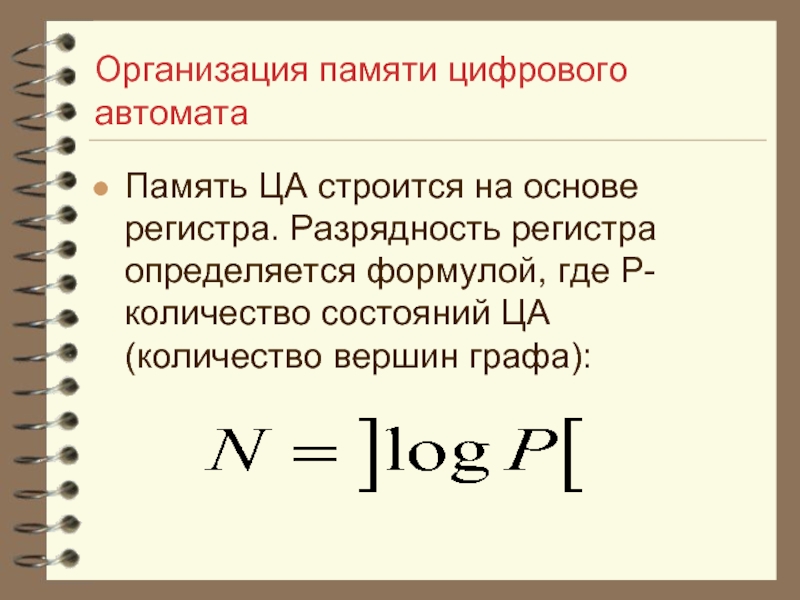

- 166. Организация памяти цифрового автомата Память ЦА строится

- 167. Пример синтеза УА для умножения

- 168. Закодированный граф ФМП

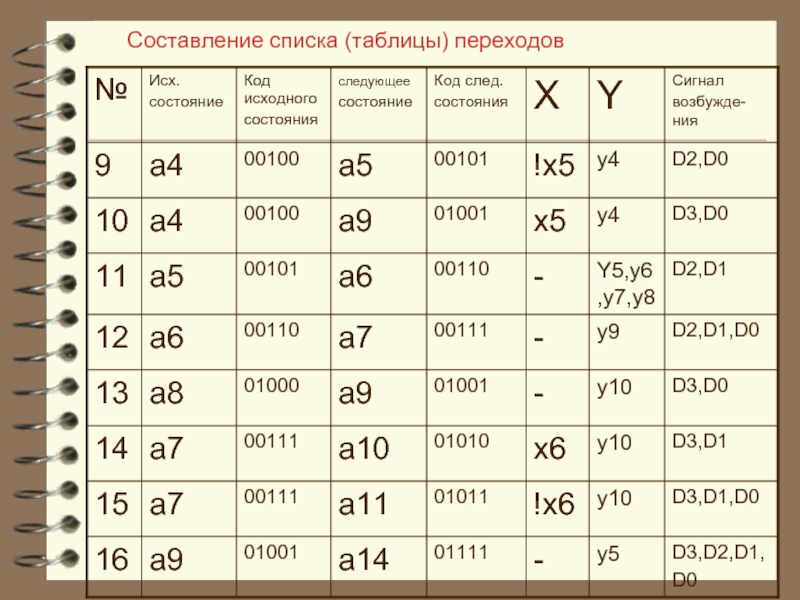

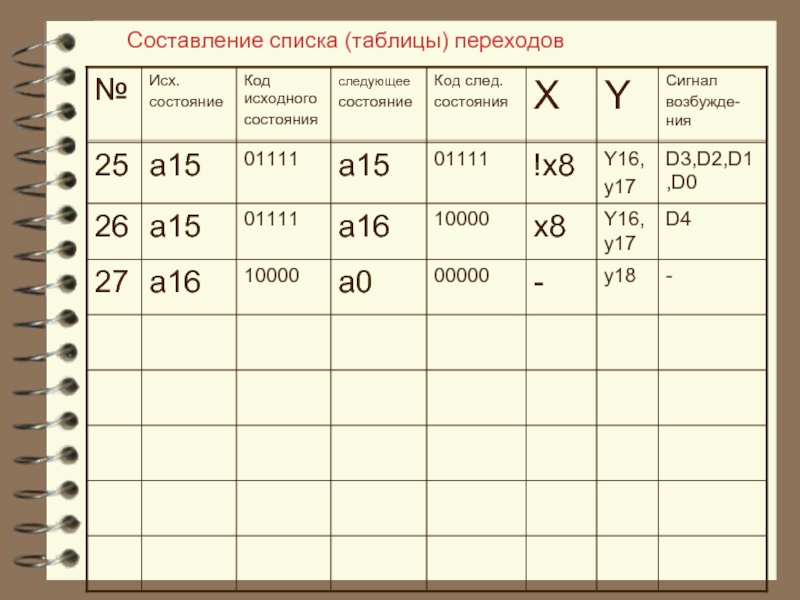

- 169. Составление списка (таблицы) переходов

- 170. Составление списка (таблицы) переходов

- 171. Составление списка (таблицы) переходов

- 172. Составление списка (таблицы) переходов

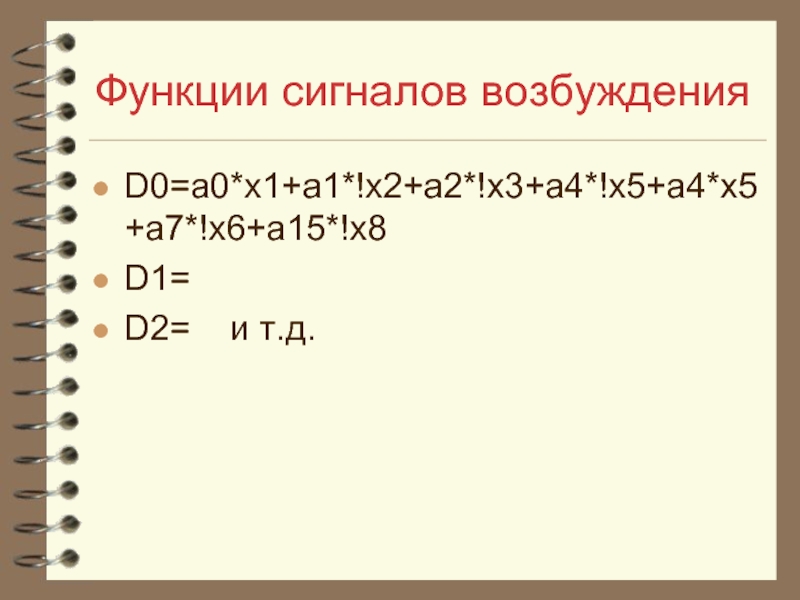

- 173. Функции сигналов возбуждения D0=a0*x1+a1*!x2+a2*!x3+a4*!x5+a4*x5+a7*!x6+a15*!x8 D1= D2= и т.д.

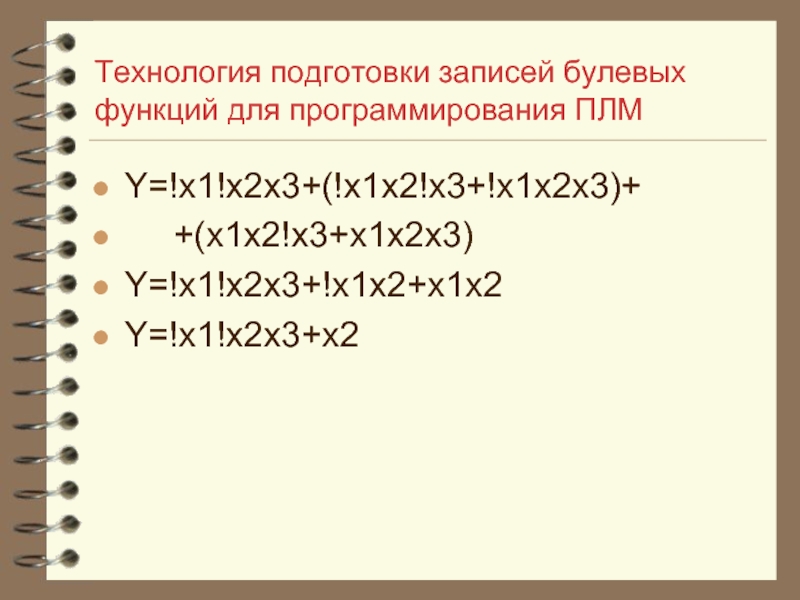

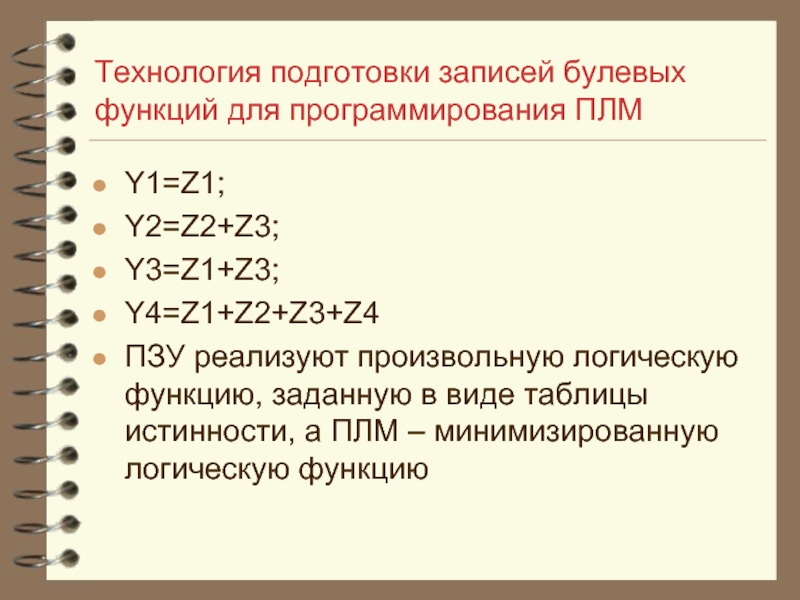

- 174. Технология подготовки записей булевых функций для программирования ПЛМ

- 175. Технология подготовки записей булевых функций для программирования ПЛМ Y=!x1!x2x3+(!x1x2!x3+!x1x2x3)+ +(x1x2!x3+x1x2x3) Y=!x1!x2x3+!x1x2+x1x2 Y=!x1!x2x3+x2

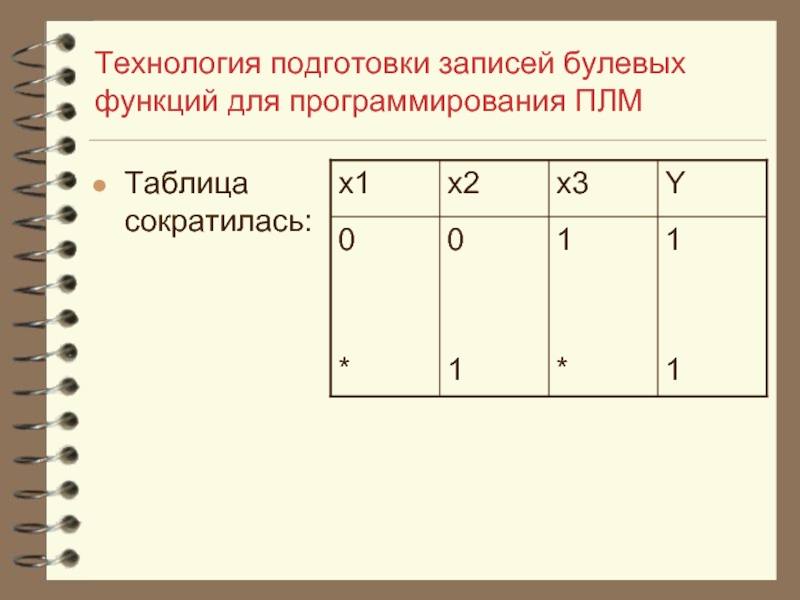

- 176. Технология подготовки записей булевых функций для программирования ПЛМ Таблица сократилась:

- 177. Технология подготовки записей булевых функций для программирования

- 178. Технология подготовки записей булевых функций для программирования

- 179. Технология подготовки записей булевых функций для программирования ПЛМ

- 180. Технология подготовки записей булевых функций для программирования ПЛМ

- 181. Технология подготовки записей булевых функций для программирования

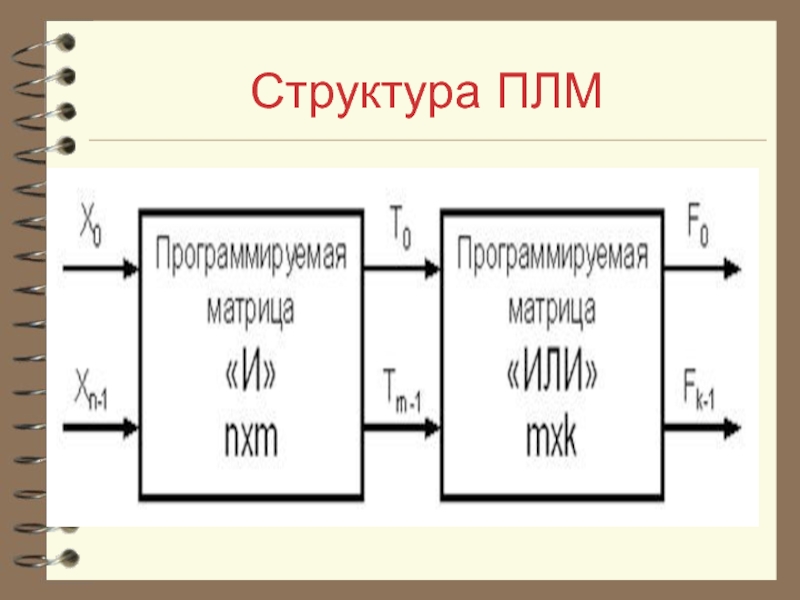

- 182. Структура ПЛМ

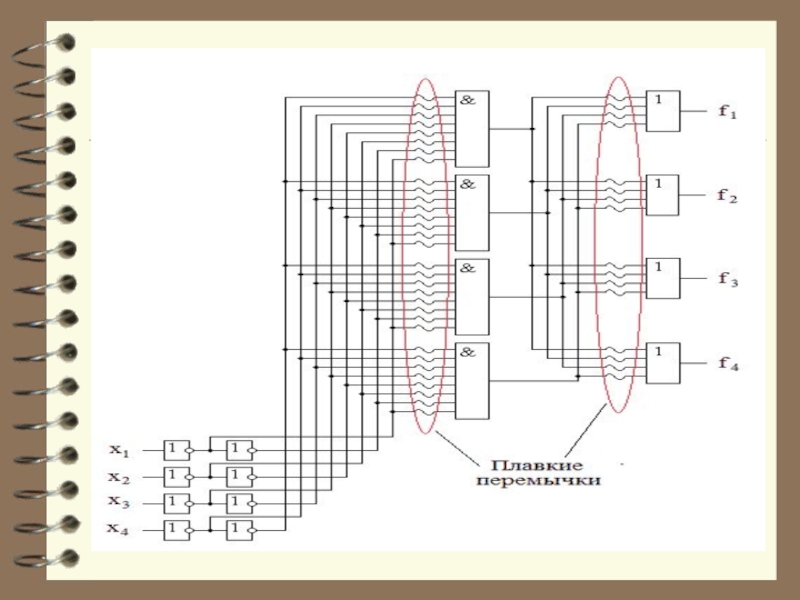

- 184. Электрическая схема ПЛМ

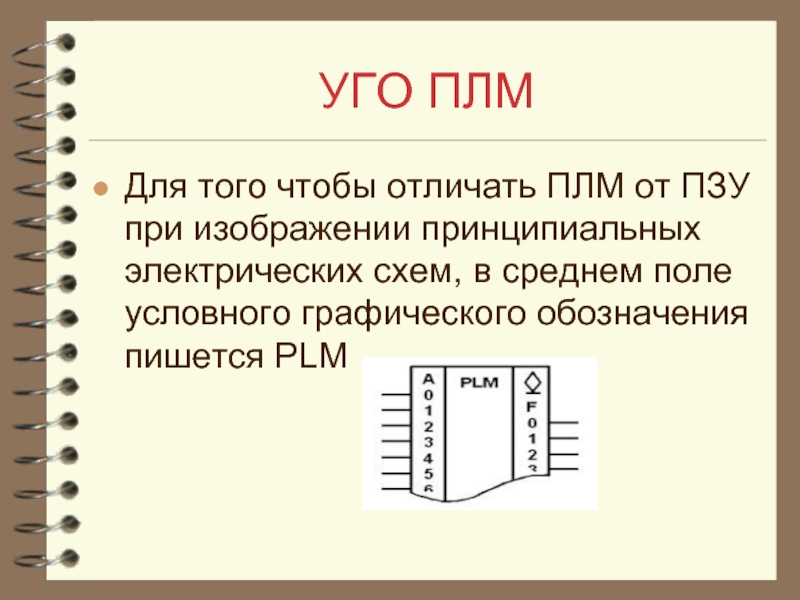

- 185. УГО ПЛМ Для того чтобы отличать ПЛМ

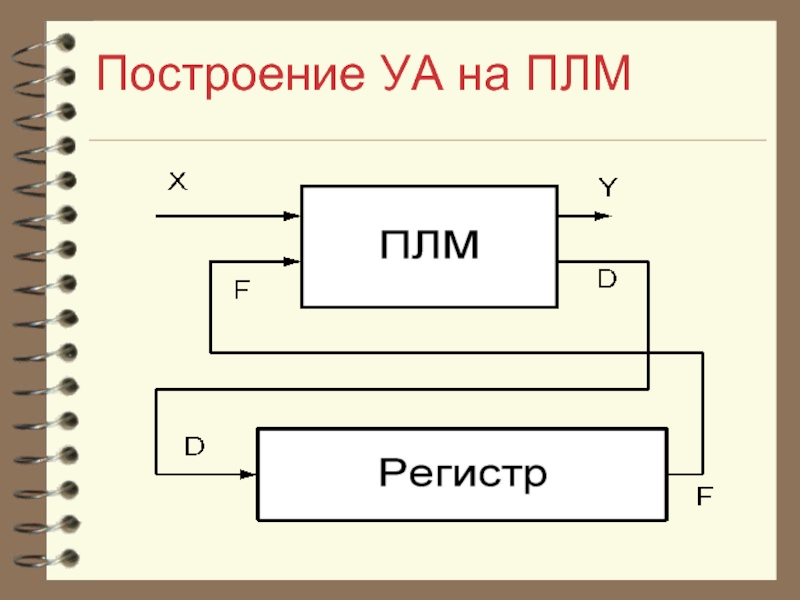

- 186. Построение УА на ПЛМ

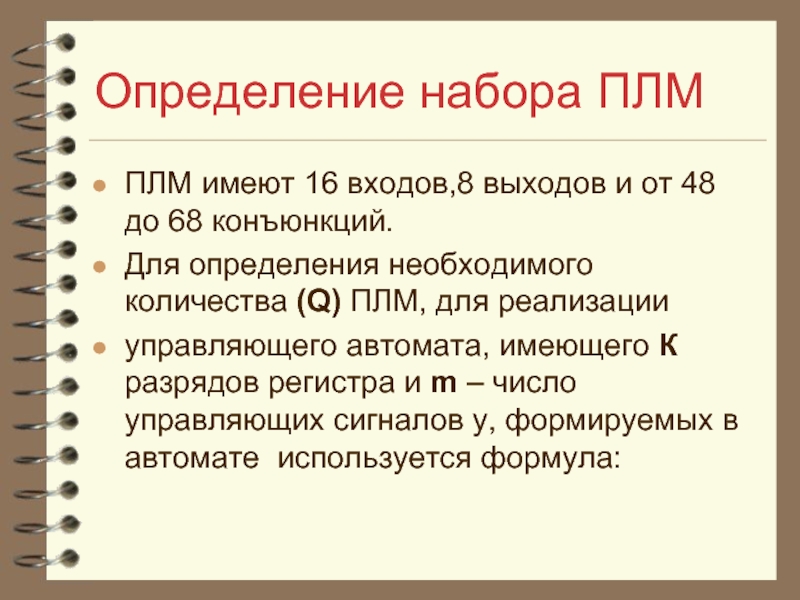

- 187. Определение набора ПЛМ ПЛМ имеют 16 входов,8

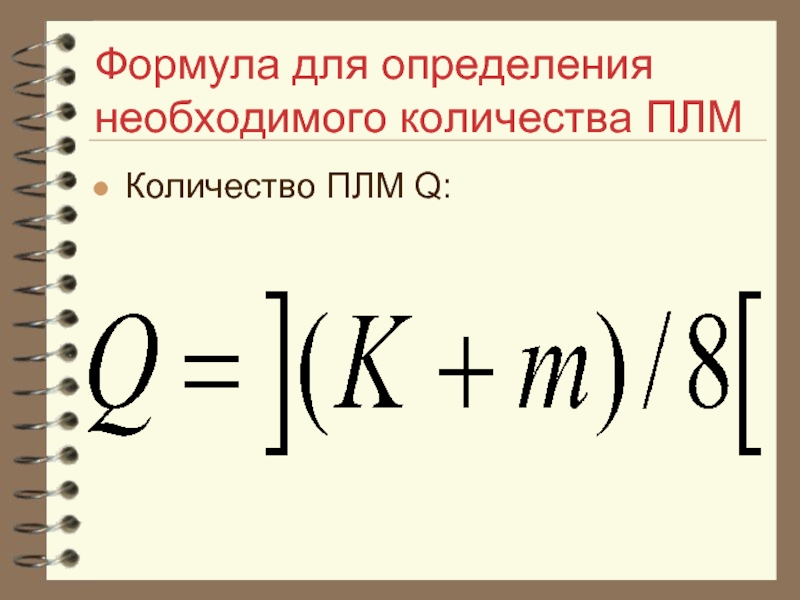

- 188. Формула для определения необходимого количества ПЛМ Количество ПЛМ Q:

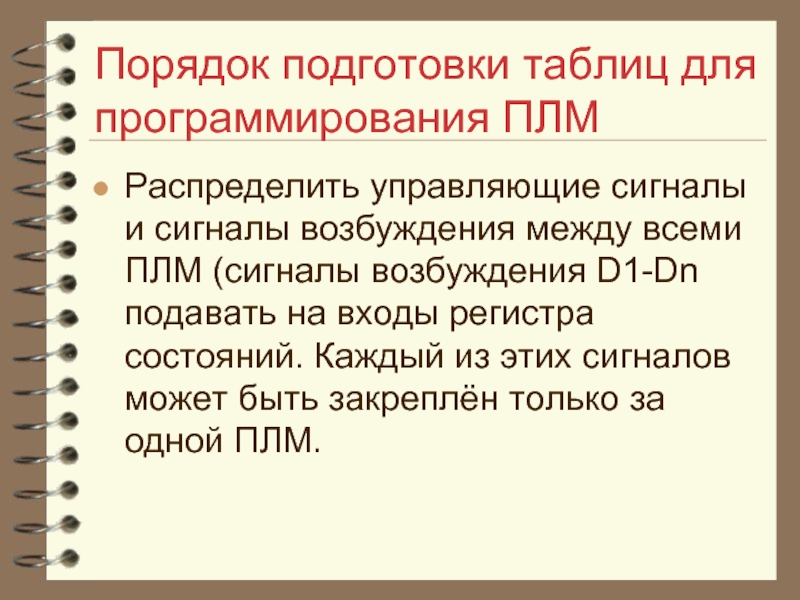

- 189. Порядок подготовки таблиц для программирования ПЛМ Распределить

- 190. Подготовка таблиц ПЛМ Выполнить (виртуальное) программирование ПЛМ.

- 191. Подготовка таблиц ПЛМ В каждой строке

Слайд 2Основная учебная литература

В.Л. Бройдо, О.П. Ильина. Архитектура ЭВМ и систем. Учебник

Э. Танненбаум. Архитектура компьютера. 4-е издание. – СПб.: Питер, 2006. – 699 с

Слайд 3Основная учебная литература

К. Хамакер, Э. Вранешич, С. Заки. Организация ЭВМ. 5-е

Слайд 4Дополнительная учебная литература

М. Гук, Аппаратные интерфейсы ПК. Энциклопедия. – Питер 2003.

Новожилов О.П., Архитектура ЭВМ и систем: учеб. Пособие для бакалавров / Новожилов О.П., М. : Юрайт, 2012. – 527 с.

Слайд 5Дополнительная учебная литература

Столингс. Структурная организация и архитектура компьютерных систем. 5-е В

Б.Ф. Томпсон, Р.Б. Томпсон. Железо ПК: Энциклопедия. 3-е издание. – СПб.: Питер, 2004. – 960 с.

Слайд 6Неймановские принципы построения ЭВМ

1. Вся информация в системе представляется и обрабатывается

Все типы слов (данные, адреса, команды) кодируются одинаково.

Слайд 7Неймановские принципы построения ЭВМ

3. Слова размещаются в ячейках

памяти и идентифицируются

4. Алгоритм решения задачи записывается в виде последовательности управляющих слов. Управляющее слово указывает на тип операции и операнды.

Слайд 8Неймановские принципы построения ЭВМ

Управляющее слово называется машинной командой. Последовательность управляющих слов

Слайд 9Неймановские принципы построения ЭВМ

5. Выполнение вычислений в ЭВМ сводится к последовательному

Слайд 10Структура машины

Фон-Неймана

Операционная устройство

Устройство управления

Запоминающее устройство

Устройство ввода-вывода

Слайд 11Структурная организация современных ЭВМ

ЭВМ- инженерная система для выполнения вычислений по алгоритмам.

ЭВМ

Состав – набор устройств.

Структура – устройства и связи между ними.

Слайд 12Структурная организация современных ЭВМ

Совокупность связей двух взаимодействующих устройств по электрическим цепям

Основными характеристиками интерфейса являются: скорость надёжность, стоимость.

Слайд 13Типы интерфейсов

Последовательный

Параллельный

Паралллельно-последовательный

Типовой шинный интерфейс:

ШУ-шина управления;

ША-шина адреса;

ШД-шина данных

Слайд 15Основные характеристики ЭВМ

1. Операционные ресурсы:

Способы представления данных; способы адресации; система машинных

Слайд 17Основные характеристики ЭВМ

3. Быстродействие.

Основная характеристика быстродействия: V [оп/сек];

Длительность операции: Tоп=1/V [сек]

Слайд 18Основные характеристики ЭВМ

4. Производительность.

Характеризует время решения задачи в однопрограммном режиме:

При мультипрограммном режиме: T=

T задачи +T ожидания ресурса

Слайд 19Основные характеристики ЭВМ

T задачи в мультипрограммном режиме определяется:

- номинальным быстродействием;

- классом

- организацией выполнения вычислительного процесса

Слайд 20Основные характеристики ЭВМ

5. Надёжность.

Надёжность характеризуется средним временем наработки на отказ

Формула Тср и Лямда

Слайд 21Основные характеристики ЭВМ

6. Стоимость.

На стоимость влияют:

- элементная база;

- операционные ресурсы;

- быстродействие;

-

- надёжность.

Слайд 23Представление данных в ЭВМ

2. Целые двоичные числа

Диапазон представления:

от –(2 в

Слайд 25Представление данных в ЭВМ

Особенности выполнения арифметических операций:

А) сложение и вычитание:

Б) умножение: отображается n младших разрядов и округляется.

Слайд 284. Числа с плавающей запятой

Структура числа:

Число с плавающей запятой состоит из:

Знака

Мантиссы (выражающей значение числа без учёта порядка)

Знака порядка

Порядка (выражающего степень основания числа, на которое умножается мантисса)

Слайд 294. Числа с плавающей запятой

Нормальная форма и нормализованная форма

Нормальной формой числа с

Слайд 304. Числа с плавающей запятой

Такая форма записи имеет недостаток: некоторые числа

Слайд 314. Числа с плавающей запятой

Нормализованная форма, в которой мантисса десятичного числа

Слайд 324. Числа с плавающей запятой

Недостаток заключается в том, что в таком

Слайд 334. Числа с плавающей запятой

Так как старший разряд (целая часть числа)

Слайд 34Cтандарт IEEE 754-1985 определяет:

как представлять нормализованные положительные и отрицательные числа с

как представлять денормализованные положительные и отрицательные числа с плавающей точкой

как представлять нулевые числа

как представлять специальную величину бесконечность (Infinity)

как представлять специальную величину "Не число" (NaN или NaNs)

четыре режима округления

Слайд 35

EEE 754-1985 определяет четыре формата представления чисел с плавающей запятой:

с одинарной точностью (single-precision) 32 бита

с двойной точностью (double-precision) 64 бита

с одинарной расширенной точностью (single-extended precision) >=43 бит (редко используемый)

с двойной расширенной точностью (double-extended precision) >= 79 бит (обычно используют 80 бит)

Слайд 36Основные понятия в представлении чисел с плавающей точкой.

Представление числа в нормализованном

Возьмем, к примеру, десятичное число 155,625 Представим это число в нормализованном экспоненциальном виде : 1,55625∙10+2=1,55625∙exp10+2 Число 1,55625∙exp10+2 состоит из двух частей: мантиссы M=1.55625 и экспоненты exp10=+2

Слайд 37

Если мантисса находится в диапазоне 1<=M<10, то число считается нормализованным.

Экспонента представлена основанием системы исчисления (в данном случае 10) и порядком (в данном случае +2).

Порядок экспоненты может иметь отрицательное значение, например число 0,0155625=1,55625∙exp10-2.

Слайд 38Представление данных в ЭВМ

Z=плюс-минус М*d в степени плюс-минус П. где d-основание

Где r=1,2,3…

Число нормализовано, если r старших разрядов мантисс не равны 0.

Слайд 39Представление данных в ЭВМ

Из-за ограничений на разрядность мантиссы и порядка возможны

- потеря значимости: М=0, П не =0 -машинный ноль;

-исчезновение порядка П< -2 в степ.(2в степ n-1)

-деление на 0

Слайд 40Представление данных в ЭВМ

5. Десятичные целые числа.

Числа обрабатываются последовательно

Слайд 43Машинные операции

1. Свойства машинных операций:

Машинная операция –это действие,

Множеству машинных операций соответствует множество машинных команд. Машинная команда инициирует определённую машинную операцию.

Слайд 44Машинные операции

Набор машинных операций характеризуется двумя свойствами:

а) функциональной

б) эффективность, которая определяется затратами на оборудования для достижения требуемой производительности.

Слайд 45Машинные операции

2. Классификация машинных операций.

а) арифметические и логические операции : +,-,*,

б) посылочные: обмен между ОП-ЦП;

в) операции прерывания;

г) ввод-вывод;

д) системные

Слайд 46Система команд ЭВМ

По функциональному назначению в системе команд ЭВМ различают следующие

команды передачи данных (обмен входами между регистрами процессора, процессора и оперативной памятью, процессора и периферийными установками).

Слайд 47Система команд ЭВМ

Команды обработки данных (команды сложения, умножения, сдвига, сравнения).

Команды

Слайд 49Способы адресации

Способ адресации – это правило определения адреса и операнда

Эффективность способа адресации влияет на временные затраты и затраты на определённый необходимый состав оборудования.

Слайд 50Способы адресации

Способы формирования адресов ячеек памяти можно разделить на абсолютные и

Абсолютные способы формирования предполагают, что двоичный код адреса ячейки памяти может быть целиком извлечен либо из адресного поля команды, либо из какой-нибудь другой ячейки в случае косвенной адресации.

Слайд 51Способы адресации

Относительные способы формирования предполагают, что двоичный код адресной ячейки памяти

Б v код базы, И v код индекса, С v код смещения.

Эти составляющие используются в различных сочетаниях.

Слайд 52Способы адресации

Относительная адресация

При относительной адресации применяется способ вычисления адреса путем суммирования

А = Б + И + С А = Б + С А = И + С

Слайд 53Способы адресации

1. Прямая адресация.

адресная часть команды содержит непосредственный (прямой) адрес

операнда

Слайд 54Способы адресации

2. Непосредственная адресация

Целочисленное значение операнда записывается в поле команды.

Слайд 55Способы адресации

3. Косвенная адресация.

Адресная часть команды содержит косвенный адрес;

Адресный код

Слайд 57Способы адресации

4. Регистровая адресация.

Применяется, когда промежуточные результаты хранятся в одном из

Слайд 59Способы адресации

5. Адресация с модификацией адресов.

Для реализуемых на ЭВМ методов решения

Слайд 60Способы адресации

Программирование циклов существенно упрощается, если после каждого выполнения цикла обеспечено

Такой процесс называется модификацией команд, и основан на возможности выполнения над кодами команд арифметических и логических операций.

Слайд 61Способы адресации

Индексная адресация

Для работы программ с массивами, требующими однотипных операций над

Слайд 63Индексная адресация

Адрес i-того операнда в массиве определяется как сумма начального адреса

Адрес индексного регистра задается в команде полем адреса индекса Аи.

В каждом i-том цикле содержимое индексного регистра изменяется на постоянную величину, как правило, это 1.

Слайд 64Способы адресации.

6. Прямая адресация с модификацией.

В полях команды содержится Рон,

Слайд 65Способы адресации

7. Регистровая адресация с модификацией.

Поля команды содержать два

Слайд 67Способы адресации

9. Стековая адресация

Стековая память широко используется в современных ЭВМ. Хотя

Слайд 699.Стековая адресация

Для чтения записи доступен только один регистр v вершина стека.

Стековая память реализуется на основе обычной памяти с использованием указателя стека и автоиндексной адресации.

Запись в стек производится с использованием автодекрементной адресации, а чтение - с использованием автоинкрементной адресации.

Слайд 70Исходные данные для проектирования ОУ

F - множество операций,

D - множество

R - множество выходных данных, результатов вычислений,

ограничения на время выполнения операции.

Слайд 71Исходные данные для проектирования ОУ

Задача проектирования- создание ОУ минимальной размерности и

Для проектирования ОУ все операции описываются в виде наборов микропрограмм.

Слайд 72Исходные данные для проектирования ОУ

Формализованная микропрограмма

(ФМП) описывает работу ОУ безотносительно к

Слайд 73Исходные данные для проектирования ОУ

Язык формализованного описания микропрограмм (ЯФМП) применяется для

(МО)и логических условий (ЛУ).

Как правило удобнее использовать инженерную версию ЯФМП.

Слайд 74ЯФМП

ЯФМП состоит из описательной части (описание слов, МО и ЛУ) и

Описательный уровень позволяет описать работу ОУ на регистровом уровне.

Содержательный уровень отслеживает выполнение переходов по логическим условиям.

Слайд 75ЯФМП

1. Описание слов:

с (n1:n2), где:

С – идентификатор

n2-младший разряд слова.

Каждое слово связано со своим регистром, либо другим устройством.

Слайд 76ЯФМП

Например, запись СчК(3:0) обозначает четырёхразрядный счётчик с присвоенным ему идентификатором СчК,

Слайд 77ЯФМП

2. Описание массивов:

М[m2:m1](n2:n1) где:

m2 и m1 –указатели номеров старшей

n2 и n1 - разряды слова внутри массива.

Например: [255:0](n2:n1)

Слайд 78ЯФМП

3. Поля

Например: Рг А(31:0); Рг А(15:0)

Адр(15:0) = РгА(15:0) КОП(15:0)=РгА(31:16)

Полям

Слайд 79ЯФМП

4. Типы слов.

Каждое слово характеризуется определённым типом.

Нашли применения следующие

- входные (I);

-внутренние (L);

- вспомогательные (A)(промежуточные) (действуют на 1 такт);

- выходные (O).

Слайд 81ЯФМП. 4. Типы слов.

Все слова, используемые в микропрограмме должны быть описаны

Слайд 82ЯФМП

5. Двоичные выражения.

Описывают преобразования, выполняемые микрооперациями.

Двоичные выражения (ДВ) состоят из

Слайд 835. Двоичные выражения.

В качестве ДВ используют:

1. Константы (двоичные, восьмеричные, шестнадцатеричные);

2. Слова,

3. Поля;

4. Элементы массивов М[31:0](15:0)

Слайд 84ЯФМП

6. Двоичные операции.

Инверсия старшинство: 1

Конкатенация старшинство: 2

Конъюнкция

Дизъюнкция старшинство: 4

Сложение по mod 2 старш: 4

Арифм. сложение старш: 5

Циклич. Сложение старш: 5

Вычитание старшинство: 5

Слайд 85Микрооперации

Синтаксис записи микрооперации:

:= оператор присваивания.

А м.быть словом, полем, элементом массива.

В

Микрооперация (МО) выполняется за один такт. В начале такта вычисляется двоичное выражение, в конце такта выполняется присваивание.

Слайд 86Микрооперации

Типовые микрооперации. Классификация.

1. Установка значения A:=const

2. Инвертирование A:=!A

3. Передача

Микрооперация передаёт информацию из одного регистра в другой.

Слайд 87Микрооперации

Оператор присваивания в синтаксической записи:

:=

Вся микрооперация выполняется за один

Слайд 88Микрооперации

4. Сдвиговые микрооперации.

При сдвиге указывается направление сдвига, на сколько разрядов осуществляется

Слайд 89Микрооперации

Синтаксис записи МО сдвига:

RK – сдвиг на к разрядов вправо;

Например: A:=R1(1.А), A:=L1(A.0)

В первом случае заполнение единицами, во втором нулями.

Слайд 91Микрооперации

Правила выполнения сдвигов:

1. При логическом сдвиге освобождаемые разряды заполняются нулями.

2. При

Слайд 92Микрооперации

При арифметическом сдвиге выполняются следующие правила:

- при сдвиге влево освобождаемые разряды

- при сдвиге вправо освобождаемые разряды заполняются значением бита знака;

- разряд знака не сдвигается, сдвигается только числовая часть числа.

Слайд 93Микрооперации

5. Микрооперации счёта.

Используются в том числе и для описания работы

А:=А+1 – инкремент;

А:=А-1 – декремент

Микрооперации арифметического сложения и вычитания.

При сложении операнды выравниваются по младшим разрядам с заполнением нулями старших лишних разрядов.

Слайд 94Микрооперации

Совместимость микроопераций.

Совместимыми называются микрооперации, которые выполняются в одном такте.

Один машинный такт

Совместимые МО подразделяются на :

А) функциональные;

Б) структурные.

Слайд 95Микрооперации

Функциональная совместимость определяется алгоритмом. Две МО будут такими, если они присваивают

А:=А+В и А:= С-D не совместимые операции

Слайд 96Микрооперации

Структурная совместимость ограничивается аппаратурно.

Две МО считаются структурно совместимыми, если они выполняются

Слайд 97Микрооперации

Логические условия.

Логические условия представляют из себя булеву функцию. В качестве первичных

Отношение – конструкция вида:

С1*С2, где *- операция отношения: больше, меньше, не равно.

Слайд 98Содержательный граф функциональной микропрограммы.

Для записи графа используются 4 типа вершин

Слайд 99Содержательный граф функциональной микропрограммы.

Типы вершин графа .

1. Вершина «начало». Определяет начало

Слайд 100Содержательный граф функциональной микропрограммы.

2. Функциональная вершина.

Используется для указания совместных МО,

Слайд 101Содержательный граф функциональной микропрограммы.

3. Условная вершина.

Используется для описания разветвлений в

Слайд 102Содержательный граф функциональной микропрограммы.

4. Конечная вершина.

Может иметь произвольное число

Слайд 103Содержательный граф функциональной микропрограммы.

Граф должен быть корректным, то есть не должен

Правила построения графа микропрограммы.

1. Граф должен иметь только одну начальную и одну конечную вершину.

Слайд 104Содержательный граф функциональной микропрограммы.

2. В каждую вершину, кроме начальной, должна входить

3. Из каждого выхода каждой вершины должна исходить одна и только одна дуга.

4. При любом наборе исходных данных должен существовать путь из начальной вершины в конечную.

Слайд 105Этапы разработки ФМП

Рассмотрим данные этапы на примере операции умножения.

Исходные данные:

1. умножение

2. умножение осуществляется в прямых кодах над модулями аргументов операции;

Слайд 106Этапы разработки ФМП

3. Произведение занимает двойную дину слова аргументов.

4. Знак результата

5. Пример умножения в столбик:

Слайд 108Этапы разработки ФМП

Словесное описание алгоритма умножения.

1. Обнулить регистр С (хранит промежуточные

Слайд 109Этапы разработки ФМП

2. Множимое располагается в

регистре А. Множитель в регистре

3. Если младший разряд множителя (В(0)) равен 1, то производится сложение множимого и содержимого регистра С, при нулевом значении сложение не производится.

Слайд 110Этапы разработки ФМП

4. Производится сдвиг вправо регистров С и В, при

Повторяются п.3 и п.4. столько раз, сколько разрядов содержит множитель.

5. Знак результата определяется как сумма по модулю 2 старших знаковых разрядов аргументов А и В и записывается в старший разряд регистра С.

Слайд 111Этапы разработки ФМП

Описание слов.

Тип слова Формат

I A(4:0) ЗнА=(4) множи-

мА=А(3:0) мое

_________________________________________________

I В(4:0) ЗнВ=(4) множи-

мВ=В(3:0) тель

__________________________________________________

Слайд 112Этапы разработки ФМП

Описание слов.

Тип слова Формат

О С(4:0) ЗнС=(4) старшая

мС=С(3:0) часть рез.

_________________________________________________

L Сч(2:0) счётчик

__________________________________________________

Слайд 113Логическое проектирование операционного автомата (ОА)

Структурный базис ОА

Структурный

а) триггеры, регистры, счётчики, и др.,

б) комбинационные схемы;

в) шины.

Слайд 114Шины. Архитектуры шин.

УГО шины.

Каждая шина должна иметь свой собственный уникальный

Слайд 115Шины. Архитектуры шин.

Шины могут изгибаться, разветвляться, пересекаться.

По шинам можно передавать информацию

Слайд 116Шины. Архитектуры шин.

По шинам можно передавать информацию от многих источников к

Слайд 117Порядок проектирования ОА

1. Описание ОА.

В общем случае ОА может

Слайд 118Порядок проектирования ОА

МП слова

МП1 А(15.0) A:=B A=0

B(15.0) A:=A+B

-----------------------------------------------------

МП2 A(7:0) A:=B B=1

B(7:0) A:=A-B

-----------------------------------------------------

Слайд 120Методика синтеза канонической структуры ОА

Исходные данные:

S; Y; X; структурный базис.

1) Выделение

Слайд 124Синтез ОА для блока умножения

Описание блока умножения:

Составление таблицы:

________________________________

Слово

________________________________

Слайд 126Порядок работы ОА

В ОА в каждом машинном такте выполняется одна или

<адрес>:=<двоичное выражение>

Слайд 127

Порядок работы ОА

ОА работает по тактам. В такте происходит:

1) формирование управляющих

2) вычисление значения двоичного выражения (МО);

3) сохраняется результат в регистре;

4) вычисляются логические условия и определяются значения условных переменных Х1, Х2,…….Хn.

Слайд 128Порядок работы ОА

Длительность машинного такта:

Tмт>ty+tmo+tлу

В конце такта запись в регистр производится

Слайд 129Характеристики ОА

1. Производительность (количество МО за такт).

2. Быстродействие (длительность такта).

3. Затраты

Слайд 130Структурная организация ОА.

Классификация структур автоматов:

1.I –автоматы. Их производительность такая же как

Слайд 131Структурная организация ОА.

2. М –автоматы: в каждом машинном такте может выполняться

3. IM – автоматы с промежуточными характеристиками: производительность >1, но имеются структурные ограничения на совместимость МО.

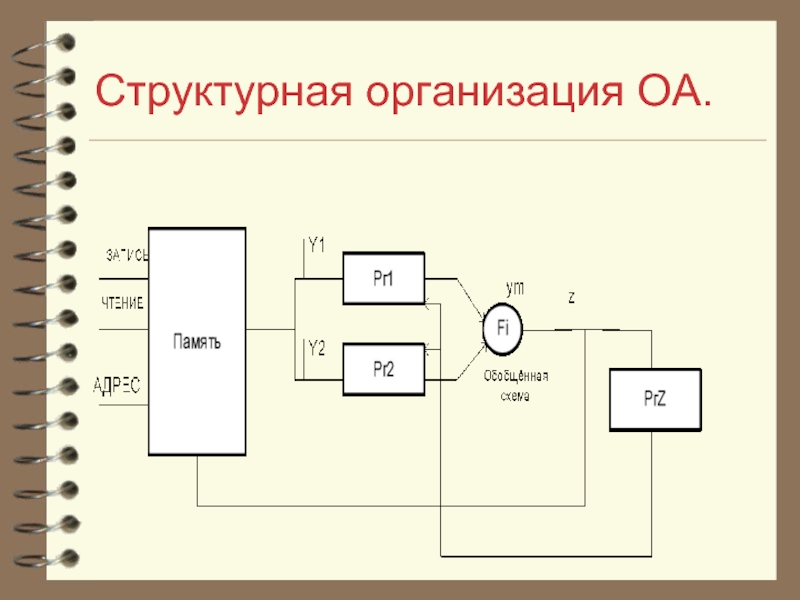

Слайд 132Структурная организация ОА.

4. S - автоматы: используются, когда надо обрабатывать большое

В этом случае для хранения используются не регистры, а память.

Слайд 134Построение ОЭ на основе регистра

Возможные операции на регистре:

1). С:= А

2). С:=0

3).

4). С: = R1(0.C)

5). C: = L1(C.0)

Слайд 144Операции АЛУ

Перечень выполняемых АЛУ операций дан в след.таблице.

Слайд 146Соединение нескольких АЛУ

При операциях над словами большой

В последнем случае совместно с АЛУ применяют микросхемы — блоки ускоренного переноса, получающие от отдельных АЛУ функции генерации и прозрачности, а также входной перенос и вырабатывающие сигналы переноса.

Слайд 148Синтез операционного элемента на основе АЛУ

Перечень микроопераций:

F=A+B

F=A-B

F=A+1

F=A-1

F=A&B

F=A/\B

Слайд 152Типы цифровых автоматов

Два типа автоматов:

А) Цифровой автомат Мили;

Б) Цифровой автомат Мура.

Слайд 153Определение автомата Мили

Конечным детерминированным автоматом типа Мили называется совокупность пяти объектов

,

где

и

со связью элементов множеств S, X и Y в абстрактном времени T = {0, 1, 2, …} уравнениями:

Слайд 154Определение автомата Мили

(Отображения и получили названия, соответственно функции переходов и функции

Особенностью автомата Мили является то, что функция выходов является двухаргументной и символ в выходном канале y(t) обнаруживается только при наличии символа во входном канале x(t). Функциональная схема не отличается от схемы абстрактного автомата.

Слайд 155Цифровой автомат Мура

Зависимость выходного сигнала только от состояния представлена в автоматах типа Мура(англ. Moore machine).

Слайд 156Цифровой автомат Мура

Конечным детерминированным автоматом типа Мура называется совокупность пяти объектов:

где S, X, Y и δ — соответствуют определению автомата типа Мили, а μ является отображением вида: μ : S → Y,

с зависимостью состояний и выходных сигналов во времени уравнением:

.

Слайд 157Цифровой автомат Мура

Особенностью автомата Мура является то, что символ y(t) в выходном канале существует все

Слайд 159Построение цифрового автомата по схеме Мура.

КС1 управляет памятью;

КС2 формирует набор выходных

V-сигнал возбуждения, управляющий памятью.

Слайд 160Построение цифрового автомата по схеме Мура.

Исходные данные для автомата Мура:

ФМП хранит

Слайд 161Построение цифрового автомата по схеме Мура

Формализуем МП с помощью закодированного графа,

логические условия -осведомительным сигналом X.

Слайд 163Этапы синтеза УА

1. Построение таблицы микроопераций и логических условий.

2. Построение закодированного

3. На закодированном графе пометить вершины индексами а0,а1…аn-1.

Слайд 164Этапы синтеза УА

4. Построение графа автомата МУРА:

Каждому состоянию поставить в соответствие

Каждому переходу поставить в соответствие дугу графа.

Слайд 165Этапы синтеза УА

5. Построение списка переходов в табличной форме. В таблице

(а нач. и а конеч.)

Слайд 166Организация памяти цифрового автомата

Память ЦА строится на основе регистра. Разрядность регистра

Слайд 173Функции сигналов возбуждения

D0=a0*x1+a1*!x2+a2*!x3+a4*!x5+a4*x5+a7*!x6+a15*!x8

D1=

D2= и т.д.

Слайд 175Технология подготовки записей булевых функций для программирования ПЛМ

Y=!x1!x2x3+(!x1x2!x3+!x1x2x3)+

+(x1x2!x3+x1x2x3)

Y=!x1!x2x3+!x1x2+x1x2

Y=!x1!x2x3+x2

Слайд 177Технология подготовки записей булевых функций для программирования ПЛМ

Данный подход можно распространить

Слайд 178Технология подготовки записей булевых функций для программирования ПЛМ

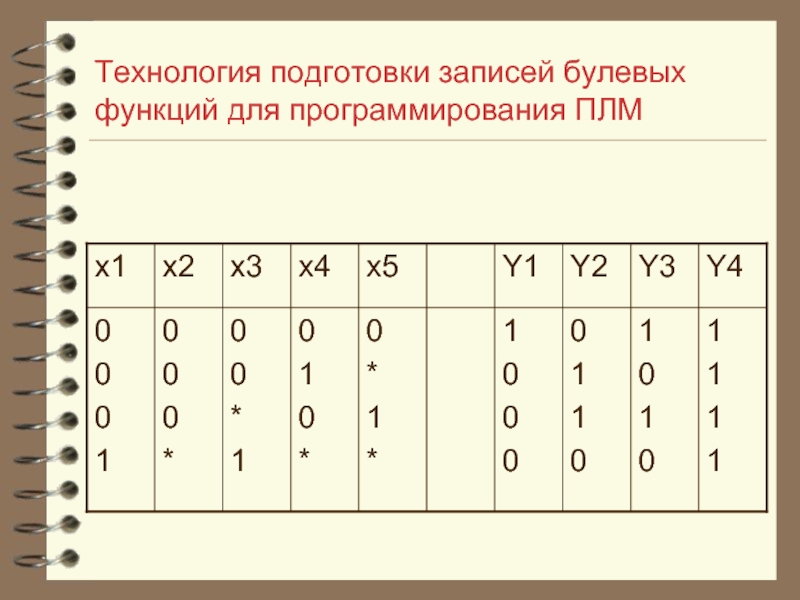

Пусть заданы четыре булевых

Слайд 181Технология подготовки записей булевых функций для программирования ПЛМ

Y1=Z1;

Y2=Z2+Z3;

Y3=Z1+Z3;

Y4=Z1+Z2+Z3+Z4

ПЗУ реализуют произвольную логическую

Слайд 185УГО ПЛМ

Для того чтобы отличать ПЛМ от ПЗУ при изображении принципиальных

Слайд 187Определение набора ПЛМ

ПЛМ имеют 16 входов,8 выходов и от 48 до

Для определения необходимого количества (Q) ПЛМ, для реализации

управляющего автомата, имеющего К разрядов регистра и m – число управляющих сигналов y, формируемых в автомате используется формула:

Слайд 189Порядок подготовки таблиц для программирования ПЛМ

Распределить управляющие сигналы и сигналы возбуждения

Слайд 190Подготовка таблиц ПЛМ

Выполнить (виртуальное) программирование ПЛМ. Для каждой ПЛМ составить таблицу

В каждой таблице указать входы, выходы и строки.

На входы F1 – Fk всех ПЛМ подключить выходы регистра состояний (старшие слева- младшие справа). На остальные входы ПЛМ подключить осведомительные сигналы (условий), используемые в данной ПЛМ. Неиспользуемые входы ПЛМ не указывать. Число входов не должно превышать 16. Число выходов в каждой ПЛМ не должно превышать 8.

Слайд 191Подготовка таблиц ПЛМ

В каждой строке входов прямое значение переменной кодировать

На выходах единицей обозначать необходимость использовать данную конъюнкцию (строку) в булевской функции, описывающей соответствующую выходную переменную (управляющий сигнал Y или сигнал возбуждения D).

Число строк в каждой матрице не должно превышать 68.

![Основные характеристики ЭВМ3. Быстродействие.Основная характеристика быстродействия: V [оп/сек];Длительность операции: Tоп=1/V [сек]](/img/tmb/1/8718/0f6f8bae44882c4ab8cfd1027b80820c-800x.jpg)

где: m2 и m1 –указатели номеров старшей и младшей ячейки массива;](/img/tmb/1/8718/df663baf9f509a6641cb9952c2ca872a-800x.jpg)