- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Описание комбинационных устройств на VHDL презентация

Содержание

- 1. Описание комбинационных устройств на VHDL

- 2. Оператор параллельного назначения сигналов Простое назначение сигналов: status

- 3. Назначение сигналов с обратной связью Нельзя назначать сигналы с обратной связью! q

- 4. Оператор условного назначения сигналов сигнал

- 5. Пример 1. Мультиплексор 8 бит

- 6. Пример 2. Бинарный дешифратор library

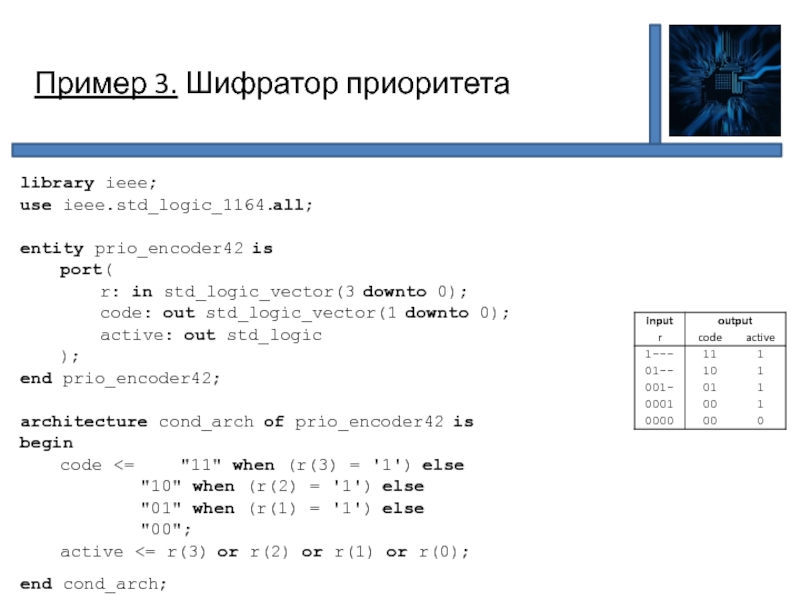

- 7. Пример 3. Шифратор приоритета library

- 8. Семантика оператора условного назначения сигнала

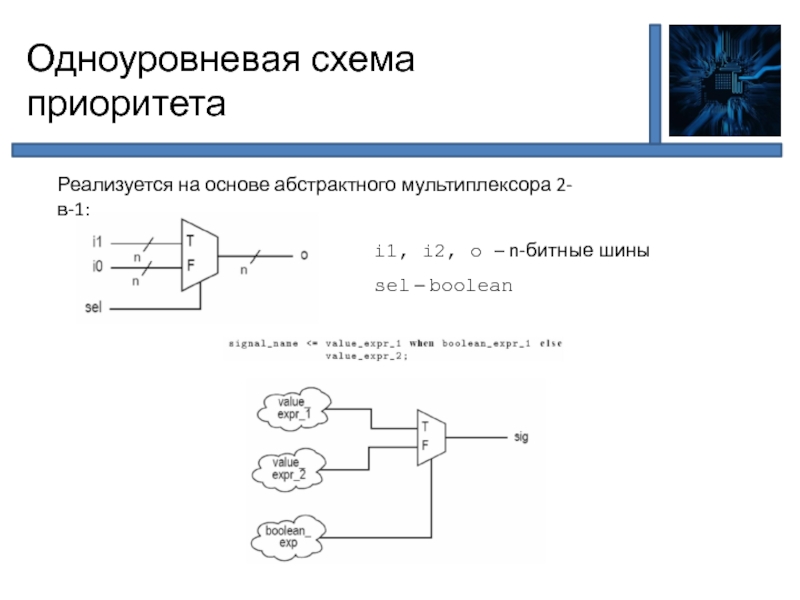

- 9. Одноуровневая схема приоритета i1, i2,

- 10. Трехуровневая схема приоритета

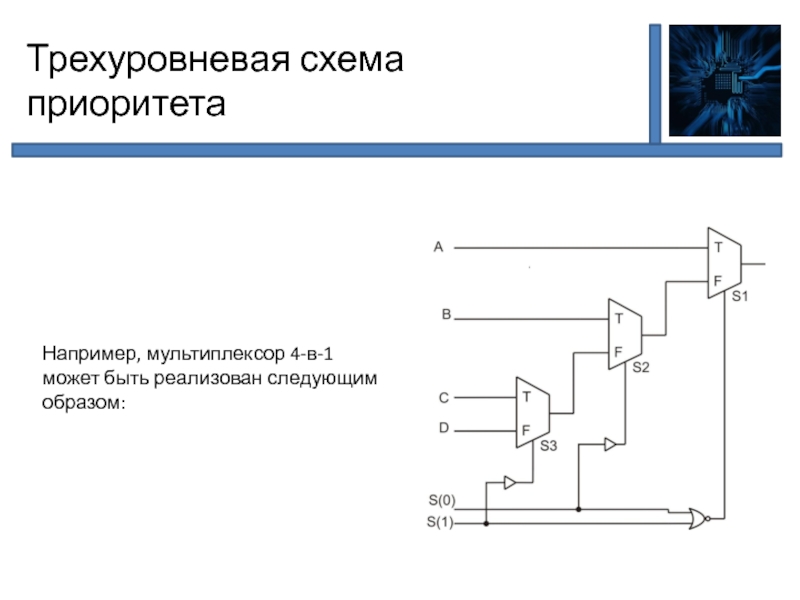

- 11. Трехуровневая схема приоритета Например, мультиплексор 4-в-1 может быть реализован следующим образом:

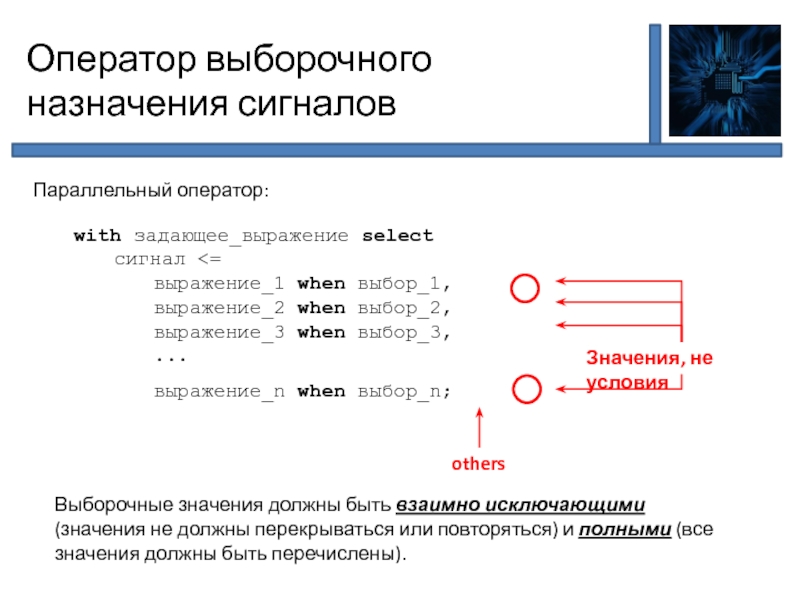

- 12. Оператор выборочного назначения сигналов Выборочные

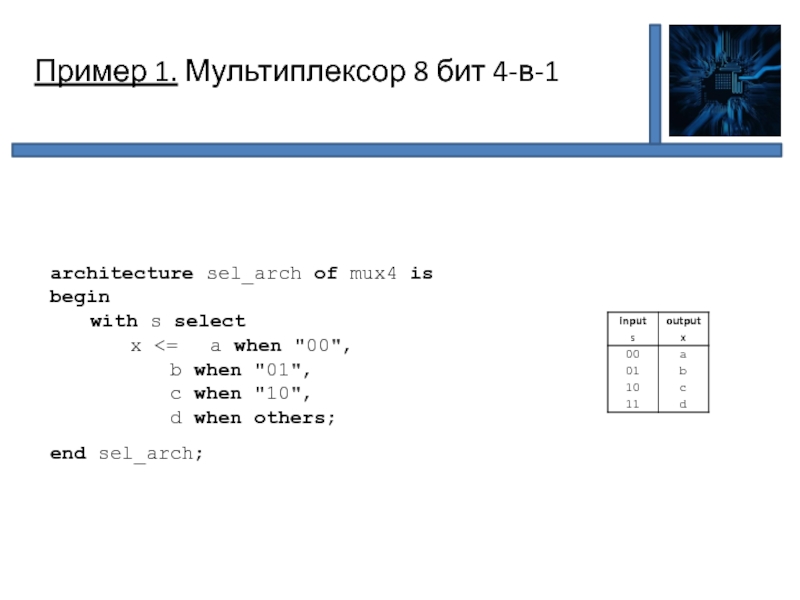

- 13. Пример 1. Мультиплексор 8 бит

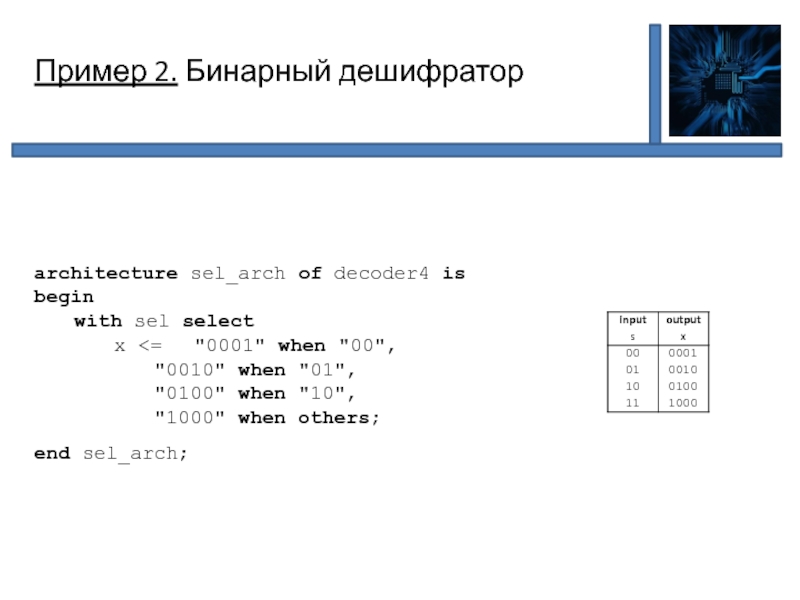

- 14. Пример 2. Бинарный дешифратор architecture

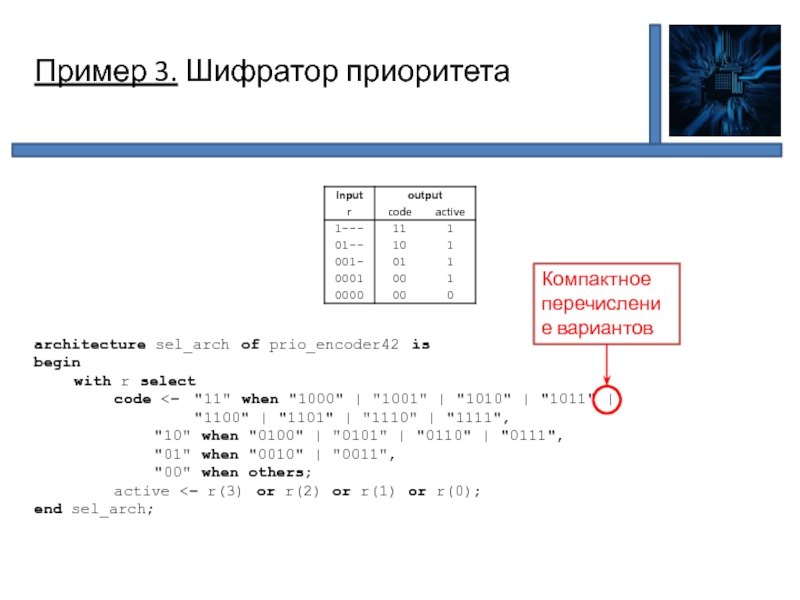

- 15. Пример 3. Шифратор приоритета architecture

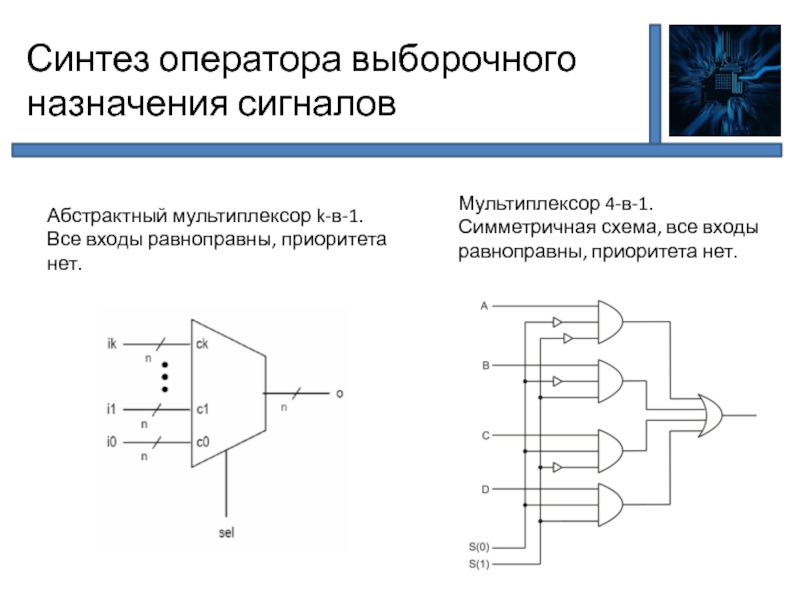

- 16. Синтез оператора выборочного назначения сигналов

- 17. Сравнение операторов На примере мультиплексора

- 18. Последовательные операторы. Оператор процесса. process(список_чувствительности)

- 19. Последовательные операторы. Оператор процесса Синтаксис: имя_сигнала

- 20. Последовательные операторы. Оператор wait Процесс

- 21. Оператор IF Какой язык программирования

- 22. Пример 1. Мультиплексор 4-в-1 architecture

- 23. Пример 2. Бинарный дешифратор architecture

- 24. Пример 3. Шифратор приоритета architecture

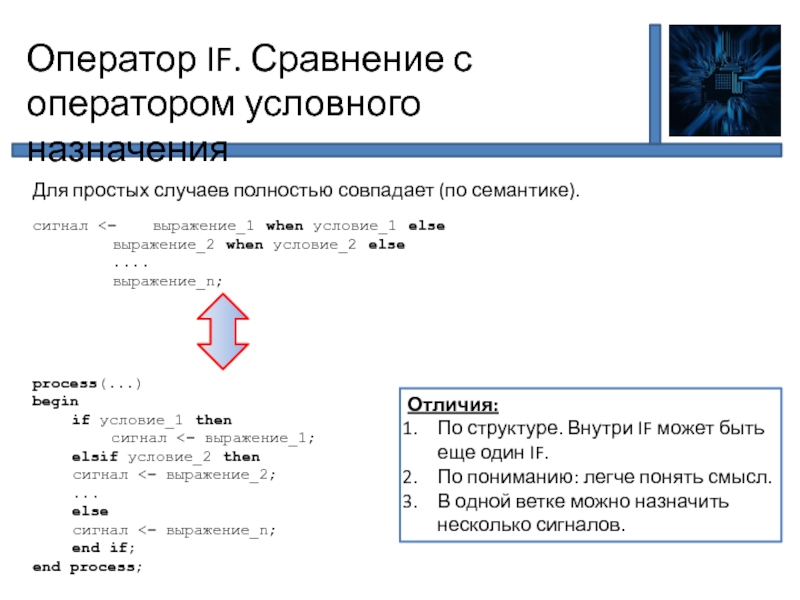

- 25. Оператор IF. Сравнение с оператором

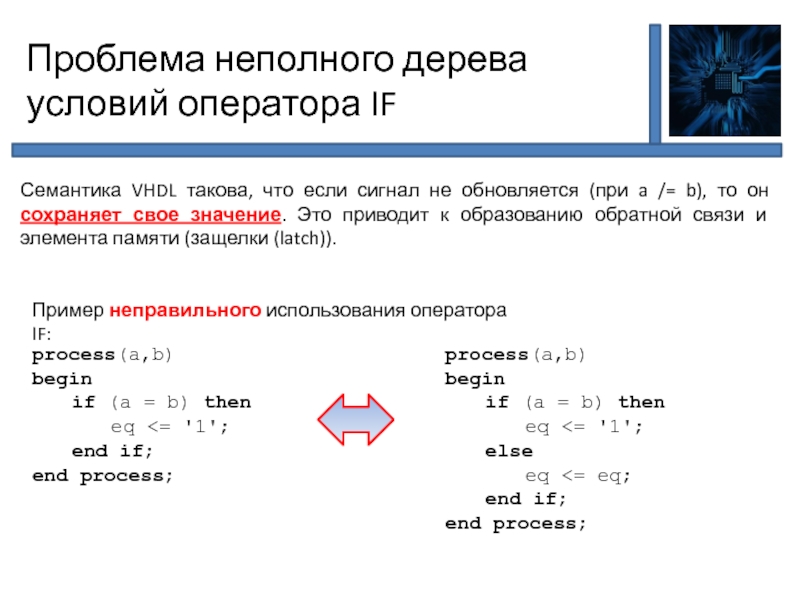

- 26. Проблема неполного дерева условий оператора

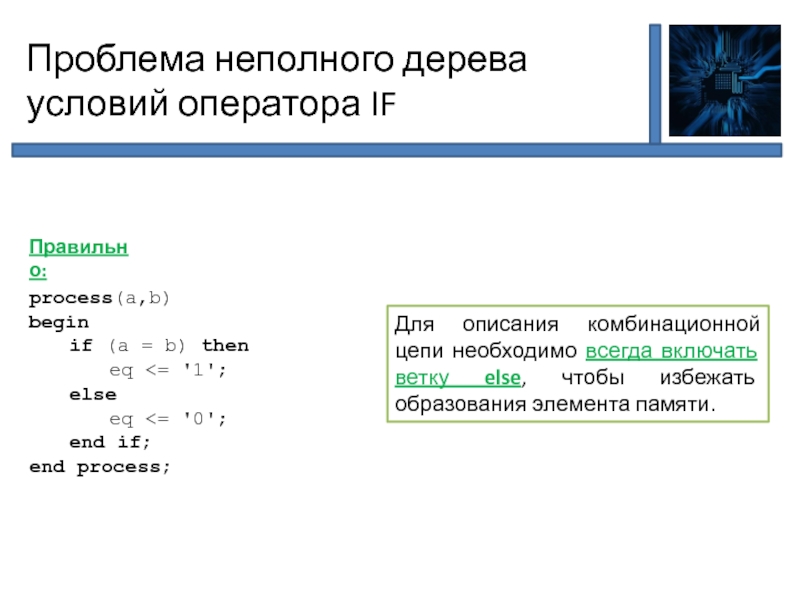

- 27. Проблема неполного дерева условий оператора

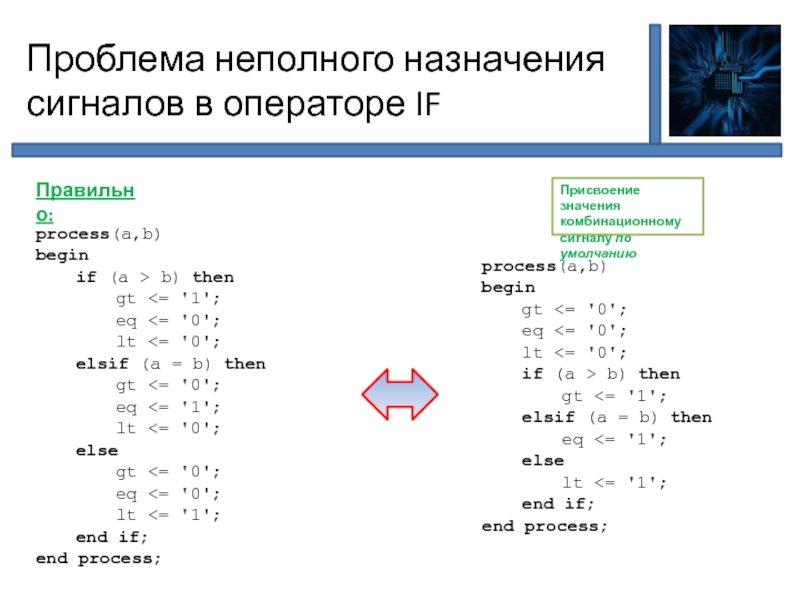

- 28. В общем случае оператор IF

- 29. Правильно: Проблема неполного назначения сигналов в операторе IF process(a,b) begin gt

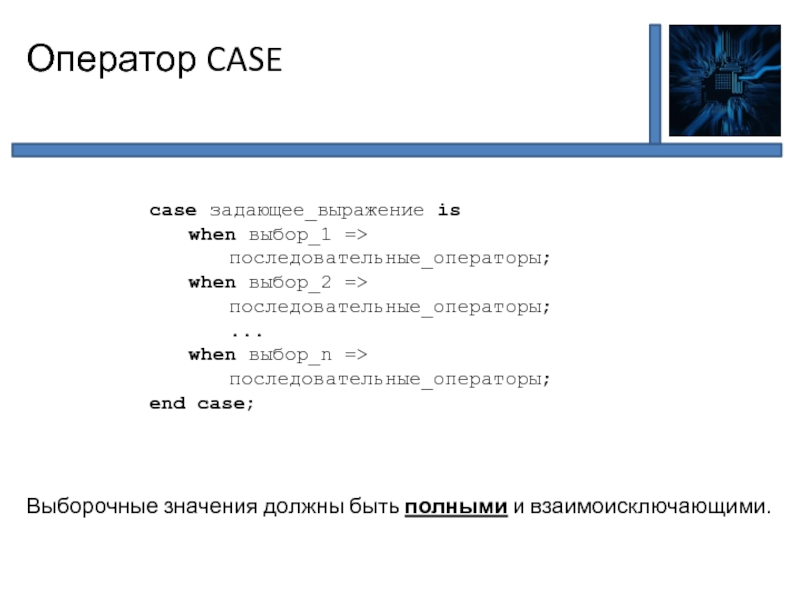

- 30. Оператор CASE Выборочные значения должны

- 31. Пример 1. Мультиплексор 4-в-1 architecture

- 32. Пример 2. Бинарный дешифратор architecture

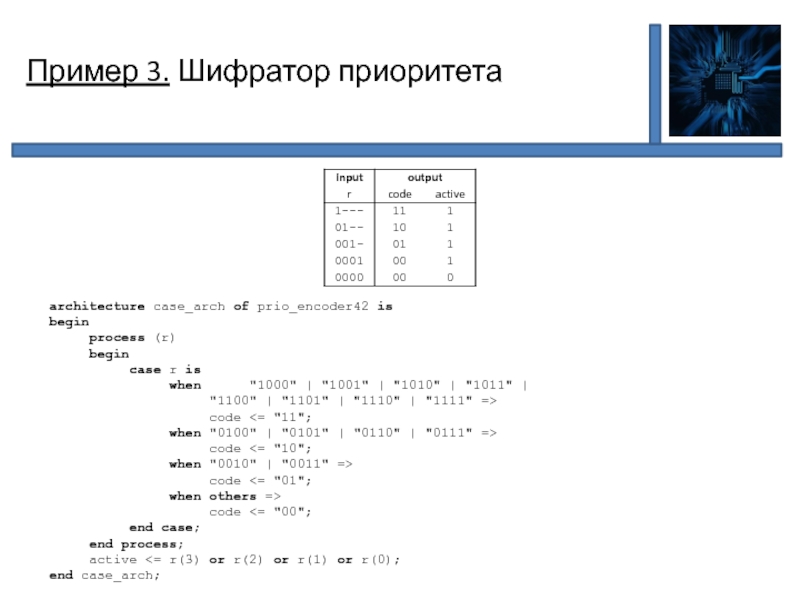

- 33. Пример 3. Шифратор приоритета architecture

- 34. Оператор CASE. Сравнение с оператором

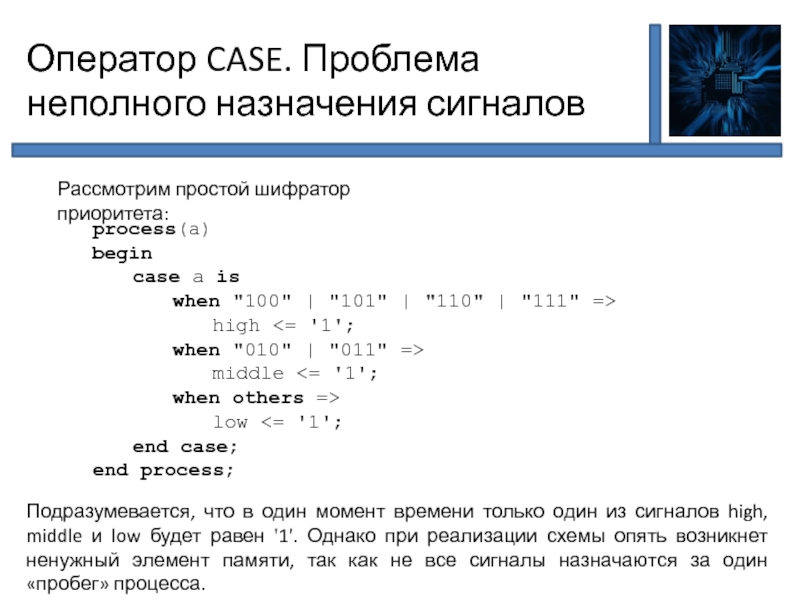

- 35. Оператор CASE. Проблема неполного назначения

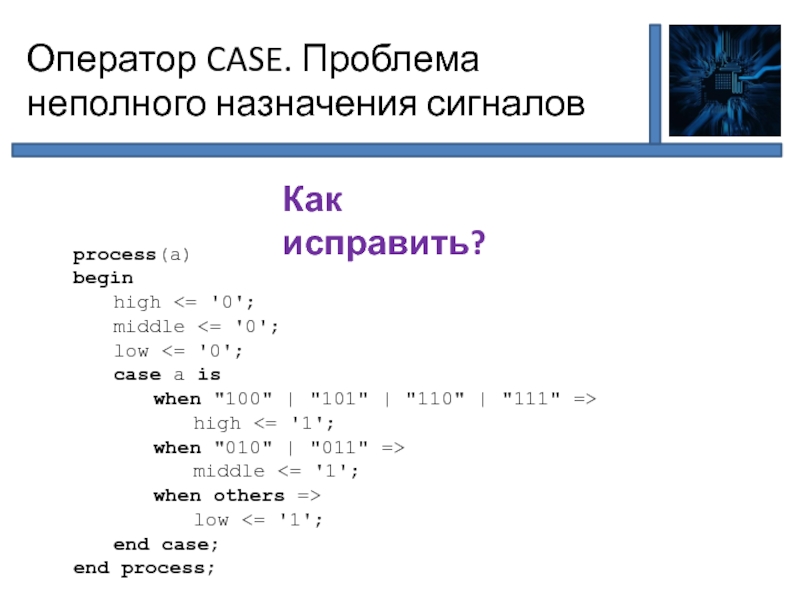

- 36. Оператор CASE. Проблема неполного назначения сигналов process(a) begin high

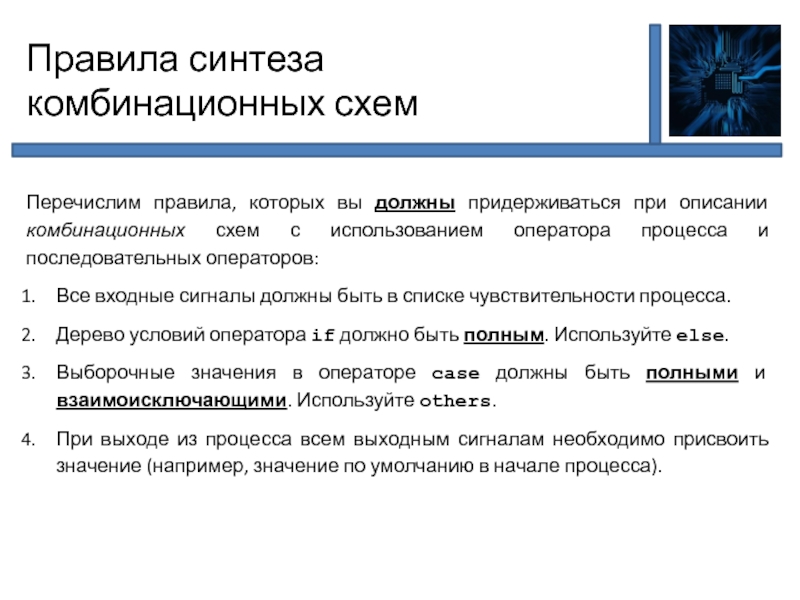

- 37. Правила синтеза комбинационных схем Перечислим

Слайд 2

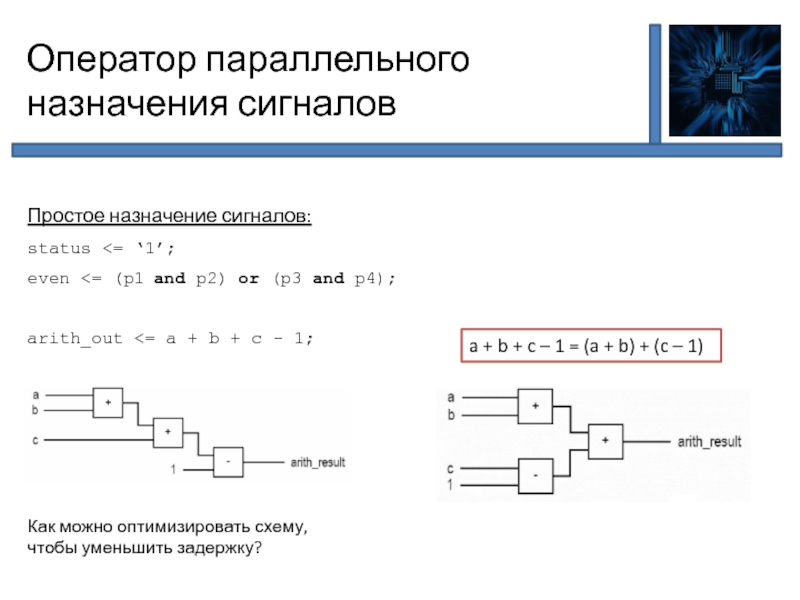

Оператор параллельного назначения сигналов

Простое назначение сигналов:

status

arith_out <= a + b + c - 1;

Как можно оптимизировать схему, чтобы уменьшить задержку?

Слайд 3

Назначение сигналов с обратной связью

Нельзя назначать сигналы с обратной связью!

q

q <= (not q and (not en)) or (d and en); -- осцилляции q при en=‘0’

architecture right_arch of right_entity is

signal q: std_logic_vector(3 downto 0);

begin

q <= ('0' & q(3 downto 1)) and d;

....

end right_arch;

architecture right_arch of right_entity is

signal q: std_logic_vector(3 downto 0);

begin

q(3) <= '0' and d(3);

q(2) <= q(3) and d(2);

q(1) <= q(2) and d(1);

q(0) <= q(1) and d(0);

....

end right_arch;

С другой стороны, код справа корректен:

Он эквивалентен следующему коду:

Слайд 4

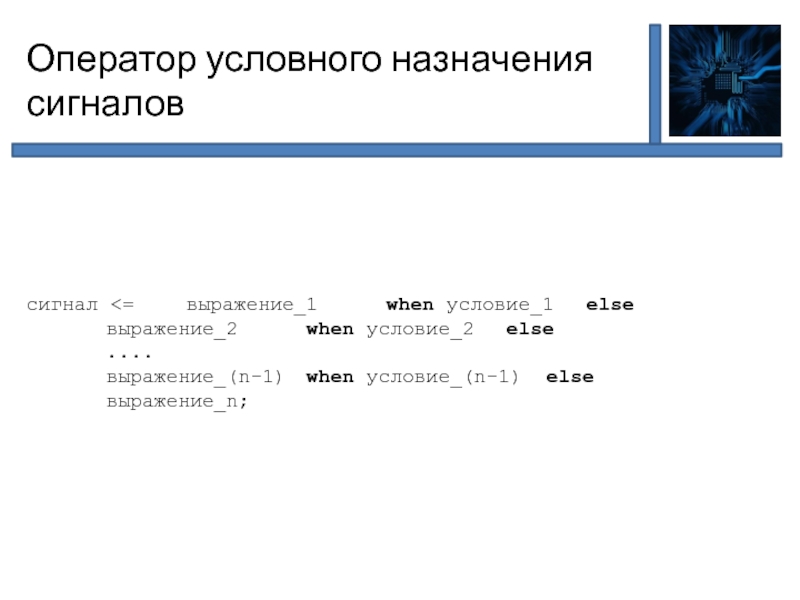

Оператор условного назначения сигналов

сигнал

....

выражение_(n-1) when условие_(n-1) else

выражение_n;

Слайд 5

Пример 1. Мультиплексор 8 бит 4-в-1

library ieee;

use ieee.std_logic_1164.all;

entity mux4 is

port(

a, b,

s: in std_logic_vector(1 downto 0);

x: out std_logic_vector(7 downto 0)

);

end mux4;

architecture cond_arch of mux4 is

begin

x <= a when (s = "00") else

b when (s = "01") else

c when (s = "10") else

d;

end cond_arch;

Слайд 6

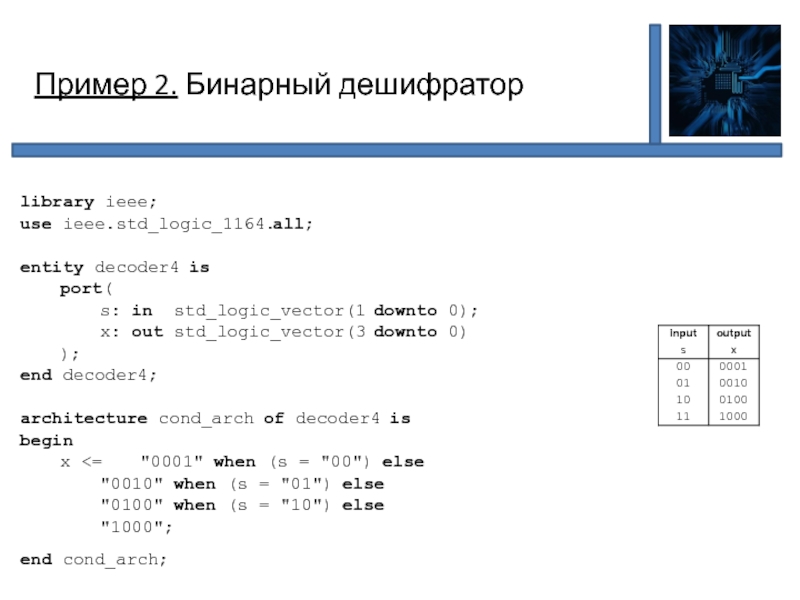

Пример 2. Бинарный дешифратор

library ieee;

use ieee.std_logic_1164.all;

entity decoder4 is

port(

s: in std_logic_vector(1 downto

x: out std_logic_vector(3 downto 0)

);

end decoder4;

architecture cond_arch of decoder4 is

begin

x <= "0001" when (s = "00") else

"0010" when (s = "01") else

"0100" when (s = "10") else

"1000";

end cond_arch;

Слайд 7

Пример 3. Шифратор приоритета

library ieee;

use ieee.std_logic_1164.all;

entity prio_encoder42 is

port(

r: in std_logic_vector(3 downto

code: out std_logic_vector(1 downto 0);

active: out std_logic

);

end prio_encoder42;

architecture cond_arch of prio_encoder42 is

begin

code <= "11" when (r(3) = '1') else

"10" when (r(2) = '1') else

"01" when (r(1) = '1') else

"00";

active <= r(3) or r(2) or r(1) or r(0);

end cond_arch;

Слайд 8

Семантика оператора условного назначения сигнала подразумевает создание приоритетной схемы, т.е. условия,

При синтезе этого оператора реализуются три схемы:

Схема, определяющая возможные значения выходного сигнала.

Схема, вычисляющая условия.

Схема определения приоритета.

Синтез оператора условного назначения сигналов

сигнал <= выражение_1 when условие_1 else

выражение_2 when условие_2 else

....

выражение_(n-1) when условие_(n-1) else

выражение_n;

Слайд 9

Одноуровневая схема приоритета

i1, i2, o – n-битные шины

sel – boolean

Реализуется на основе абстрактного мультиплексора 2-в-1:

Слайд 11

Трехуровневая схема приоритета

Например, мультиплексор 4-в-1 может быть реализован следующим образом:

Слайд 12

Оператор выборочного назначения сигналов

Выборочные значения должны быть взаимно исключающими (значения не

Параллельный оператор:

with задающее_выражение select

сигнал <=

выражение_1 when выбор_1,

выражение_2 when выбор_2,

выражение_3 when выбор_3,

...

выражение_n when выбор_n;

Значения, не условия

others

Слайд 13

Пример 1. Мультиплексор 8 бит 4-в-1

architecture sel_arch of mux4 is

begin

with s

x <= a when "00",

b when "01",

c when "10",

d when others;

end sel_arch;

Слайд 14

Пример 2. Бинарный дешифратор

architecture sel_arch of decoder4 is

begin

with sel select

x

"0010" when "01",

"0100" when "10",

"1000" when others;

end sel_arch;

Слайд 15

Пример 3. Шифратор приоритета

architecture sel_arch of prio_encoder42 is

begin

with r select

code

"1100" | "1101" | "1110" | "1111",

"10" when "0100" | "0101" | "0110" | "0111",

"01" when "0010" | "0011",

"00" when others;

active <= r(3) or r(2) or r(1) or r(0);

end sel_arch;

Компактное перечисление вариантов

Слайд 16

Синтез оператора выборочного назначения сигналов

Мультиплексор 4-в-1.

Симметричная схема, все входы равноправны, приоритета

Абстрактный мультиплексор k-в-1.

Все входы равноправны, приоритета нет.

Слайд 17

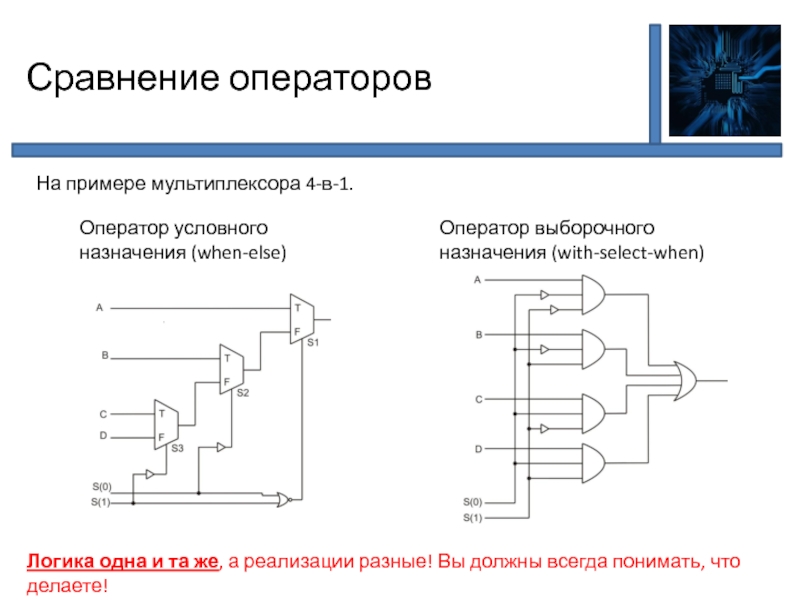

Сравнение операторов

На примере мультиплексора 4-в-1.

Оператор условного назначения (when-else)

Оператор выборочного назначения (with-select-when)

Логика

Слайд 18

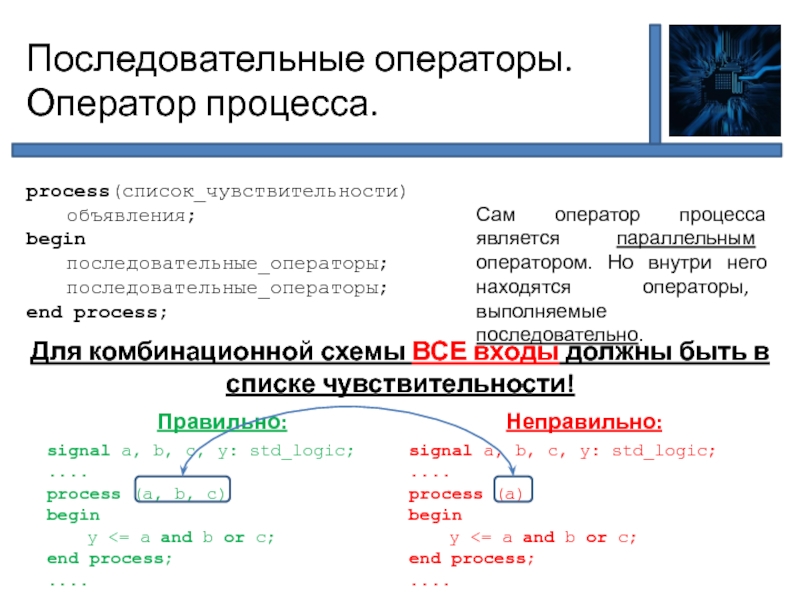

Последовательные операторы. Оператор процесса.

process(список_чувствительности)

объявления;

begin

последовательные_операторы;

последовательные_операторы;

end process;

Сам оператор процесса является параллельным оператором.

Для комбинационной схемы ВСЕ входы должны быть в списке чувствительности!

Слайд 19

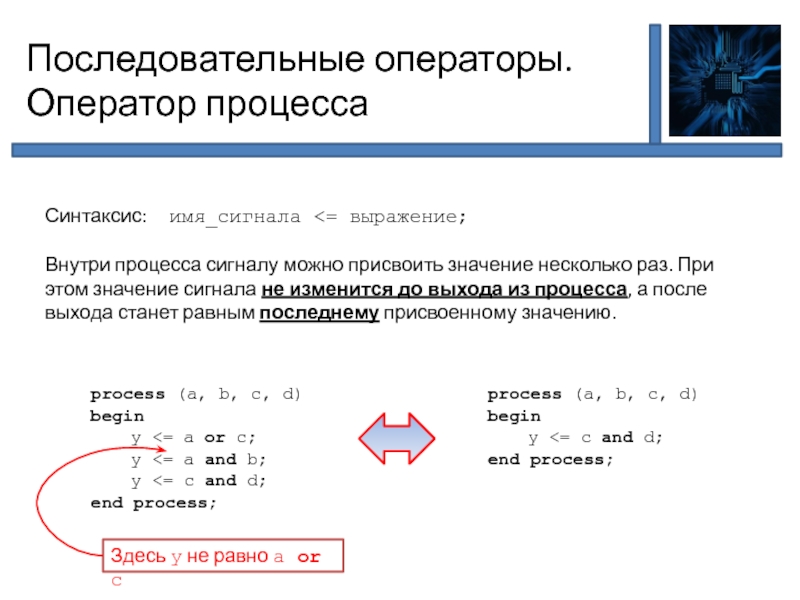

Последовательные операторы. Оператор процесса

Синтаксис: имя_сигнала

Здесь y не равно a or c

Слайд 20

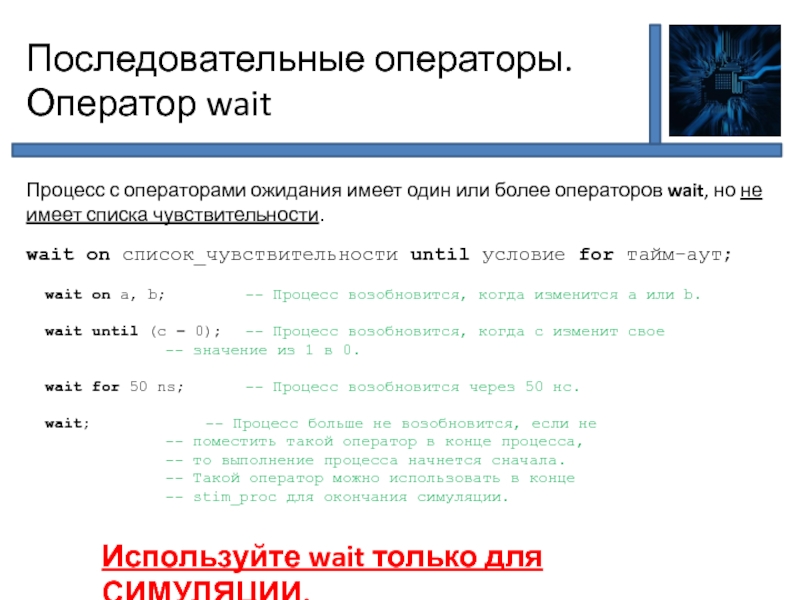

Последовательные операторы. Оператор wait

Процесс с операторами ожидания имеет один или более

wait on список_чувствительности until условие for тайм-аут;

wait on a, b; -- Процесс возобновится, когда изменится a или b.

wait until (c = 0); -- Процесс возобновится, когда c изменит свое

-- значение из 1 в 0.

wait for 50 ns; -- Процесс возобновится через 50 нс.

wait; -- Процесс больше не возобновится, если не

-- поместить такой оператор в конце процесса,

-- то выполнение процесса начнется сначала.

-- Такой оператор можно использовать в конце

-- stim_proc для окончания симуляции.

Используйте wait только для СИМУЛЯЦИИ.

Слайд 21

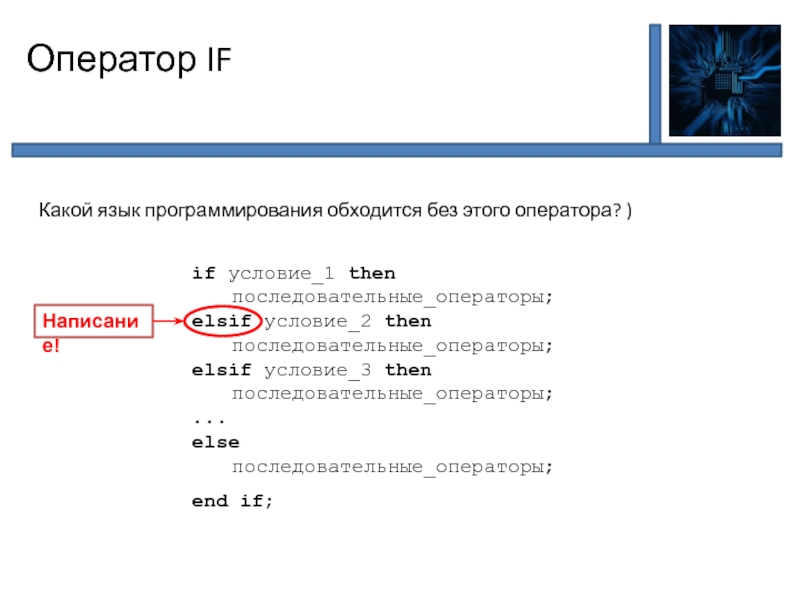

Оператор IF

Какой язык программирования обходится без этого оператора? )

if условие_1 then

последовательные_операторы;

elsif

последовательные_операторы;

elsif условие_3 then

последовательные_операторы;

...

else

последовательные_операторы;

end if;

Написание!

Слайд 22

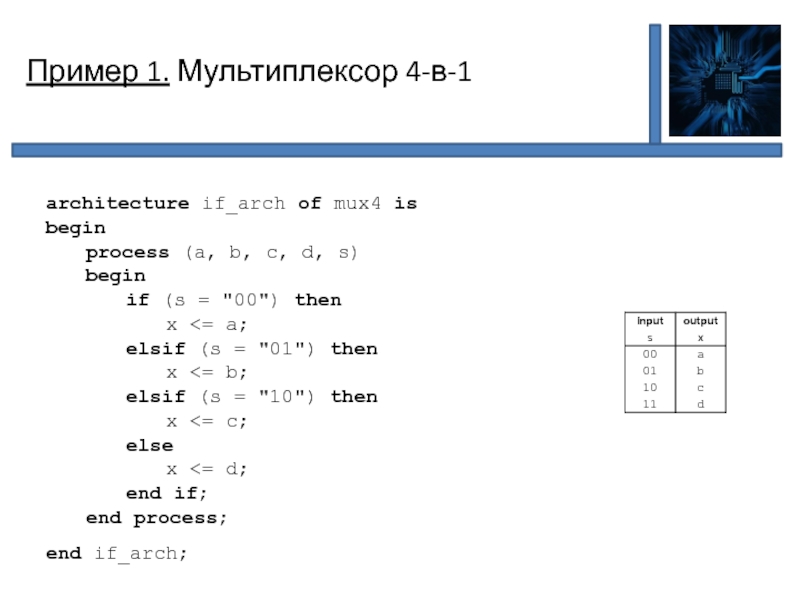

Пример 1. Мультиплексор 4-в-1

architecture if_arch of mux4 is

begin

process (a, b, c,

begin

if (s = "00") then

x <= a;

elsif (s = "01") then

x <= b;

elsif (s = "10") then

x <= c;

else

x <= d;

end if;

end process;

end if_arch;

Слайд 23

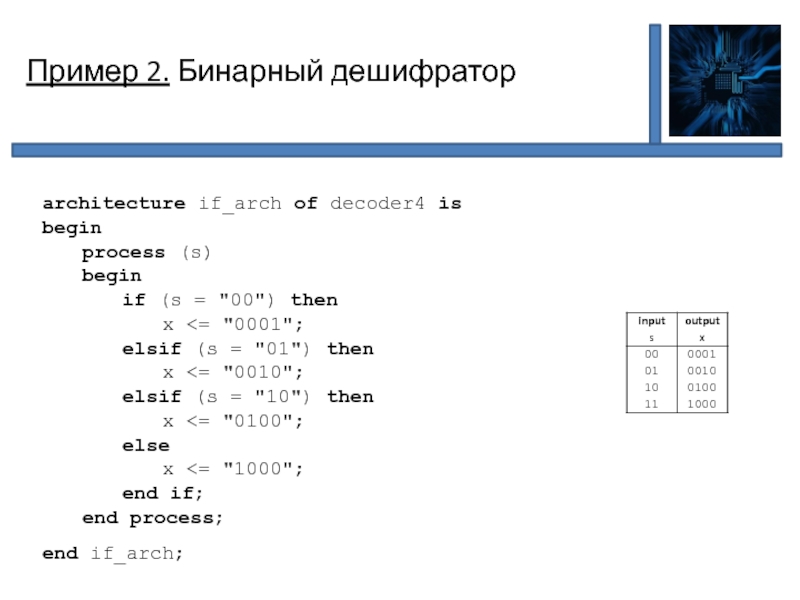

Пример 2. Бинарный дешифратор

architecture if_arch of decoder4 is

begin

process (s)

begin

if (s =

x <= "0001";

elsif (s = "01") then

x <= "0010";

elsif (s = "10") then

x <= "0100";

else

x <= "1000";

end if;

end process;

end if_arch;

Слайд 24

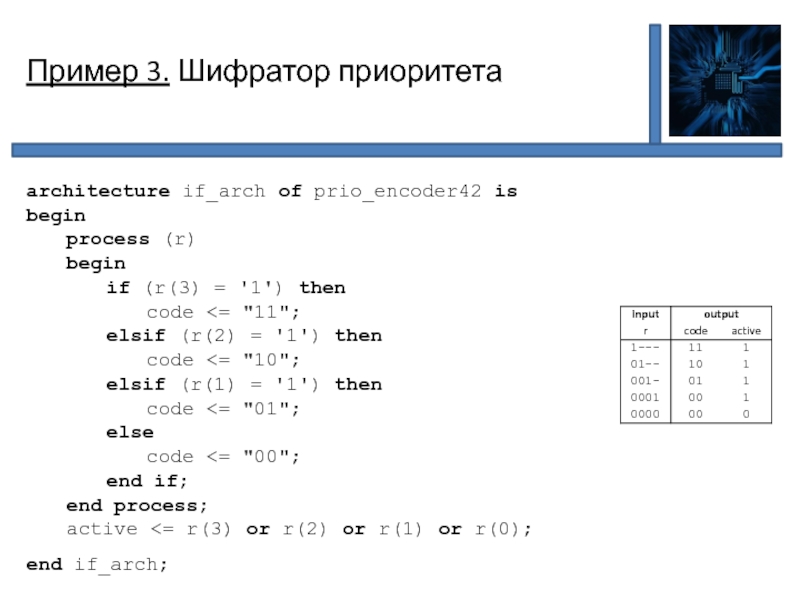

Пример 3. Шифратор приоритета

architecture if_arch of prio_encoder42 is

begin

process (r)

begin

if (r(3) =

code <= "11";

elsif (r(2) = '1') then

code <= "10";

elsif (r(1) = '1') then

code <= "01";

else

code <= "00";

end if;

end process;

active <= r(3) or r(2) or r(1) or r(0);

end if_arch;

Слайд 25

Оператор IF. Сравнение с оператором условного назначения

Для простых случаев полностью совпадает

Отличия:

По структуре. Внутри IF может быть еще один IF.

По пониманию: легче понять смысл.

В одной ветке можно назначить несколько сигналов.

сигнал <= выражение_1 when условие_1 else

выражение_2 when условие_2 else

....

выражение_n;

process(...)

begin

if условие_1 then

сигнал <= выражение_1;

elsif условие_2 then

сигнал <= выражение_2;

...

else

сигнал <= выражение_n;

end if;

end process;

Слайд 26

Проблема неполного дерева условий оператора IF

Пример неправильного использования оператора IF:

process(a,b)

begin

if (a

eq <= '1';

end if;

end process;

process(a,b)

begin

if (a = b) then

eq <= '1';

else

eq <= eq;

end if;

end process;

Семантика VHDL такова, что если сигнал не обновляется (при a /= b), то он сохраняет свое значение. Это приводит к образованию обратной связи и элемента памяти (защелки (latch)).

Слайд 27

Проблема неполного дерева условий оператора IF

Правильно:

Для описания комбинационной цепи необходимо всегда

process(a,b)

begin

if (a = b) then

eq <= '1';

else

eq <= '0';

end if;

end process;

Слайд 28

В общем случае оператор IF имеет несколько веток. Возможно, что сигналу

Проблема неполного назначения сигналов в операторе IF

Пример: компаратора двух чисел с тремя выходами: gt (greater than, a > b), lt (less than, a < b), eq (equal a=b).

process(a,b)

begin

if (a > b) then

gt <= '1';

elsif (a = b) then

eq <= '1';

else

lt <= '1';

end if;

end process;

Неправильно:

Слайд 29

Правильно:

Проблема неполного назначения сигналов в операторе IF

process(a,b)

begin

gt

if (a > b) then

gt <= '1';

elsif (a = b) then

eq <= '1';

else

lt <= '1';

end if;

end process;

process(a,b)

begin

if (a > b) then

gt <= '1';

eq <= '0';

lt <= '0';

elsif (a = b) then

gt <= '0';

eq <= '1';

lt <= '0';

else

gt <= '0';

eq <= '0';

lt <= '1';

end if;

end process;

Присвоение значения комбинационному сигналу по умолчанию

Слайд 30

Оператор CASE

Выборочные значения должны быть полными и взаимоисключающими.

case задающее_выражение is

when выбор_1

последовательные_операторы;

when выбор_2 =>

последовательные_операторы;

...

when выбор_n =>

последовательные_операторы;

end case;

Слайд 31

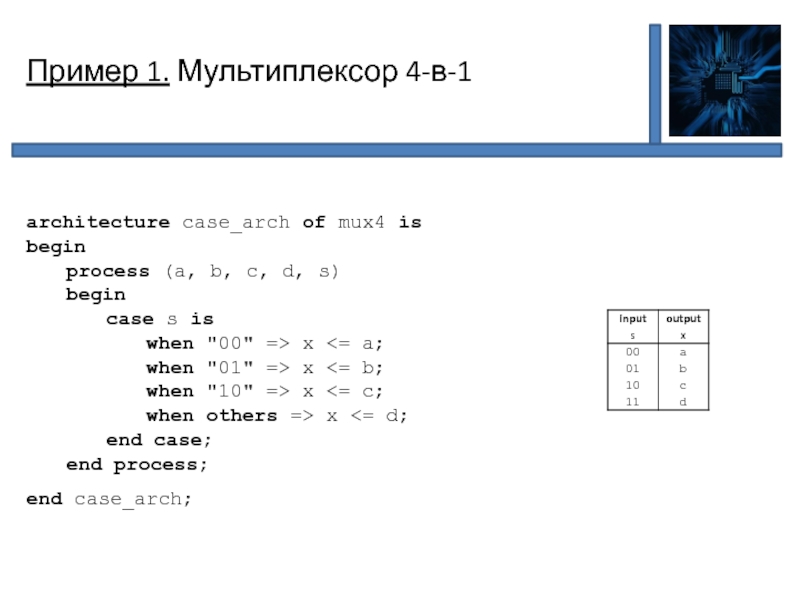

Пример 1. Мультиплексор 4-в-1

architecture case_arch of mux4 is

begin

process (a, b, c,

begin

case s is

when "00" => x <= a;

when "01" => x <= b;

when "10" => x <= c;

when others => x <= d;

end case;

end process;

end case_arch;

Слайд 32

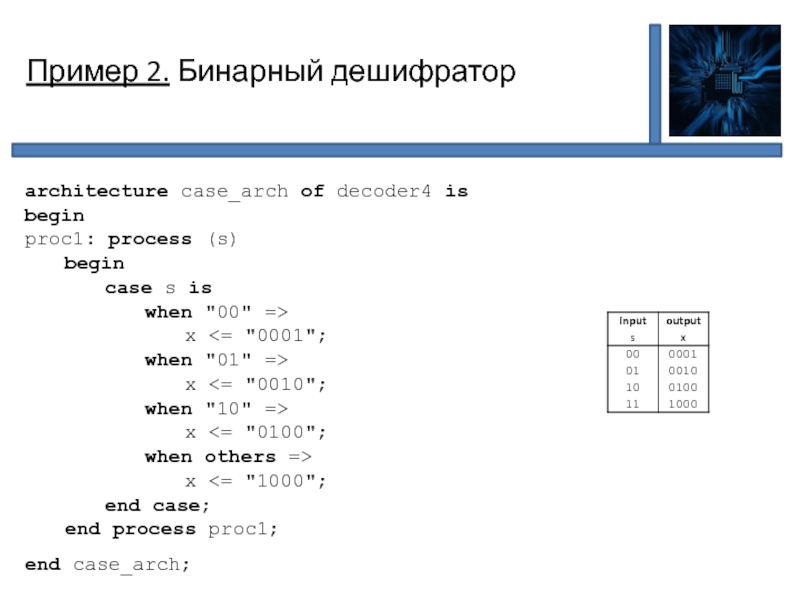

Пример 2. Бинарный дешифратор

architecture case_arch of decoder4 is

begin

proc1: process (s)

begin

case s

when "00" =>

x <= "0001";

when "01" =>

x <= "0010";

when "10" =>

x <= "0100";

when others =>

x <= "1000";

end case;

end process proc1;

end case_arch;

Слайд 33

Пример 3. Шифратор приоритета

architecture case_arch of prio_encoder42 is

begin

process (r)

begin

case r is

when

"1100" | "1101" | "1110" | "1111" =>

code <= "11";

when "0100" | "0101" | "0110" | "0111" =>

code <= "10";

when "0010" | "0011" =>

code <= "01";

when others =>

code <= "00";

end case;

end process;

active <= r(3) or r(2) or r(1) or r(0);

end case_arch;

Слайд 34

Оператор CASE. Сравнение с оператором выборочного назначения

with задающее_выражение select

сигнал

выражение_2 when выбор_2,

...

выражение_n when выбор_n;

process(...)

begin

case задающее_выражение is

when выбор_1 => сигнал <= выражение_1;

when выбор_2 => сигнал <= выражение_2;

...

when выбор_n => сигнал <= выражение_n;

end case;

end process;

Слайд 35

Оператор CASE. Проблема неполного назначения сигналов

Рассмотрим простой шифратор приоритета:

Подразумевается, что в

process(a)

begin

case a is

when "100" | "101" | "110" | "111" =>

high <= '1';

when "010" | "011" =>

middle <= '1';

when others =>

low <= '1';

end case;

end process;

Слайд 36

Оператор CASE. Проблема неполного назначения сигналов

process(a)

begin

high

case a is

when "100" | "101" | "110" | "111" =>

high <= '1';

when "010" | "011" =>

middle <= '1';

when others =>

low <= '1';

end case;

end process;

Как исправить?

Слайд 37

Правила синтеза комбинационных схем

Перечислим правила, которых вы должны придерживаться при описании

Все входные сигналы должны быть в списке чувствительности процесса.

Дерево условий оператора if должно быть полным. Используйте else.

Выборочные значения в операторе case должны быть полными и взаимоисключающими. Используйте others.

При выходе из процесса всем выходным сигналам необходимо присвоить значение (например, значение по умолчанию в начале процесса).

x" alt="">

x" alt="">