- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

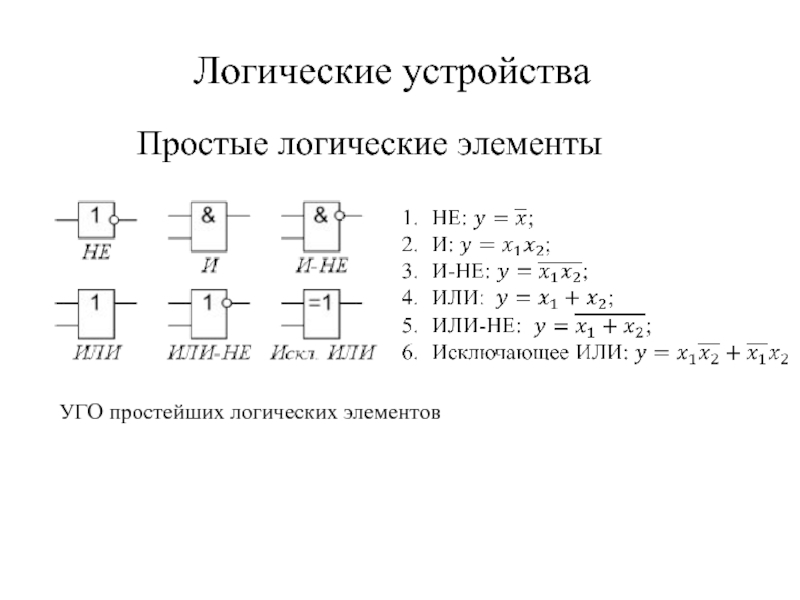

Логические устройства. Простые логические элементы презентация

Содержание

- 1. Логические устройства. Простые логические элементы

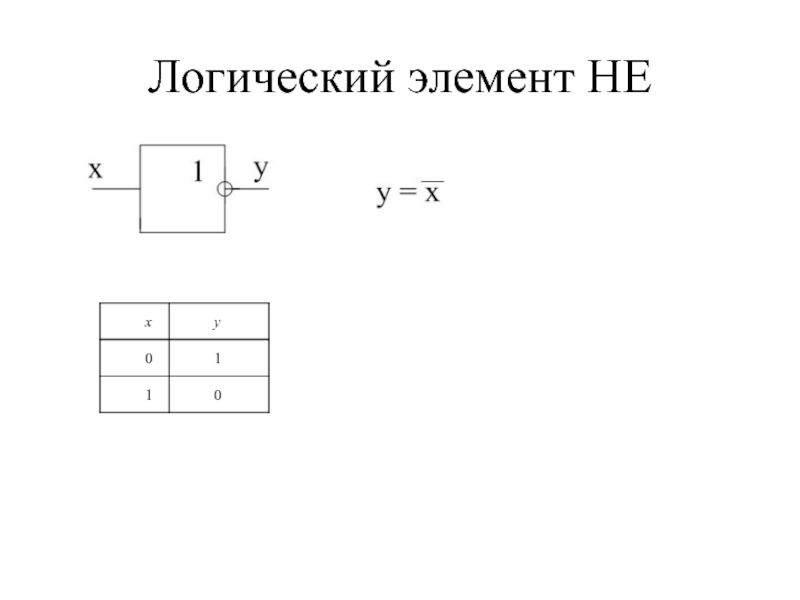

- 2. Логический элемент НЕ

- 3. Логический элемент И

- 4. Сложные логические элементы 2-2И-2ИЛИ y=x1x2+x3x4

- 6. Комбинационные логические устройства Дешифратор и шифратор. Мультиплексор и демультиплексор. Полусумматор и сумматор. Арифметико-логическое устройство.

- 7. Дешифраторы Дешифраторы осуществляют преобразование входного двоичного

- 9. Линейный дешифратор Схема такого дешифратора строится на

- 11. Шифраторы Шифраторы, в отличие от дешифраторов,

- 12. Демультиплексоры и мультиплексоры Демультиплексор используется в

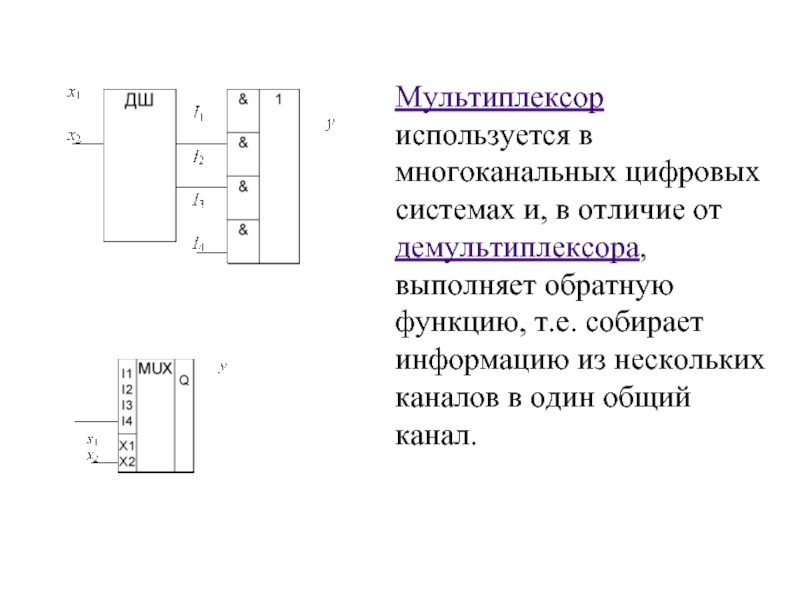

- 13. Мультиплексор используется в многоканальных цифровых системах

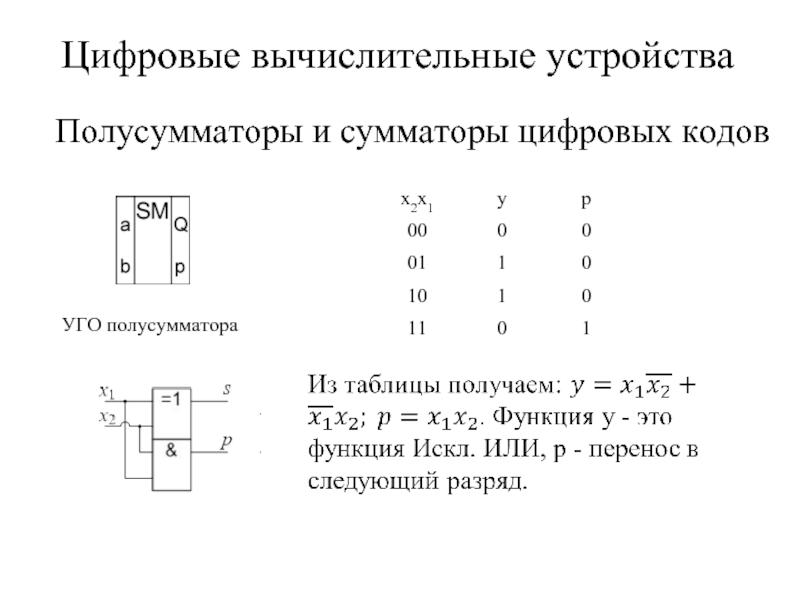

- 14. Цифровые вычислительные устройства Полусумматоры и сумматоры цифровых кодов УГО полусумматора

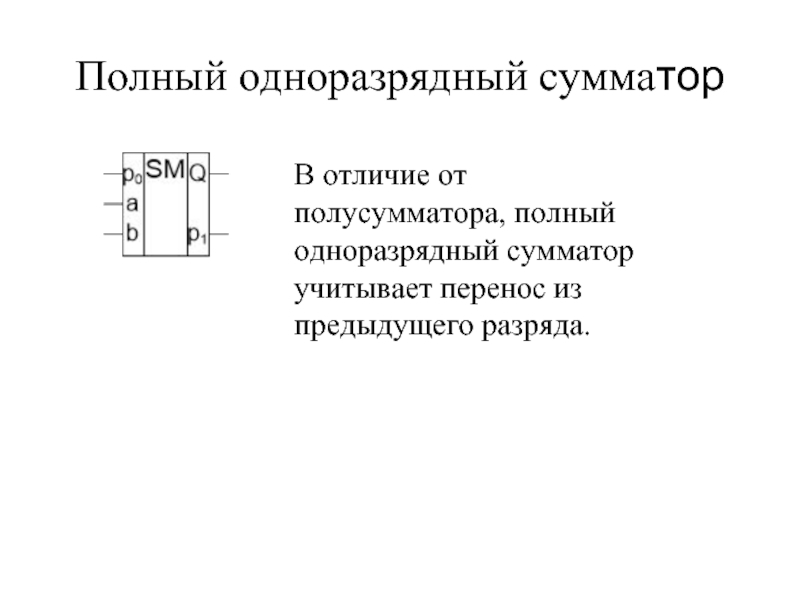

- 15. Полный одноразрядный сумматор В отличие от полусумматора, полный одноразрядный сумматор учитывает перенос из предыдущего разряда.

- 16. Многоразрядные сумматоры Многоразрядный сумматор предназначен для суммирования

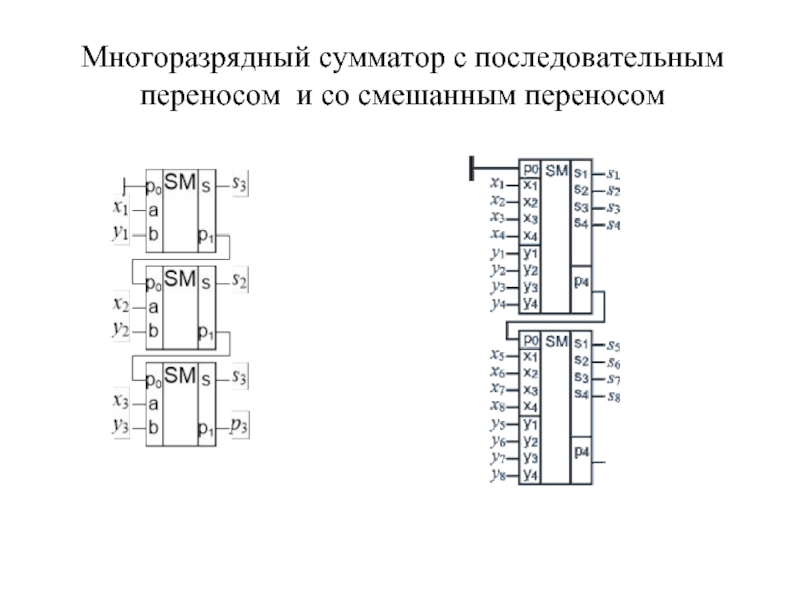

- 17. Многоразрядный сумматор с последовательным переносом и cо смешанным переносом

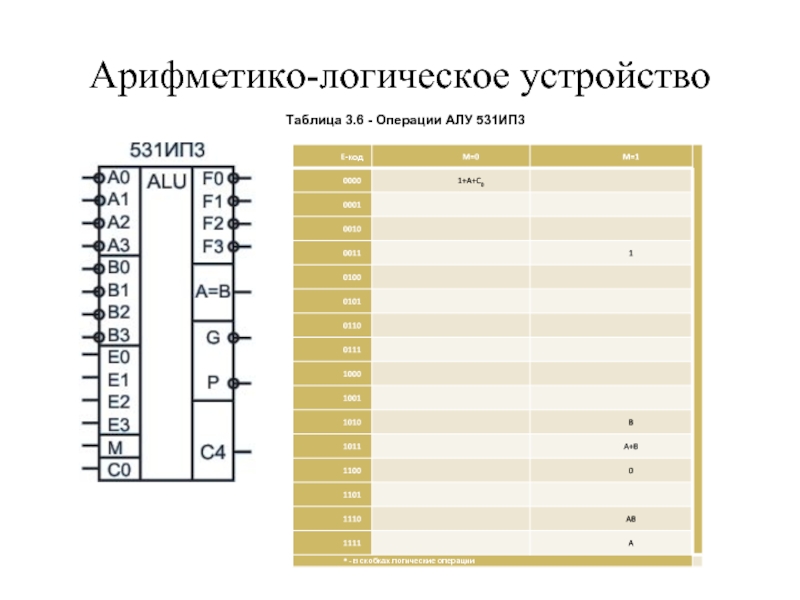

- 18. Арифметико-логическое устройство Таблица 3.6 - Операции АЛУ 531ИП3

- 19. Тактируемые цифровые устройства Цифровые запоминающие устройства Триггеры

- 20. Асинхронные триггеры RS-триггер. Этот триггер является

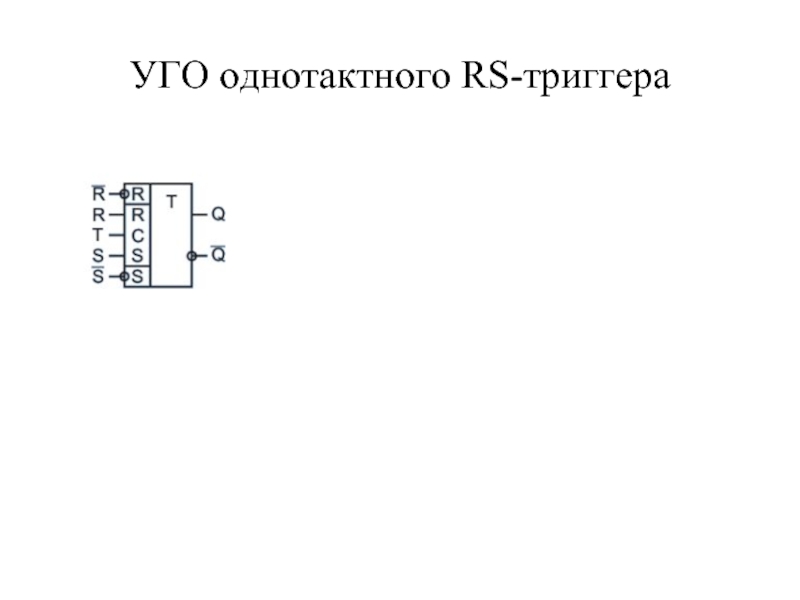

- 22. Синхронные триггеры RS-триггер Однотактный RS триггер (слева) и его временные диаграммы (справа)

- 23. УГО однотактного RS-триггера

- 24. Триггер D-типа а) б) в) Однотактный D-триггер

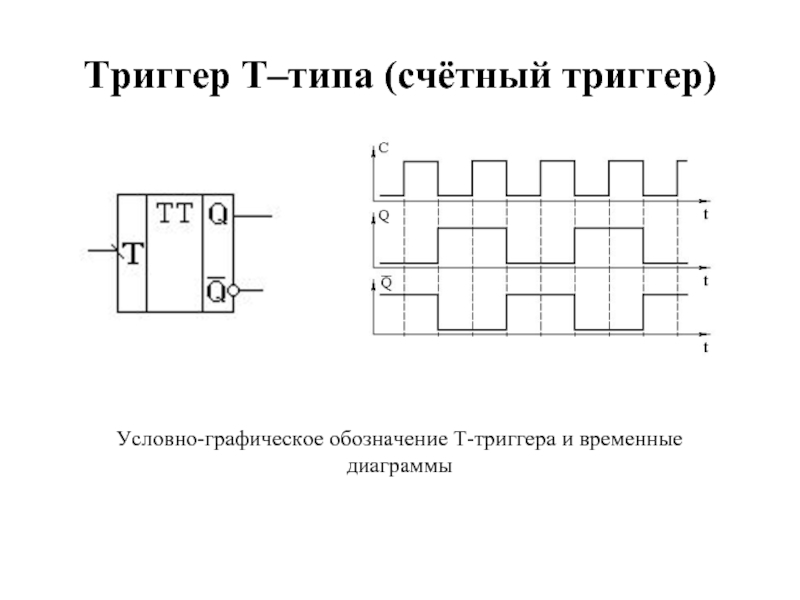

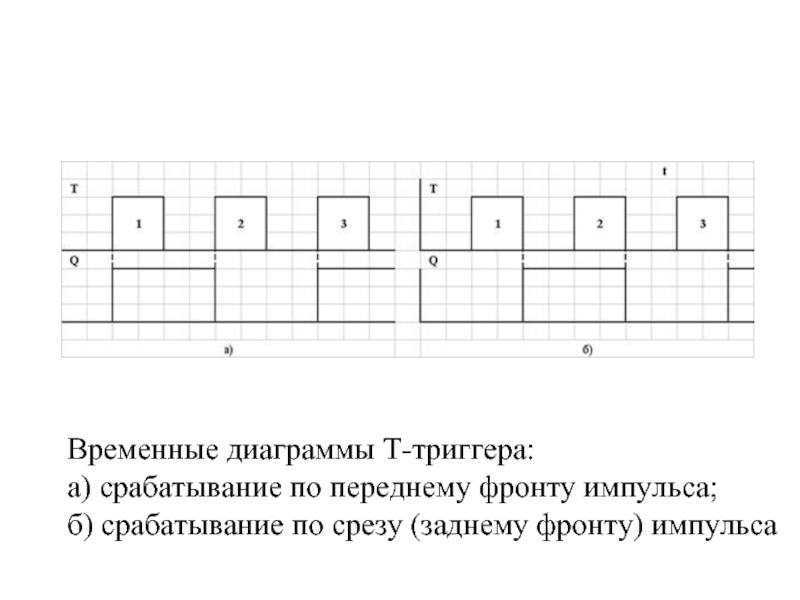

- 25. Триггер T–типа (счётный триггер) Условно-графическое обозначение T-триггера и временные диаграммы

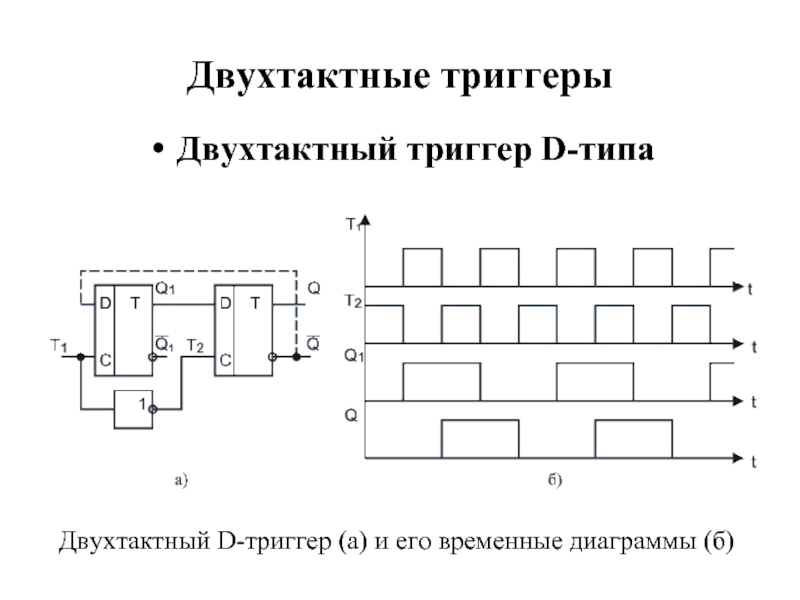

- 26. Двухтактные триггеры Двухтактный триггер D-типа Двухтактный D-триггер (а) и его временные диаграммы (б)

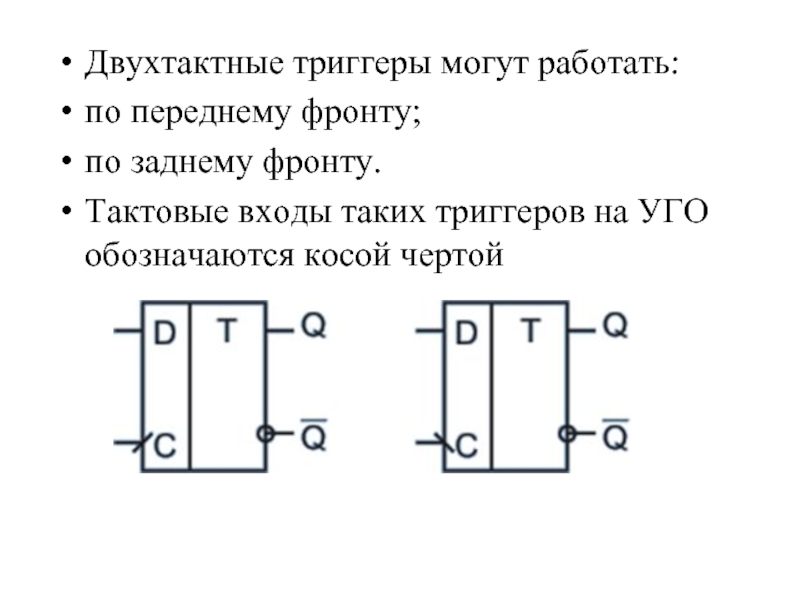

- 27. Двухтактные триггеры могут работать: по переднему

- 28. Временные диаграммы Т-триггера: а) срабатывание

- 29. Регистры Регистрами называются многоразрядные цифровые запоминающие

- 30. Регистры делятся на: 1. параллельные; 2. последовательные; 3.параллельно-последовательные.

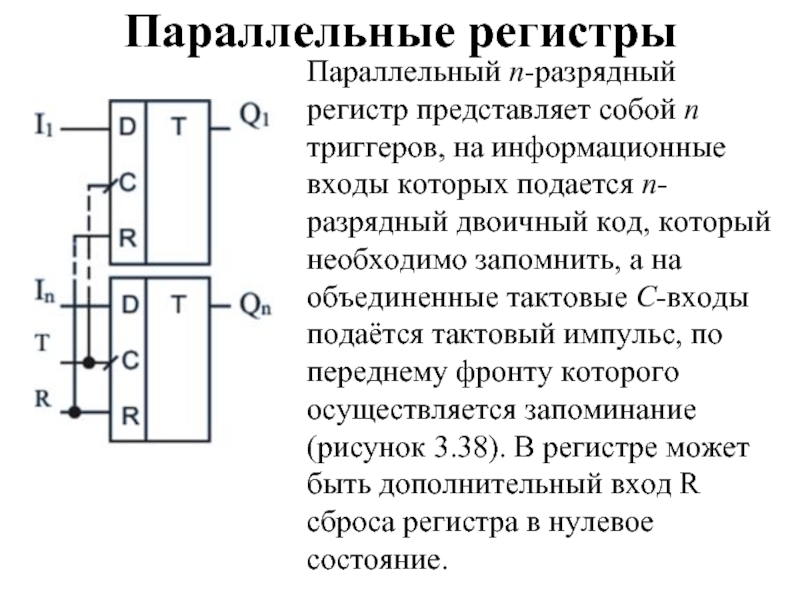

- 31. Параллельные регистры Параллельный n-разрядный регистр представляет собой

- 32. Параллельные регистры Параллельный n-разрядный регистр представляет собой

- 33. Последовательные регистры Последовательные регистры работают с последовательным

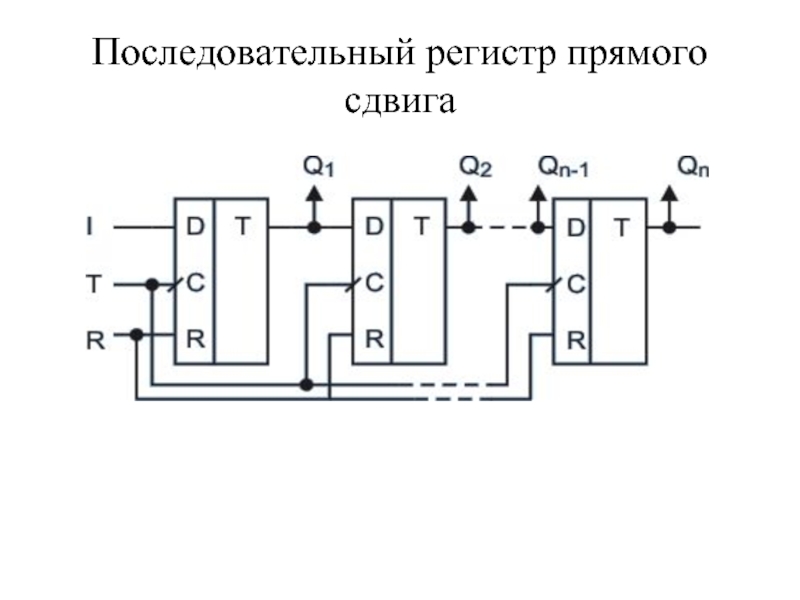

- 34. Последовательный регистр прямого сдвига

- 35. Регистры прямого сдвига осуществляют приём (передачу) информации,

- 36. Реверсивный регистр Вход V управляет направлением сдвига

- 37. Реверсивный сдвиговый регистр позволяет осуществить сдвиг информации

- 38. Параллельно-последовательные регистры Такие регистры служат для преобразования

- 39. Параллельно-последовательные регистры Параллельно-последовательный регистр

- 40. Параллельно-последовательные регистры При V=0 организуется режим параллельного

- 41. Счётчики импульсов Счетчиком называется устройство, предназначенное для

- 42. К основным характеристикам счетчиков относятся модуль счета

- 43. Асинхронные счётчики импульсов Асинхронный счетчик импульсов представляет

- 44. Суммирующие асинхронные счётчики Коэффициент пересчета

- 45. Суммирующие асинхронные счётчики

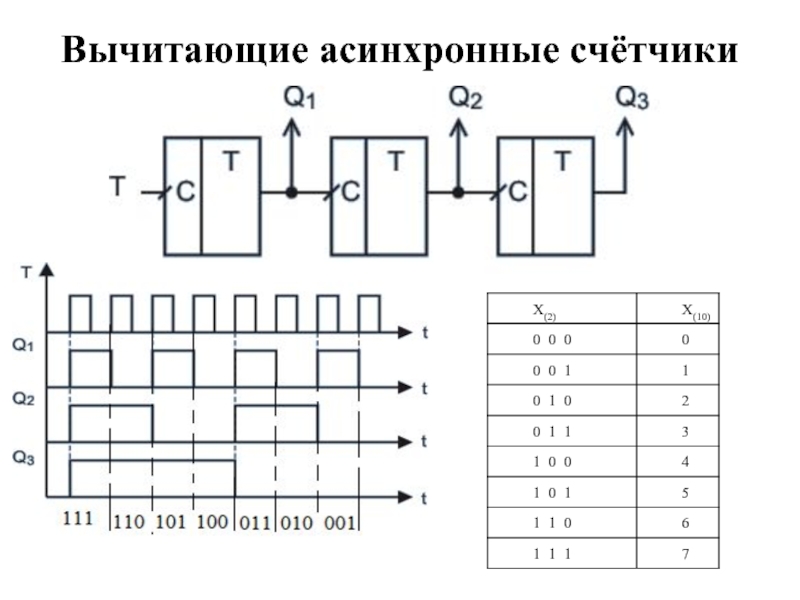

- 46. Вычитающие асинхронные счётчики

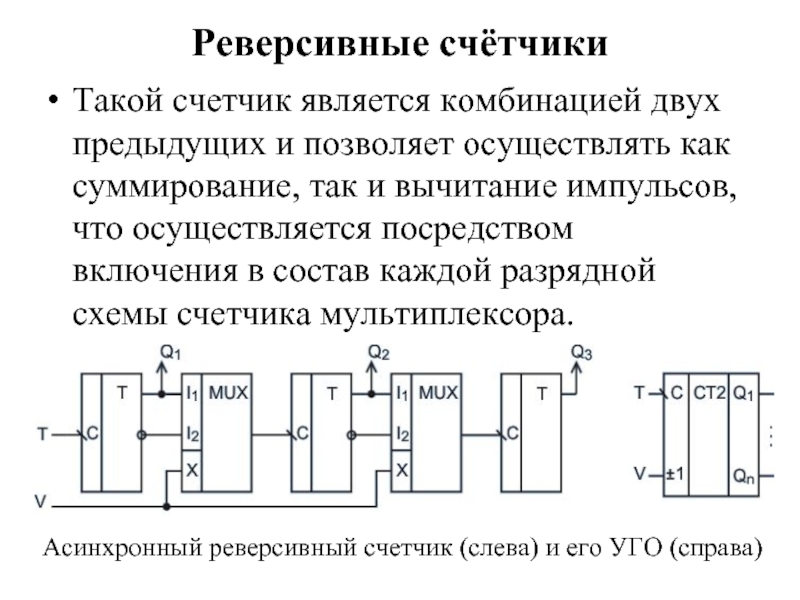

- 47. Реверсивные счётчики Такой счетчик является комбинацией двух

- 48. Реверсивные счётчики Сигнал на входе V определяет

- 49. Асинхронные счётчики с произвольным коэффициентом пересчёта В

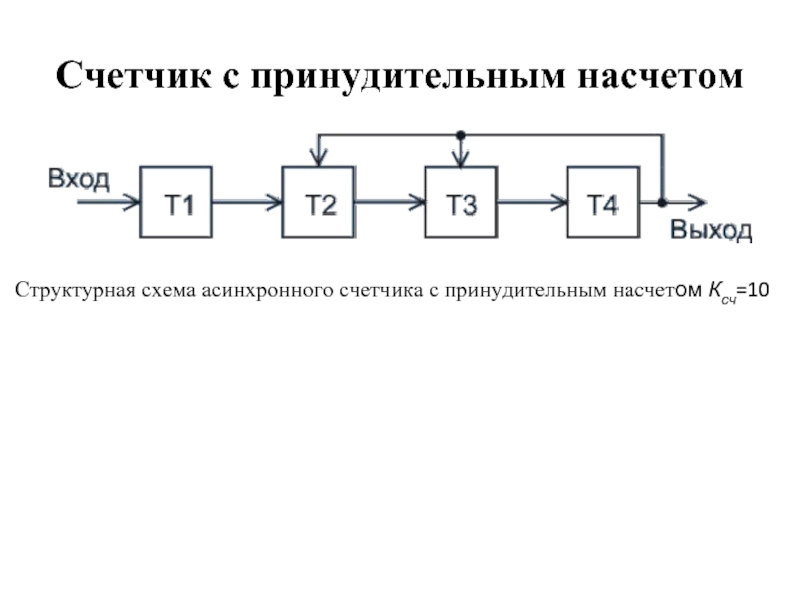

- 50. Счетчик с принудительным насчетом Структурная схема асинхронного счетчика с принудительным насчетом Ксч=10

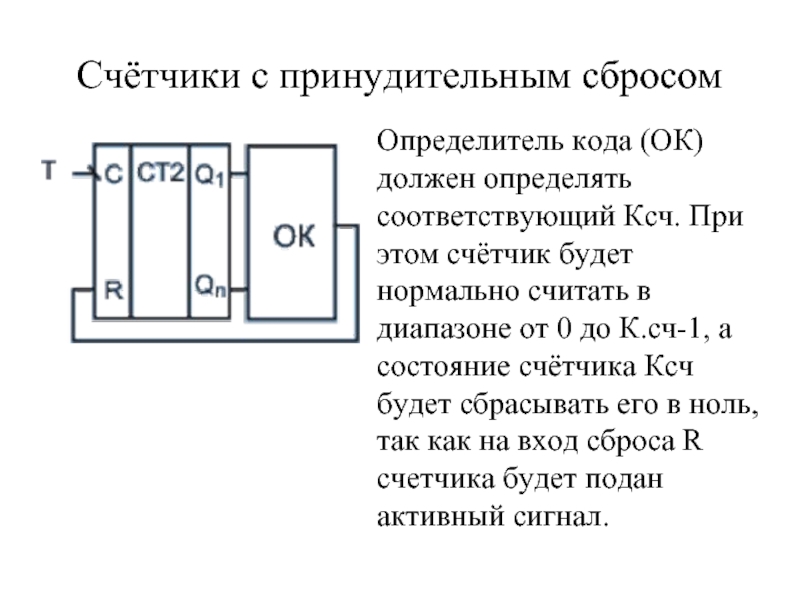

- 51. Счётчики с принудительным сбросом Определитель кода (ОК)

- 52. Счетчики с переносом Такие счётчики делятся на

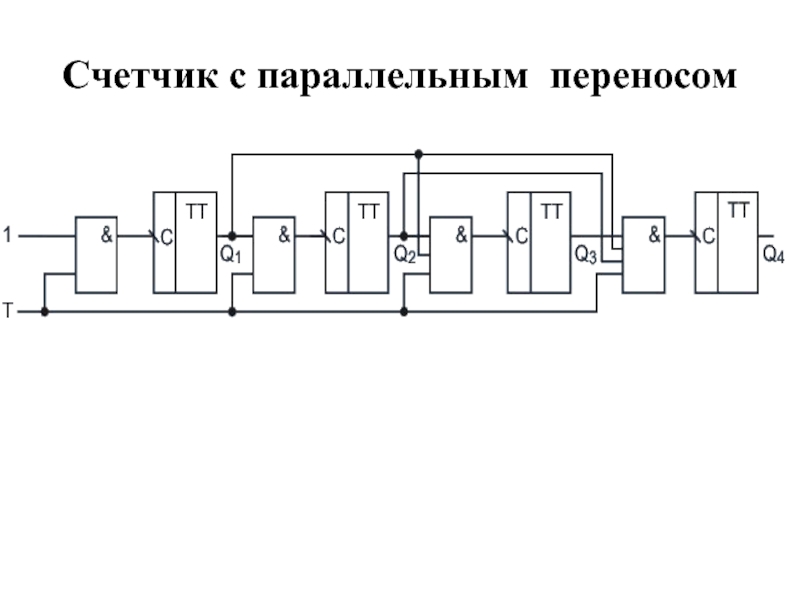

- 53. Счетчик с параллельным переносом

- 54. Счётчик с последовательным переносом

- 55. Счётчик с последовательным переносом Счетчик с параллельным переносом

- 56. Счетчики с комбинированным переносом Идея построения счетчиков

- 57. Счётчики с произвольным коэффициентом пересчёта Функциональная схема дешифратора (определителя) выходного кода счетчика

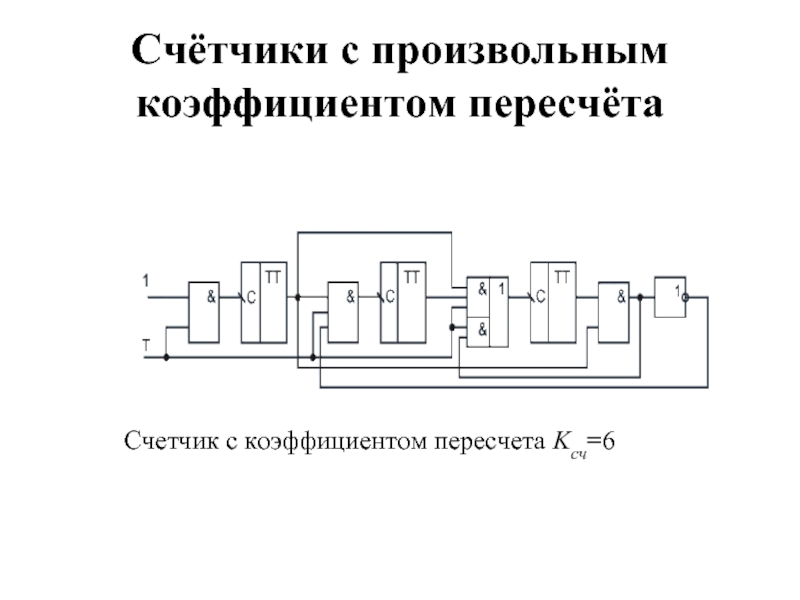

- 58. Счётчики с произвольным коэффициентом пересчёта Счетчик с коэффициентом пересчета Kсч=6

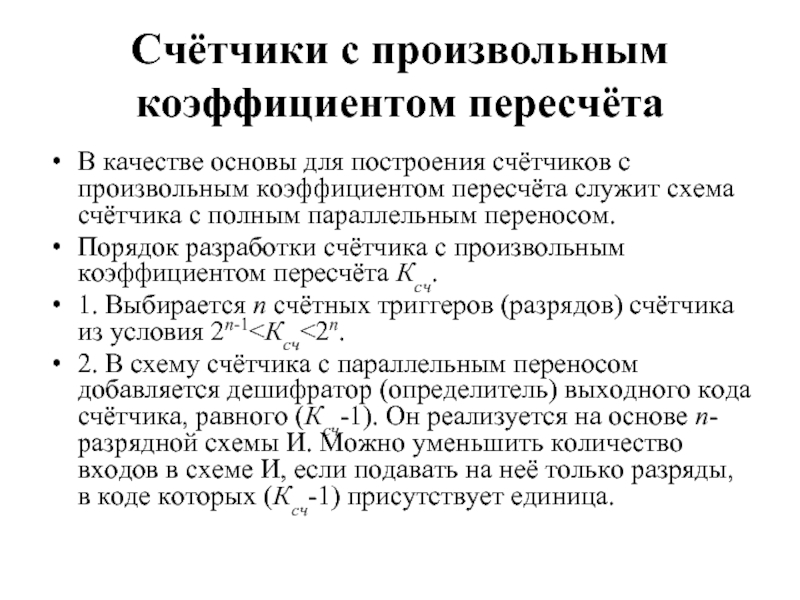

- 59. Счётчики с произвольным коэффициентом пересчёта В качестве

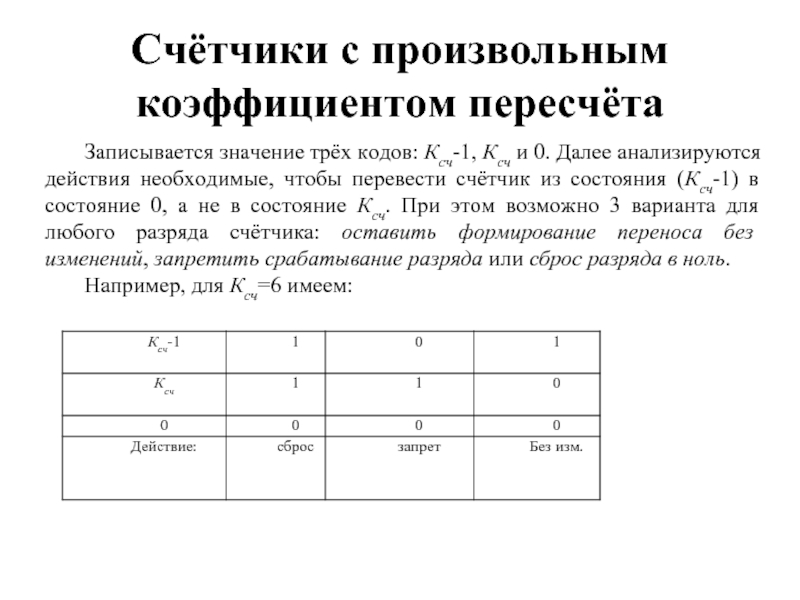

- 60. Счётчики с произвольным коэффициентом пересчёта Записывается значение

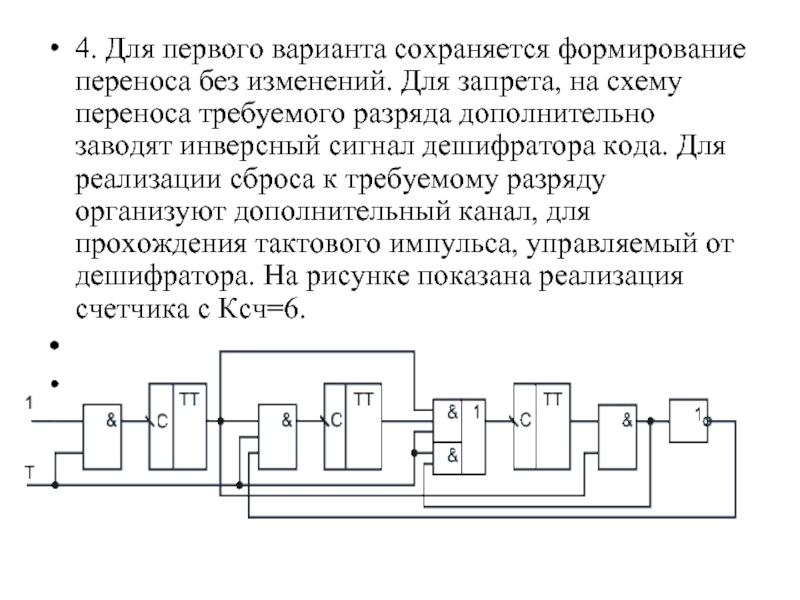

- 61. 4. Для первого варианта сохраняется формирование переноса

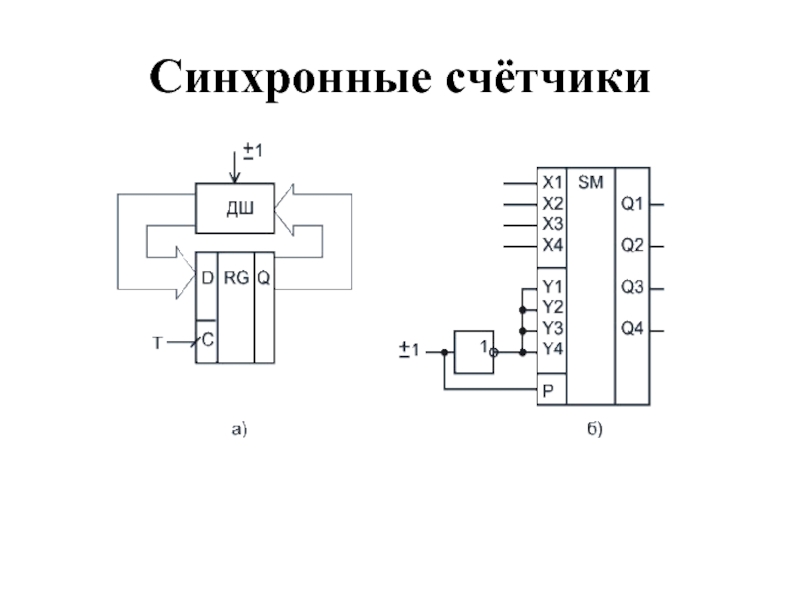

- 62. Синхронные счётчики

- 63. Минимизация логических функций Карта Вейча – это

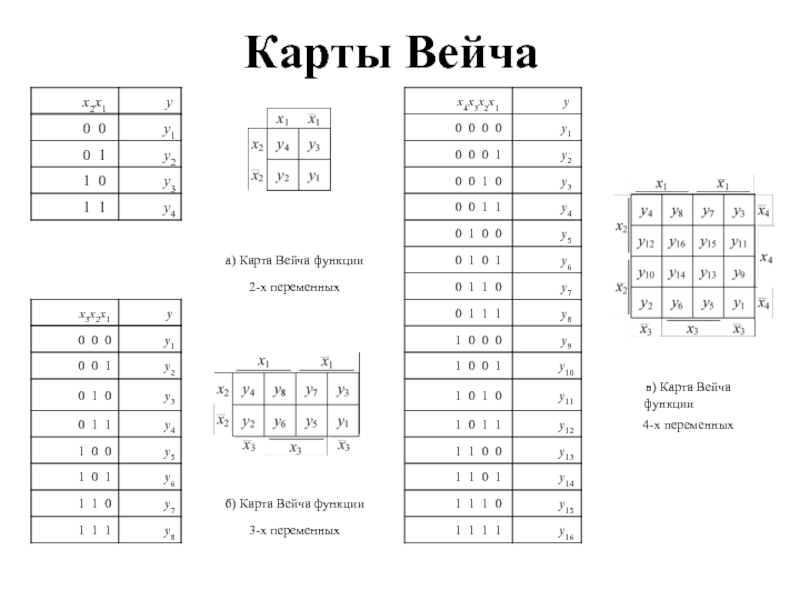

- 64. Карты Вейча

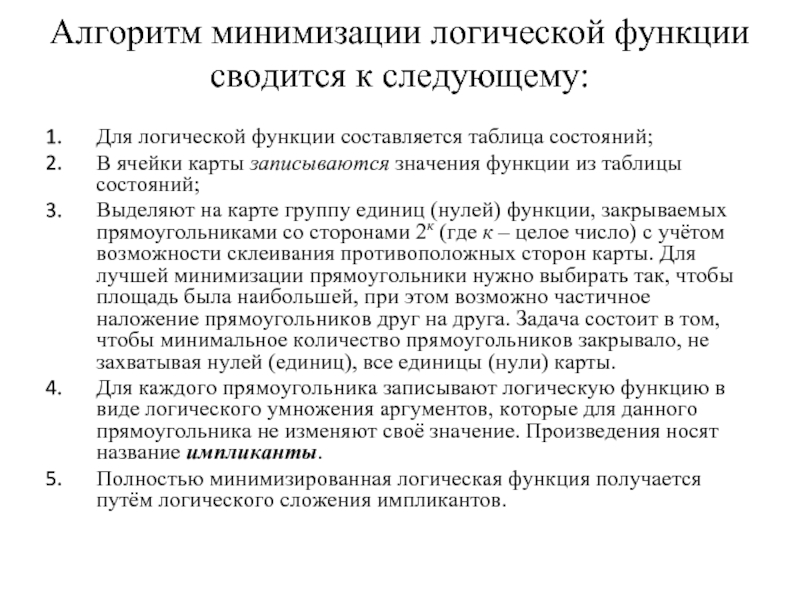

- 65. Алгоритм минимизации логической функции сводится к следующему:

Слайд 6Комбинационные логические устройства

Дешифратор и шифратор.

Мультиплексор и демультиплексор.

Полусумматор и сумматор.

Арифметико-логическое устройство.

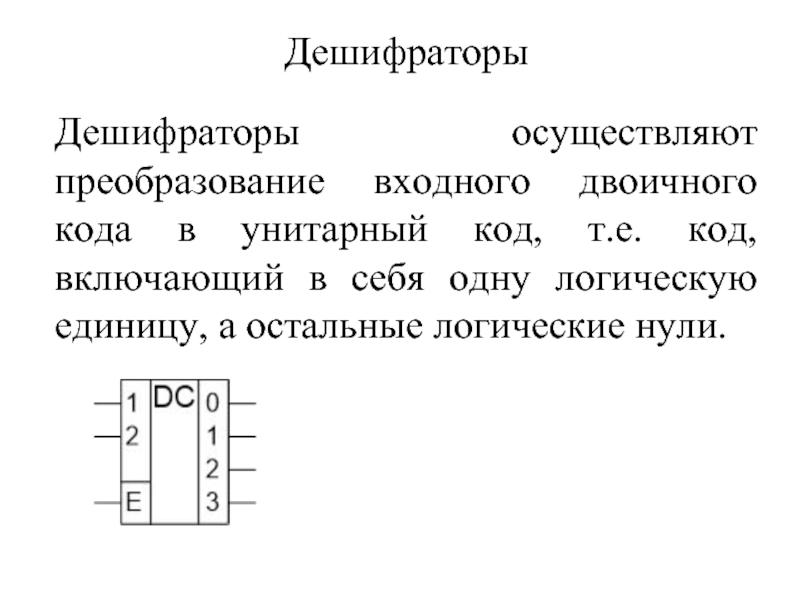

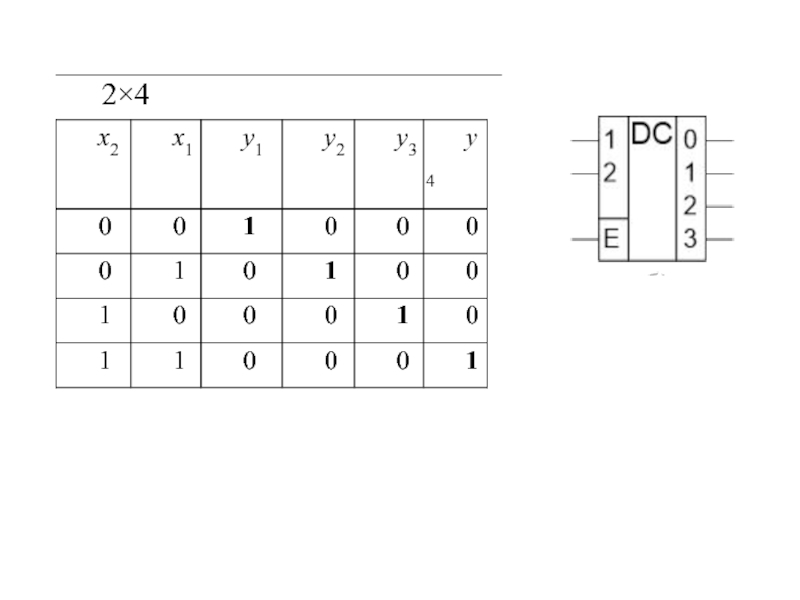

Слайд 7Дешифраторы

Дешифраторы осуществляют преобразование входного двоичного кода в унитарный код, т.е. код,

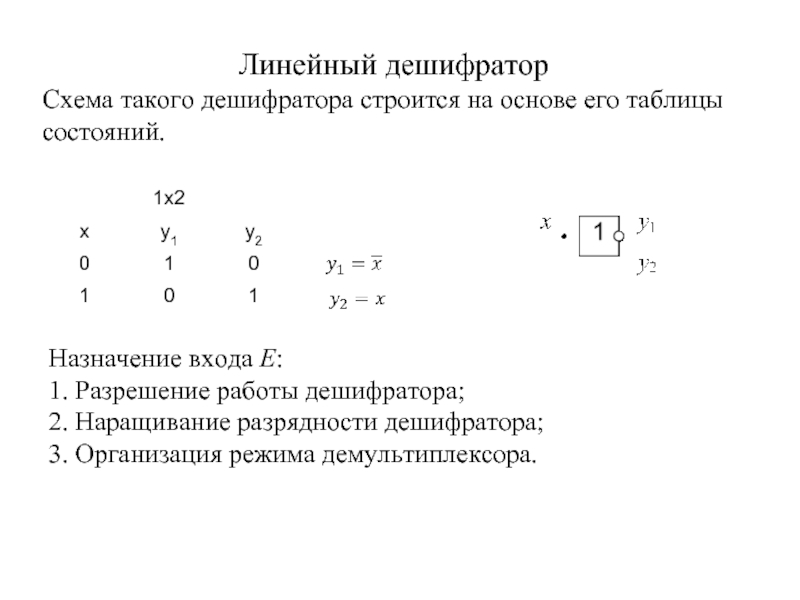

Слайд 9Линейный дешифратор

Схема такого дешифратора строится на основе его таблицы состояний.

Назначение

1. Разрешение работы дешифратора;

2. Наращивание разрядности дешифратора;

3. Организация режима демультиплексора.

Слайд 11Шифраторы

Шифраторы, в отличие от дешифраторов, осуществляют обратную функцию, т.е. преобразуют унитарный

Вывод Е – вход включения шифратора

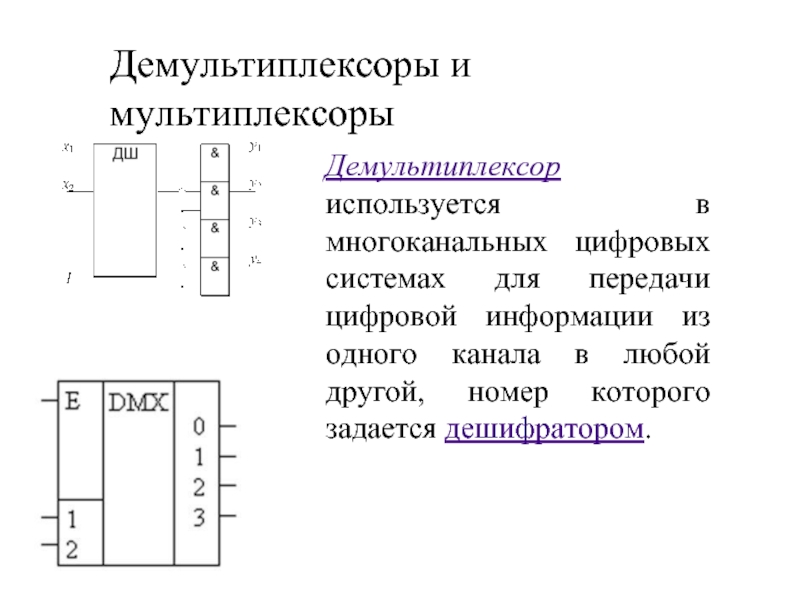

Слайд 12Демультиплексоры и мультиплексоры

Демультиплексор используется в многоканальных цифровых системах для передачи цифровой

Слайд 13

Мультиплексор используется в многоканальных цифровых системах и, в отличие от демультиплексора,

Слайд 15Полный одноразрядный сумматор

В отличие от полусумматора, полный одноразрядный сумматор учитывает перенос

Слайд 16Многоразрядные сумматоры

Многоразрядный сумматор предназначен для суммирования двух многоразрядный двоичных чисел и

При этом могут использоваться три различных варианта построения сумматора: параллельный многоразрядный сумматор с последовательным переносом; сумматор с параллельным (сквозным) переносом; сумматор со смешанным переносом.

Слайд 19Тактируемые цифровые устройства

Цифровые запоминающие устройства

Триггеры

Триггер – это одноразрядное, цифровое запоминающее устройство,

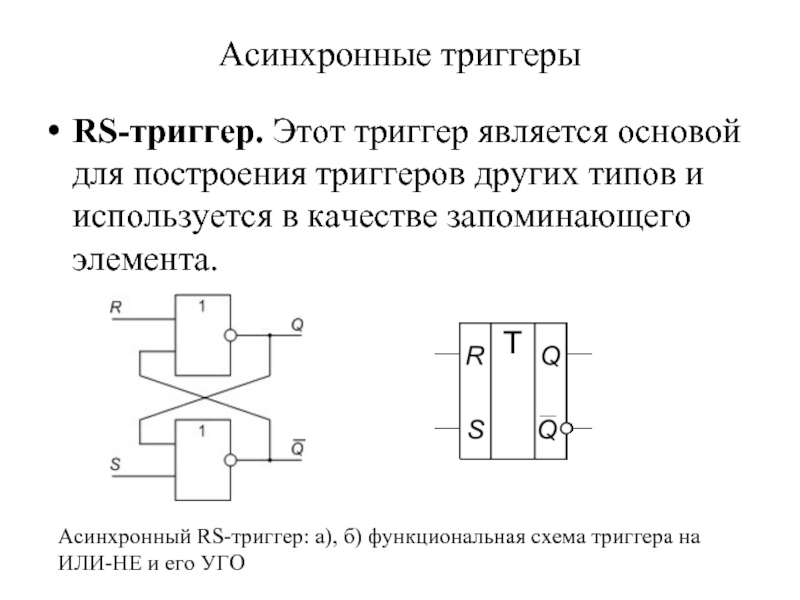

Слайд 20Асинхронные триггеры

RS-триггер. Этот триггер является основой для построения триггеров других типов

Асинхронный RS-триггер: а), б) функциональная схема триггера на ИЛИ-НЕ и его УГО

Слайд 22Синхронные триггеры

RS-триггер

Однотактный RS триггер (слева) и его временные диаграммы (справа)

Слайд 24Триггер D-типа

а)

б)

в)

Однотактный D-триггер его функциональная схема (а),

УГО (б) и временные

Слайд 25Триггер T–типа (счётный триггер)

Условно-графическое обозначение T-триггера и временные диаграммы

Слайд 26Двухтактные триггеры

Двухтактный триггер D-типа

Двухтактный D-триггер (а) и его временные диаграммы (б)

Слайд 27Двухтактные триггеры могут работать:

по переднему фронту;

по заднему фронту.

Тактовые входы

Слайд 28

Временные диаграммы Т-триггера:

а) срабатывание по переднему фронту импульса;

б) срабатывание по

Слайд 29Регистры

Регистрами называются многоразрядные цифровые запоминающие устройства, предназначенные для приёма, хранения,

Основу регистра составляют триггеры. Обычно используются D-триггеры, как наиболее удобные для записи и хранения информации.

Слайд 31Параллельные регистры

Параллельный n-разрядный регистр представляет собой n триггеров, на информационные входы

Слайд 32Параллельные регистры

Параллельный n-разрядный регистр представляет собой n триггеров, на информационные входы

Слайд 33Последовательные регистры

Последовательные регистры работают с последовательным кодом, разряды которого разделены во

Различают регистры прямого сдвига и реверсивные регистры.

Слайд 35Регистры прямого сдвига осуществляют приём (передачу) информации, сдвигая её в регистре

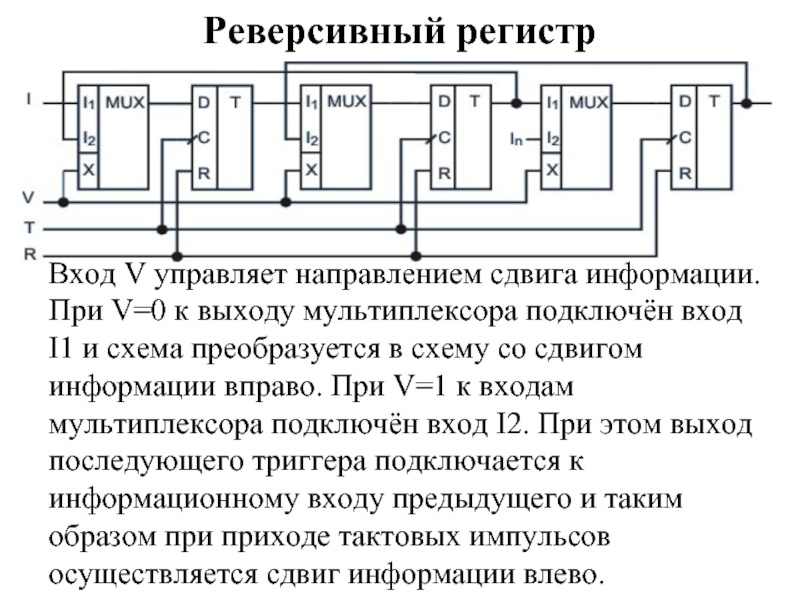

Слайд 36Реверсивный регистр

Вход V управляет направлением сдвига информации. При V=0 к выходу

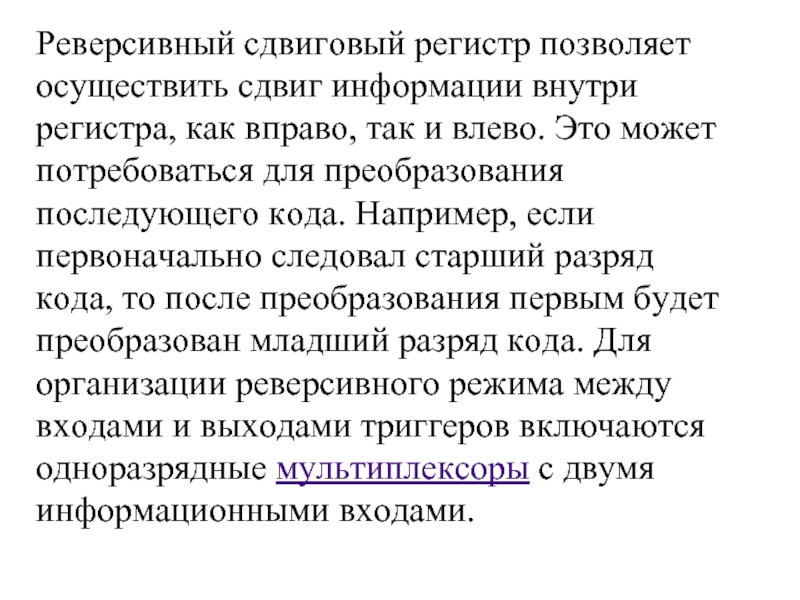

Слайд 37Реверсивный сдвиговый регистр позволяет осуществить сдвиг информации внутри регистра, как вправо,

Слайд 38Параллельно-последовательные регистры

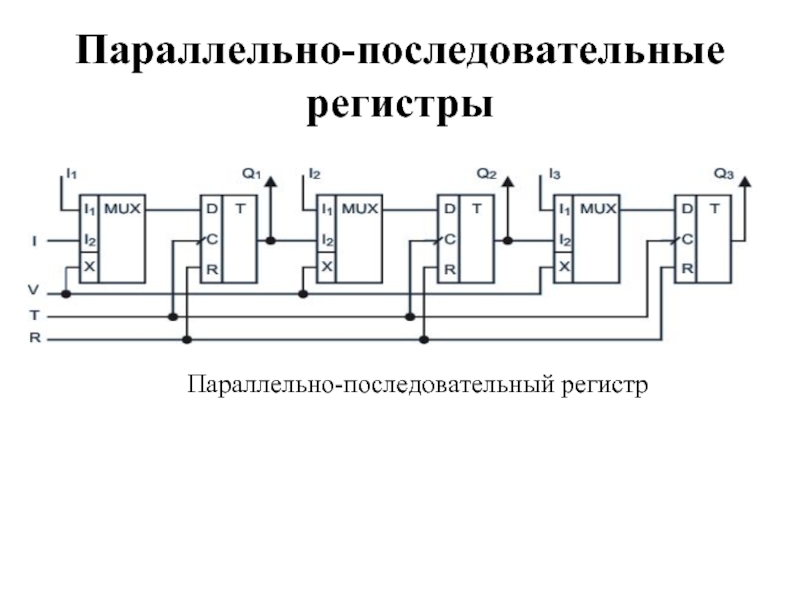

Такие регистры служат для преобразования информации с последовательного кода в

Для организации одновременного наличия двух режимов (параллельного и последовательного) чаще пользуются более простым схемотехническим решением - между триггерами включают одноразрядный мультиплексор.

Слайд 40Параллельно-последовательные регистры

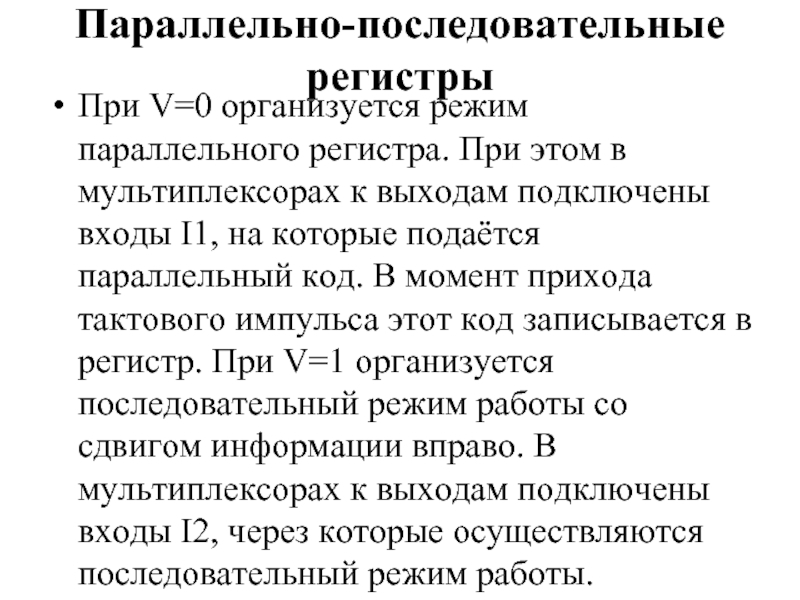

При V=0 организуется режим параллельного регистра. При этом в мультиплексорах

Слайд 41Счётчики импульсов

Счетчиком называется устройство, предназначенное для счета входных импульсов и фиксации

Слайд 42К основным характеристикам счетчиков относятся модуль счета (коэффициент пересчета Ксч) и

Основой для построения счётчиков является счётный триггер или T-триггер. Он представляет собой простейший одноразрядный счётчик

Слайд 43Асинхронные счётчики импульсов

Асинхронный счетчик импульсов представляет собой последовательно соединенные триггеры Т-типа,

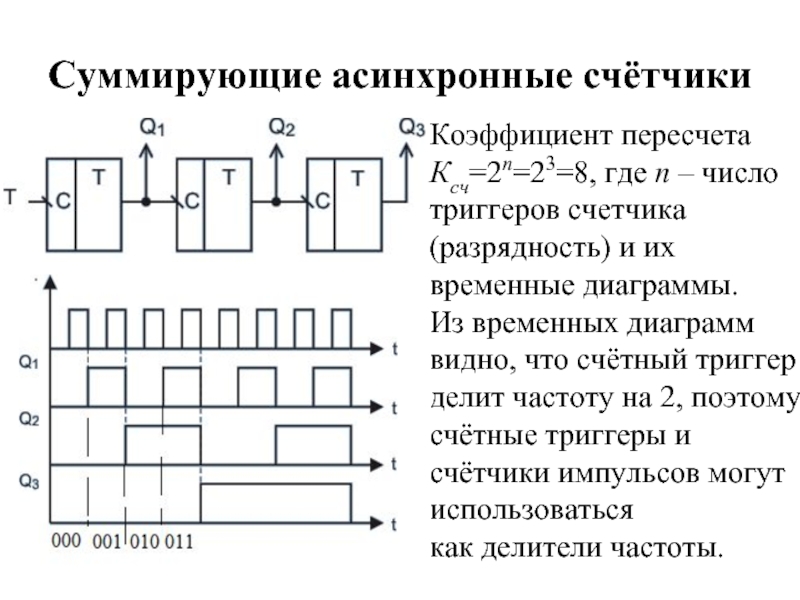

Слайд 44Суммирующие асинхронные счётчики

Коэффициент пересчета Ксч=2n=23=8, где n – число триггеров счетчика

Из временных диаграмм видно, что счётный триггер делит частоту на 2, поэтому счётные триггеры и счётчики импульсов могут использоваться

как делители частоты.

Слайд 47Реверсивные счётчики

Такой счетчик является комбинацией двух предыдущих и позволяет осуществлять как

Асинхронный реверсивный счетчик (слева) и его УГО (справа)

Слайд 48Реверсивные счётчики

Сигнал на входе V определяет вид межразрядной связи, а, следовательно,

Слайд 49Асинхронные счётчики с произвольным коэффициентом пересчёта

В асинхронных счётчиках произвольный коэффициент пересчёта

Слайд 50Счетчик с принудительным насчетом

Структурная схема асинхронного счетчика с принудительным насчетом

Слайд 51Счётчики с принудительным сбросом

Определитель кода (ОК) должен определять соответствующий Ксч. При

Слайд 52Счетчики с переносом

Такие счётчики делятся на 2 типа:

1. С параллельным

2.С последовательным переносом.

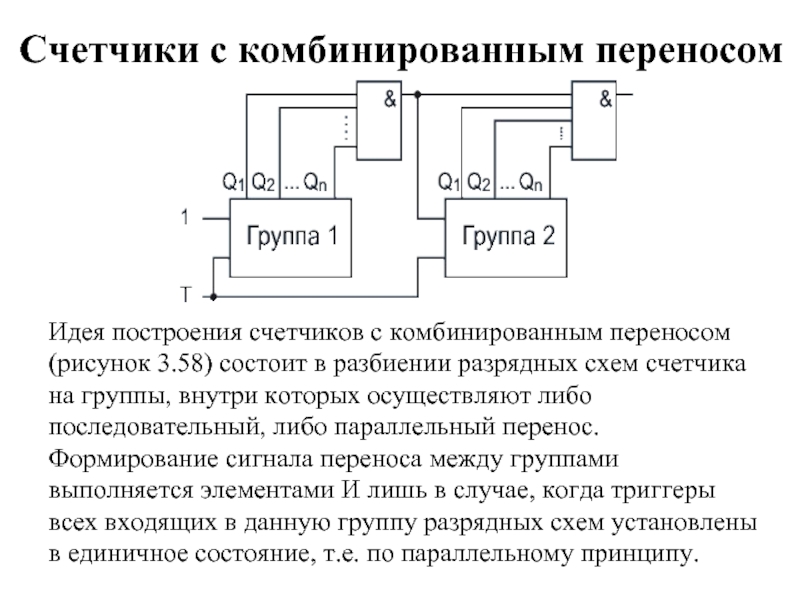

Слайд 56Счетчики с комбинированным переносом

Идея построения счетчиков с комбинированным переносом (рисунок 3.58)

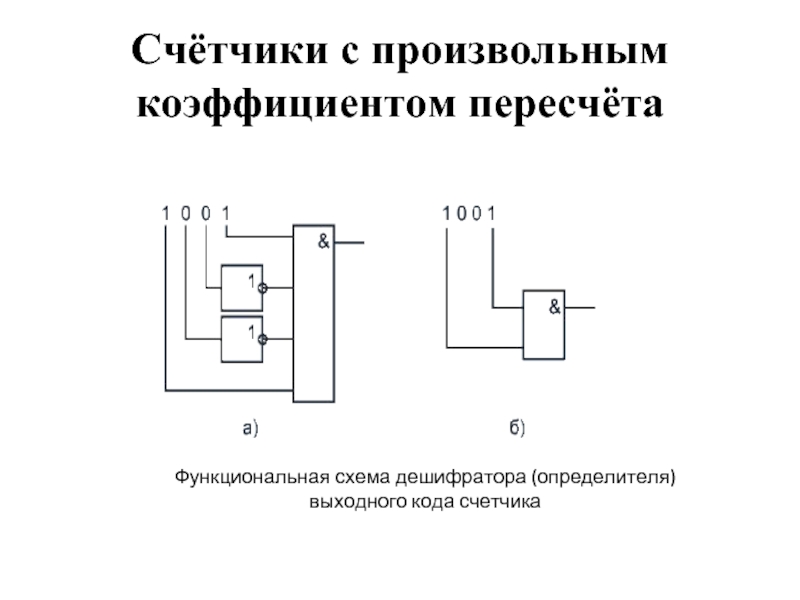

Слайд 57Счётчики с произвольным коэффициентом пересчёта

Функциональная схема дешифратора (определителя)

выходного кода счетчика

Слайд 59Счётчики с произвольным коэффициентом пересчёта

В качестве основы для построения счётчиков с

Порядок разработки счётчика с произвольным коэффициентом пересчёта Ксч.

1. Выбирается n счётных триггеров (разрядов) счётчика из условия 2n-1<Ксч<2n.

2. В схему счётчика с параллельным переносом добавляется дешифратор (определитель) выходного кода счётчика, равного (Ксч-1). Он реализуется на основе n-разрядной схемы И. Можно уменьшить количество входов в схеме И, если подавать на неё только разряды, в коде которых (Ксч-1) присутствует единица.

Слайд 60Счётчики с произвольным коэффициентом пересчёта

Записывается значение трёх кодов: Ксч-1, Ксч и

Например, для Ксч=6 имеем:

Слайд 614. Для первого варианта сохраняется формирование переноса без изменений. Для запрета,

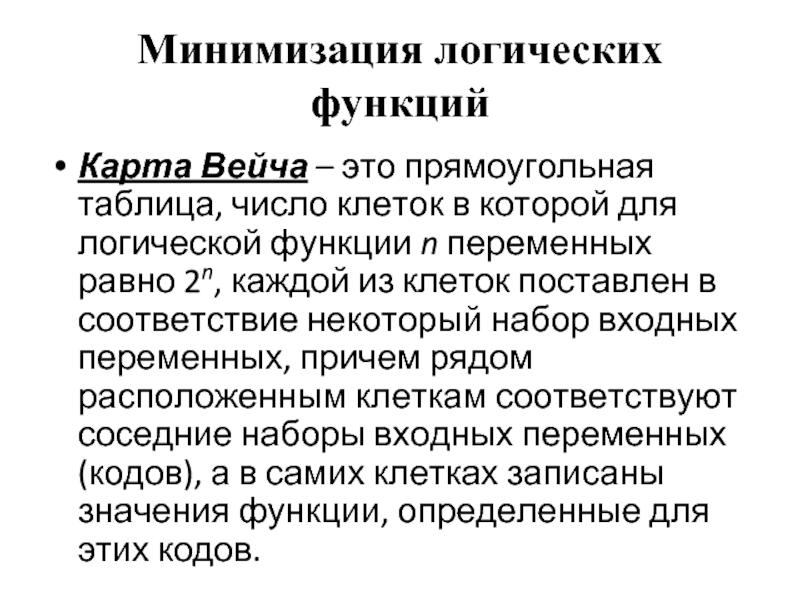

Слайд 63Минимизация логических функций

Карта Вейча – это прямоугольная таблица, число клеток в

Слайд 65Алгоритм минимизации логической функции сводится к следующему:

Для логической функции составляется таблица

В ячейки карты записываются значения функции из таблицы состояний;

Выделяют на карте группу единиц (нулей) функции, закрываемых прямоугольниками со сторонами 2к (где к – целое число) с учётом возможности склеивания противоположных сторон карты. Для лучшей минимизации прямоугольники нужно выбирать так, чтобы площадь была наибольшей, при этом возможно частичное наложение прямоугольников друг на друга. Задача состоит в том, чтобы минимальное количество прямоугольников закрывало, не захватывая нулей (единиц), все единицы (нули) карты.

Для каждого прямоугольника записывают логическую функцию в виде логического умножения аргументов, которые для данного прямоугольника не изменяют своё значение. Произведения носят название импликанты.

Полностью минимизированная логическая функция получается путём логического сложения импликантов.