- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

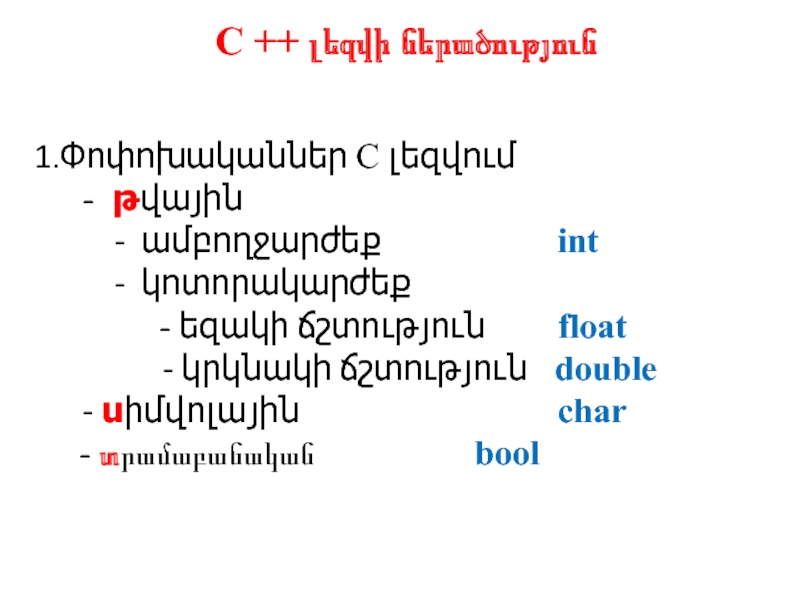

- Информатика

- История

- Литература

- Маркетинг

- Математика

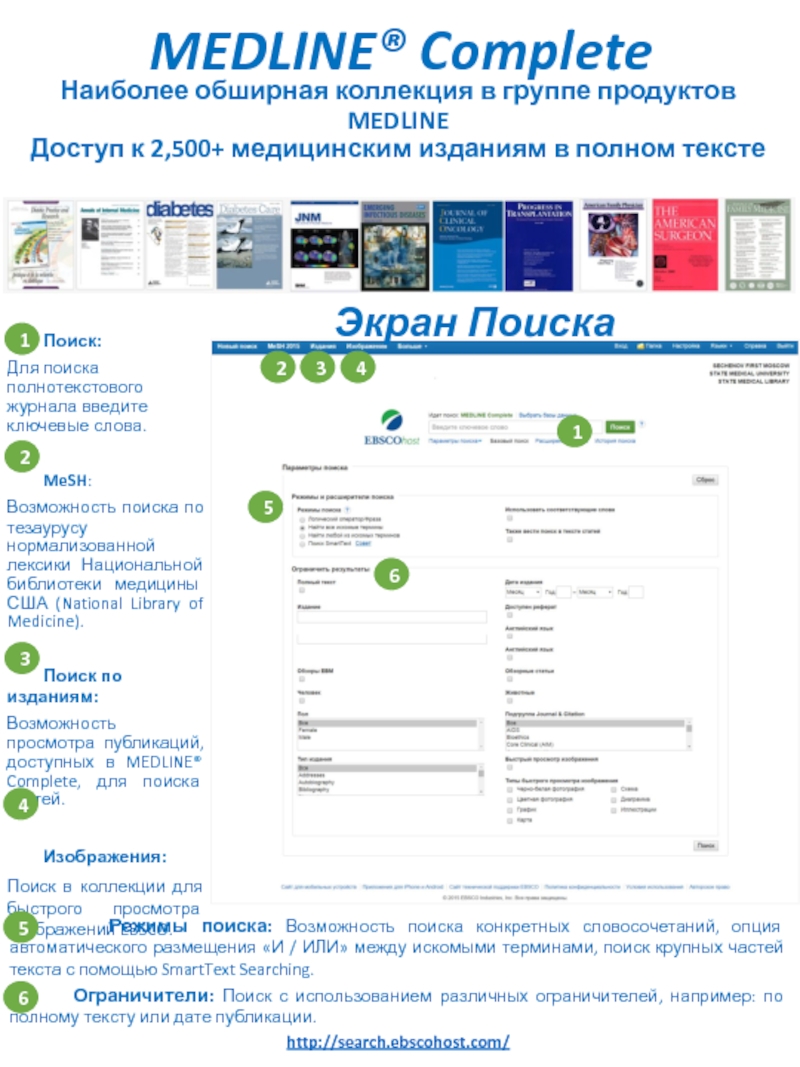

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Концепция машины с хранимой в памяти программой. (Тема 2) презентация

Содержание

- 1. Концепция машины с хранимой в памяти программой. (Тема 2)

- 2. Основными свойствами алгоритма являются: дискретность, определенность, массовость

- 3. Массовость алгоритма подразумевает его применимость к множеству

- 4. В основе архитектуры современных ВМ лежит представление

- 5. Сущность фон-неймановской концепции вычислительной машины можно свести

- 6. Согласно принципу двоичного кодирования, вся информация, как

- 7. Код операции представляет собой указание, какая операция

- 8. Принцип программного управления Все вычисления, предусмотренные

- 9. Принцип однородности памяти Команды и данные хранятся

- 10. Концепция вычислительной машины, изложенная в статье фон

- 11. Принцип адресности Структурно основная память состоит из

- 12. Фон-неймановская архитектура

- 13. Фон Неймана определил основные устройства ВМ, с

- 14. Введенная информация сначала запоминается в основной памяти,

- 15. Для таких ЗУ характерна энергозависимость – хранимая

- 16. Для долговременного хранения больших программ и массивов

- 17. Устройство управления (УУ) – важнейшая часть ВМ,

- 18. Пересылка информации между любыми элементами ВМ инициируется

- 19. Еще одной неотъемлемой частью ВМ является арифметико-логическое

- 20. Флаги могут анализироваться в УУ с целью

- 21. Классификация архитектур По структуре вычислительных машин

- 22. В настоящее время примерно одинаковое распространение получили

- 23. Структура фон-неймановской вычислительной машины

- 24. У фон-неймановских ВМ таким «узким местом» является

- 25. Структура вычислительной машины на базе общей шины

- 26. Благодаря этим свойствам шинная архитектура получила широкое

- 27. В целом, при сохранении фон-неймановской концепции последовательного

- 28. Структура с одной шиной

- 29. Структура с двумя видами шин

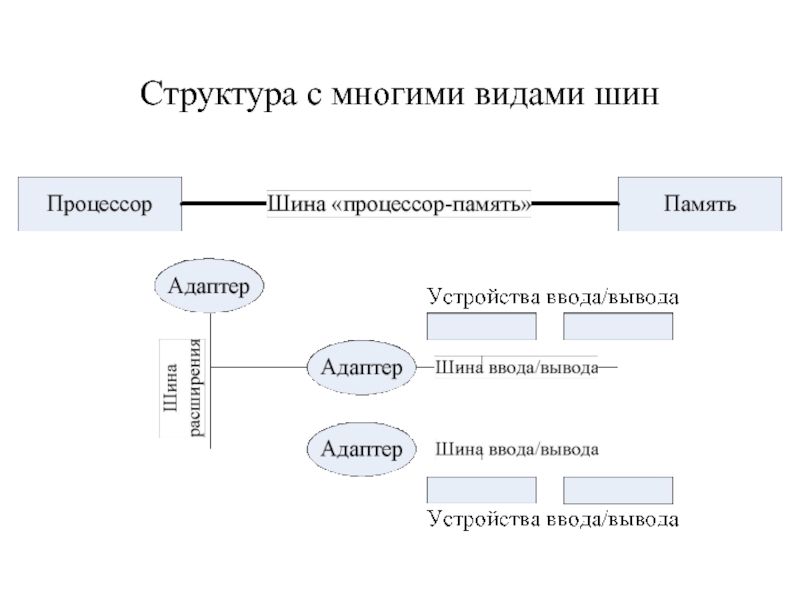

- 30. Структура с многими видами шин

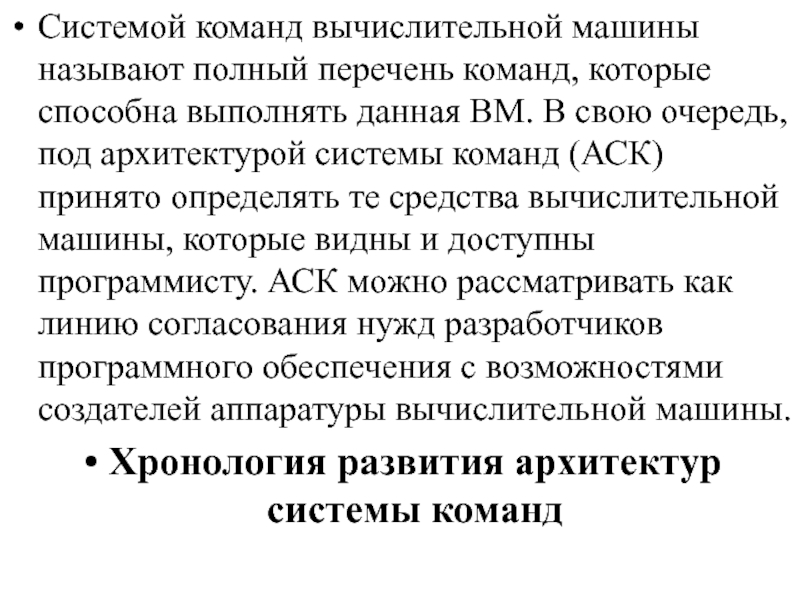

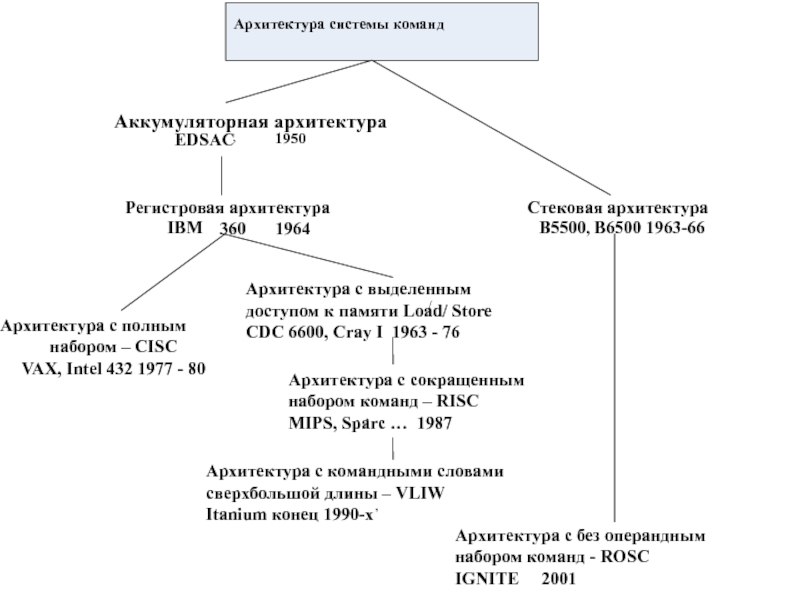

- 31. Классификация архитектур По системам команд

- 32. Системой команд вычислительной машины называют полный перечень

- 34. Стековая архитектура Стеком называется память, по

- 35. Принцип действия стековой памяти

- 36. Верхнюю ячейку называют вершиной стека. Для работы

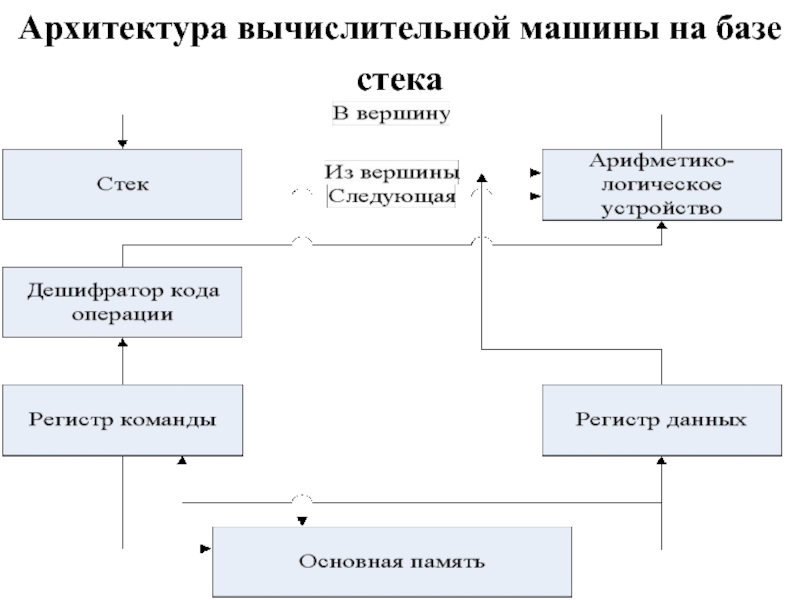

- 37. Архитектура вычислительной машины на базе стека

- 38. Для выполнения арифметической или логической операции на

- 39. К достоинствам АСК на базе стека следует

- 40. Аккумуляторная архитектура Архитектура на базе аккумулятора исторически

- 41. Архитектура ВМ на базе аккумулятора.

- 42. Для выполнения операции в АЛУ производится считывание

- 43. Регистровая архитектура В машинах данного типа процессор

- 44. RISC-архитектура предполагает использование существенно большего числа РОН

- 45. В варианте «регистр-регистр» операнды могут находиться только

- 46. К достоинствам регистровых АСК следует отнести: компактность

- 47. Архитектура с выделенным доступом к памяти В

- 48. В архитектуре отсутствуют команды обработки, допускающие прямое

- 49. Классификация по составу и сложности команд

- 50. Пытаясь преодолеть семантический разрыв, разработчики вычислительных машин

- 51. В вычислительных машинах типа CISC проблема семантического

- 52. К типу CISC можно отнести практически все

- 53. Термин RISC впервые был использован Д. Паттерсоном

- 54. Элементы RISC-архитектуры впервые появились в вычислительных машинах

- 55. Помимо CISC- и RISC-архитектур в общей классификации

- 56. Основные направления в развитии архитектур процессоров

- 57. Конвейер команд Идея конвейера команд была

- 58. 3. Вычисление адресов операндов (ВА). Вычисление исполнительных

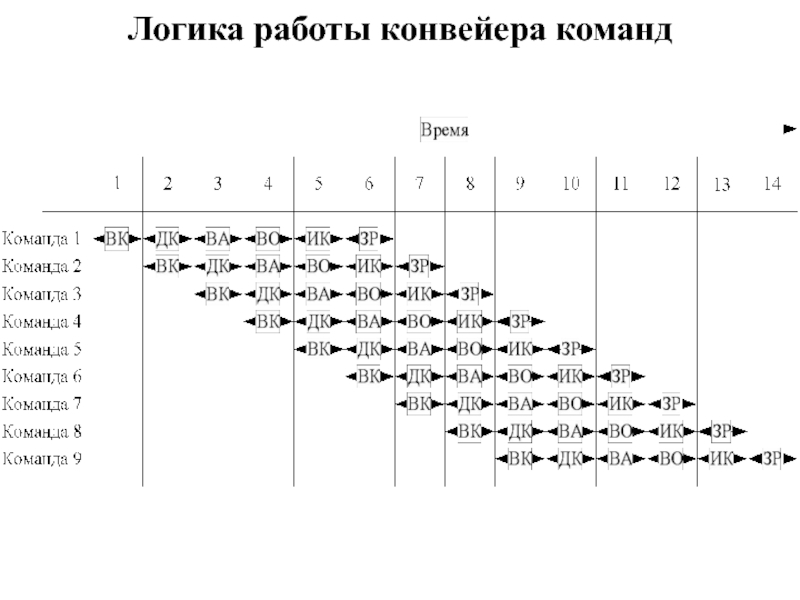

- 59. Логика работы конвейера команд

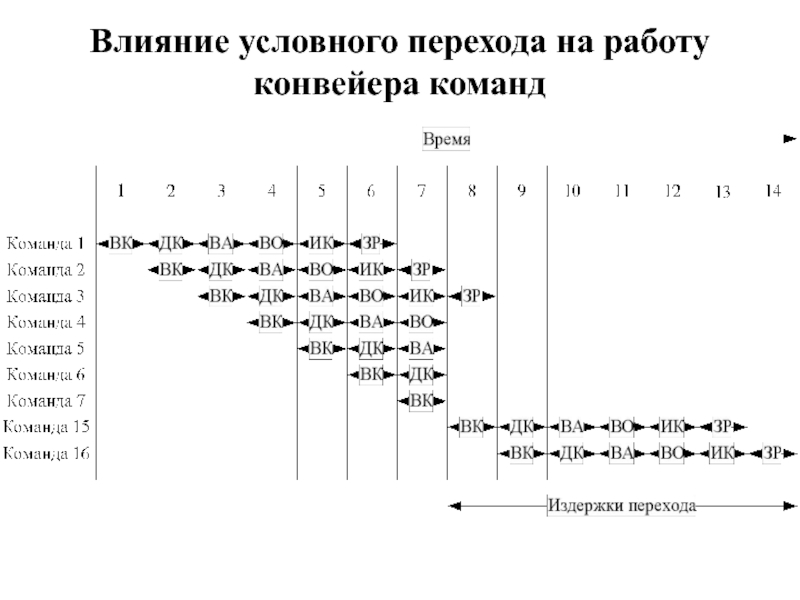

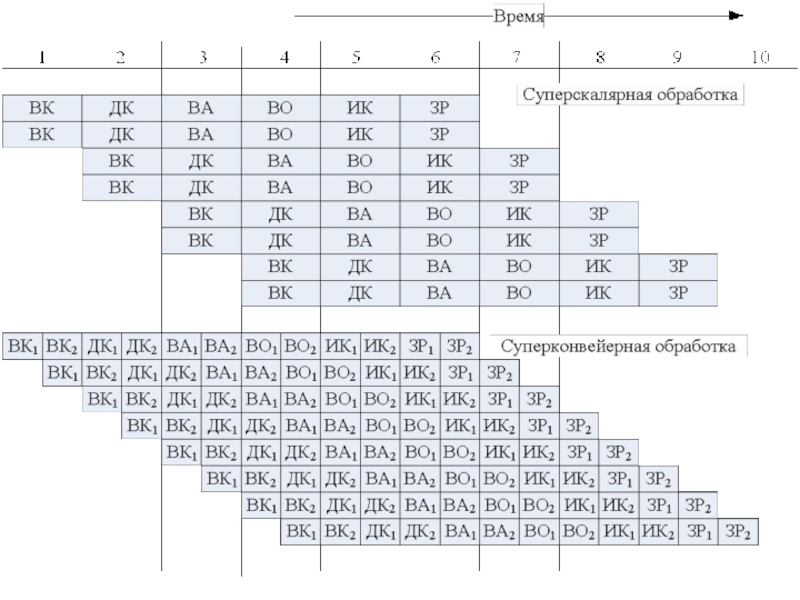

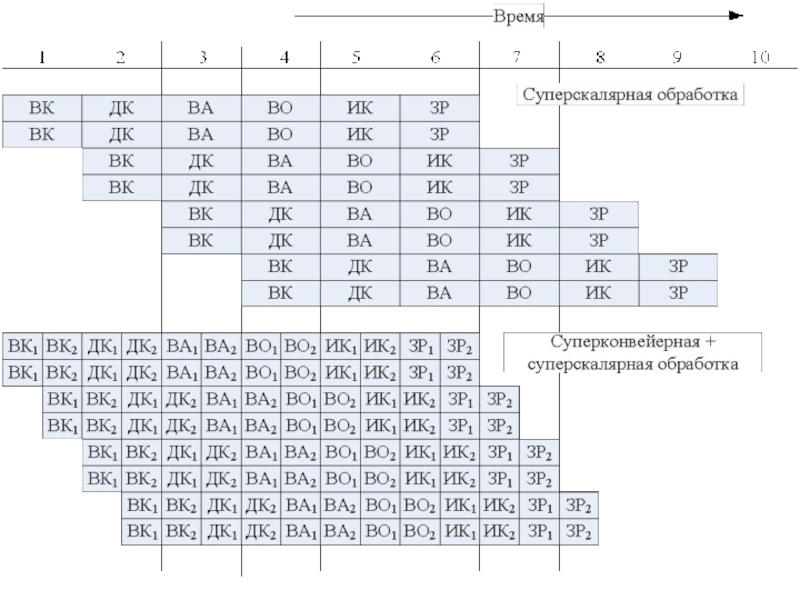

- 60. На рисунке показан конвейер с шестью ступенями,

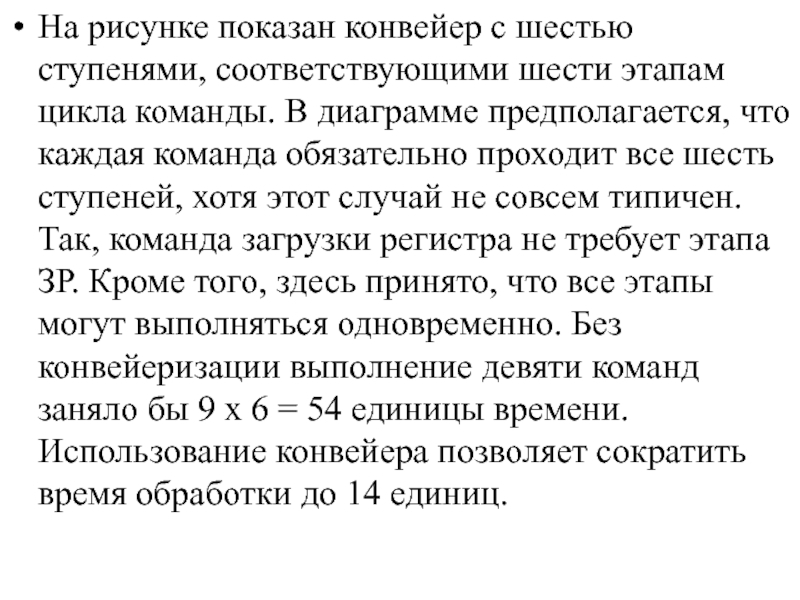

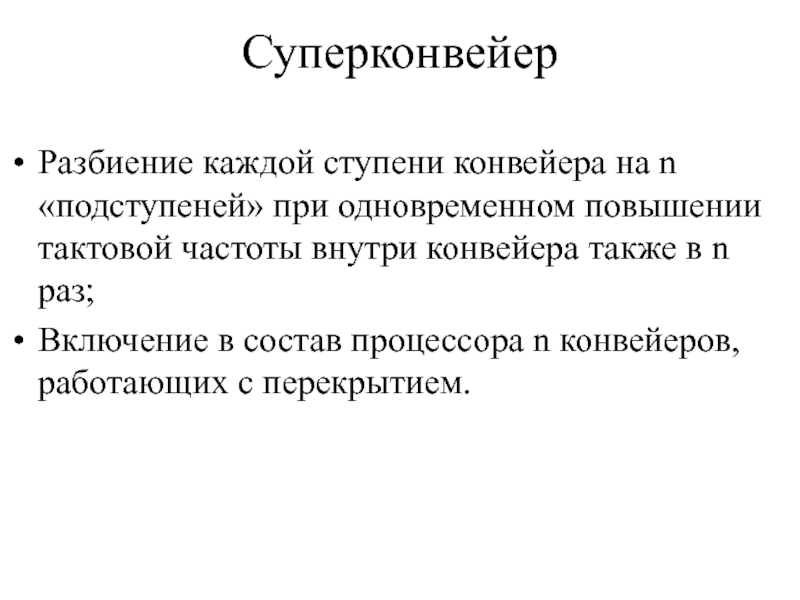

- 61. Суперконвейер Разбиение каждой ступени конвейера на n

- 63. Каждая из шести ступеней стандартного конвейера разбита

- 64. Структурный риск - попытка нескольких команд одновременно

- 65. Структурный риск имеет место, когда несколько команд,

- 66. «Чтение после записи» (ЧПЗ): команда j читает

- 67. Для решения этих проблем применяют предвыборку команд

- 68. Влияние условного перехода на работу конвейера команд

- 69. Пусть команда 3 – это условный переход

- 70. Статическое предсказание переходов. Динамическое предсказание переходов. Классификации схем предсказания переходов

- 71. Переход происходит всегда. Переход не происходит никогда.

- 72. Предполагается, что каждая команда условного перехода в

- 73. Предполагается, что ни одна из команд условного

- 74. По результатам профилирования, тем командам, которые чаще

- 75. Для одних команд предполагается, что переход произойдет,

- 76. Одноуровневые или бимодальные. Двухуровневые или коррелированные. Гибридные.

- 77. Одноуровневые схемы предсказания переходов Идея

- 78. Предсказание осуществляется на основе предыдущих исходов как

- 79. Гибридные схемы объединяют в себе несколько различных

- 80. Асимметричная схема сочетает в себе черты

- 81. Суперскалярность Суперскалярным (этот термин впервые был

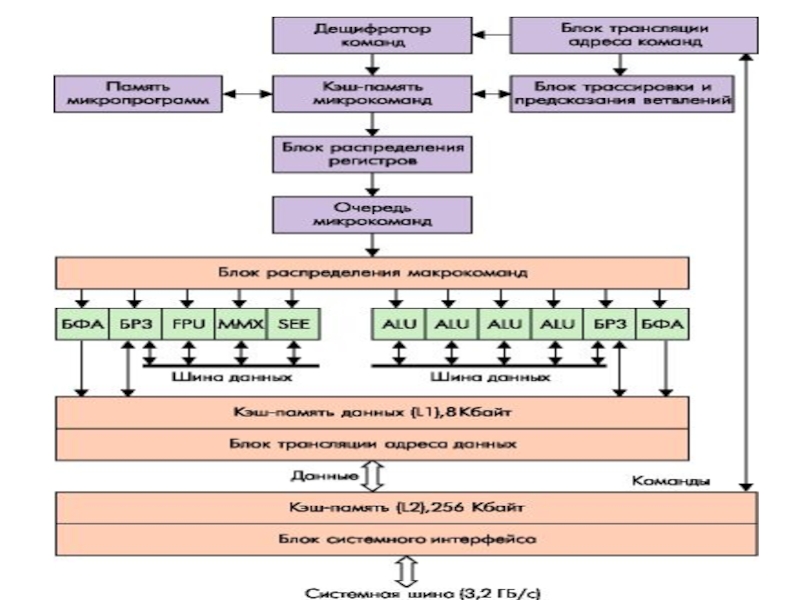

- 82. Архитектура суперскалярного процессора

- 83. Блок выборки команд извлекает команды из основной

- 84. Каждый накопитель команд связан со своим функциональным

- 85. Эта операция называется выдачей команд. Блок распределения

- 89. БФА - блок формирования адреса БРЗ -

- 90. Hyper-threading ( Hyper-threading — Гиперпоточность) В процессорах

- 91. Потоки С точки зрения процессора, поток –

- 92. Развитие микропроцессоров CMP (Chip Multi Processing -многоядерность

- 93. Направление CMP Создание на одном кристалле нескольких

- 94. Направление SMT На одном процессоре осуществляется

- 95. Архитектура EPIC На входе процессора последовательность больших

- 96. Недостатки Значительно усложняются компиляторы Производительность микропроцессора во многом определяется качеством компилятора Увеличивается сложность отладки

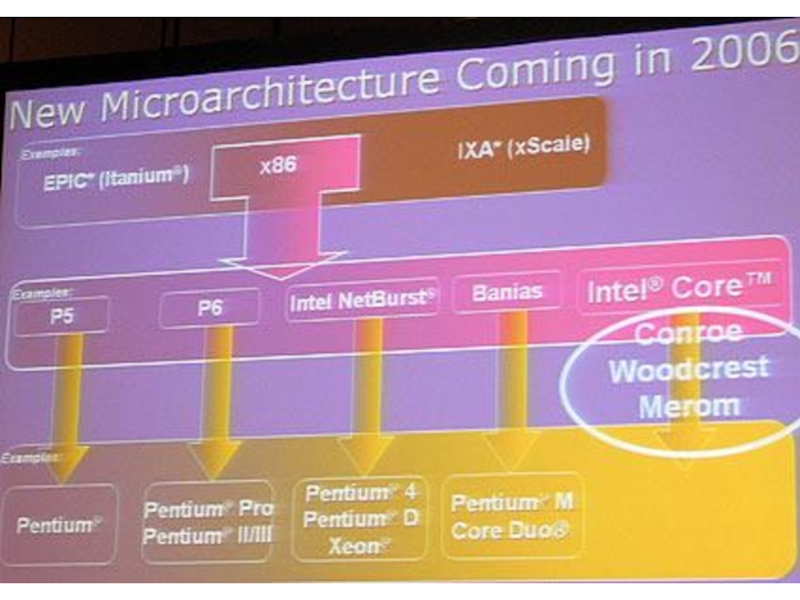

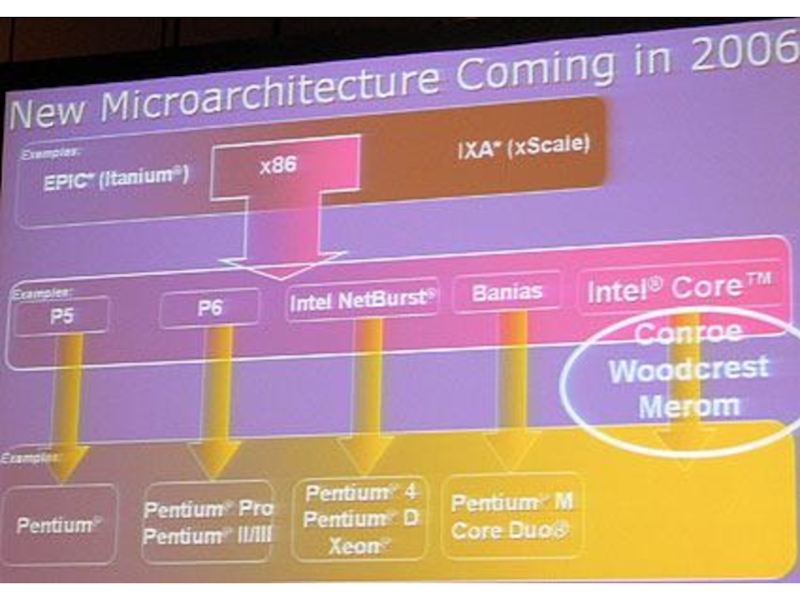

- 97. Развитие микропроцессоров на примере линейки микропроцессоров X86 фирмы Intel

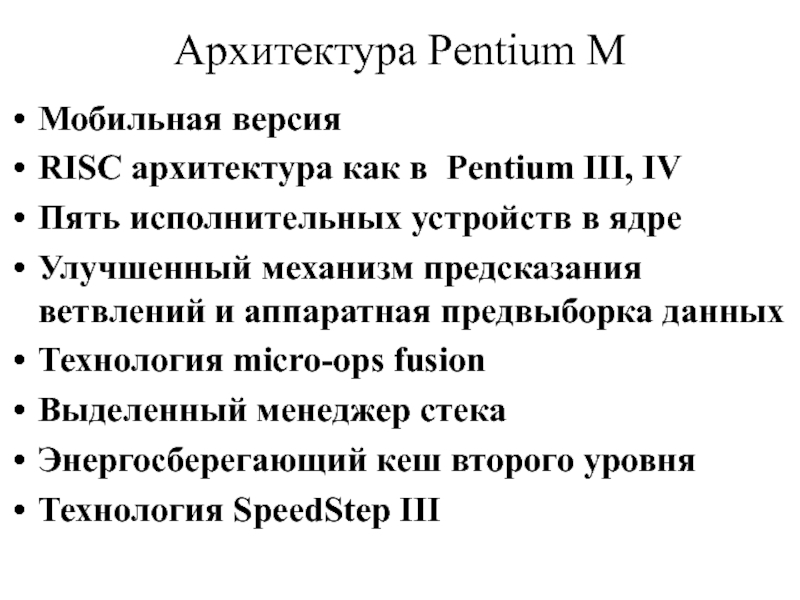

- 99. Архитектура Pentium M Мобильная версия RISC

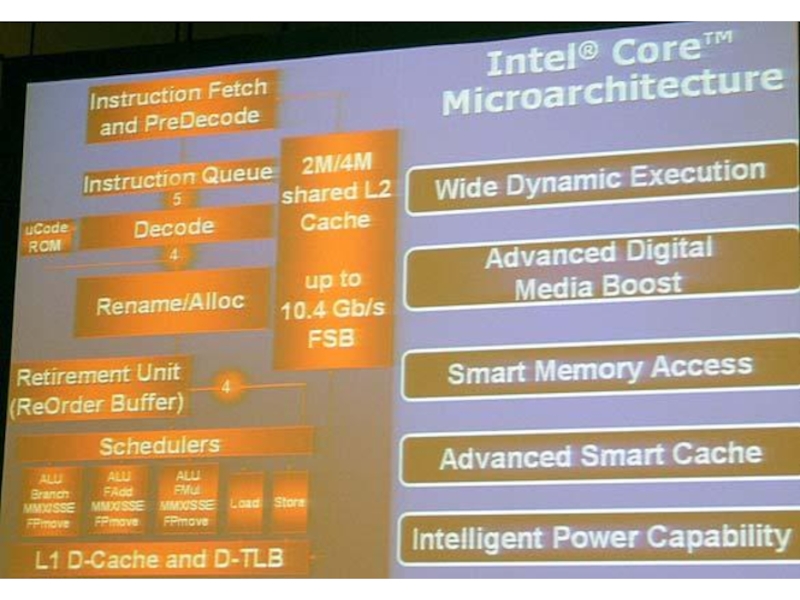

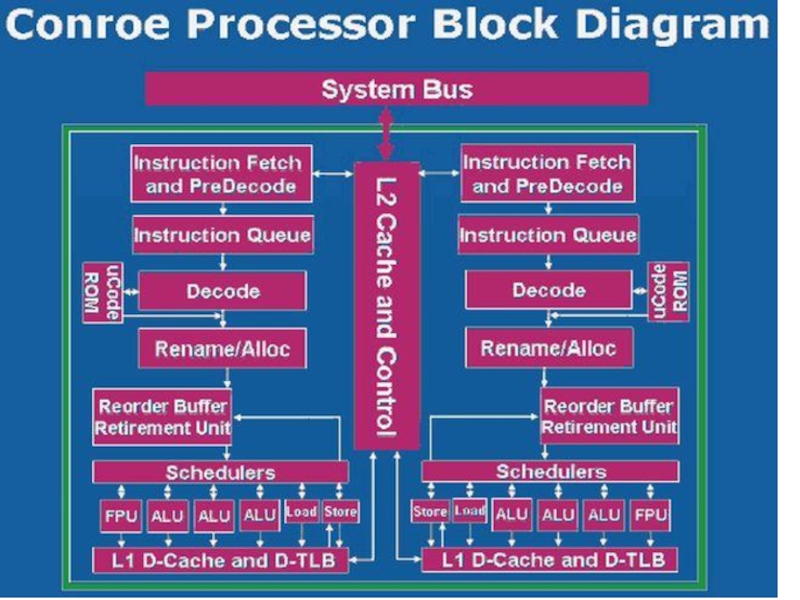

- 100. Архитектура Intel Core Conroe - настольные ПК

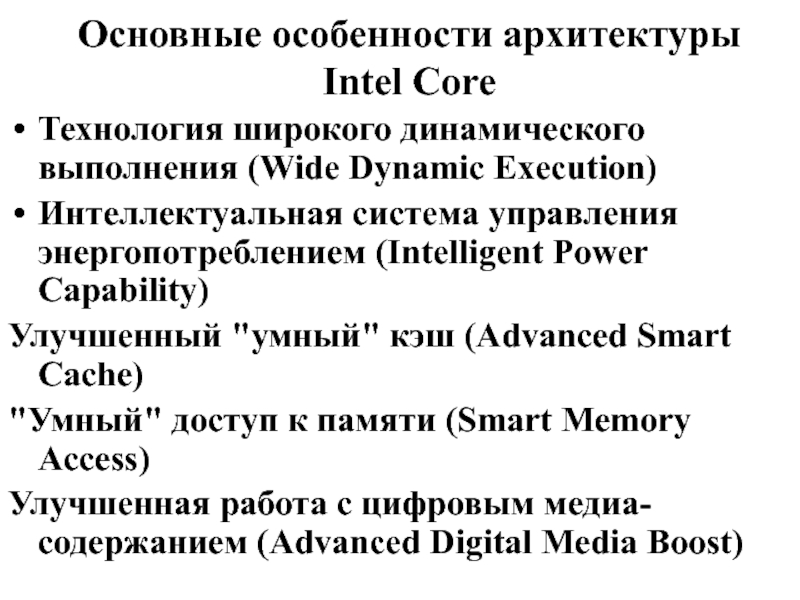

- 103. Основные особенности архитектуры Intel Core Технология

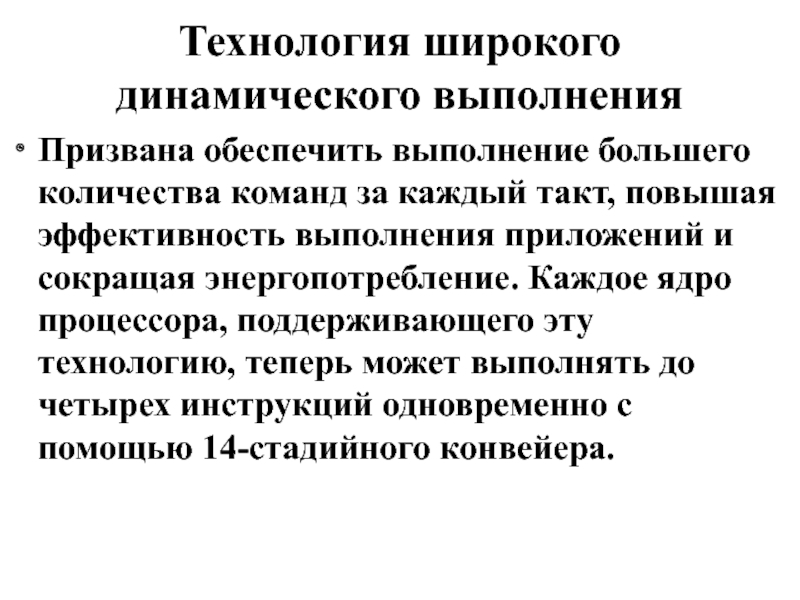

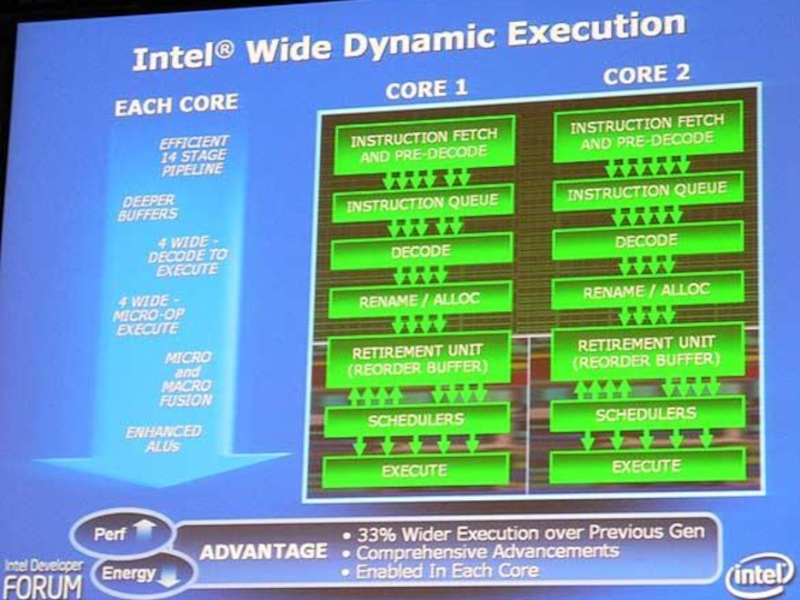

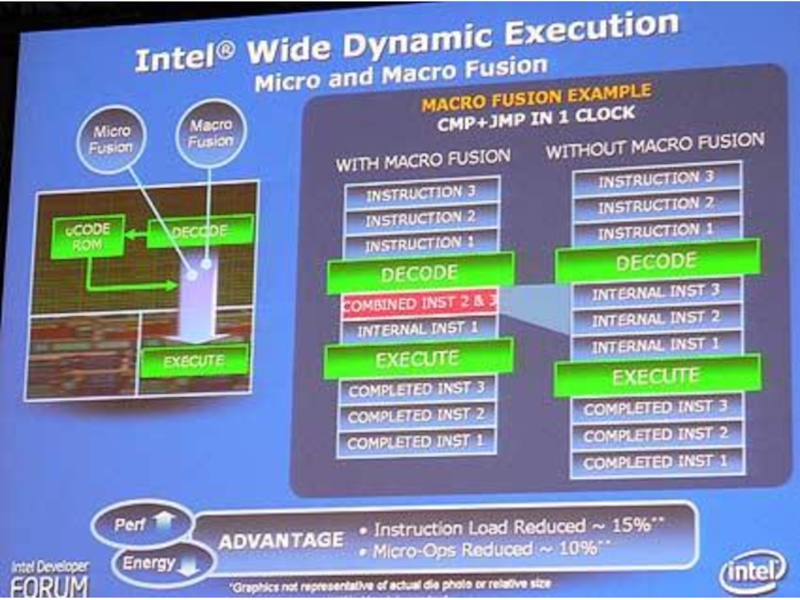

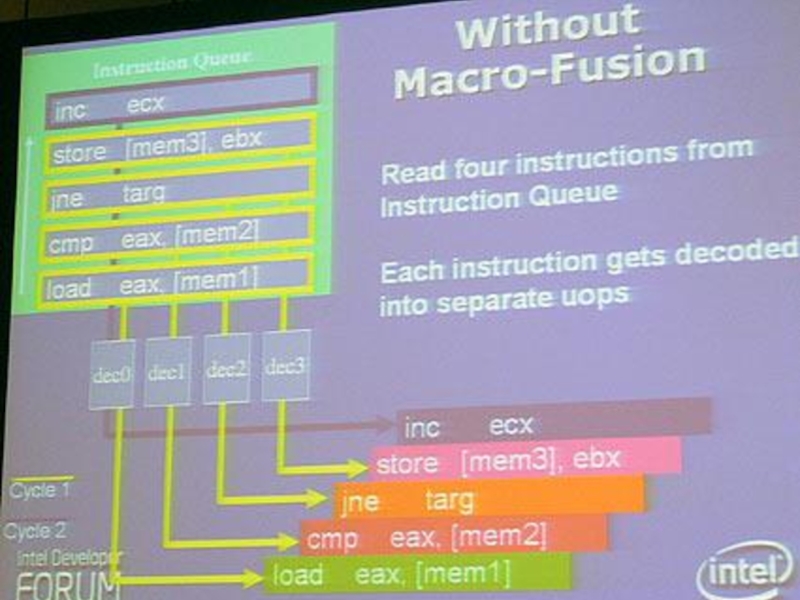

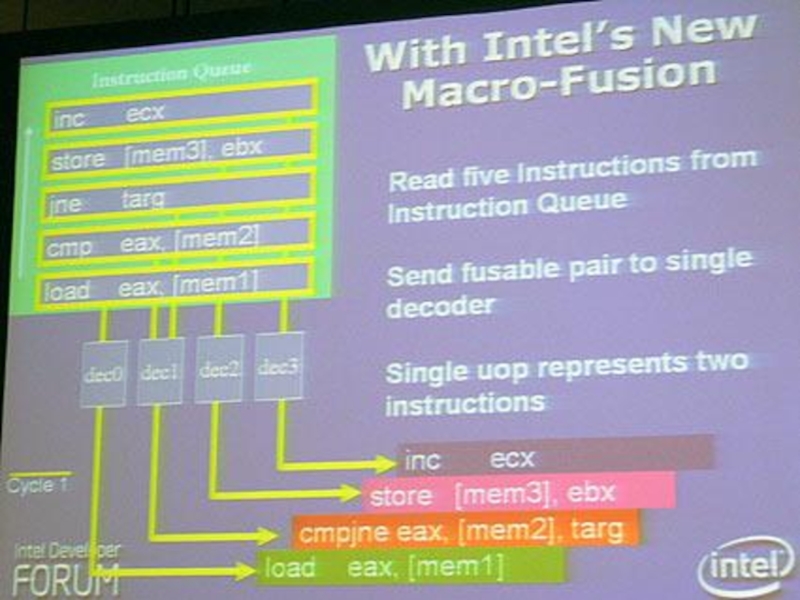

- 104. Технология широкого динамического выполнения Призвана обеспечить выполнение

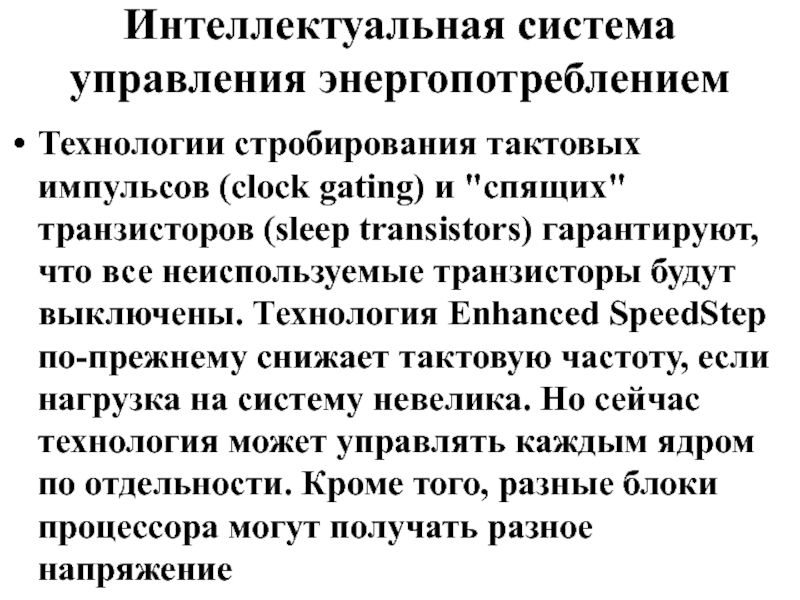

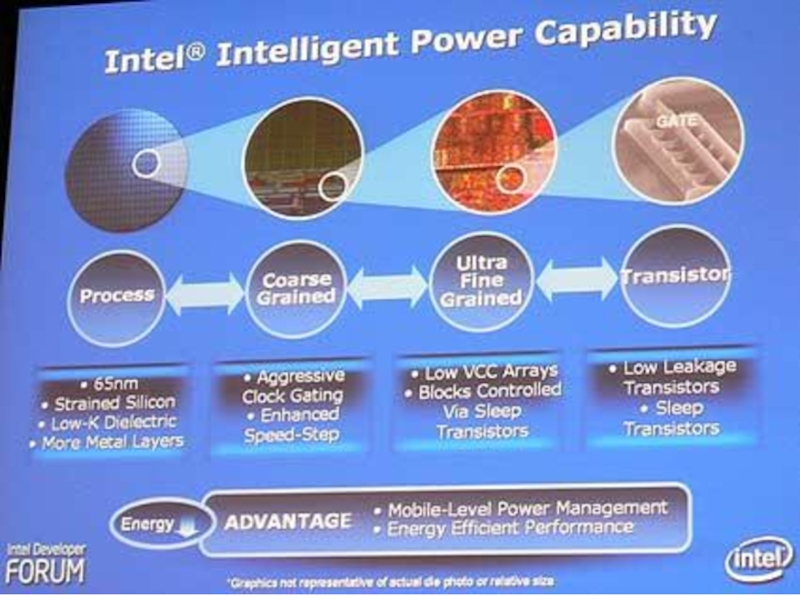

- 109. Интеллектуальная система управления энергопотреблением Технологии стробирования тактовых

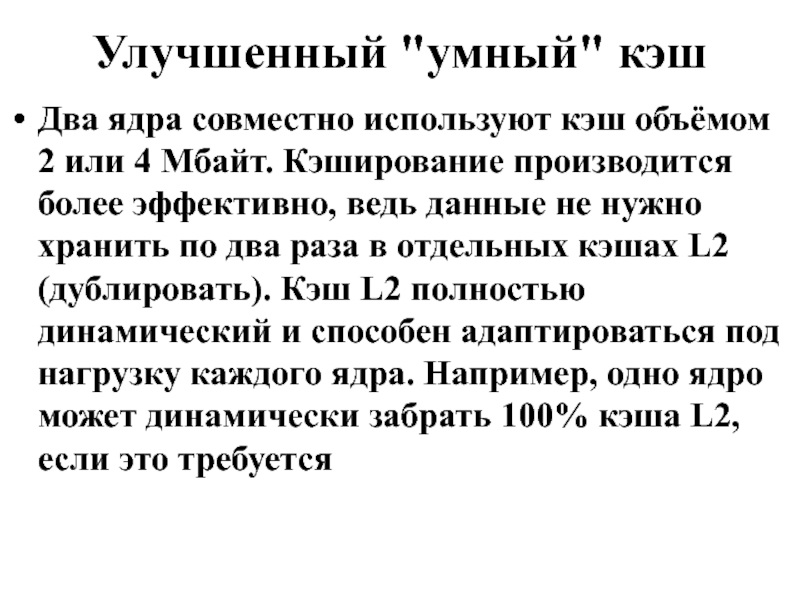

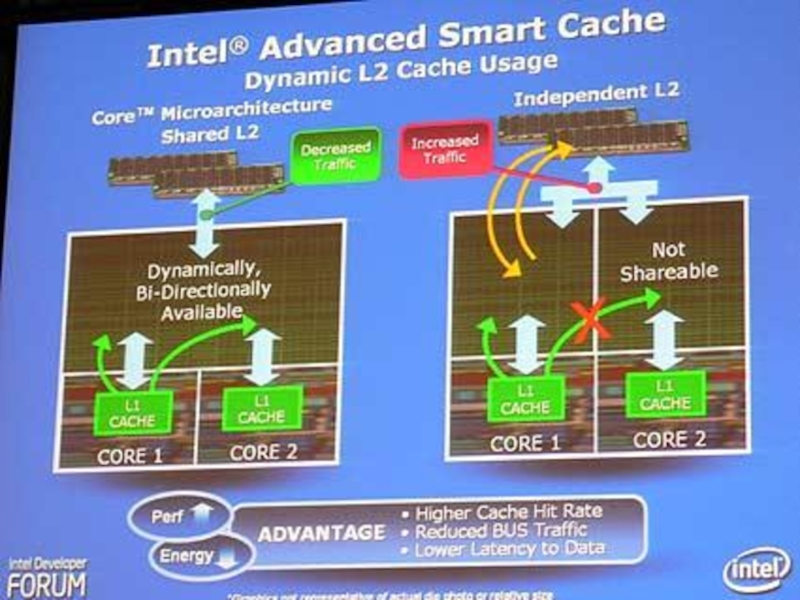

- 111. Улучшенный "умный" кэш Два ядра совместно используют

- 113. "Умный" доступ к памяти Улучшенная предварительная выборка

- 114. "Умный" доступ к памяти Улучшенная предварительная выборка

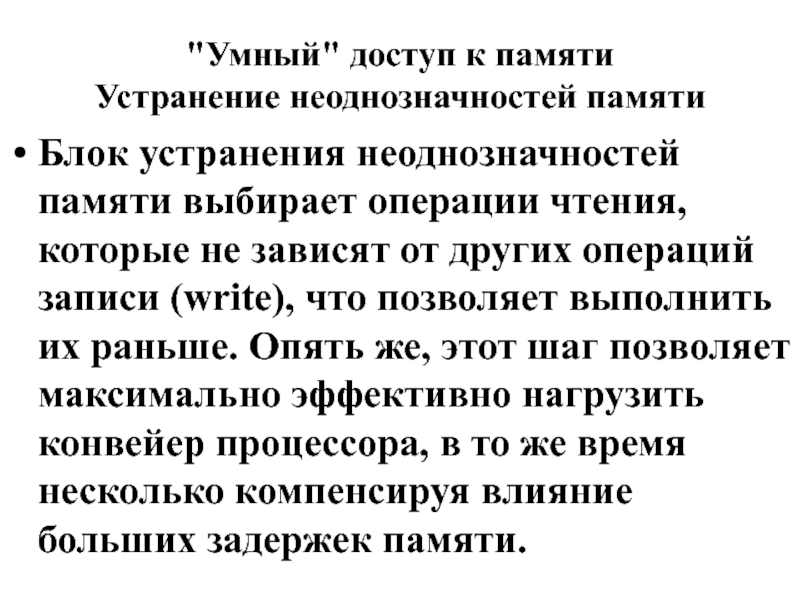

- 115. "Умный" доступ к памяти Устранение неоднозначностей памяти

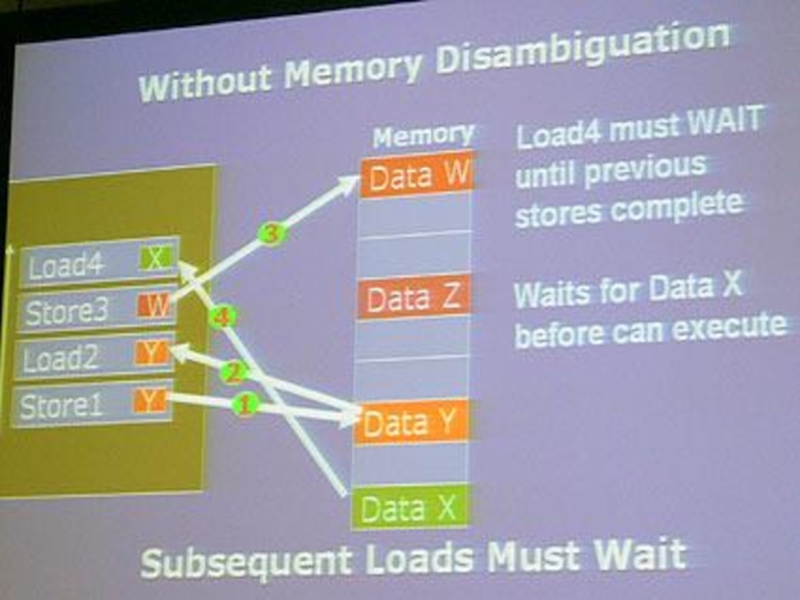

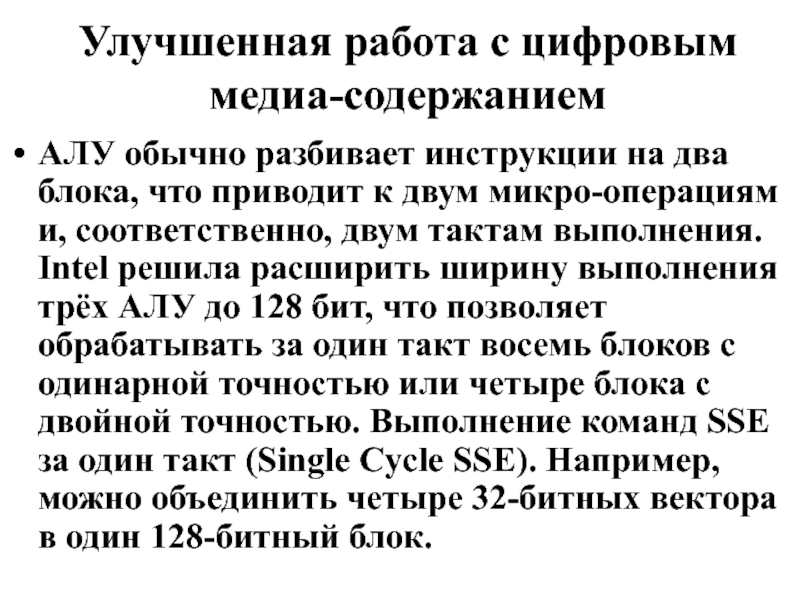

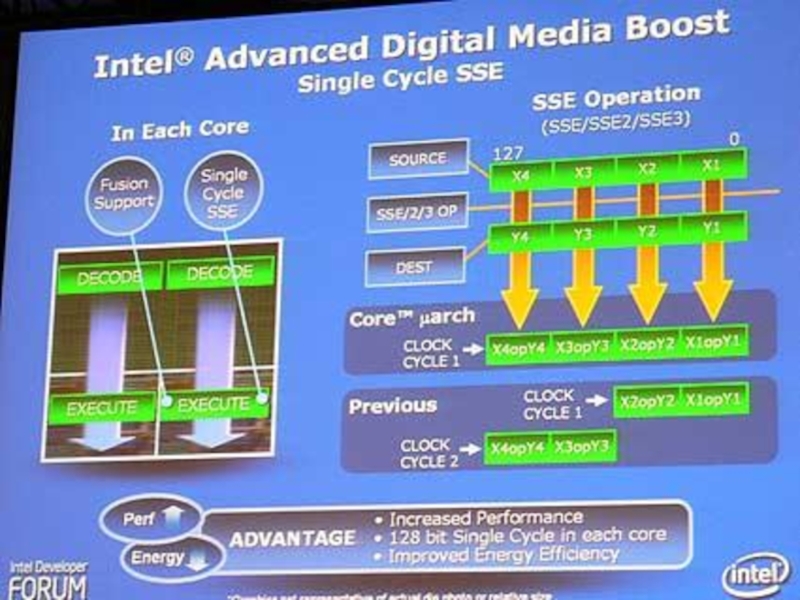

- 118. Улучшенная работа с цифровым медиа-содержанием АЛУ обычно

- 121. Архитектура Core i3 - i7 Основной

- 122. Прочие блоки могут быть следующими: разделяемый кэш

- 123. Core i3 Компания Intel разработала в 2006

- 125. Core i3 Самое основное отличие новых процессоров

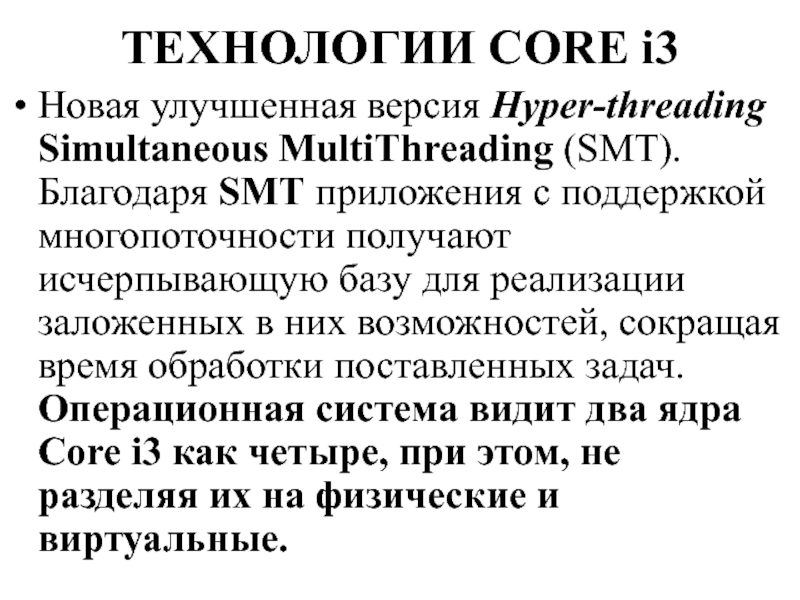

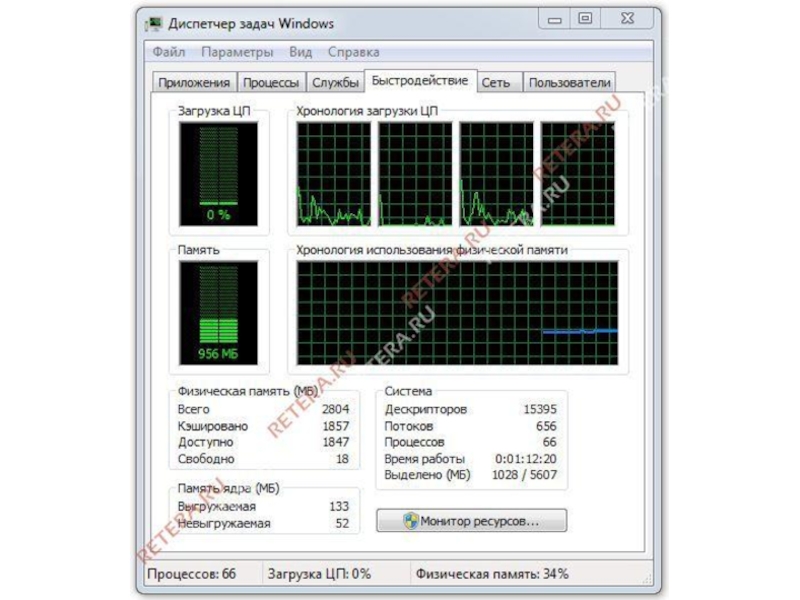

- 127. ТЕХНОЛОГИИ CORE i3 Новая улучшенная версия Hyper-threading

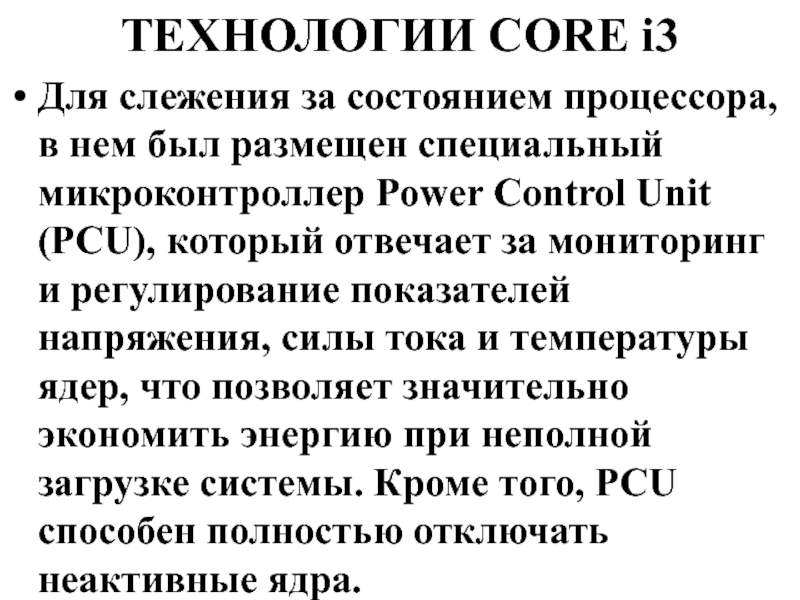

- 129. ТЕХНОЛОГИИ CORE i3 Для слежения за состоянием

- 130. ТЕХНОЛОГИИ CORE i3 Линейка процессоров Core i3,

- 131. ТЕХНОЛОГИИ CORE i3 Virtualization Technology (VT)

- 132. ТЕХНОЛОГИИ CORE i3 Execute Disable Bit обеспечивает

- 133. ТЕХНОЛОГИИ CORE i3 Enhanced Intel SpeedStep -

- 134. ТЕХНОЛОГИИ CORE i3 Trusted Execution состоит из

- 135. ТЕХНОЛОГИИ CORE i3 Intel 64 Architecture поддерживает

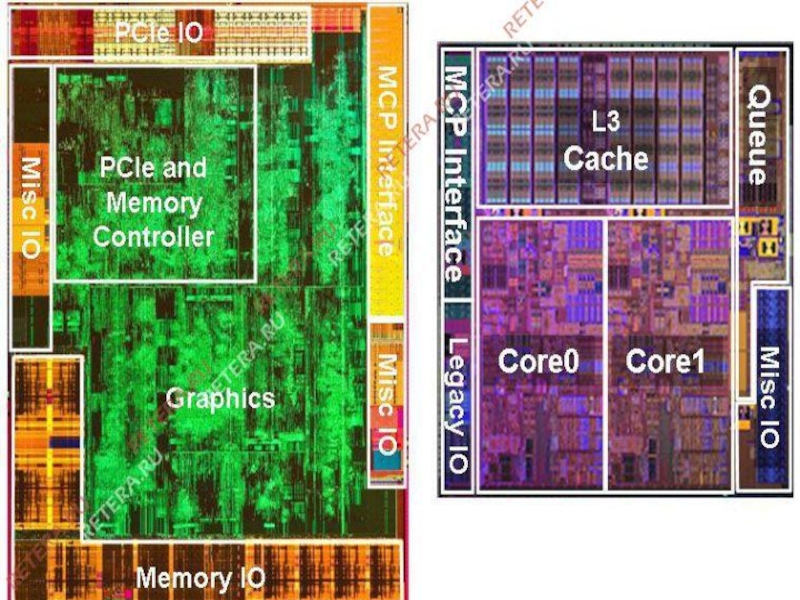

- 136. ГРАФИЧЕСКОЕ ЯДРО Графический чип Intel HD

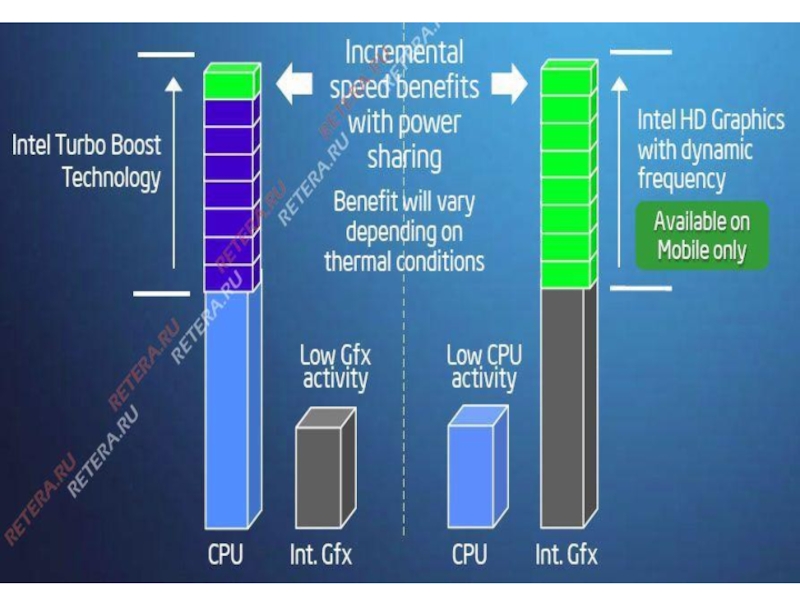

- 137. ГРАФИЧЕСКОЕ ЯДРО Графический чип находится на общем

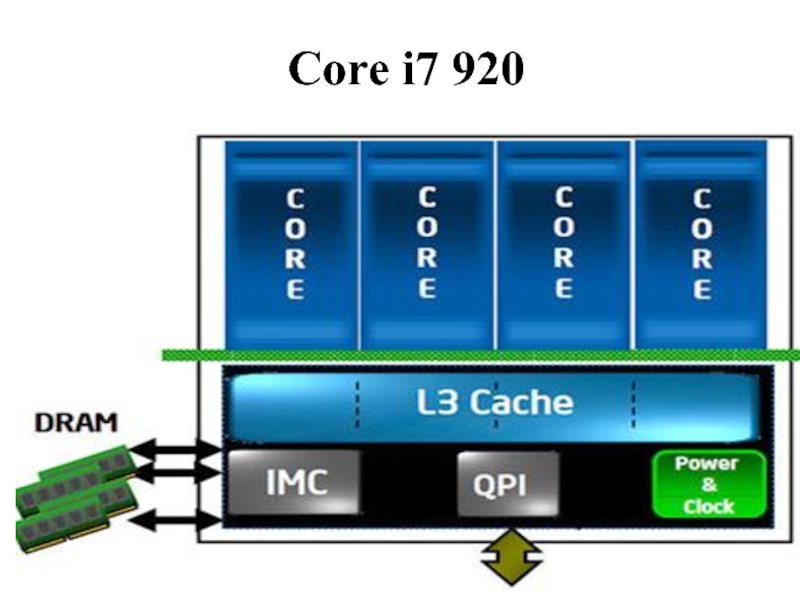

- 139. Core i7 920

- 140. Core i7 920 Трёхканальный контроллер памяти DDR3

- 141. Core i7 920 Управление энергопотреблением

- 142. Core i7 920 Управление энергопотреблением Технология

- 143. Подсистема кэширования L2 является «персональной собственностью»

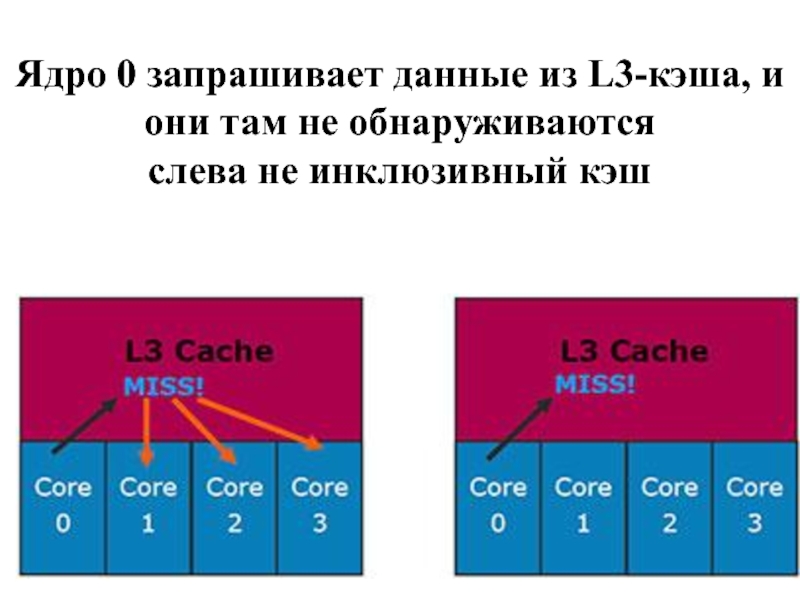

- 144. Ядро 0 запрашивает данные из L3-кэша, и они там не обнаруживаются слева не инклюзивный кэш

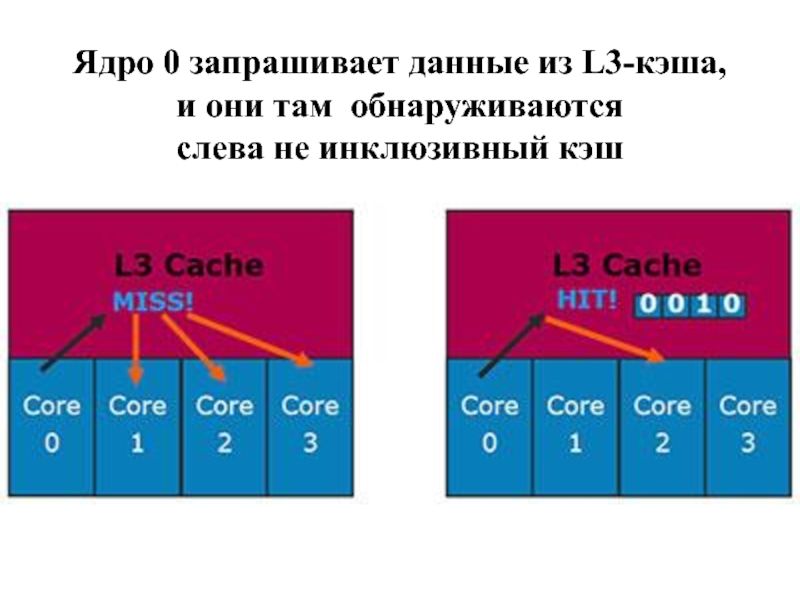

- 145. Ядро 0 запрашивает данные из L3-кэша, и они там обнаруживаются слева не инклюзивный кэш

Слайд 1Концепция машины с хранимой в памяти программой

Определения:

Вычислительная машина – совокупность

Алгоритм – одно из фундаментальных понятий математики и вычислительной техники. Международная организация стандартов (ISO) формулирует понятие алгоритм как «конечный набор предписаний, определяющий решение задачи посредством конечного количества операций»

Слайд 2Основными свойствами алгоритма являются: дискретность, определенность, массовость и результативность.

Дискретность выражается в

Свойство определенности означает, что в алгоритме указано все, что должно быть сделано, причем ни одно из действий не должно трактоваться двояко.

Слайд 3Массовость алгоритма подразумевает его применимость к множеству значений исходных данных, а

Наконец, результативность алгоритма состоит в возможности получения результата за конечное число шагов.

Рассмотренные свойства алгоритмов предопределяют возможность их реализации на ВМ, при этом процесс, порождаемый алгоритмом, называют вычислительным процессом.

Слайд 4В основе архитектуры современных ВМ лежит представление алгоритма решения задачи в

ВМ, где определенным образом закодированные команды программы хранятся в памяти, известна под названием вычислительной машины с хранимой в памяти программой. Идея принадлежит создателям вычислителя ENIАС Эккерту, Мочли и фон Нейману.

Слайд 5Сущность фон-неймановской концепции вычислительной машины можно свести к четырем принципам:

двоичного кодирования;

программного управления;

однородности памяти;

адресности

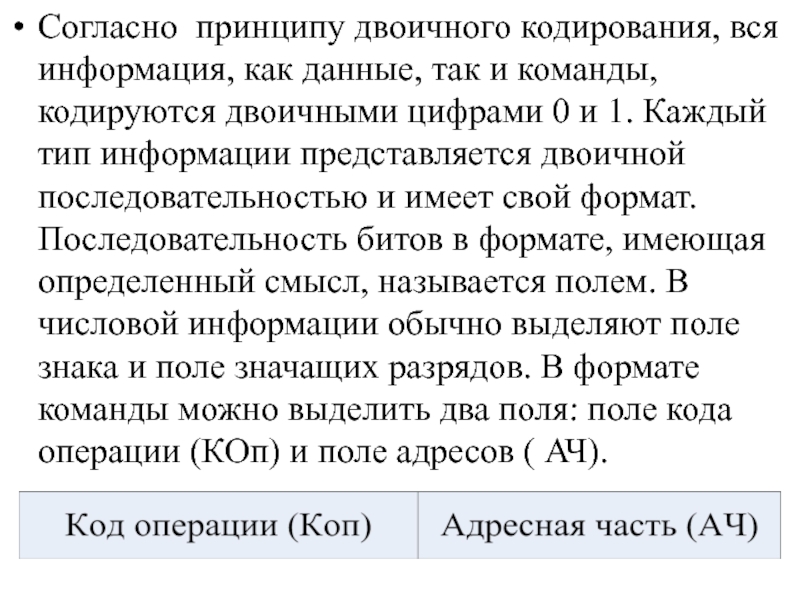

Слайд 6Согласно принципу двоичного кодирования, вся информация, как данные, так и команды,

Слайд 7Код операции представляет собой указание, какая операция должна быть выполнена, и

Вид адресной части и число составляющих ее адресов зависят от типа команды: в командах преобразования данных АЧ содержит адреса объектов обработки (операндов) и результата; в командах изменения порядка вычислений – адрес следующей команды программы; в командах ввода/вывода – номер устройства ввода/вывода. Адресная часть также задается с помощью m-разрядной двоичной комбинации. Таким образом, команда в вычислительной машине имеет вид (r+m)-разрядной двоичной комбинации.

Слайд 8Принцип программного управления

Все вычисления, предусмотренные алгоритмом решения задачи, должны быть

Слайд 9Принцип однородности памяти

Команды и данные хранятся в одной и той же

Слайд 10Концепция вычислительной машины, изложенная в статье фон Неймана, предполагает единую память

Слайд 11Принцип адресности

Структурно основная память состоит из пронумерованных ячеек, причем процессору в

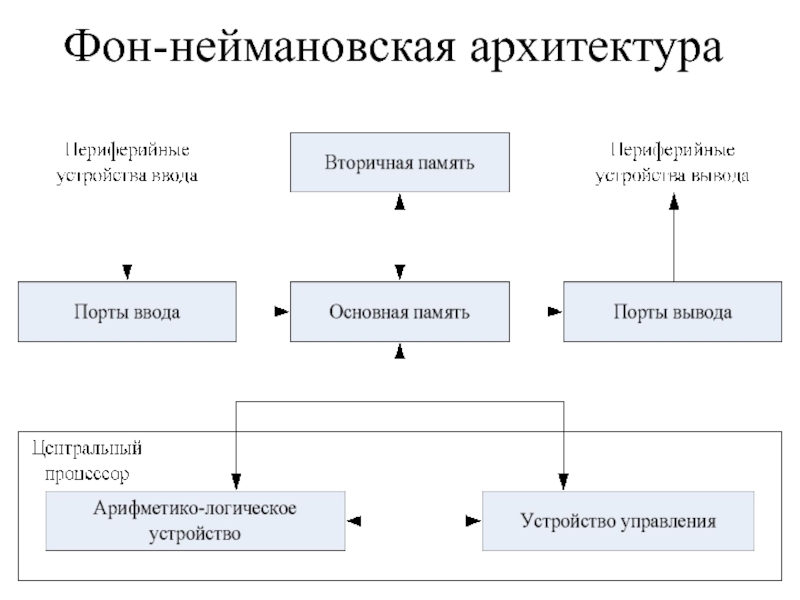

Слайд 13Фон Неймана определил основные устройства ВМ, с помощью которых должны быть

В любой ВМ имеются средства для ввода программ и данных к ним. Информация поступает из подсоединенных к ЭВМ периферийных устройств (ПУ) ввода. Результаты вычислений выводятся на периферийные устройства вывода. Связь и взаимодействие ВМ и ПУ обеспечивают порты ввода и порты вывода. Термином порт обозначают аппаратуру сопряжения периферийного устройства с ВМ и управления им. Совокупность портов ввода и вывода называют устройством ввода/вывода (УВВ) или модулем ввода/вывода ВМ (МВВ).

Слайд 14Введенная информация сначала запоминается в основной памяти, а затем переносится во

Слайд 15Для таких ЗУ характерна энергозависимость – хранимая информация теряется при отключении

Размер ячейки основной памяти обычно принимается равным 8 двоичным разрядам – байту. Для хранения больших чисел используются 2,4 или 8 байтов, размещаемых в ячейках с последовательными адресами. В этом случае за адрес числа часто принимается адрес его младшего байта.

Слайд 16Для долговременного хранения больших программ и массивов данных в ВМ обычно

Слайд 17Устройство управления (УУ) – важнейшая часть ВМ, организующая автоматическое выполнение программ

Слайд 18Пересылка информации между любыми элементами ВМ инициируется своим сигналом управления (СУ),

Слайд 19Еще одной неотъемлемой частью ВМ является арифметико-логическое устройство (АЛУ). АЛУ обеспечивает

Слайд 20Флаги могут анализироваться в УУ с целью принятия решения о дальнейшей

УУ и АЛУ тесно взаимосвязаны и их обычно рассматривают как единое устройство, известное как центральный процессор (ЦП) или просто процессор. Помимо УУ и АЛУ в процессор входит также набор регистров общего назначения (РОН), служащих для промежуточного хранения информации в процессе ее обработки.

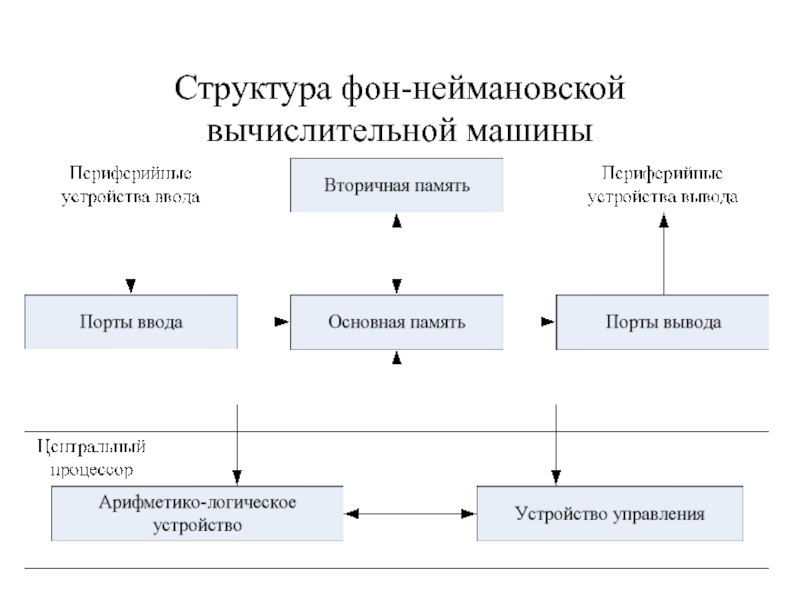

Слайд 22В настоящее время примерно одинаковое распространение получили два способа построения вычислительных

Типичным представителем первого способа может служить классическая фон-неймановская ВМ. В ней между взаимодействующими устройствами (процессор, память, устройство ввода/вывода) имеются непосредственные связи. Особенности связей (число линий в шинах, пропускная способность и т. п.) определяются видом информации, характером и интенсивностью обмена. Достоинством архитектуры с непосредственными связями можно считать возможность развязки «узких мест» путем улучшения структуры и характеристик только определенных связей, что экономически может быть наиболее выгодным решением.

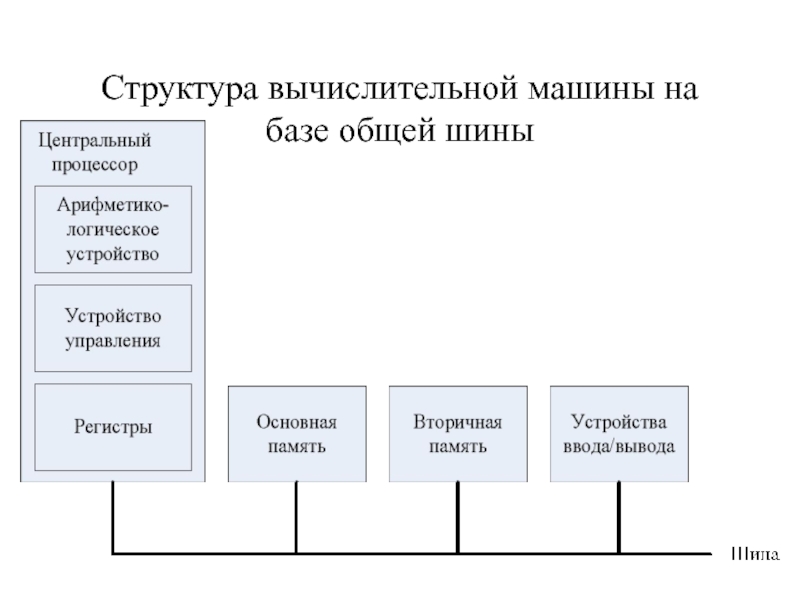

Слайд 24У фон-неймановских ВМ таким «узким местом» является канал пересылки данных между

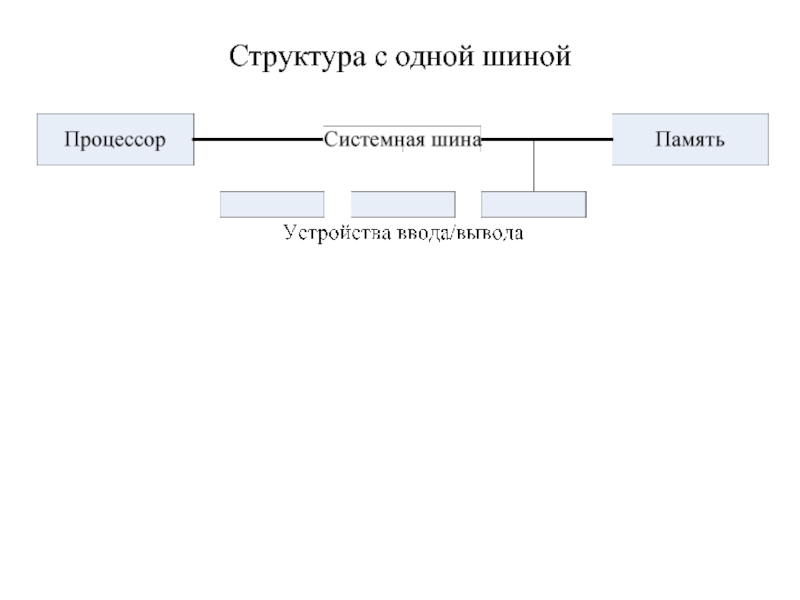

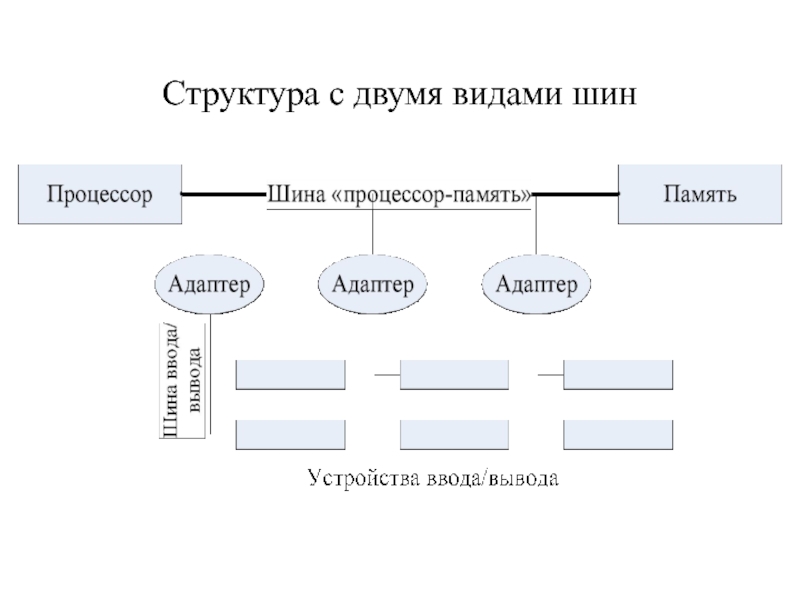

В варианте с общей шиной все устройства вычислительной машины подключены к магистральной шине, служащей единственным трактом для потоков команд, данных и управления. Наличие общей шины существенно упрощает реализацию ВМ, позволяет легко менять состав и конфигурацию машины.

Слайд 26Благодаря этим свойствам шинная архитектура получила широкое распространение в мини и

Слайд 27В целом, при сохранении фон-неймановской концепции последовательного выполнения команд программы шинная

Слайд 32Системой команд вычислительной машины называют полный перечень команд, которые способна выполнять

Хронология развития архитектур системы команд

Слайд 34Стековая архитектура

Стеком называется память, по своей структурной организации отличная от основной

Стек образует множество логически взаимосвязанных ячеек ,взаимодействующих по принципу «последним вошел, первым вышел» (LIFO, Last In First Out).

Слайд 36Верхнюю ячейку называют вершиной стека. Для работы со стеком предусмотрены две

Слайд 38Для выполнения арифметической или логической операции на вход АЛУ подается информация,

Слайд 39К достоинствам АСК на базе стека следует отнести возможность сокращения адресной

С другой стороны, стековая АСК по определению не предполагает произвольного доступа к памяти, из-за чего компилятору трудно создать эффективный программный код, хотя создание самих компиляторов упрощается. Кроме того, стек становится «узким местом» ВМ в плане повышения производительности.

Слайд 40Аккумуляторная архитектура

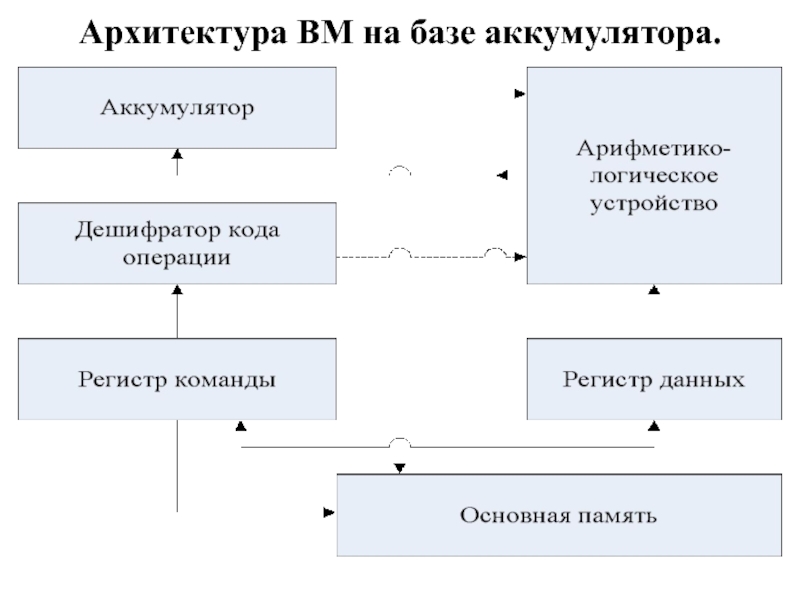

Архитектура на базе аккумулятора исторически возникла одной из первых. В

Слайд 42Для выполнения операции в АЛУ производится считывание одного из операндов из

Достоинствами аккумуляторной АСК можно считать короткие команды и простоту декодирования команд. Однако наличие всего одного регистра порождает многократные обращения к основной памяти.

Слайд 43Регистровая архитектура

В машинах данного типа процессор включает в себя массив регистров

Размер регистров обычно фиксирован и совпадает с размером машинного слова. К любому регистру можно обратиться, указав его номер. Количество РОН в архитектурах типа CISC обычно невелико (от 8 до 32), и для представления номера конкретного регистра необходимо не более пяти разрядов, благодаря чему в адресной части команд обработки допустимо одновременно указать номера двух, а зачастую и трех регистров (двух регистров операндов и регистра результата).

Слайд 44RISC-архитектура предполагает использование существенно большего числа РОН (до нескольких сотен), однако

Регистровая архитектура допускает расположение операндов в одной из двух запоминающих сред: основной памяти или регистрах. С учетом возможного размещения операндов в рамках регистровых АСК выделяют три подвида команд обработки:

регистр-регистр;

регистр-память;

память-память.

Слайд 45В варианте «регистр-регистр» операнды могут находиться только в регистрах. В них

Слайд 46К достоинствам регистровых АСК следует отнести: компактность получаемого кода, высокую скорость

Примерами машин на базе РОН могут служить CDC 6600, IBM 360/3/0, PDP-11, все современные персональные компьютеры. Правомочно утверждать, что в наши дни этот вид архитектуры системы команд является преобладающим.

Слайд 47Архитектура с выделенным доступом к памяти

В архитектуре с выделенным доступом к

Слайд 48В архитектуре отсутствуют команды обработки, допускающие прямое обращение к основной памяти.

Слайд 49Классификация по составу и сложности команд

Современная технология программирования ориентирована на

Слайд 50Пытаясь преодолеть семантический разрыв, разработчики вычислительных машин в настоящее время выбирают

архитектуру с полным набором команд: CISC (Complex Instruction Set Computer);

архитектуру с сокращенным набором команд: RISC (Reduced Instruction Set Computer);

архитектуру с командными словами сверхбольшой длины: VLIW (Very Long Instruction Word).

Слайд 51В вычислительных машинах типа CISC проблема семантического разрыва решается за счет

Для CISC-архитектуры типичны:

наличие в процессоре сравнительно небольшого числа регистров общего назначения;

большое количество машинных команд, некоторые из них аппаратно реализуют сложные операторы ЯВУ;

разнообразие способов адресации операндов; множество форматов команд различной разрядности;

наличие команд, где обработка совмещается с обращением к памяти.

Слайд 52К типу CISC можно отнести практически все ВМ, выпускавшиеся до середины

Рассмотренный способ решения проблемы семантического разрыва вместе с тем ведет к усложнению аппаратуры ВМ, главным образом устройства управления, что, в свою очередь, негативно сказывается на производительности ВМ в целом.

Указанные недостатки привели к созданию RISC архитектуре команд.

Слайд 53Термин RISC впервые был использован Д. Паттерсоном и Д. Дитцелем в

Слайд 54Элементы RISC-архитектуры впервые появились в вычислительных машинах CDC 6600 и суперЭВМ

Отметим, что в последних микропроцессорах фирмы Intel и AMD широко используются идеи, свойственные RISC-архитектуре, так что многие различия между CISC и RISC постепенно стираются.

Слайд 55Помимо CISC- и RISC-архитектур в общей классификации был упомянут еще один

Слайд 56Основные направления в развитии архитектур процессоров

Конвейеризация вычислений

Суперконвейерные процессоры

Суперскалярные

Слайд 57Конвейер команд

Идея конвейера команд была предложена в 1956 году академиком

Выборка команды (ВК). Чтение очередной команды из памяти и занесение ее в регистр команды.

Декодирование команды (ДК). Определение кода операции и способов адресации операндов.

Слайд 583. Вычисление адресов операндов (ВА). Вычисление исполнительных адресов каждого из операндов

4. Выборка операндов (ВО). Извлечение операндов из памяти. Эта операция не нужна для операндов, находящихся в регистрах.

5. Исполнение команды (ИК). Исполнение указанной операции.

6. Запись результата (ЗР). Занесение результата в память.

Слайд 60На рисунке показан конвейер с шестью ступенями, соответствующими шести этапам цикла

Слайд 61Суперконвейер

Разбиение каждой ступени конвейера на n «подступеней» при одновременном повышении тактовой

Включение в состав процессора n конвейеров, работающих с перекрытием.

Слайд 63Каждая из шести ступеней стандартного конвейера разбита на две более простые

В сущности, суперконвейеризация сводится к увеличению количества ступеней конвейера как за счет добавления новых ступеней, так и путем дробления имеющихся ступеней на несколько простых подступеней. Главное требование — возможность реализации операции в каждой подступени наиболее простыми техническими средствами, а значит, с минимальными затратами времени.

Слайд 64Структурный риск - попытка нескольких команд одновременно обратиться к одному и

Риск по данным - взаимосвязь команд по данным.

Риск по управлению - неоднозначность при выборке следующей команды в случае команд перехода.

Классификация рисков конвейеров

Слайд 65Структурный риск имеет место, когда несколько команд, находящихся на разных ступенях

Слайд 66«Чтение после записи» (ЧПЗ): команда j читает X до того, как

«Запись после чтения» (ЗПЧ): команда j запи -сывает новое значение X до того как команда i успела прочитать X, то есть команда i ошибочно получит новое значение X вместо старого.

«Запись после записи» (ЗПЗ): команда j записывает новое значение X прежде, чем команда i успела записать в качестве X свое значение, то есть X ошибочно содержит i-е значение X вместо j-го

Три типа конфликтов по данным

Слайд 67Для решения этих проблем применяют предвыборку команд и их спекулятивное выполнение.

Слайд 69Пусть команда 3 – это условный переход к команде 15. До

Слайд 70 Статическое предсказание переходов.

Динамическое предсказание переходов.

Классификации схем предсказания переходов

Слайд 71Переход происходит всегда.

Переход не происходит никогда.

Предсказание определяется по результатам профилирования.

Предсказание определяется

Предсказание зависит от направления перехода.

Стратегии статического предсказания для команд УП

Слайд 72 Предполагается, что каждая команда условного перехода в программе обязательно завершится переходом,

Переход происходит всегда

Слайд 73 Предполагается, что ни одна из команд условного перехода в программе никогда

Переход не происходит никогда

Слайд 74 По результатам профилирования, тем командам, которые чаще завершались переходом, назначается стратегия

Предсказание определяется по результатам профилирования

Слайд 75 Для одних команд предполагается, что переход произойдет, для других — его

Предсказание определяется кодом операции команды перехода

Слайд 76Одноуровневые или бимодальные.

Двухуровневые или коррелированные.

Гибридные.

Асимметричные.

Стратегии динамического предсказания для команд УП

Слайд 77

Одноуровневые схемы предсказания переходов

Идея одноуровневых схем предсказания, сводится к отделению

Слайд 78 Предсказание осуществляется на основе предыдущих исходов как команды УП, для которой

Двухуровневые схемы предсказания переходов

Слайд 79 Гибридные схемы объединяют в себе несколько различных механизмов предсказания — элементарных

Гибридные схемы предсказания переходов

Слайд 80 Асимметричная схема сочетает в себе черты гибридных и коррелированных схем

Асимметричные схемы предсказания переходов

Слайд 81Суперскалярность

Суперскалярным (этот термин впервые был использован в 1987 году) называется

Слайд 83Блок выборки команд извлекает команды из основной памяти через кэш-память команд.

Блок декодирования расшифровывает код операции, содержащийся в извлеченных из кэш-памяти командах. Блоки диспетчеризации и распределения взаимодействуют между собой и в совокупности играют в суперскалярном процессоре роль контроллера трафика. Оба блока хранят очереди декодированных команд. Очередь блока распределения часто рассредоточивается по несколько самостоятельным буферам – накопителям команд или схемам резервирования,– предназначенным для хранения команд, которые уже декодированы, но еще не выполнены.

Слайд 84Каждый накопитель команд связан со своим функциональным блоком (ФБ), поэтому число

В дополнение к очереди, блок диспетчеризации хранит также список свободных функциональных блоков, называемый табло (scoreboard). Табло используется для отслеживания состояния очереди распределения. Один раз за цикл блок диспетчеризации извлекает команды из своей очереди, считывает из памяти или регистров операнды этих команд, после чего, в зависимости от состояния табло, помещает команды и значения операндов в очередь распределения.

Слайд 85Эта операция называется выдачей команд. Блок распределения в каждом цикле проверяет

Блок исполнения состоит из набора функциональных блоков. Примерами ФБ могут служить целочисленные операционные блоки, блоки умножения и сложения с плавающей запятой, блок доступа к памяти. Когда исполнение команды завершается, ее результат записывается и анализируется блоком обновления состояния, который обеспечивает учет полученного результата теми командами в очередях распределения, где этот результат выступает в качестве одного из операндов.

Слайд 89БФА - блок формирования адреса

БРЗ - блок регистров замещения

FPU - АЛУ

MMX - блок для выполнения мультимедийных инструкций

SEE - блок для выполнения потоковых (SIMD) инструкций

ALU - АЛУ для целых чисел

Слайд 90Hyper-threading ( Hyper-threading — Гиперпоточность)

В процессорах с использованием этой технологии каждый

Слайд 91Потоки

С точки зрения процессора, поток – это набор инструкций, которые необходимо

Когда поток отправляется на процессор, адрес памяти потока загружается в этот счетчик команд

После каждой инструкции значение этого регистра увеличивается. Процесс выполняется до завершения потока.

По окончании выполнения потока, в счетчик команд заносится адрес следующей инструкции, которую нужно выполнить.

Потоки могут прерывать друг друга, при этом процессор запоминает значение счетчика команд в стеке и загружает в счетчик новое значение.

Слайд 92Развитие микропроцессоров

CMP (Chip Multi Processing -многоядерность )

SMT (Simultaneous MultiThreading -многонитевая

EPIC (Explicitly Parallel Instruction Computing - очень длинное командное слово )

Слайд 93Направление CMP

Создание на одном кристалле нескольких микропроцессоров и организация их работы

Слайд 94Направление SMT

На одном процессоре осуществляется запуск нескольких задач одновременно, при

Слайд 95Архитектура EPIC

На входе процессора последовательность больших команд, состоящих из нескольких простых

Преимущества перед суперскалярами:

Меньше места на процессоре тратится на управление, больше остается на ресурсы: регистры, исполнительные устройства, кэш-память.

Более тщательное планирование дает лучшее заполнение исполнительных устройств (больше команд за такт).

Слайд 96Недостатки

Значительно усложняются компиляторы

Производительность микропроцессора во многом определяется качеством компилятора

Увеличивается сложность отладки

Слайд 99Архитектура Pentium M

Мобильная версия

RISC архитектура как в Pentium III, IV

Пять

Улучшенный механизм предсказания ветвлений и аппаратная предвыборка данных

Технология micro-ops fusion

Выделенный менеджер стека

Энергосберегающий кеш второго уровня

Технология SpeedStep III

Слайд 103Основные особенности архитектуры Intel Core

Технология широкого динамического выполнения (Wide Dynamic Execution)

Интеллектуальная система управления энергопотреблением (Intelligent Power Capability)

Улучшенный "умный" кэш (Advanced Smart Cache)

"Умный" доступ к памяти (Smart Memory Access)

Улучшенная работа с цифровым медиа-содержанием (Advanced Digital Media Boost)

Слайд 104Технология широкого динамического выполнения

Призвана обеспечить выполнение большего количества команд за каждый

Слайд 109Интеллектуальная система управления энергопотреблением

Технологии стробирования тактовых импульсов (clock gating) и "спящих"

Слайд 111Улучшенный "умный" кэш

Два ядра совместно используют кэш объёмом 2 или 4

Слайд 113"Умный" доступ к памяти

Улучшенная предварительная выборка

Каждый двуядерный процессор Core оснащён восемью

Слайд 114"Умный" доступ к памяти

Улучшенная предварительная выборка

Блоки предварительной выборки памяти постоянно оценивают

Слайд 115"Умный" доступ к памяти

Устранение неоднозначностей памяти

Блок устранения неоднозначностей памяти выбирает операции

Слайд 118Улучшенная работа с цифровым медиа-содержанием

АЛУ обычно разбивает инструкции на два блока,

Слайд 121Архитектура Core i3 - i7

Основной чертой новой архитектуры стала модульность

Ядро это классический одноядерный x86-процессор: он состоит из исполнительного ядра, кэша 1-го уровня размером 64 КБ, поделенного на 2 равные части для данных и инструкций и кэша 2-го уровня размером 256 КБ.

Слайд 122Прочие блоки могут быть следующими:

разделяемый кэш 3-го уровня;

контроллер памяти;

контроллер шины QPI

контроллер шины PCI Express;

контроллер энергопотребления (PCU) и генератор частот;

контроллер интегрированной графики

Слайд 123Core i3

Компания Intel разработала в 2006 году концепцию Tick-Tock (тик-так). Суть

Слайд 125Core i3

Самое основное отличие новых процессоров от предыдущих версий – это

Слайд 127ТЕХНОЛОГИИ CORE i3

Новая улучшенная версия Hyper-threading Simultaneous MultiThreading (SMT). Благодаря SMT

Слайд 129ТЕХНОЛОГИИ CORE i3

Для слежения за состоянием процессора, в нем был размещен

Слайд 130ТЕХНОЛОГИИ CORE i3

Линейка процессоров Core i3, в отличии от более дорогих

Слайд 131ТЕХНОЛОГИИ CORE i3

Virtualization Technology (VT) - Аппаратная виртуализация, позволяет запускать на

Слайд 132ТЕХНОЛОГИИ CORE i3

Execute Disable Bit обеспечивает защиту от вредоносных атак, направленных

Слайд 133ТЕХНОЛОГИИ CORE i3

Enhanced Intel SpeedStep - энергосберегающая технология Intel, вызывающая, в

Слайд 134ТЕХНОЛОГИИ CORE i3

Trusted Execution состоит из последовательно защищённых этапов обработки. В

Слайд 135ТЕХНОЛОГИИ CORE i3

Intel 64 Architecture поддерживает 64-битные вычисления, что позволяет устанавливать

Слайд 136ГРАФИЧЕСКОЕ ЯДРО

Графический чип Intel HD Graphics так же использует систему из

Слайд 137ГРАФИЧЕСКОЕ ЯДРО

Графический чип находится на общем кристалле с контроллером памяти, что

Использование технологии HD Graphics Turbo Boost. Данная разработка позволяет в зависимости от ситуации динамическим образом изменять частоту графического чипа с 133 до 667 МГц. Но при этом используется одно ограничение: суммарное тепловыделение процессора и графического чипа не должны превышать заявленных 35 Ватт. Таким образом, происходит распределение теплового пакета между CPU и GPU.

Слайд 140Core i7 920

Трёхканальный контроллер памяти DDR3 с максимальной скоростью 32 GBps

Процессорная шина Intel (QuickPath Interconnect) - 20-битная шина с топологией соединения «точка-точка», 16 бит в каждую сторону несут полезную информацию, и ещё 4 бита служат для коррекции ошибок и прочих служебных целей обеспечивает скорость передачи данных 12,8 ГБ/с в каждую сторону

Слайд 141Core i7 920

Управление энергопотреблением

частота и напряжение питания для каждого ядра

Слайд 142Core i7 920

Управление энергопотреблением

Технология Turbo Boost процессора может повышать частоту

Слайд 143Подсистема кэширования

L2 является «персональной собственностью» конкретного ядра, и оно ни с

L3 является динамически разделяемым. Более того, он является инклюзивным: данные, находящиеся в L1/L2 — обязаны присутствовать в L3.