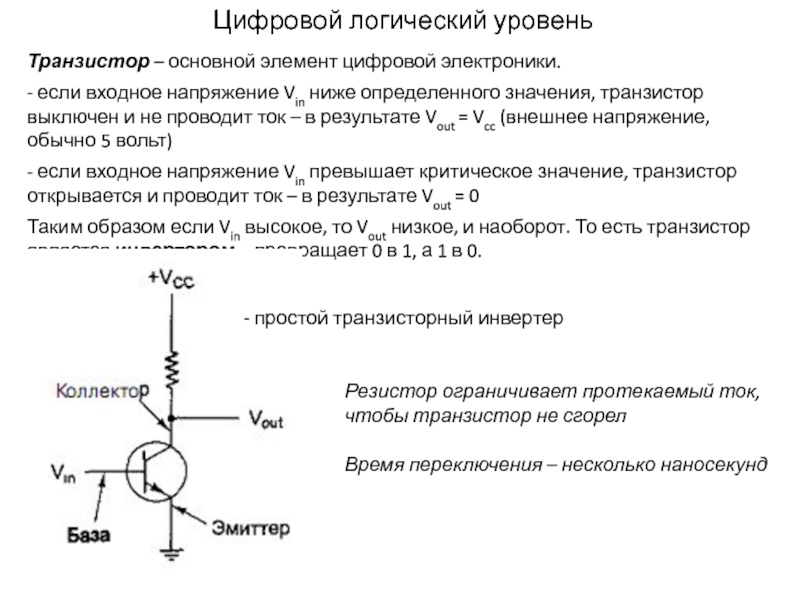

- если входное напряжение Vin превышает критическое значение, транзистор открывается и проводит ток – в результате Vout = 0

Таким образом если Vin высокое, то Vout низкое, и наоборот. То есть транзистор является инвертором – превращает 0 в 1, а 1 в 0.

- простой транзисторный инвертер

Резистор ограничивает протекаемый ток, чтобы транзистор не сгорел

Время переключения – несколько наносекунд