- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Технические средства цифровых систем автоматизации презентация

Содержание

- 1. Технические средства цифровых систем автоматизации

- 2. 1. Логические элементы цифровой автоматики

- 3. Основные логические элементы, соответствующие им логические функции алгебры логики и релейные схемы

- 4. Схемы основных логических элементов

- 5. 1. Запоминающие элементы цифровой автоматики

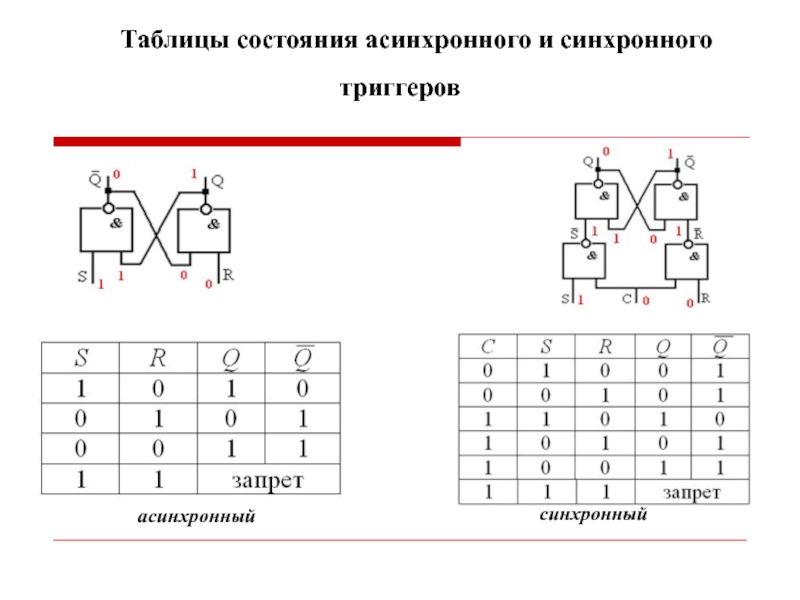

- 6. Таблицы состояния асинхронного и синхронного триггеров асинхронный синхронный

- 7. Динамический D-триггер

- 8. Таблица состояния D-триггера

- 9. 1.2. Регистры памяти Регистры,

- 10. Применяются для записи и

- 11. 1.2. Регистры памяти Последовательный регистр

- 12. Применяются для записи цифровых

- 13. 1.3. Двоичные счетчики Двоичный

- 14. На вход С первого

- 15. 1.4. Шифраторы Структура шифратора.

- 16. 1.4. Шифраторы Таблица состояния

- 17. 1.5. Дешифраторы Структура дешифратора

- 18. 1.6. Мультиплексоры Структура мультиплексора Di –

- 19. 1.7. Распределители После первого тактового импульса

- 20. 1.8. Сумматоры Структурная схема сумматора Сумматоры

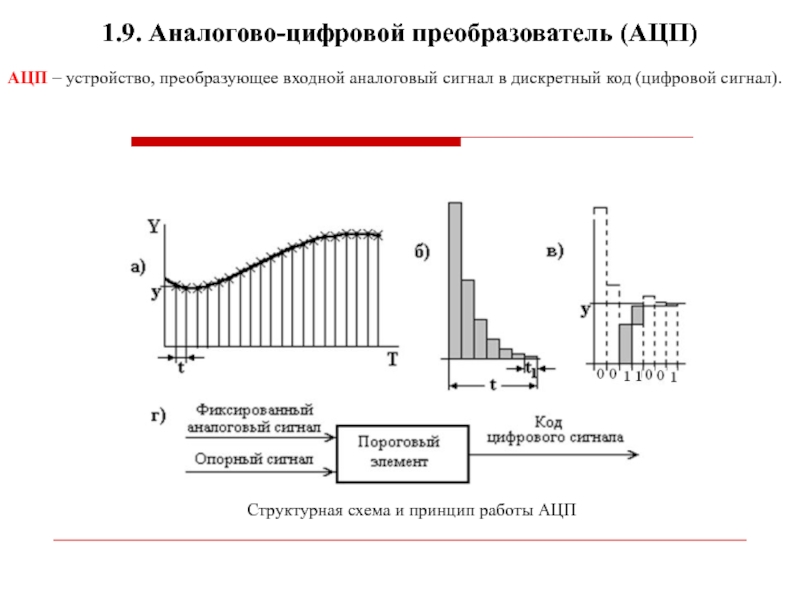

- 21. 1.9. Аналогово-цифровой преобразователь (АЦП) Структурная схема

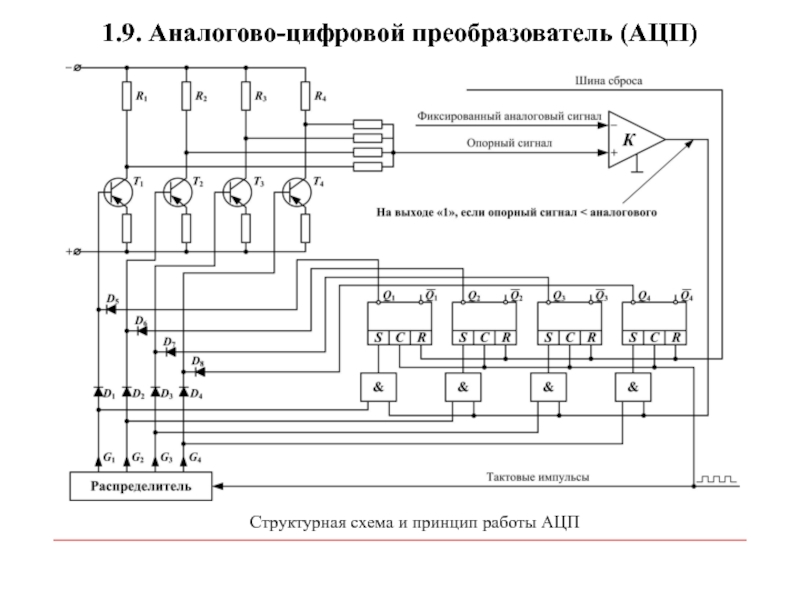

- 22. 1.9. Аналогово-цифровой преобразователь (АЦП) Структурная схема и принцип работы АЦП

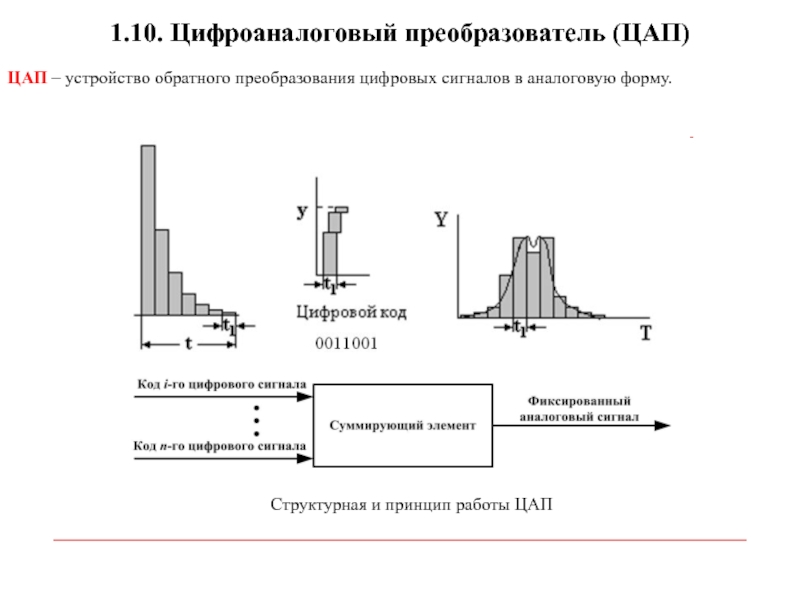

- 23. 1.10. Цифроаналоговый преобразователь (ЦАП) Структурная и

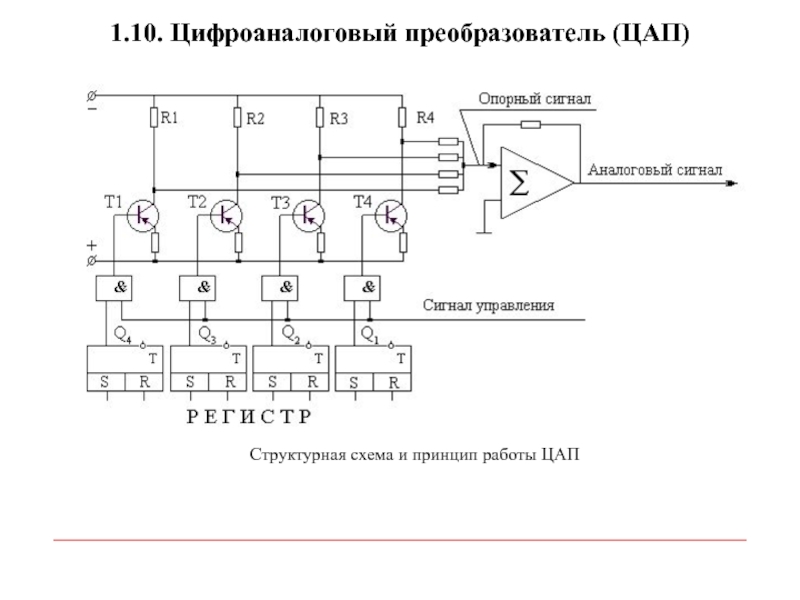

- 24. 1.10. Цифроаналоговый преобразователь (ЦАП) Структурная схема и принцип работы ЦАП

Слайд 1ТЕХНИЧЕСКИЕ СРЕДСТВА ЦИФРОВЫХ СИСТЕМ АВТОМАТИЗАЦИИ

ФГБОУ ВПО «Пермский национальный исследовательский политехнический университет»

Лекция

Слайд 21. Логические элементы цифровой автоматики

Основой систем цифровой автоматики

Как аргументы, так и функции всегда дискретны и могут принимать только одно из двух значений «истинно» или «ложно». В системах автоматики значение «истинно» является «логической единицей», «ложно» – «логическим нулем»

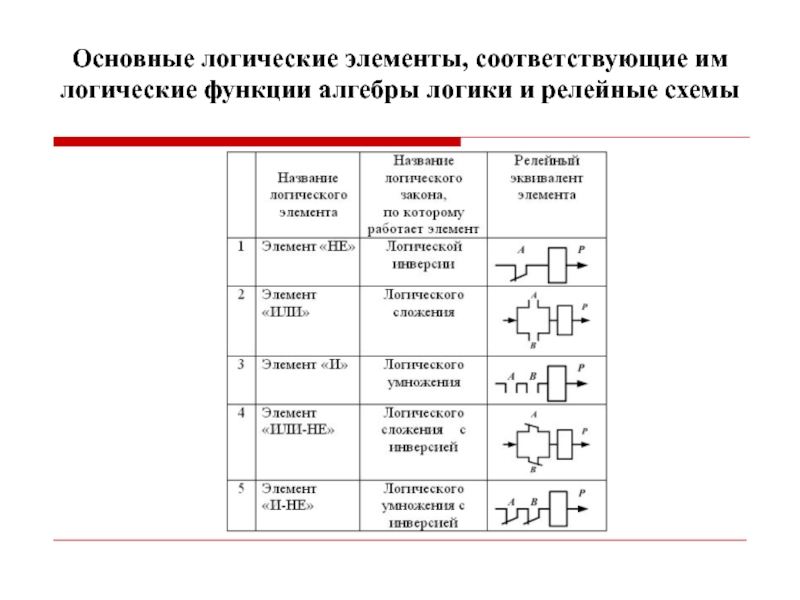

Слайд 3Основные логические элементы, соответствующие им логические функции алгебры логики и релейные

Слайд 51. Запоминающие элементы цифровой автоматики

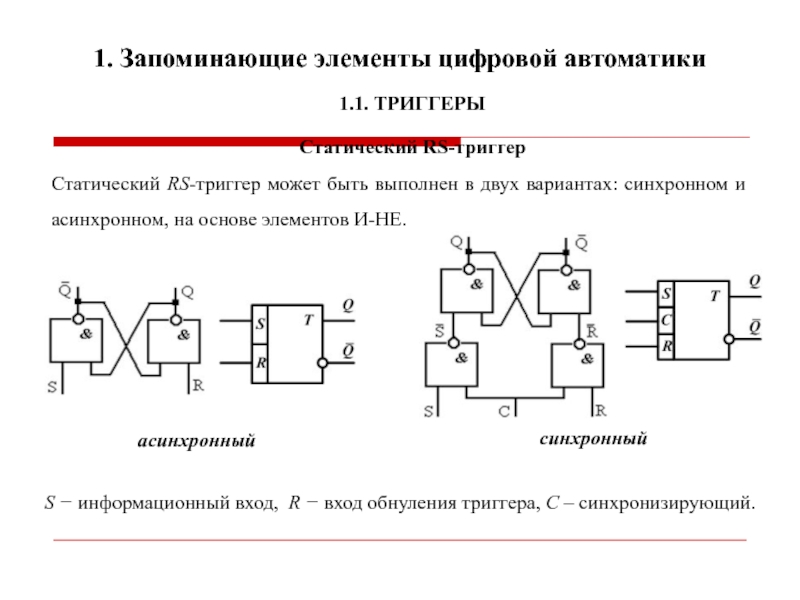

1.1. ТРИГГЕРЫ

Статический RS-триггер может быть выполнен в двух вариантах: синхронном и асинхронном, на основе элементов И-НЕ.

S − информационный вход, R − вход обнуления триггера, С – синхронизирующий.

асинхронный

синхронный

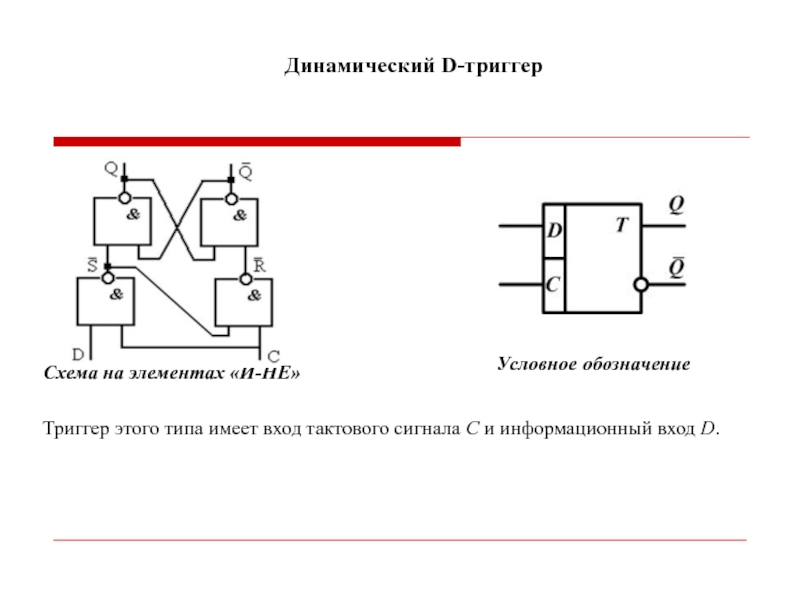

Слайд 7 Динамический D-триггер

Триггер этого типа

Схема на элементах «И-НЕ»

Условное обозначение

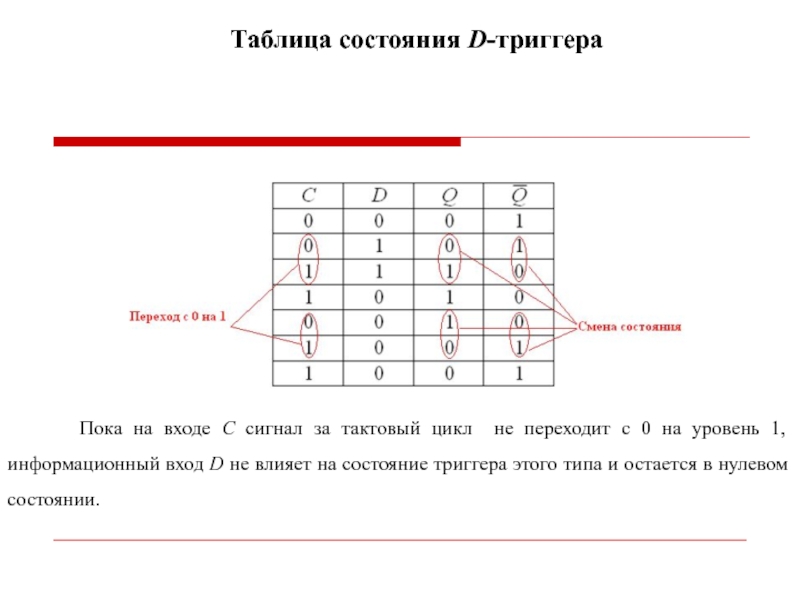

Слайд 8 Таблица состояния D-триггера

Пока на

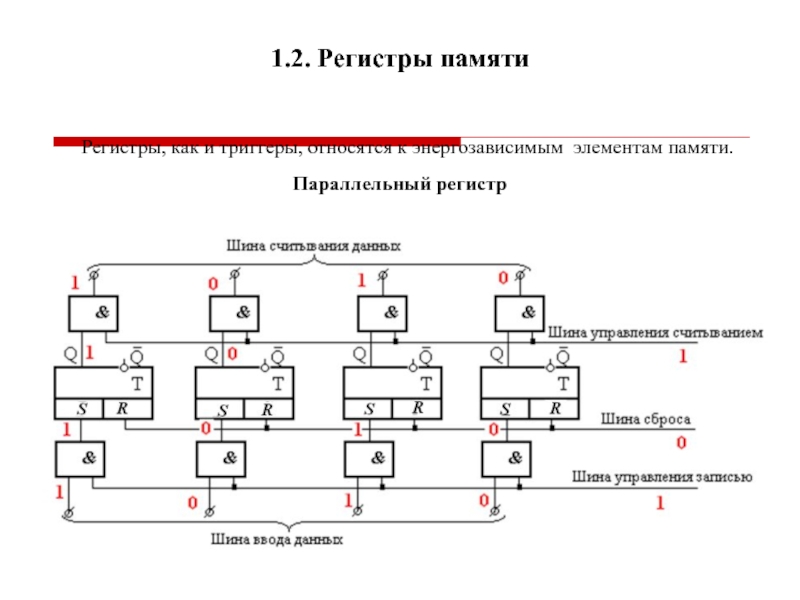

Слайд 91.2. Регистры памяти

Регистры, как и триггеры, относятся к

Параллельный регистр

Слайд 10 Применяются для записи и считывания цифровых сигналов в

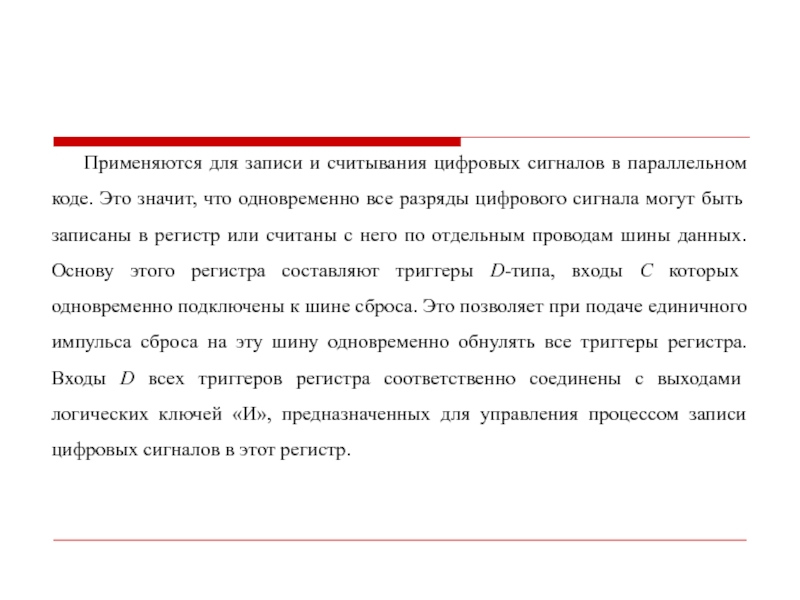

Слайд 12 Применяются для записи цифровых сигналов в последовательном коде.

Основой последовательного регистра является D-триггер.

На входы С всех триггеров регистра одновременно подаются тактовые импульсы. В это же время на вход D триггера младшего разряда подается первый символ записываемого цифрового сигнала.

1.2. Регистры памяти

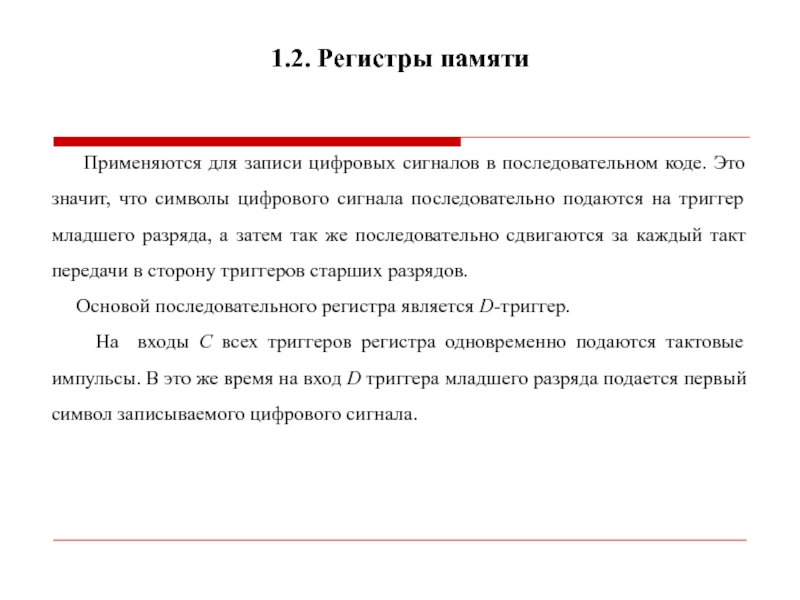

Слайд 131.3. Двоичные счетчики

Двоичный счетчик, выполнен на основе трех

При J = 1 и K = 1 триггер меняет свое состояние на противоположное в момент окончания каждого синхронизирующего сигнала.

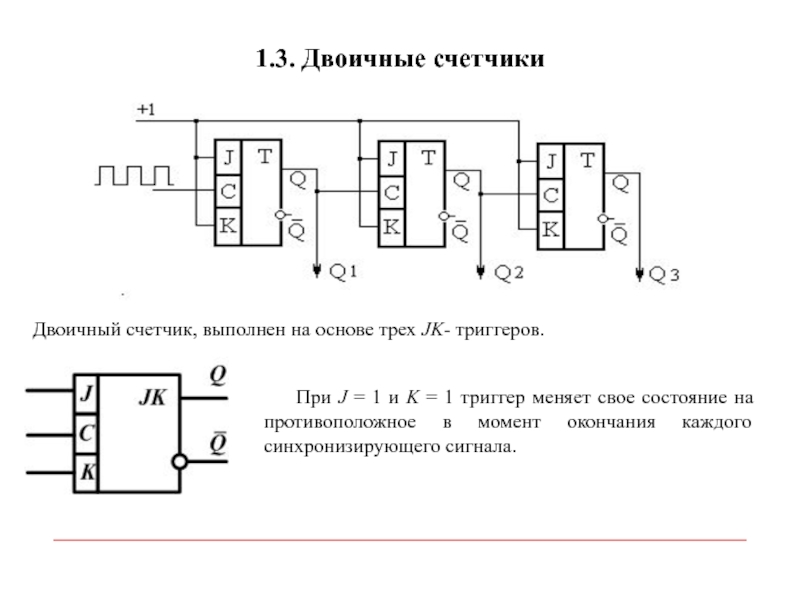

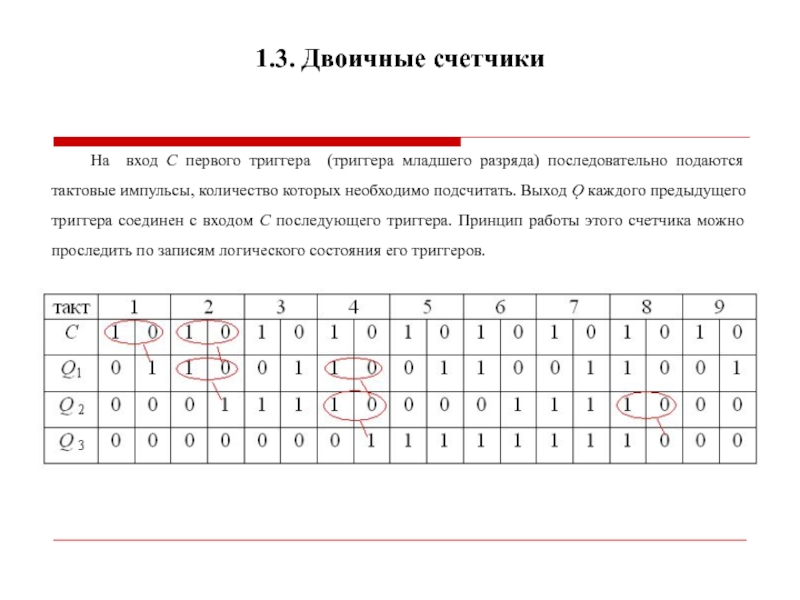

Слайд 14 На вход С первого триггера (триггера младшего разряда)

1.3. Двоичные счетчики

Слайд 151.4. Шифраторы

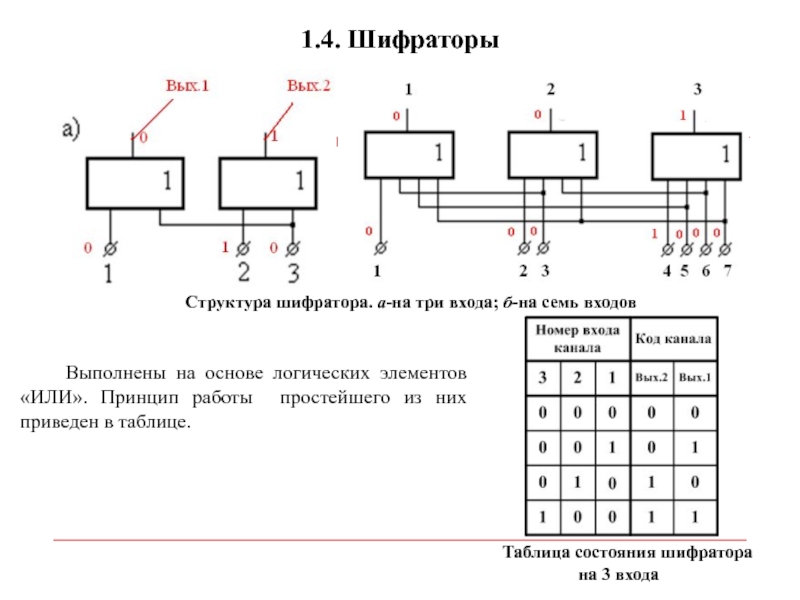

Структура шифратора. а-на три входа; б-на семь

Выполнены на основе логических элементов «ИЛИ». Принцип работы простейшего из них приведен в таблице.

Таблица состояния шифратора на 3 входа

Слайд 161.4. Шифраторы

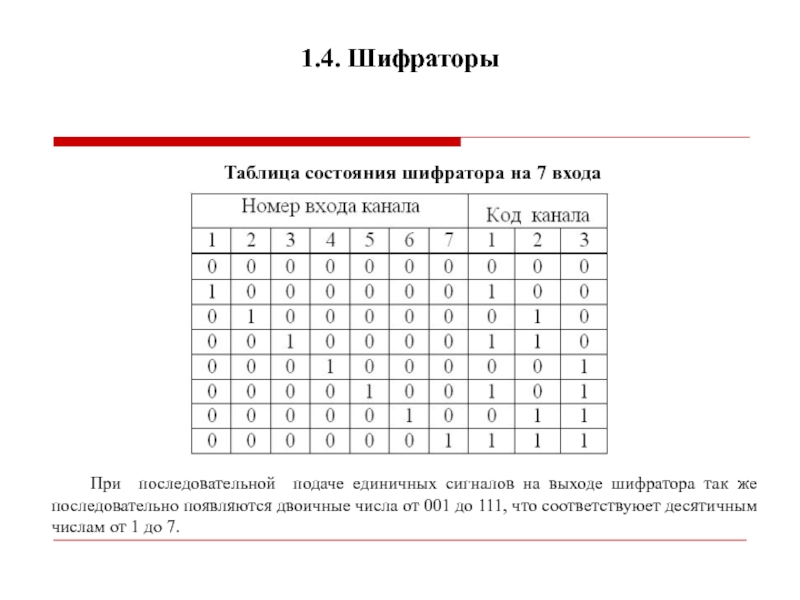

Таблица состояния шифратора на 7 входа

При последовательной

Слайд 171.5. Дешифраторы

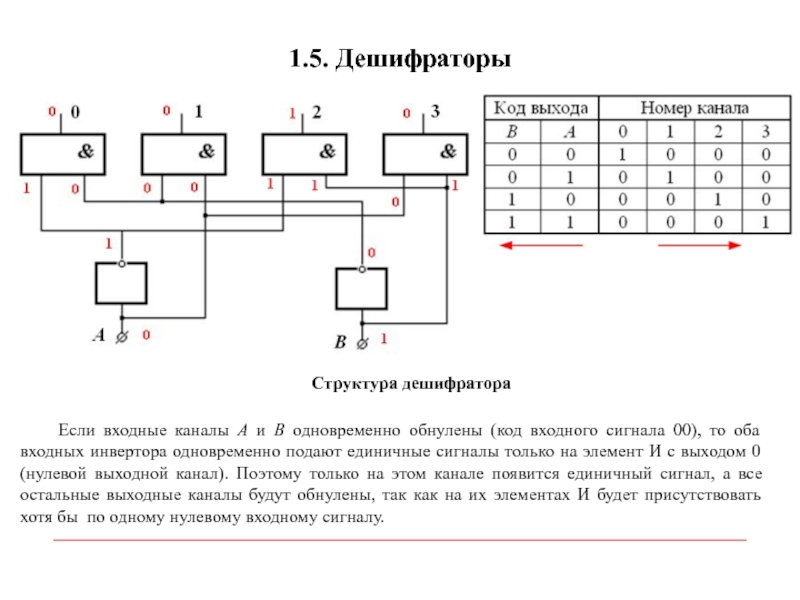

Структура дешифратора

Если входные каналы А и

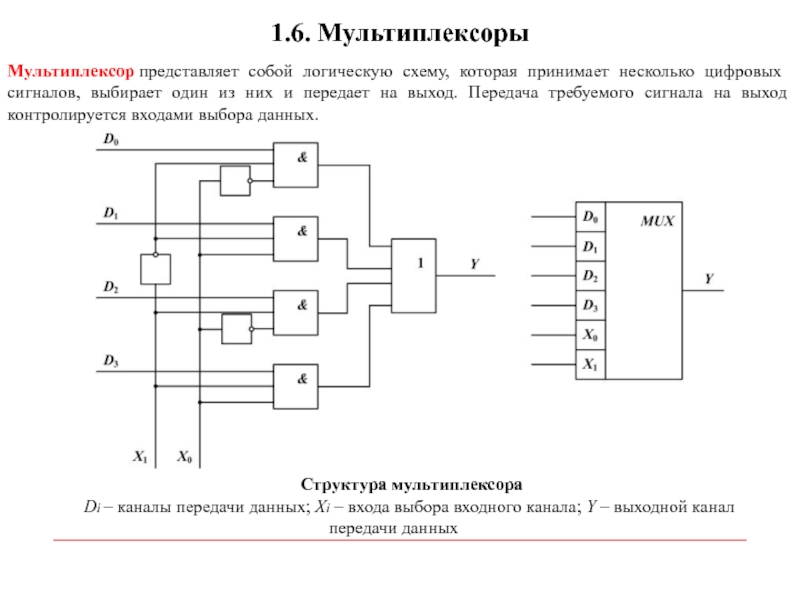

Слайд 181.6. Мультиплексоры

Структура мультиплексора

Di – каналы передачи данных; Xi – входа

Мультиплексор представляет собой логическую схему, которая принимает несколько цифровых сигналов, выбирает один из них и передает на выход. Передача требуемого сигнала на выход контролируется входами выбора данных.

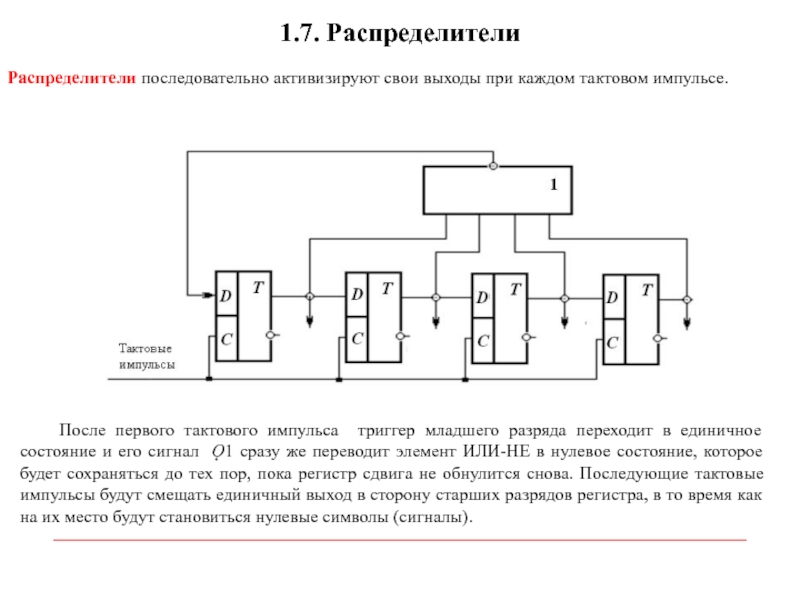

Слайд 191.7. Распределители

После первого тактового импульса триггер младшего разряда переходит в

Распределители последовательно активизируют свои выходы при каждом тактовом импульсе.

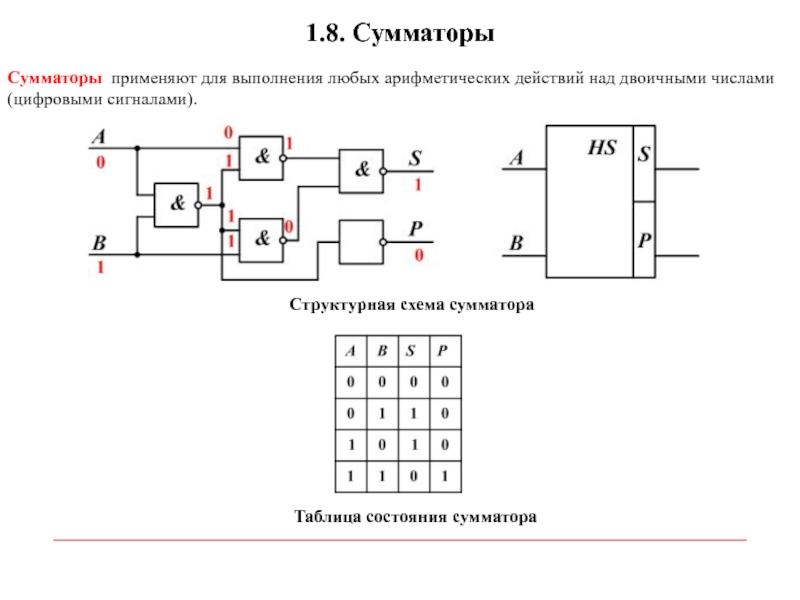

Слайд 201.8. Сумматоры

Структурная схема сумматора

Сумматоры применяют для выполнения любых арифметических действий

Таблица состояния сумматора