- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Сумматоры. Виды презентация

Содержание

- 1. Сумматоры. Виды

- 2. Двоичный сумматор Двоичный сумматор (SM) служит

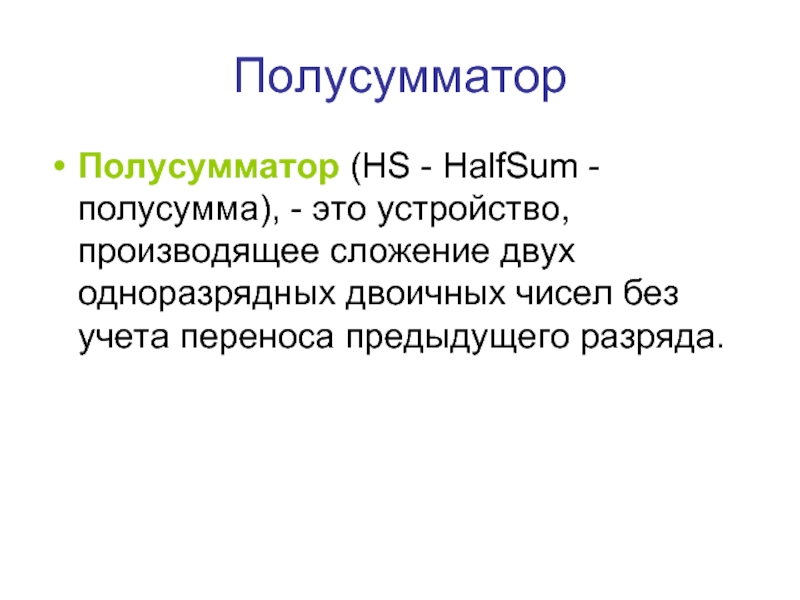

- 3. Полусумматор Полусумматор (HS - HalfSum -

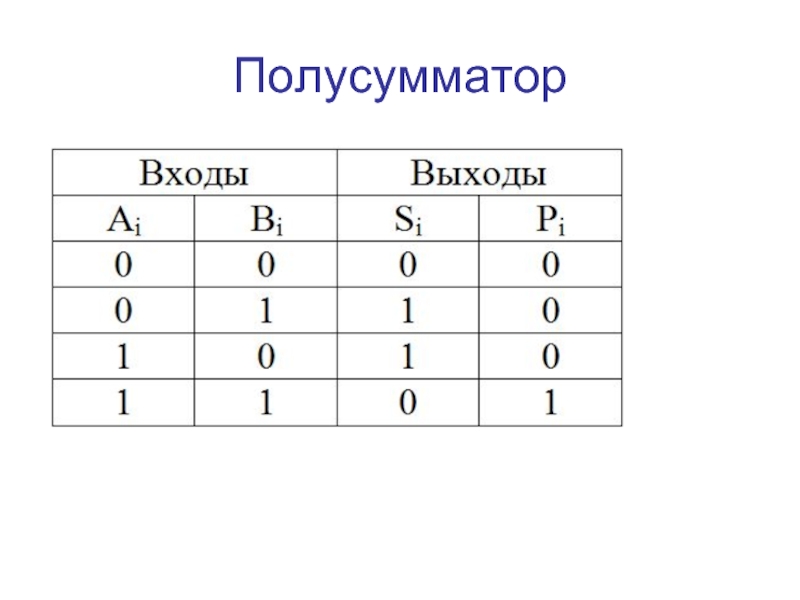

- 4. Полусумматор

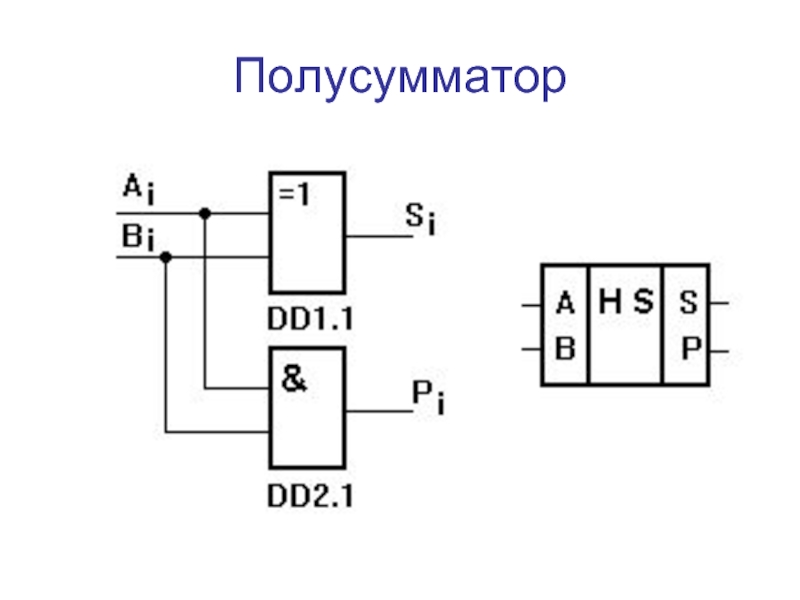

- 5. Полусумматор

- 6. Полный одноразрядный сумматор Полный одноразрядный сумматор

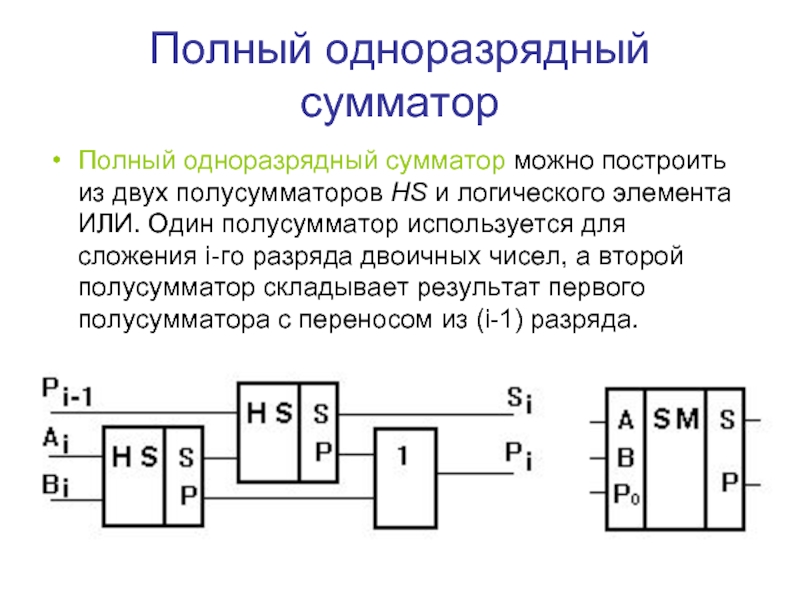

- 7. Полный одноразрядный сумматор Полный одноразрядный сумматор можно

- 8. Многоразрядный сумматор Для сложения двух многоразрядных двоичных

- 9. Многоразрядный сумматор В корпусе микросхемы К155ИМ3 четыре

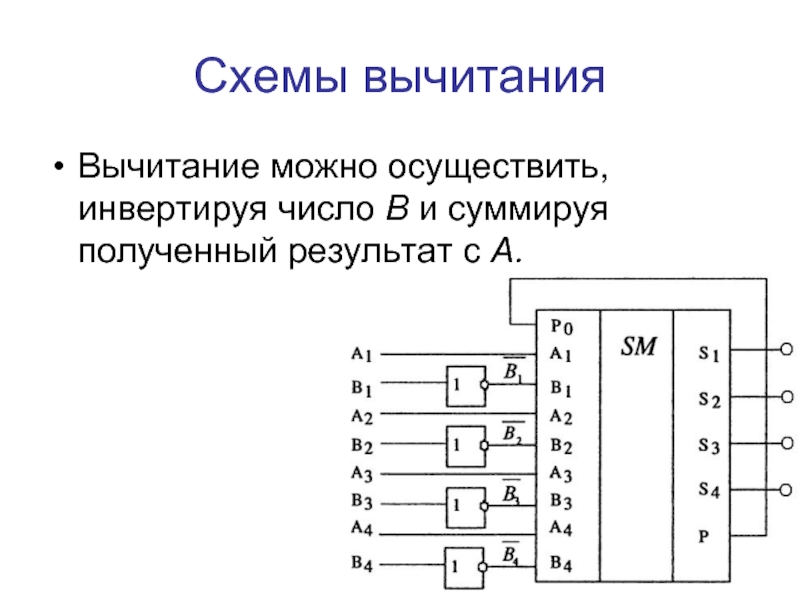

- 10. Схемы вычитания Вычитание можно осуществить, инвертируя число В и суммируя полученный результат с А.

- 11. Схемы вычитания При А > В получаем

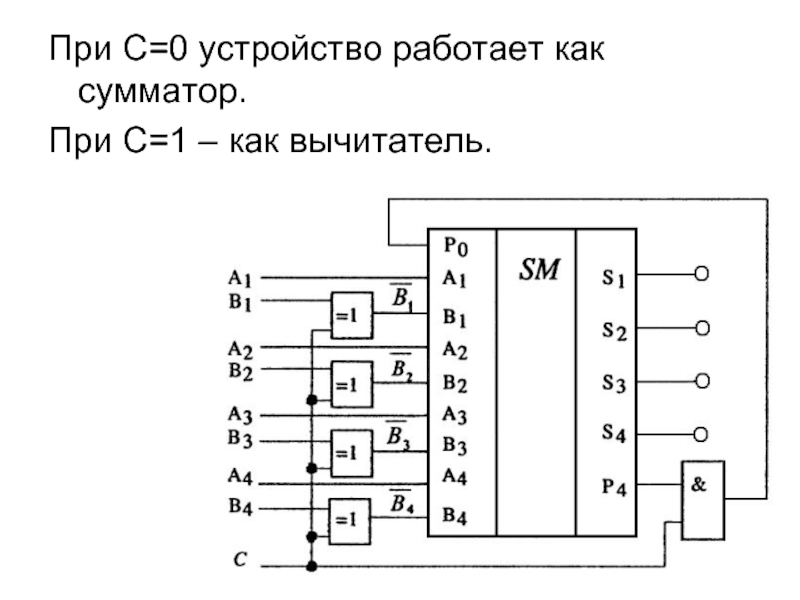

- 12. При С=0 устройство работает как сумматор. При С=1 – как вычитатель.

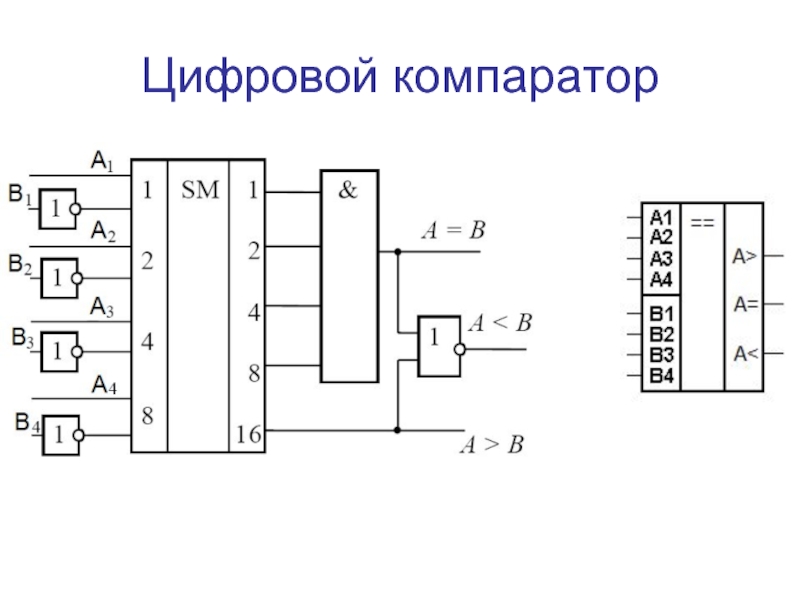

- 13. Цифровой компаратор Цифровым компаратором называют устройство, фиксирующее

- 14. Цифровой компаратор

- 15. Цифровой компаратор Компаратор, фиксирующий равнозначность кодов А

Слайд 1Сумматоры

Полусумматор

Полный одноразрядный сумматор

Многоразрядный сумматор

Схемы вычитания

Цифровой компаратор

Слайд 2Двоичный сумматор

Двоичный сумматор (SM) служит для формирования арифметической суммы n-разрядных

двоичных чисел А и В. Результатом сложения (при n = 4) является четырехразрядная сумма S и выход переноса Р, который можно рассматривать как пятый разряд суммы.

Слайд 3Полусумматор

Полусумматор (HS - HalfSum - полусумма), - это устройство, производящее

сложение двух одноразрядных двоичных чисел без учета переноса предыдущего разряда.

Слайд 6Полный одноразрядный сумматор

Полный одноразрядный сумматор суммирует биты соответствующих разрядов двух

двоичных чисел с учетом переноса и вырабатывает перенос в следующий разряд.

Слайд 7Полный одноразрядный сумматор

Полный одноразрядный сумматор можно построить из двух полусумматоров HS

и логического элемента ИЛИ. Один полусумматор используется для сложения i-го разряда двоичных чисел, а второй полусумматор складывает результат первого полусумматора с переносом из (i-1) разряда.

Слайд 8Многоразрядный сумматор

Для сложения двух многоразрядных двоичных чисел используют многоразрядные сумматоры, представляющие

собой в простейшем виде последовательное соединение одноразрядных сумматоров.

Слайд 9Многоразрядный сумматор

В корпусе микросхемы К155ИМ3 четыре полных одноразрядных сумматора объединены в

схему четырехразрядного сумматора.

Слайд 10Схемы вычитания

Вычитание можно осуществить, инвертируя число В и суммируя полученный результат

с А.

Слайд 11Схемы вычитания

При А > В получаем Р = 1.Результат S формируется

в прямом коде.

При A < B получаем Р = 0. Результат S формируется в обратном

При A < B получаем Р = 0. Результат S формируется в обратном

Слайд 13Цифровой компаратор

Цифровым компаратором называют устройство, фиксирующее результат сравнения n-разрядных двоичных кодов

чисел.

Цифровой компаратор можно построить на сумматоре, подавая на один суммирующий вход прямой код числа А, на другой — инверсный код числа В.

Цифровой компаратор можно построить на сумматоре, подавая на один суммирующий вход прямой код числа А, на другой — инверсный код числа В.

Слайд 15Цифровой компаратор

Компаратор, фиксирующий равнозначность кодов А и В, можно выполнить на

ЛЭ по схеме, показанной на рис.