- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Сумматоры. Двоичные сумматоры презентация

Содержание

- 1. Сумматоры. Двоичные сумматоры

- 2. ПОВТОРЕНИЕ Цифровыми устройствами комбинационного типа - ?

- 3. ПОВТОРЕНИЕ. ПРИНЦИП СЛОЖЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

- 4. ДВОИЧНЫЕ СУММАТОРЫ Сумматор — устройство, преобразующее информационные

- 5. КЛАССИФИКАЦИЯ СУММАТОРОВ В зависимости от формы представления информации различают сумматоры аналоговые и цифровые.

- 6. ПО СПОСОБУ РЕАЛИЗАЦИИ механические электромеханические электронные пневматические

- 7. ПО ПРИНЦИПУ ДЕЙСТВИЯ на счётчиках, считающие количества

- 8. ПО АРХИТЕКТУРЕ четвертьсумматоры — бинарные (двухоперандные) сумматоры

- 9. ПО СПОСОБУ ДЕЙСТВИЯ Последовательные (одноразрядные), в которых

- 10. ПО СПОСОБУ ОРГАНИЗАЦИИ ПЕРЕНОСА С последовательным переносом;

- 11. ПО СПОСОБУ ВЫПОЛНЕНИЯ ОПЕРАЦИИ СЛОЖЕНИЯ И ВОЗМОЖНОСТИ

- 12. ДВОИЧНЫЙ СУММАТОР Двоичный сумматор может быть определён

- 13. ВАЖНЕЙШИМИ ПАРАМЕТРАМИ СУММАТОРОВ ЯВЛЯЮТСЯ: разрядность; статические

- 14. ВАЖНЕЙШИМИ ПАРАМЕТРАМИ СУММАТОРОВ ЯВЛЯЮТСЯ: динамические параметры. Сумматоры

- 15. ЧЕТВЕРТЬСУММАТОР Простейшим двоичным суммирующим элементом является четвертьсумматор.

- 16. СХЕМА ИМЕЕТ ДВА ВХОДА А И B

- 17. РЕАЛИЗУЕМ ЧЕТВЕРТЬСУММАТОР В БАЗИСАХ И-НЕ, ИЛИ-НЕ:

- 18. ПОЛУСУММАТОР Cхема, которая обеспечивает сложение двух однобитных

- 19. СХЕМА A – первый входной сигнал

- 20. В ДВОИЧНОЙ СИСТЕМЕ СЛОЖЕНИЕ ДВУХ ДВОИЧНЫХ ЧИСЕЛ ОСУЩЕСТВЛЯЕТСЯ ПО ПРАВИЛУ, ОПИСАННОМУ В ТАБЛИЦЕ:

- 21. ФОРМУЛА ДЛЯ S (ВЫВОД) Формулу для S

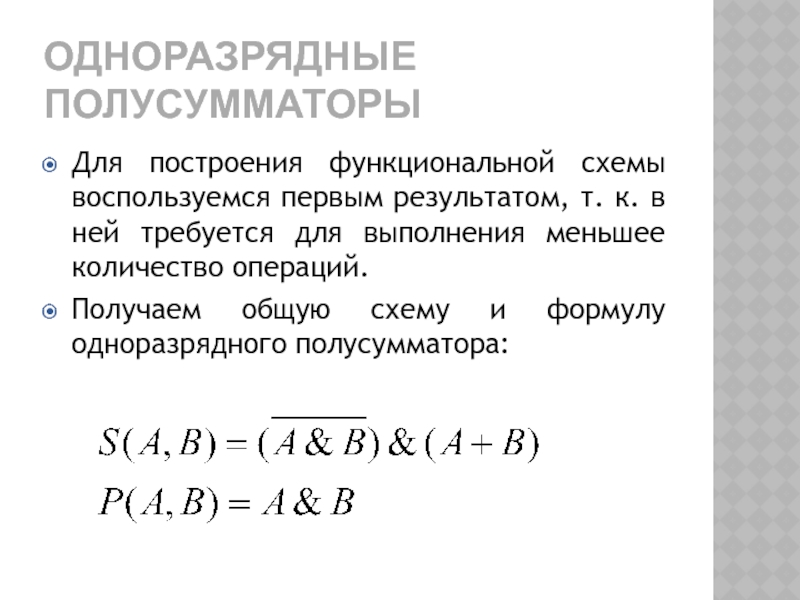

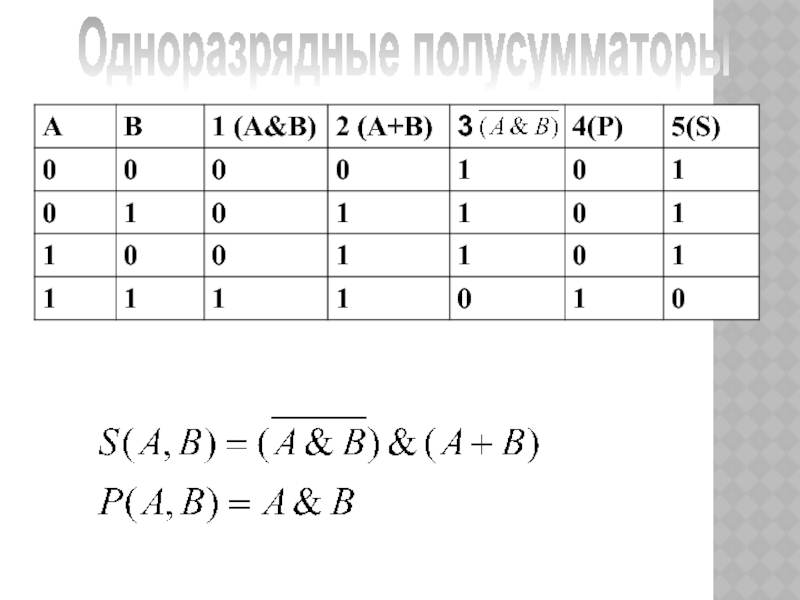

- 22. ОДНОРАЗРЯДНЫЕ ПОЛУСУММАТОРЫ Для построения функциональной схемы воспользуемся

- 23. Одноразрядные полусумматоры

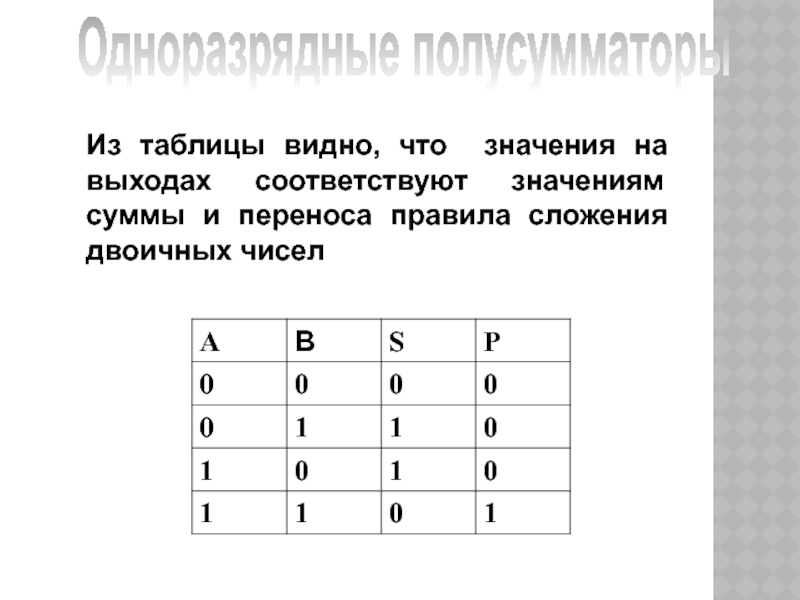

- 24. Одноразрядные полусумматоры Из таблицы

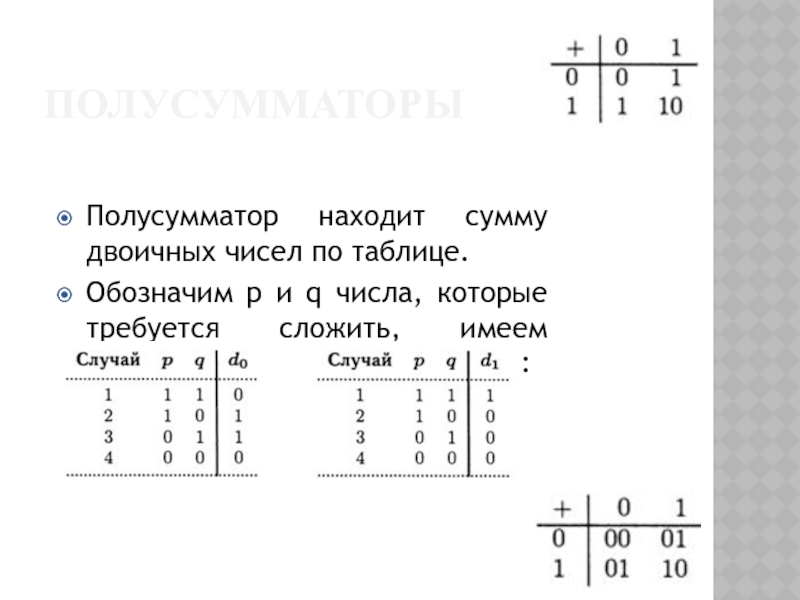

- 25. ПОЛУСУММАТОРЫ Полусумматор находит сумму двоичных чисел по

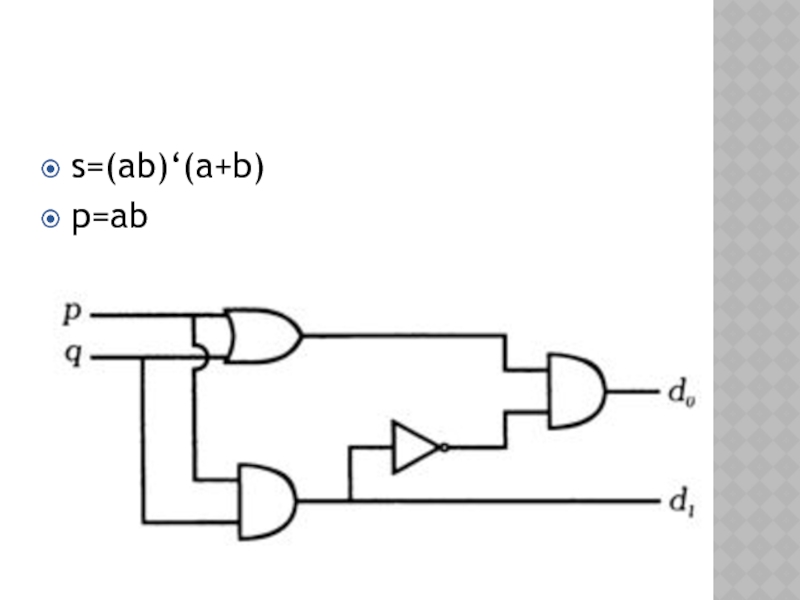

- 26. s=(ab)‘(a+b) p=ab

- 27. ПОЛНЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР Одноразрядный двоичный сумматор на

- 28. ПОЛНЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР Через вход A и

- 29. ПОЛНЫЙ ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР Имеет три входа:

- 30. A – первый вход B –

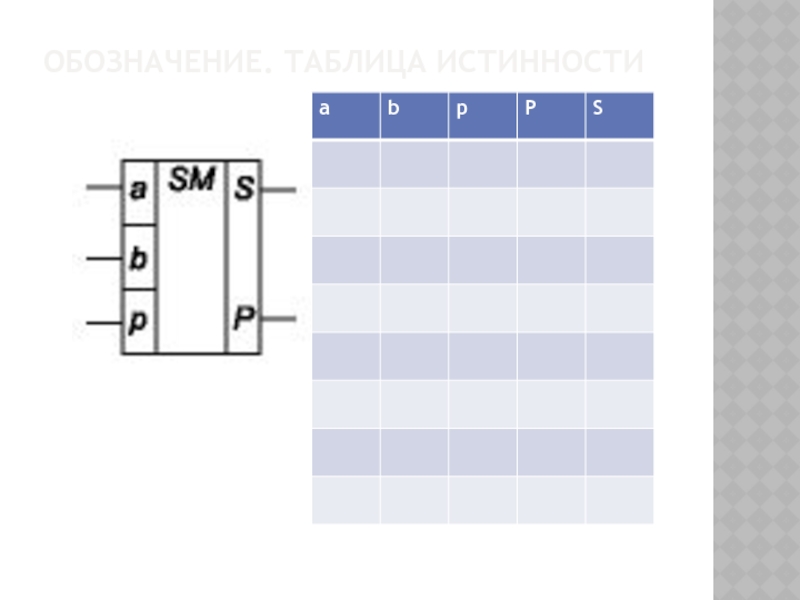

- 31. ОБОЗНАЧЕНИЕ. ТАБЛИЦА ИСТИННОСТИ

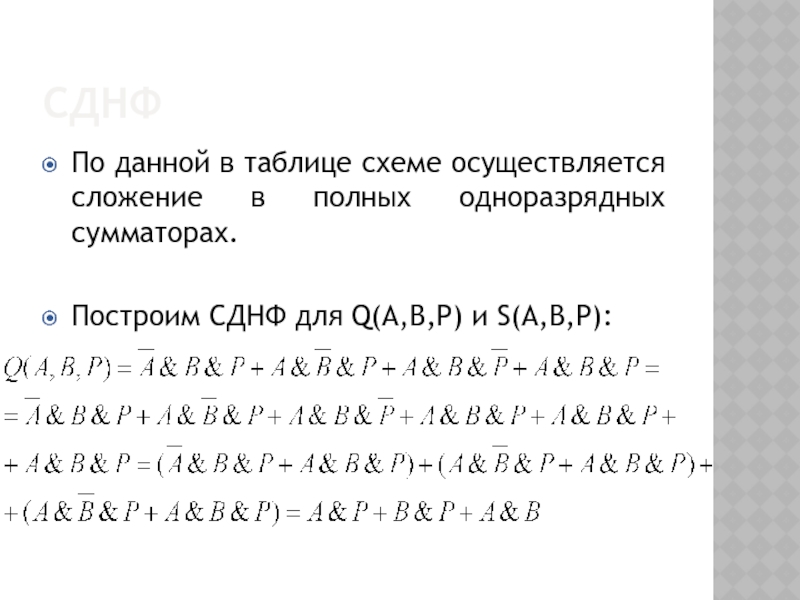

- 32. СДНФ По данной в таблице схеме осуществляется

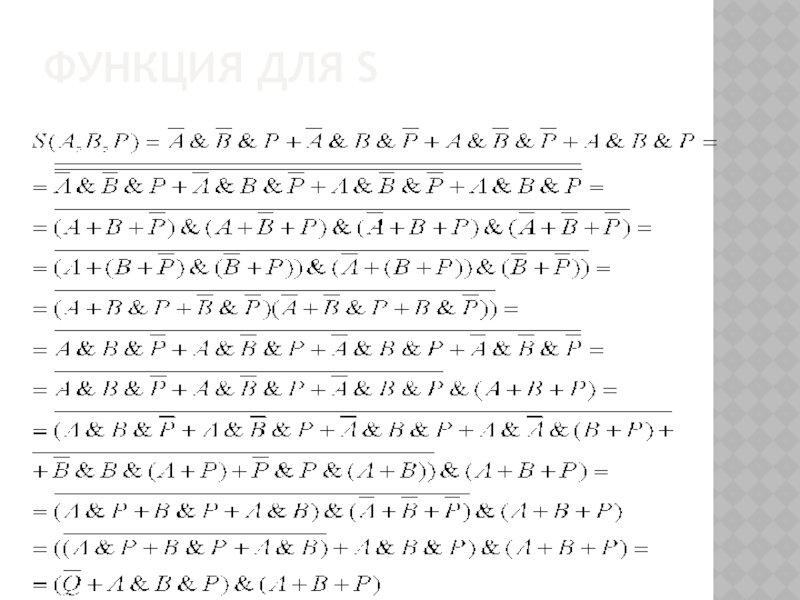

- 33. ФУНКЦИЯ ДЛЯ S

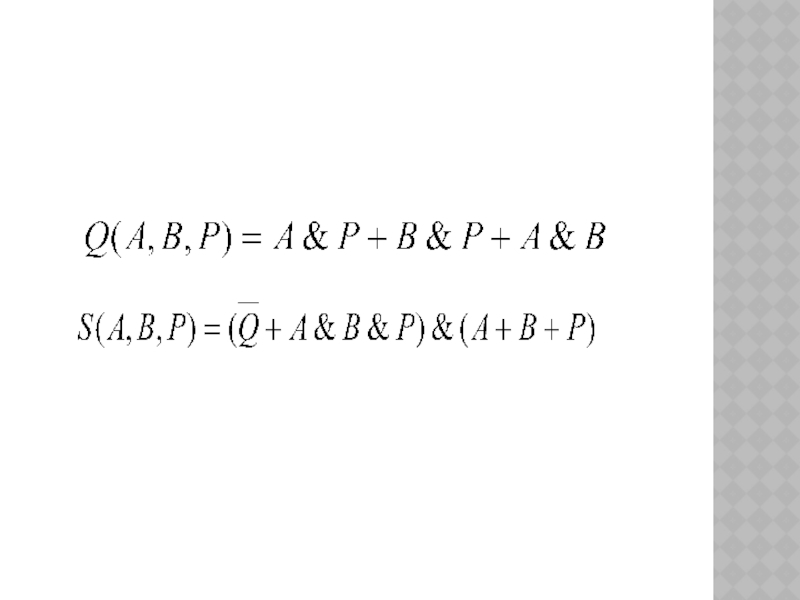

- 34. ПОЛУЧАЕМ СТРУКТУРНЫЕ ФОРМУЛЫ

- 35. СХЕМА A A A B P S Q

- 36. МНОГОРАЗРЯДНЫЕ ДВОИЧНЫЕ СУММАТОРЫ В зависимости от способа

- 37. ПОСЛЕДОВАТЕЛЬНЫЕ СУММАТОРЫ Последовательные сумматоры строятся на основе

- 38. СУММАТОР ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ

- 39. ПАРАЛЛЕЛЬНЫЕ СУММАТОРЫ Параллельные сумматоры комбинационного типа представляют

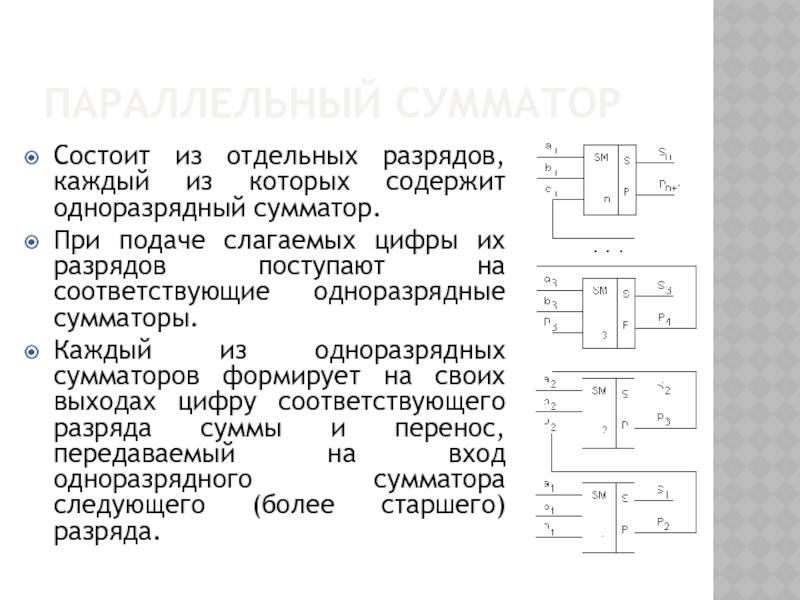

- 40. ПАРАЛЛЕЛЬНЫЙ СУММАТОР Состоит из отдельных разрядов, каждый

- 41. ПАРАЛЛЕЛЬНЫЕ МНОГОРАЗРЯДНЫЕ СУММАТОРЫ Простейшими из параллельных сумматоров

- 42. БЫСТРОДЕЙСТВИЕ СУММАТОРА Быстродействие сумматора при сложении двух

- 43. ДЕСЯТИЧНЫЕ СУММАТОРЫ Для построения многоразрядных двоичных сумматоров,

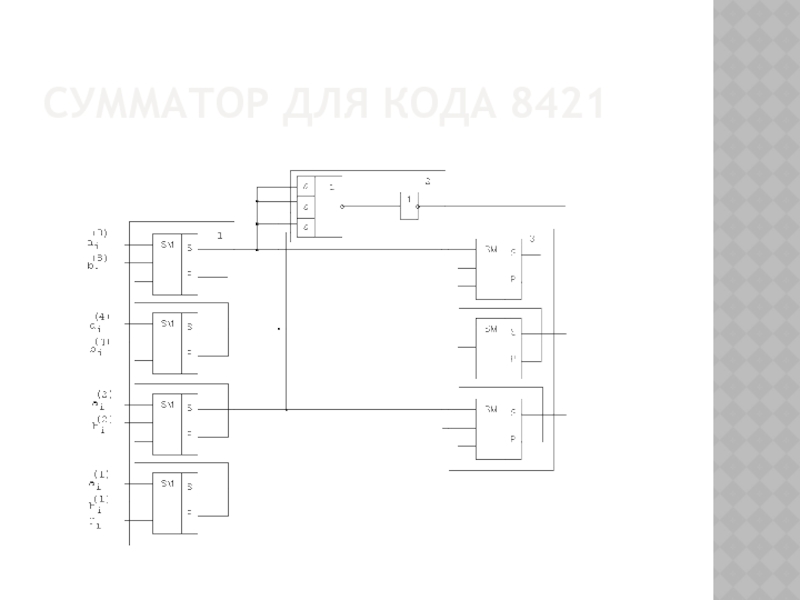

- 44. СУММАТОР ДЛЯ КОДА 8421

- 45. СХЕМА ФОРМИРОВАНИЯ ОБРАТНОГО КОДА В десятичной системе

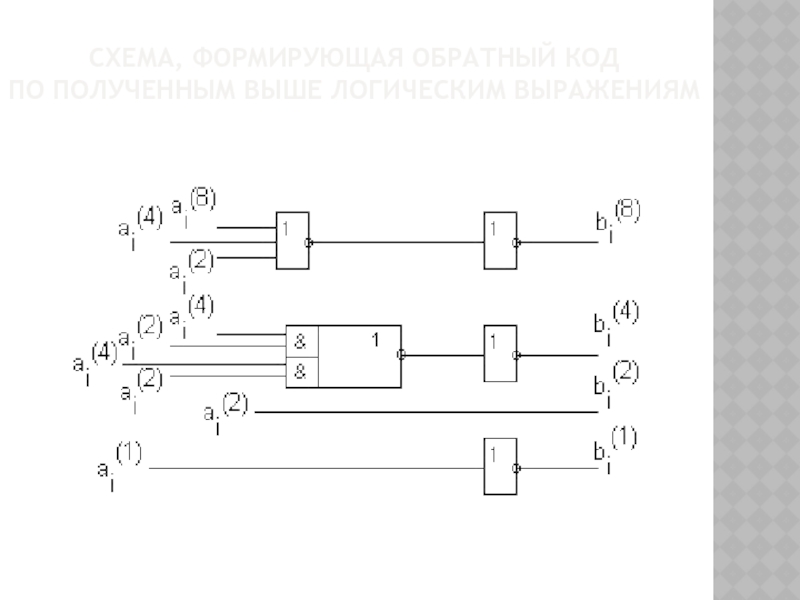

- 46. СХЕМА, ФОРМИРУЮЩАЯ ОБРАТНЫЙ КОД ПО ПОЛУЧЕННЫМ ВЫШЕ ЛОГИЧЕСКИМ ВЫРАЖЕНИЯМ

- 47. АРИФМЕТИКО-ЛОГИЧЕСКИЕ УСТРОЙСТВА Основными арифметическими операциями являются сложение и

- 48. Для повышения быстродействия ЭВМ разработаны и

- 49. МЕТОДИКА ПОСТРОЕНИЯ ОДНОРАЗРЯДНОГО АРИФМЕТИЧЕСКОГО УСТРОЙСТВА ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ СУММИРОВАНИЯ И ВЫЧИТАНИЯ

- 50. ОПЕРАЦИЯ ВЫЧИТАНИЯ Для выполнения операции вычитания не

- 51. ВЫЧИТАНИЕ Вычитание числа В из А выполняется

- 52. МНОГОРАЗРЯДНЫЕ АЛУ Многоразрядные АЛУ выпускаются в виде интегральных

- 53. МС 564ИП3 (РИСУНОК 26,А) — ЭТО 4-РАЗРЯДНОЕ ПАРАЛЛЕЛЬНОЕ АЛУ, ВЫПОЛНЯЮЩАЯ 16 АРИФМЕТИЧЕСКИХ И 16 ЛОГИЧЕСКИХ ОПЕРАЦИЙ.

- 54. A(а0–а3) — первый операнд, B(b0–b3) — второй операнд, S(s0–s3) —

- 55. ДЗ Применение сумматоров.

Слайд 4ДВОИЧНЫЕ СУММАТОРЫ

Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в

Двоичными сумматорами называют логические устройства, выполняющие операцию сложения двух чисел, представленных в двоичном коде.

Сумматор является основным узлом арифметико-логического устройства ЭВМ и служит для суммирования чисел посредством поразрядного сложения.

Слайд 5КЛАССИФИКАЦИЯ СУММАТОРОВ

В зависимости от формы представления информации различают сумматоры аналоговые и

Слайд 7ПО ПРИНЦИПУ ДЕЙСТВИЯ

на счётчиках, считающие количества импульсов в операндах

функциональные, выдающие на

каждый раз вычисляющие функцию разряда суммы по модулю и функцию разряда переноса

с таблицами заранее вычисленных значений функции разряда суммы по модулю и значений функции разряда переноса записанных в:

ПЗУ, ППЗУ (аппаратные) или

ОЗУ (аппаратные и программные)

Слайд 8ПО АРХИТЕКТУРЕ

четвертьсумматоры — бинарные (двухоперандные) сумматоры по модулю без разряда переноса,

полусумматоры — бинарные (двухоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма по модулю в данном разряде, а на другом — перенос в следующий (старший разряд);

полные сумматоры — тринарные (трёхоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма по модулю в данном разряде, а на другом — перенос в следующий (более старший разряд). Такие сумматоры изначально ориентированы только на показательные позиционные системы счисления.

Слайд 9ПО СПОСОБУ ДЕЙСТВИЯ

Последовательные (одноразрядные), в которых обработка разрядов чисел ведётся поочерёдно,

Параллельные (многоразрядные), в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование;

Слайд 10ПО СПОСОБУ ОРГАНИЗАЦИИ ПЕРЕНОСА

С последовательным переносом;

С параллельным переносом;

С условным переносом;

С групповым

Слайд 11ПО СПОСОБУ ВЫПОЛНЕНИЯ ОПЕРАЦИИ СЛОЖЕНИЯ И ВОЗМОЖНОСТИ СОХРАНЕНИЯ РЕЗУЛЬТАТА СЛОЖЕНИЯ МОЖНО

комбинационный, выполняющий микрооперацию "S = A плюс B", в котором результат выдается по мере его образования (это комбинационная схема в общепринятом смысле слова);

сумматор с сохранением результата "S = A плюс B";

накапливающий, выполняющий микрооперацию "S = S плюс B".

Слайд 12ДВОИЧНЫЙ СУММАТОР

Двоичный сумматор может быть определён тремя способами:

1. табличным, в виде

Табличный способ определения двоичного сумматора является основным

Слайд 13ВАЖНЕЙШИМИ ПАРАМЕТРАМИ СУММАТОРОВ ЯВЛЯЮТСЯ:

разрядность;

статические параметры: Uвх, Uвх, Iвх и так

Слайд 14ВАЖНЕЙШИМИ ПАРАМЕТРАМИ СУММАТОРОВ ЯВЛЯЮТСЯ:

динамические параметры. Сумматоры характеризуются четырьмя задержками распространения:

от

от одновременной подачи всех слагаемых до установления всех выходов суммы при постоянном уровне на входе переноса;

от подачи входного переноса до установления выходного переноса при постоянном уровне на входах слагаемых;

от подачи всех слагаемых до установления выходного переноса при постоянном уровне на входах слагаемых.

Слайд 15ЧЕТВЕРТЬСУММАТОР

Простейшим двоичным суммирующим элементом является четвертьсумматор.

Происхождение названия этого элемента следует

Наиболее известны для данной схемы названия: элемент "сумма по модулю 2" и элемент "исключающее ИЛИ".

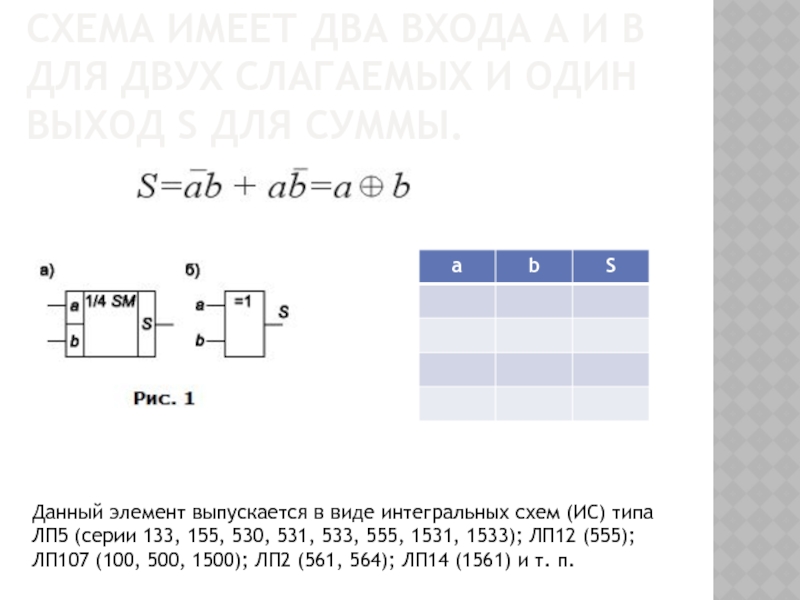

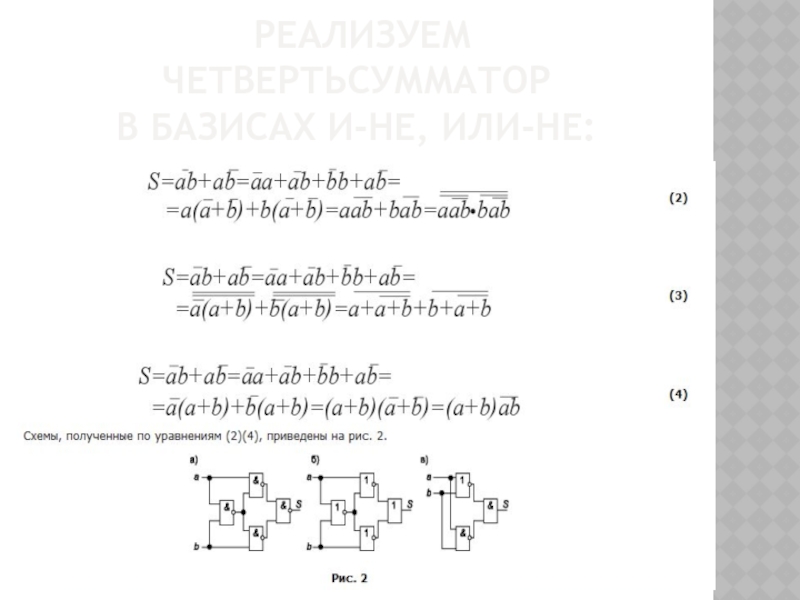

Слайд 16СХЕМА ИМЕЕТ ДВА ВХОДА А И B ДЛЯ ДВУХ СЛАГАЕМЫХ И

Данный элемент выпускается в виде интегральных схем (ИС) типа ЛП5 (серии 133, 155, 530, 531, 533, 555, 1531, 1533); ЛП12 (555); ЛП107 (100, 500, 1500); ЛП2 (561, 564); ЛП14 (1561) и т. п.

Слайд 18ПОЛУСУММАТОР

Cхема, которая обеспечивает сложение двух однобитных чисел А и В называется

Полусумматор имеет 4 сигнальных линии: два входа для сигналов, представляющих одноразрядные двоичные числа А и В, и два выхода: сумма А и В по модулю 2 (S) и сигнал переноса (P).

При этом S наименее значимый бит, а P наиболее значимый бит.

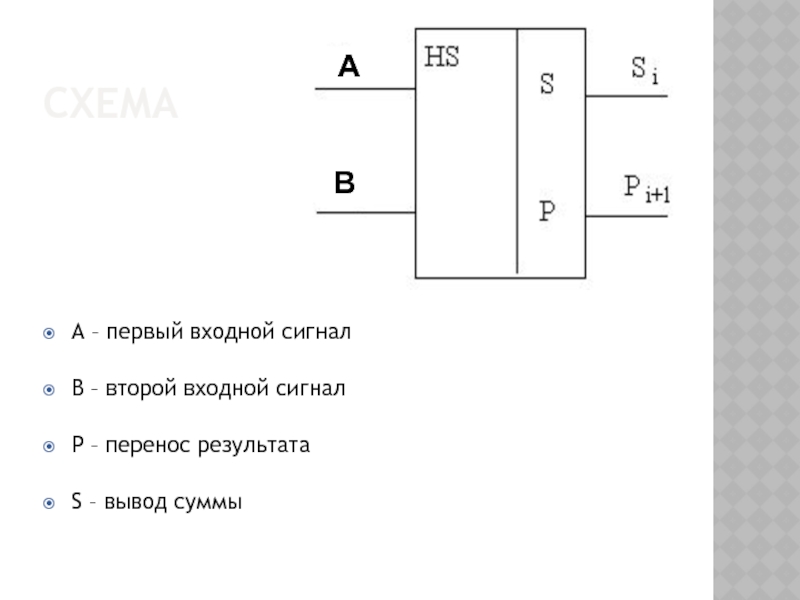

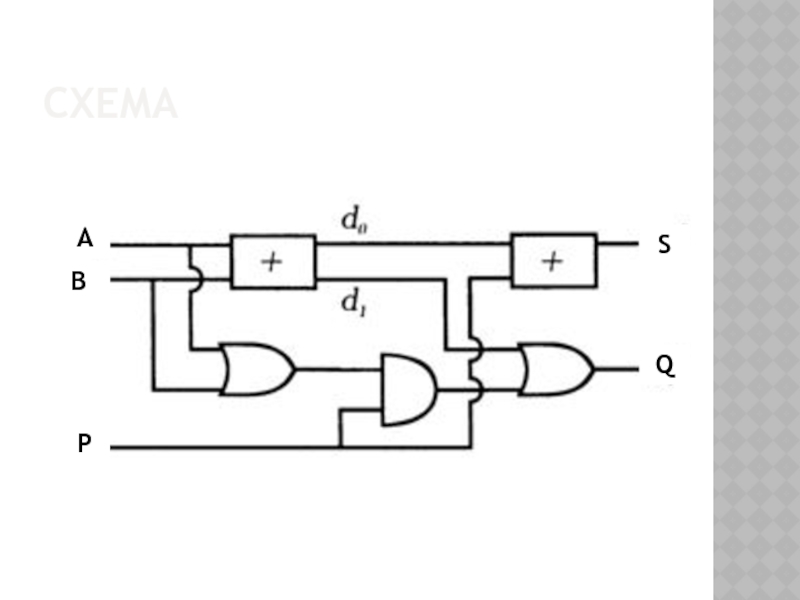

Слайд 19СХЕМА

A – первый входной сигнал

B – второй входной сигнал

P – перенос

S – вывод суммы

Слайд 20В ДВОИЧНОЙ СИСТЕМЕ СЛОЖЕНИЕ ДВУХ ДВОИЧНЫХ ЧИСЕЛ ОСУЩЕСТВЛЯЕТСЯ ПО ПРАВИЛУ, ОПИСАННОМУ

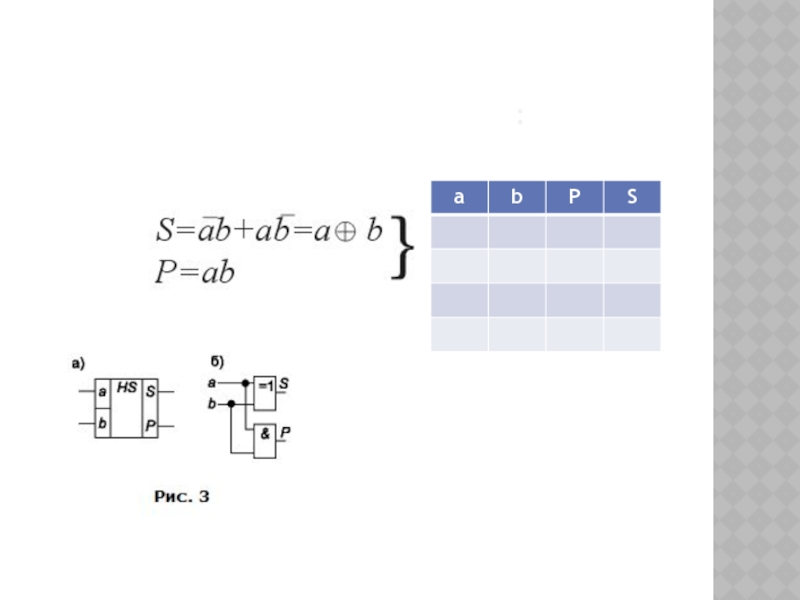

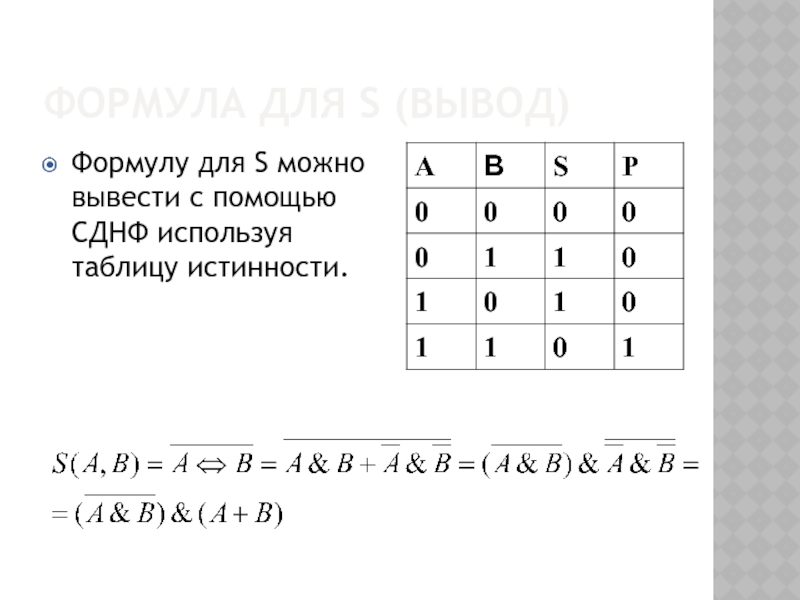

Слайд 21ФОРМУЛА ДЛЯ S (ВЫВОД)

Формулу для S можно вывести с помощью СДНФ

Слайд 22ОДНОРАЗРЯДНЫЕ ПОЛУСУММАТОРЫ

Для построения функциональной схемы воспользуемся первым результатом, т. к. в

Получаем общую схему и формулу одноразрядного полусумматора:

Слайд 24Одноразрядные полусумматоры

Из таблицы видно, что значения на выходах соответствуют значениям суммы

Слайд 25ПОЛУСУММАТОРЫ

Полусумматор находит сумму двоичных чисел по таблице.

Обозначим p и q числа,

Слайд 27ПОЛНЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР

Одноразрядный двоичный сумматор на три входа и два выхода

Слайд 28ПОЛНЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР

Через вход A и B сумматор воспринимает двоичные цифры

На выход S сумматор выдает сумму в данном разряде, на выход Q – значение переноса в старший разряд.

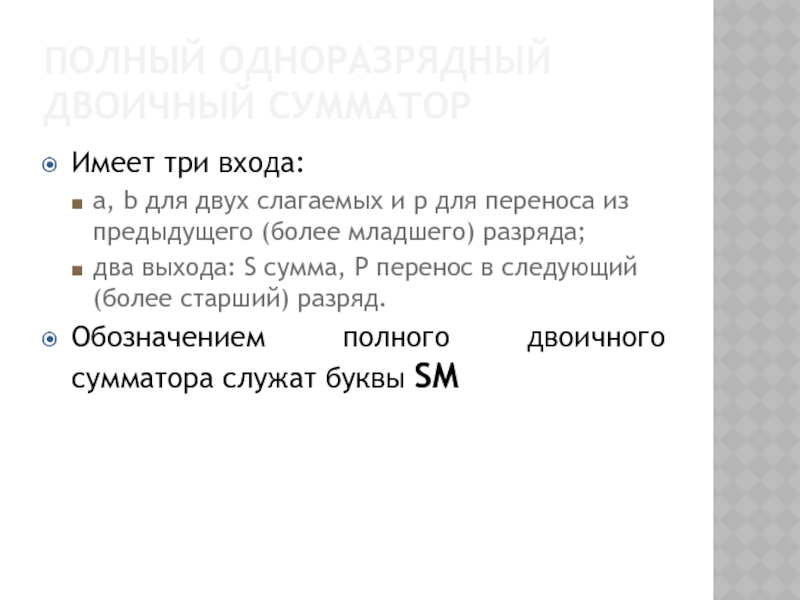

Слайд 29ПОЛНЫЙ ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР

Имеет три входа:

a, b для двух слагаемых

два выхода: S сумма, P перенос в следующий (более старший) разряд.

Обозначением полного двоичного сумматора служат буквы SM

Слайд 30A – первый вход

B – второй вход

P – третий вход

Q –

S – вывод суммы

Полные одноразрядные сумматоры

Слайд 32СДНФ

По данной в таблице схеме осуществляется сложение в полных одноразрядных сумматорах.

Построим

Слайд 36МНОГОРАЗРЯДНЫЕ ДВОИЧНЫЕ СУММАТОРЫ

В зависимости от способа ввода кодов слагаемых сумматоры делятся

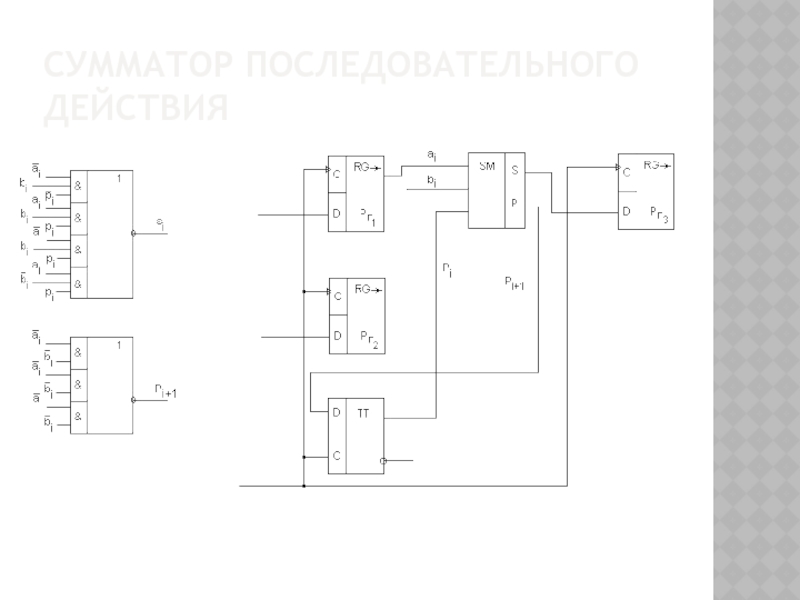

Слайд 37ПОСЛЕДОВАТЕЛЬНЫЕ СУММАТОРЫ

Последовательные сумматоры строятся на основе одноразрядной суммирующей схемы. В таких

Слайд 39ПАРАЛЛЕЛЬНЫЕ СУММАТОРЫ

Параллельные сумматоры комбинационного типа представляют собой композиции одноразрядных суммирующих схем,

Слайд 40ПАРАЛЛЕЛЬНЫЙ СУММАТОР

Состоит из отдельных разрядов, каждый из которых содержит одноразрядный сумматор.

При

Каждый из одноразрядных сумматоров формирует на своих выходах цифру соответствующего разряда суммы и перенос, передаваемый на вход одноразрядного сумматора следующего (более старшего) разряда.

Слайд 41ПАРАЛЛЕЛЬНЫЕ МНОГОРАЗРЯДНЫЕ СУММАТОРЫ

Простейшими из параллельных сумматоров (ПС) являются ПС с последовательной

На входы каждой одноразрядной схемы сумматора поступают два слагаемых и перенос из предыдущего разряда.

Сигнал переноса, образованный в младшем разряде, распространяется последовательно по цепям переноса к старшим разрядам. Время распространения переноса определяется суммарной задержкой этих цепей.

Слайд 42БЫСТРОДЕЙСТВИЕ СУММАТОРА

Быстродействие сумматора при сложении двух n-разрядных чисел характеризуется временем суммирования,

Следовательно, сумматоры с последовательным переносом обладают низким быстродействием. С целью повышения быстродействия (сокращения времени сложения) применяются сумматоры с одновременным переносом.

Слайд 43ДЕСЯТИЧНЫЕ СУММАТОРЫ

Для построения многоразрядных двоичных сумматоров, как было показано выше, необходимы

Последние выполняют операцию суммирования .десятичных цифр , и переноса, поступающих в разряд, и формируют на выходах десятичную цифру суммы и перенос для передачи в следующий десятичный разряд.

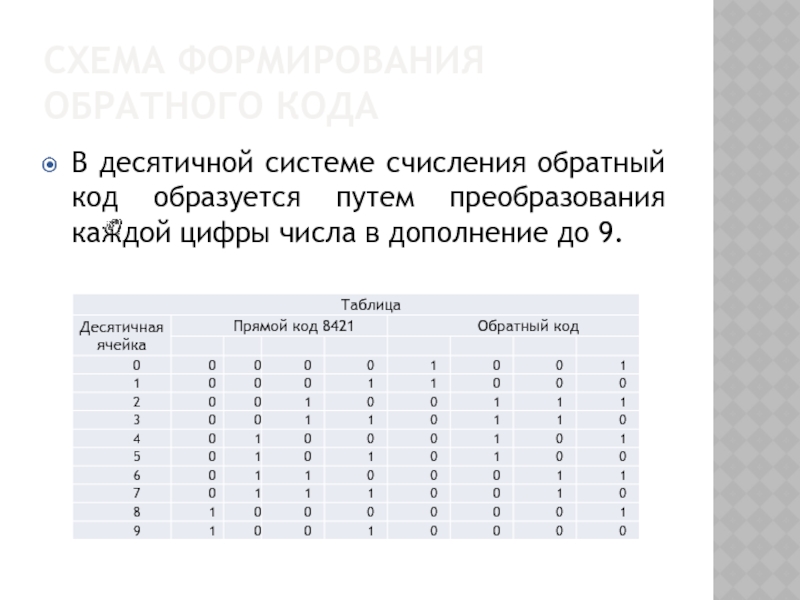

Слайд 45СХЕМА ФОРМИРОВАНИЯ ОБРАТНОГО КОДА

В десятичной системе счисления обратный код образуется путем

Слайд 47АРИФМЕТИКО-ЛОГИЧЕСКИЕ УСТРОЙСТВА

Основными арифметическими операциями являются сложение и вычитание.

Разработаны коды дополнительный и

Слайд 48

Для повышения быстродействия ЭВМ разработаны и используются комбинированные арифметико-логические устройства, которые

Слайд 49МЕТОДИКА ПОСТРОЕНИЯ ОДНОРАЗРЯДНОГО АРИФМЕТИЧЕСКОГО УСТРОЙСТВА

ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ

СУММИРОВАНИЯ И ВЫЧИТАНИЯ

Слайд 50ОПЕРАЦИЯ ВЫЧИТАНИЯ

Для выполнения операции вычитания не требуется получение дополнительных сигналов, поэтому

Необходимо лишь обеспечить коммутацию сигналов переноса и заёма в соответствии с кодом операции.

Слайд 51ВЫЧИТАНИЕ

Вычитание числа В из А выполняется путем суммирования отрицательного числа В

Прибавление этой единицы эффективно реализуется в полном сумматоре путем замены его первого каскада (полусумматора) на полный сумматор, вход переноса которого подключается к напряжению с уровнем логической 1.

Слайд 52МНОГОРАЗРЯДНЫЕ АЛУ

Многоразрядные АЛУ выпускаются в виде интегральных микросхем или входят в состав

Слайд 53МС 564ИП3 (РИСУНОК 26,А) — ЭТО 4-РАЗРЯДНОЕ ПАРАЛЛЕЛЬНОЕ АЛУ, ВЫПОЛНЯЮЩАЯ 16 АРИФМЕТИЧЕСКИХ И

Слайд 54

A(а0–а3) — первый операнд,

B(b0–b3) — второй операнд,

S(s0–s3) — код операции — 4 разряда.

Если M=0, то выполняются

F(f0–f3) — результат операции. На выходе A=B появляется «1», если при выполнении операции вычитания результат операции будет равен «0», то есть A=B. Поскольку АЛУ параллельного типа, то имеются выходы генерации G и распространения переноса H. Pn и Рn+4 — входной и выходной переносы.