B

B

B

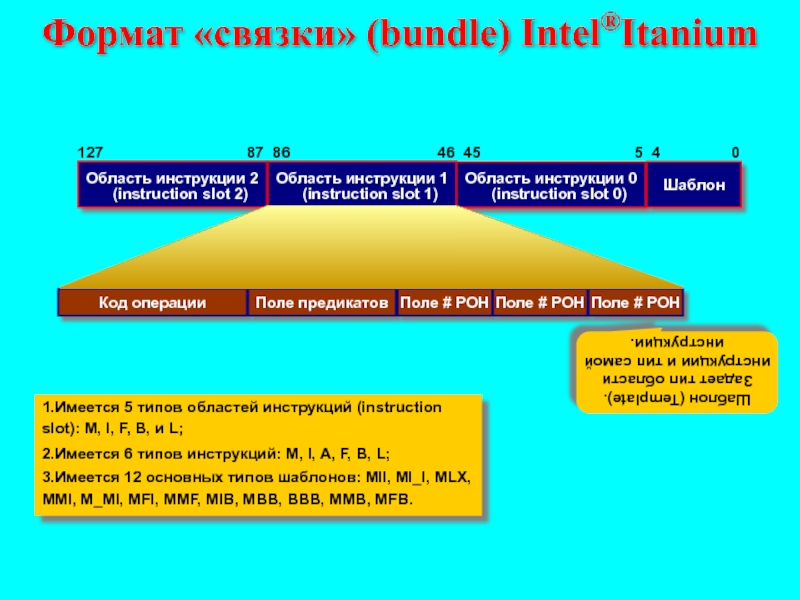

M

M

I

I

F

F

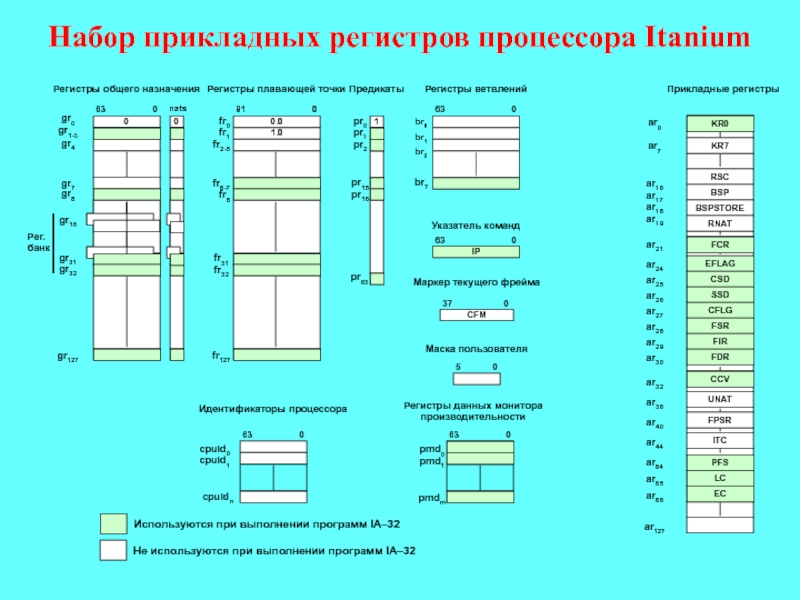

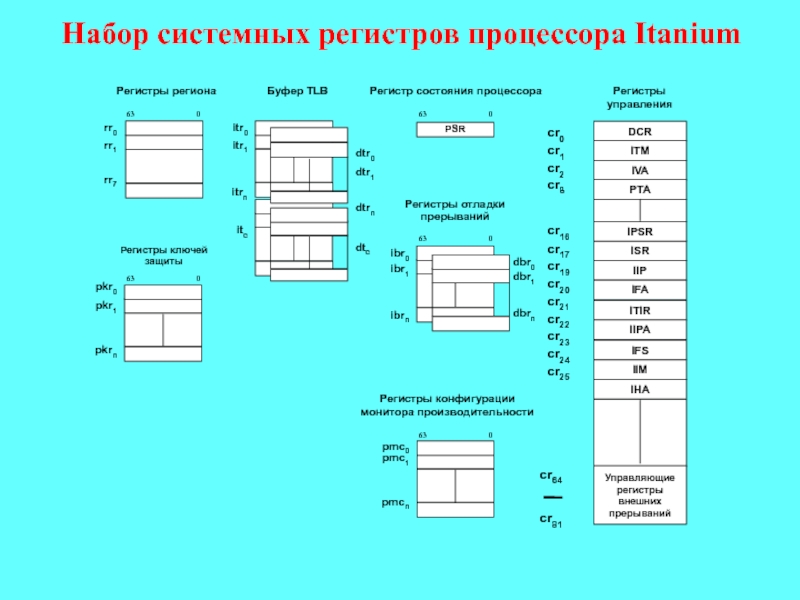

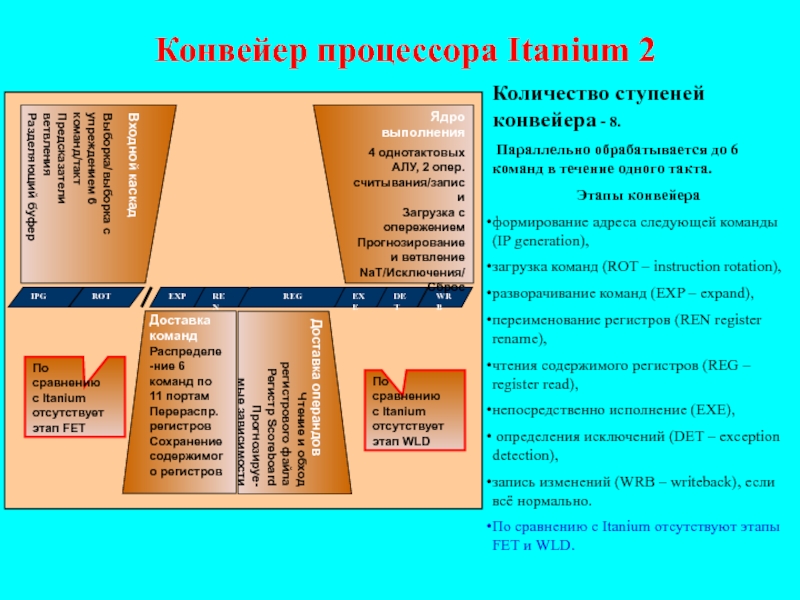

Стек регистров / вращение регистров

Прогнозирование, обработка исключений

128 целочисленных регистров

128 регистров ПТ

Блоки ветвле-ния

Блоки ветвле-ния

Блоки ветвления

Целочисл. и ММ функц. блоки

Кэш данных L1

и БПА данных ( включая TLB)

ALAT

Функц.

блоки ПТ

Контроллер системной шины

Регистры прогнозирования и ветвления

Буфер разделения

8 связок

КЭШ команд L1 и механизм выборки/выборки с упреждением

Ширина шины 64 бита; 266МГц

ядро

Блоки умножения с накопл.