- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Средства проектирования цифровых устройств с использованием программируемых логических интегральных схем презентация

Содержание

- 1. Средства проектирования цифровых устройств с использованием программируемых логических интегральных схем

- 2. V.I Архитектура интегральных схем с программируемой структурой

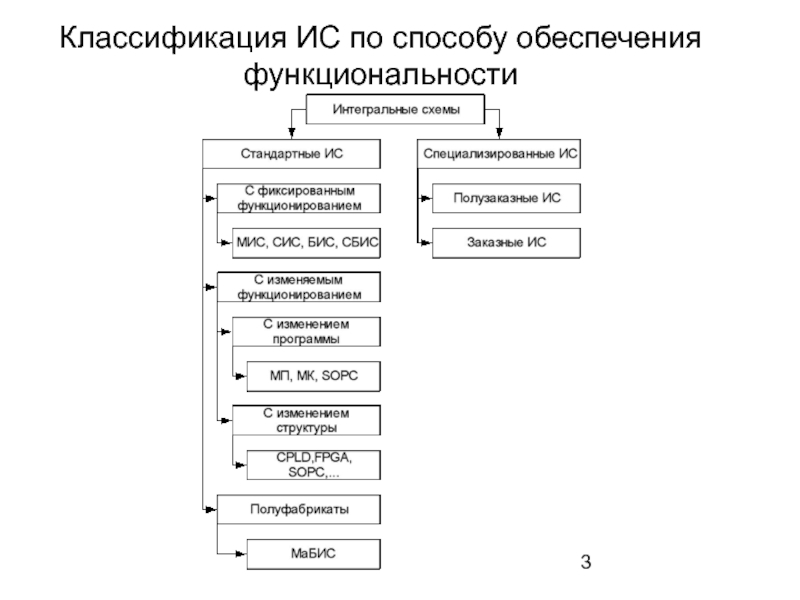

- 3. Классификация ИС по способу обеспечения функциональности

- 4. Эволюция ПЛИС

- 5. Преимуществами современных ПЛИС являются: Простота и

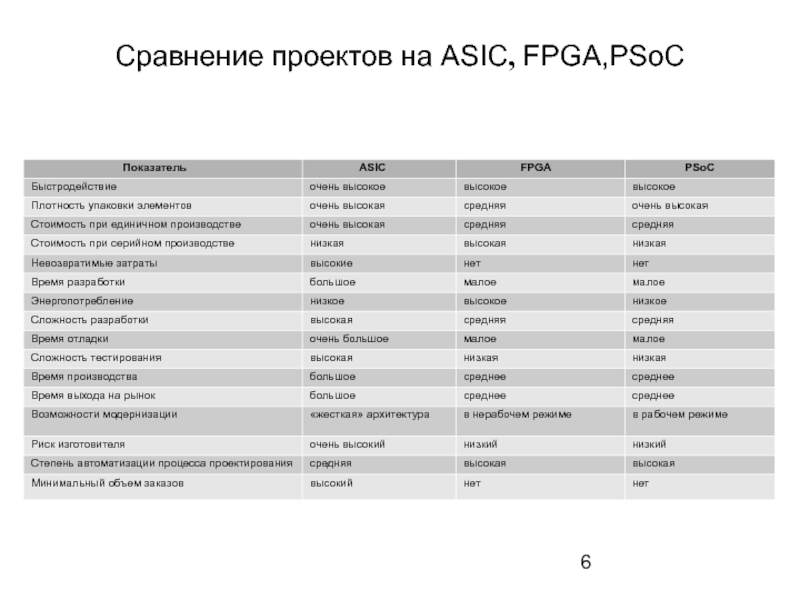

- 6. Сравнение проектов на ASIC, FPGA,PSoC

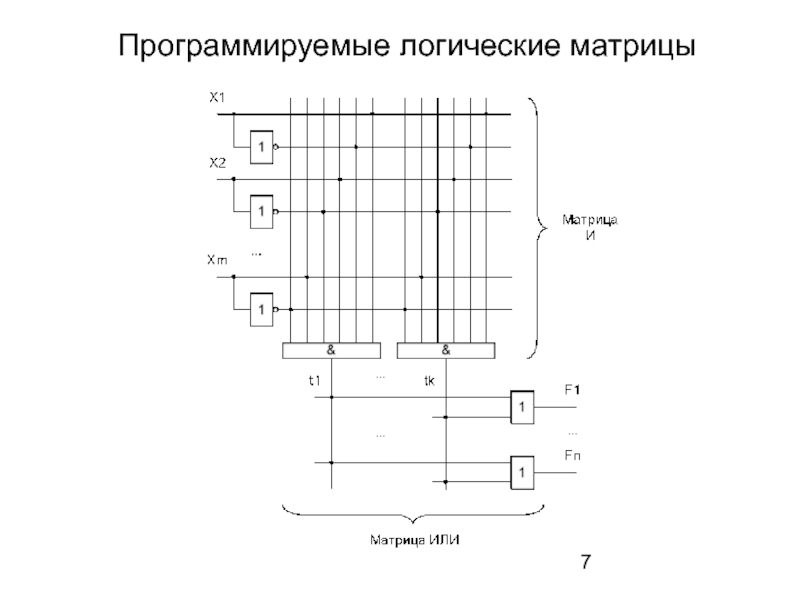

- 7. Программируемые логические матрицы

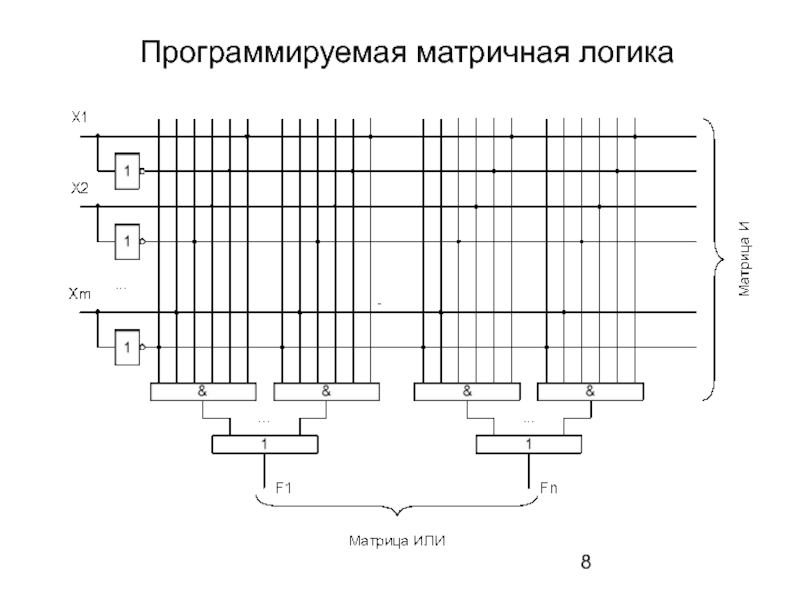

- 8. Программируемая матричная логика

- 9. Расширение функциональных возможностей ПЛМ и ПМЛ возможно

- 10. Структура базовых матричных кристаллов Типовые структуры

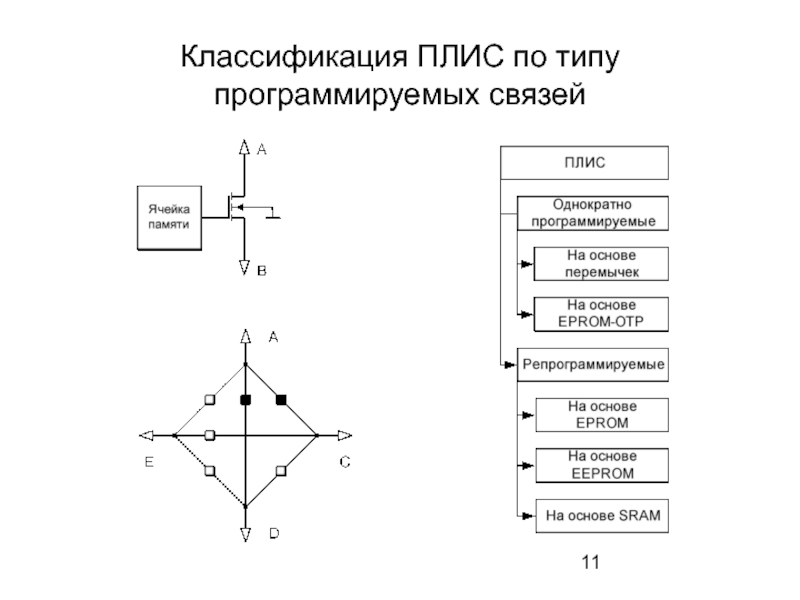

- 11. Классификация ПЛИС по типу программируемых связей

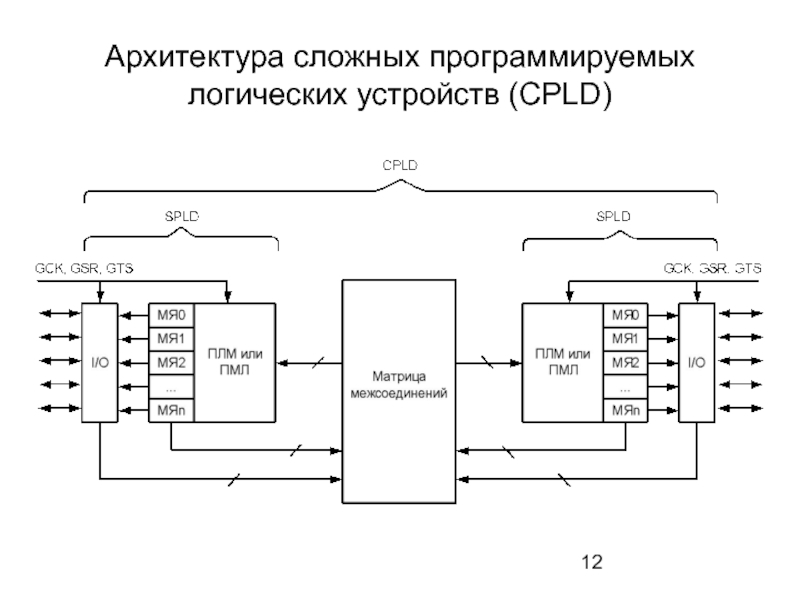

- 12. Архитектура сложных программируемых логических устройств (CPLD)

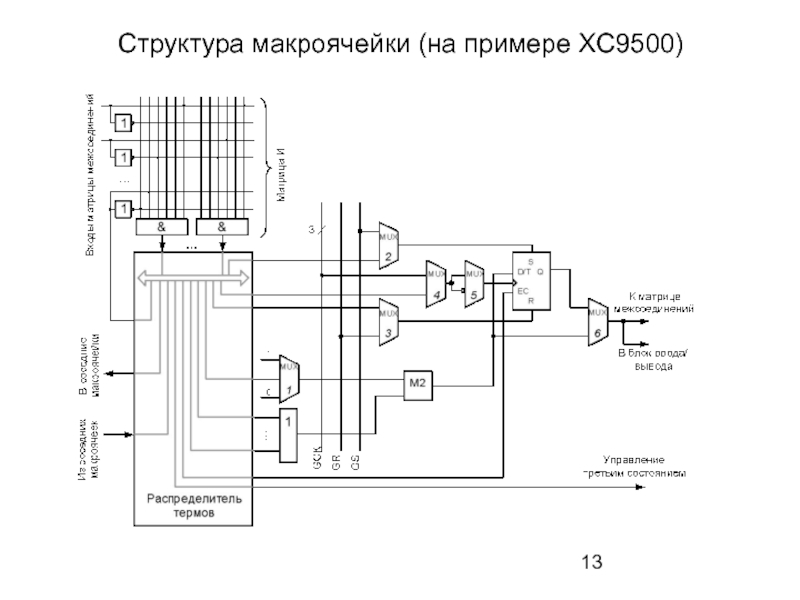

- 13. Структура макроячейки (на примере XC9500)

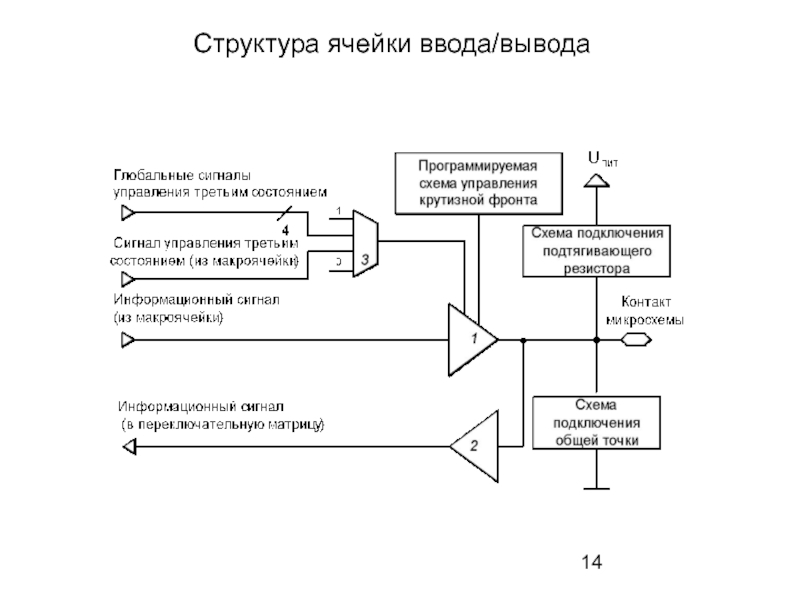

- 14. Структура ячейки ввода/вывода

- 15. Архитектура ПЛИС семейства кристаллов XC9500

- 16. Функциональный блок CPLD (на примере XC9500)

- 17. Макроячейка (на примере XC9500)

- 18. Распределитель термов

- 19. Увеличение функциональности распределитель термов CPLD

- 20. Программирование распределителя термов CPLD

- 21. Схема распределения тактовых сигналов (на примере XC9500)

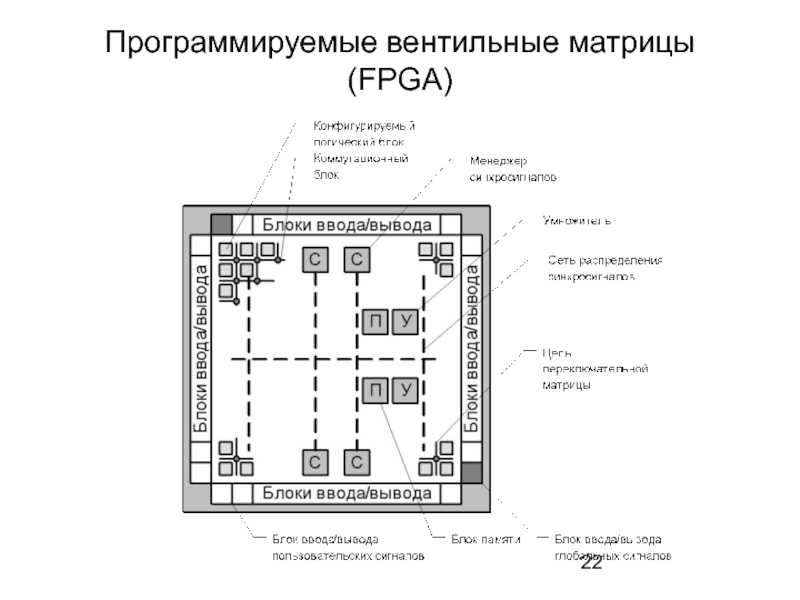

- 22. Программируемые вентильные матрицы (FPGA)

- 23. Структура КЛБ (на примере Spartan 3)

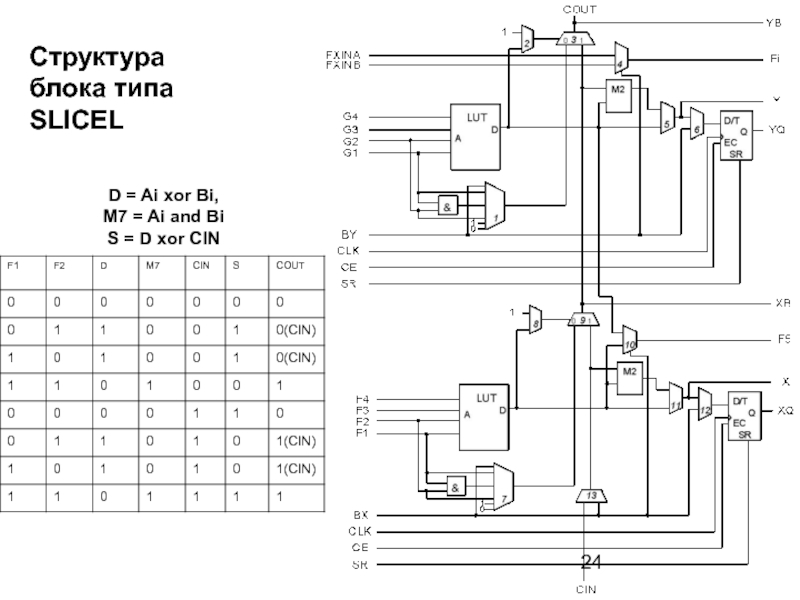

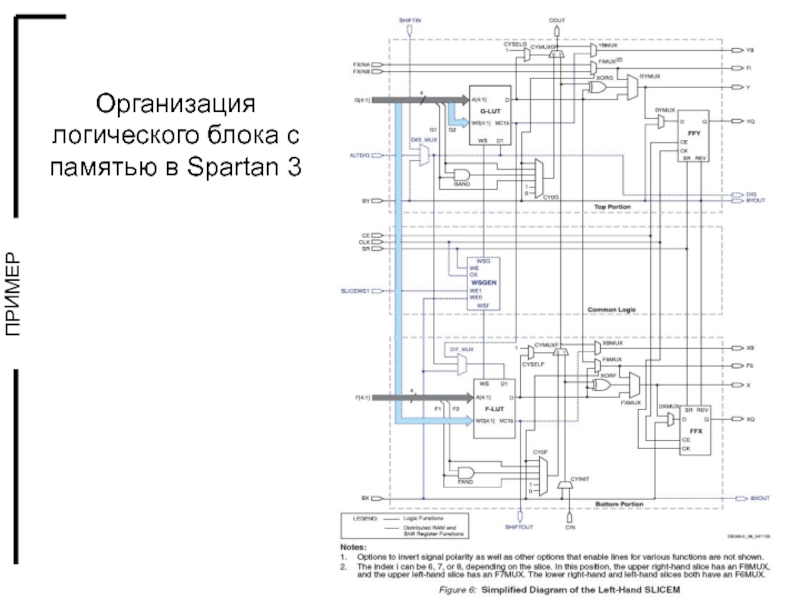

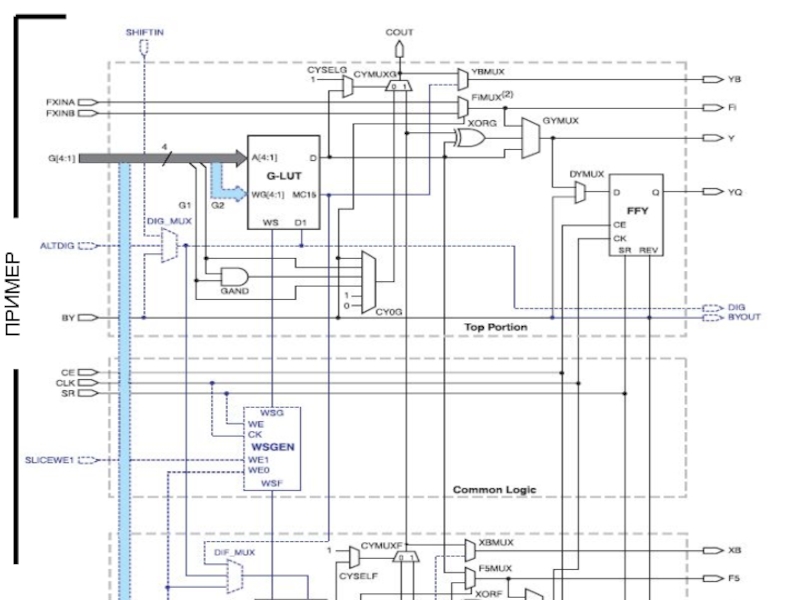

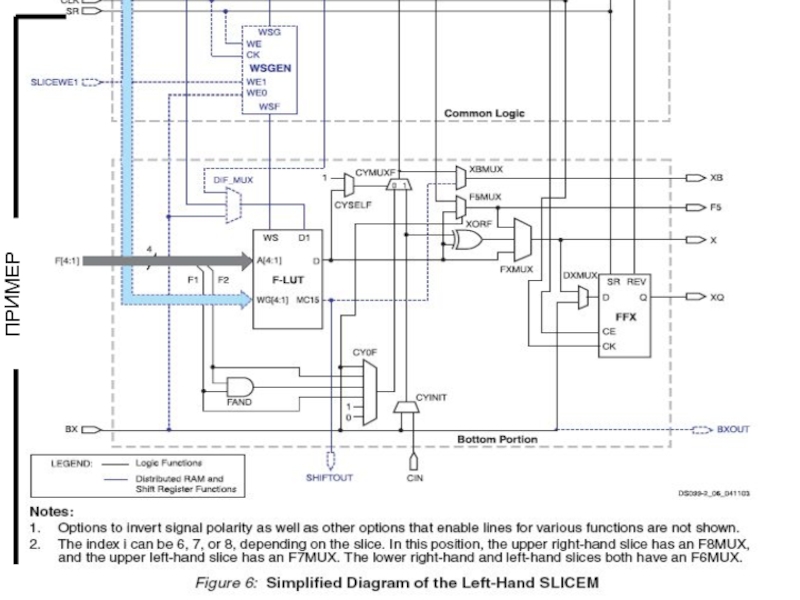

- 24. Структура блока типа SLICEL D

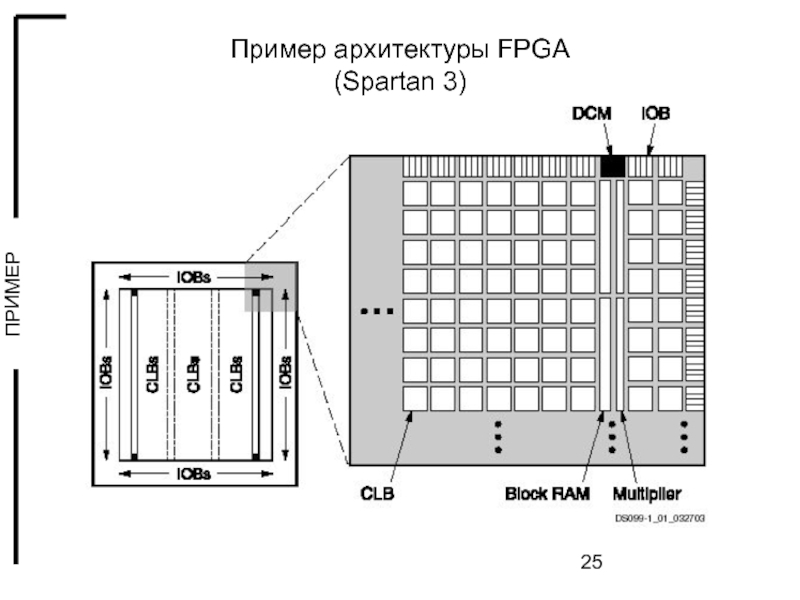

- 25. Пример архитектуры FPGA (Spartan 3)

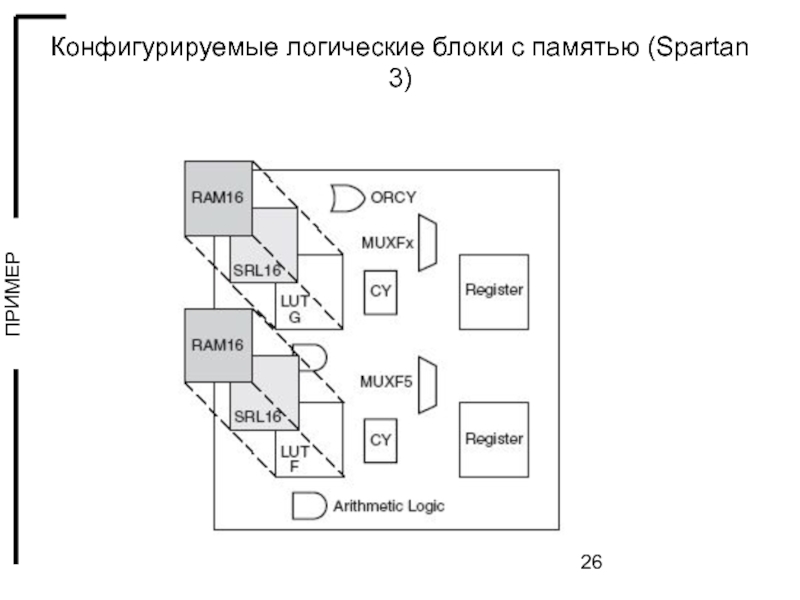

- 26. Конфигурируемые логические блоки с памятью (Spartan 3)

- 27. Организация логического блока с памятью в Spartan 3

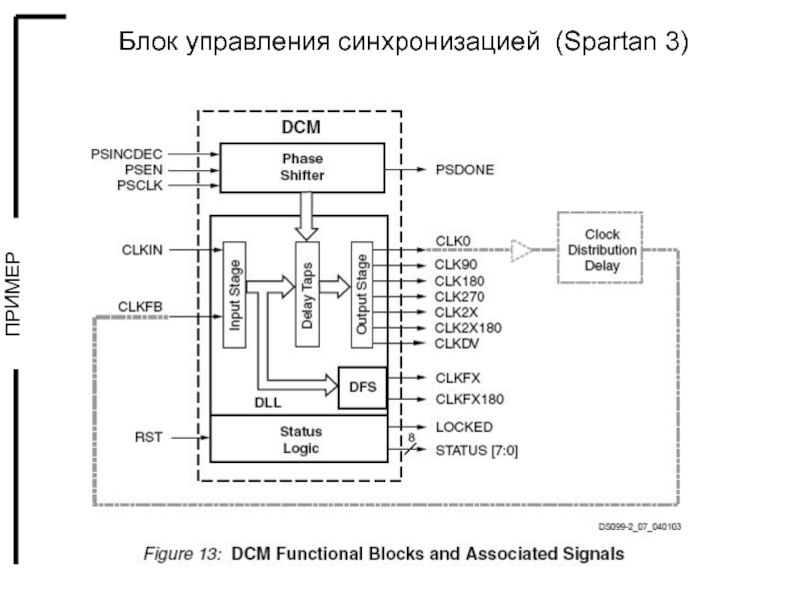

- 30. Блок управления синхронизацией (Spartan 3)

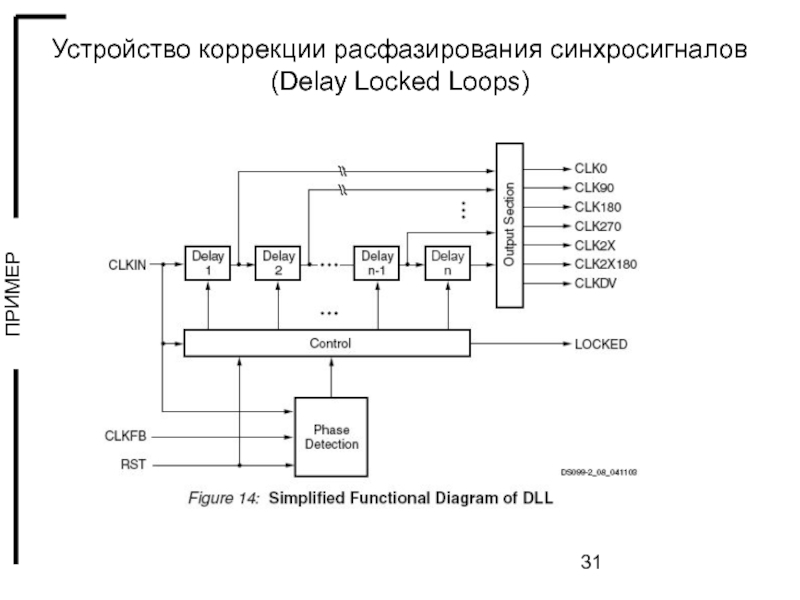

- 31. Устройство коррекции расфазирования синхросигналов (Delay Locked Loops)

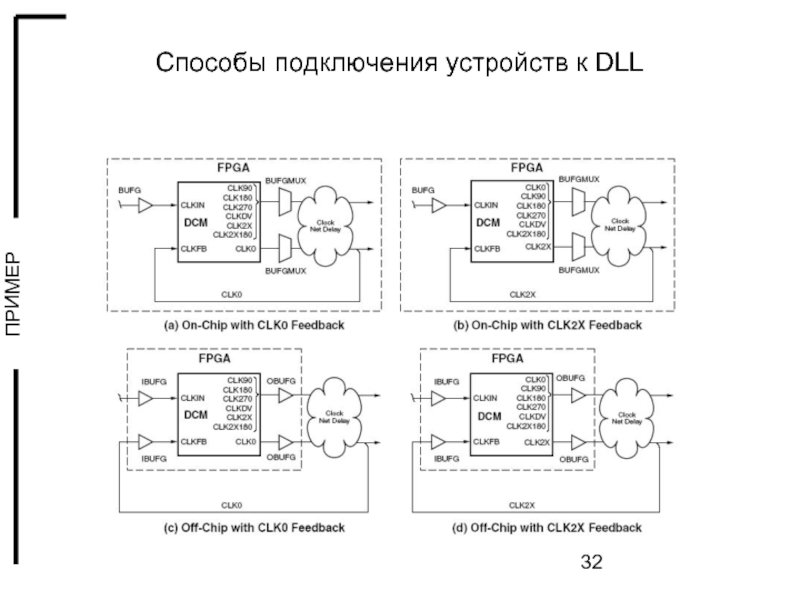

- 32. Способы подключения устройств к DLL

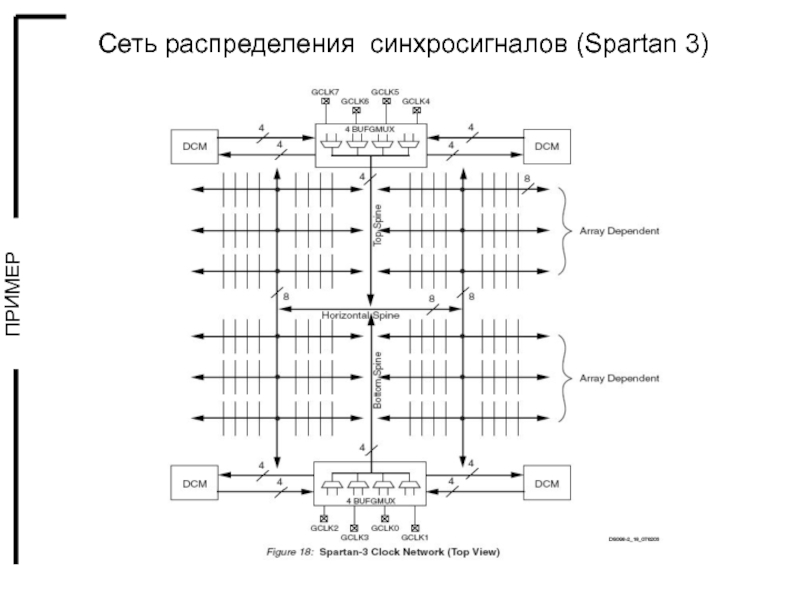

- 33. Сеть распределения синхросигналов (Spartan 3)

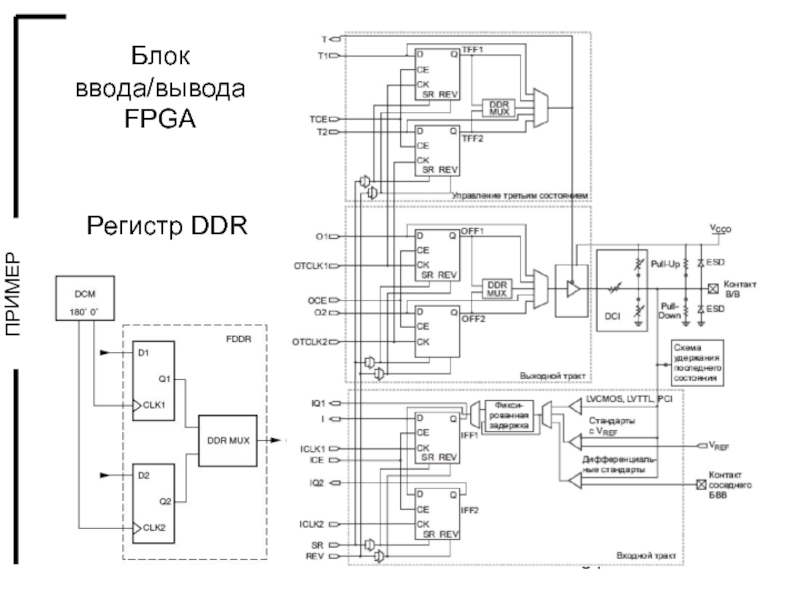

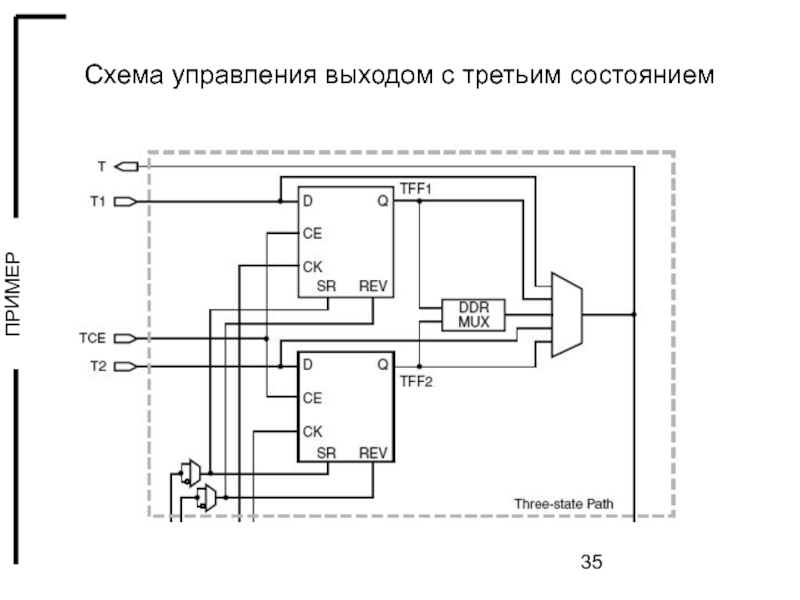

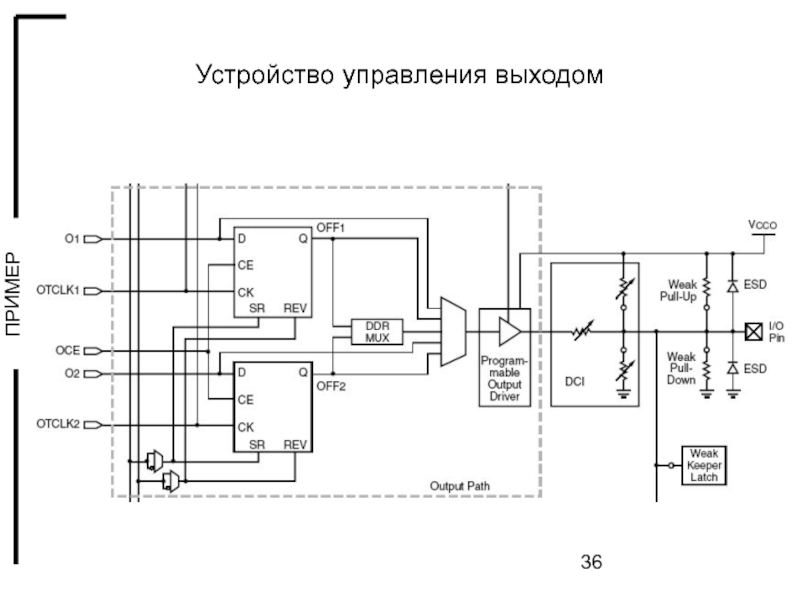

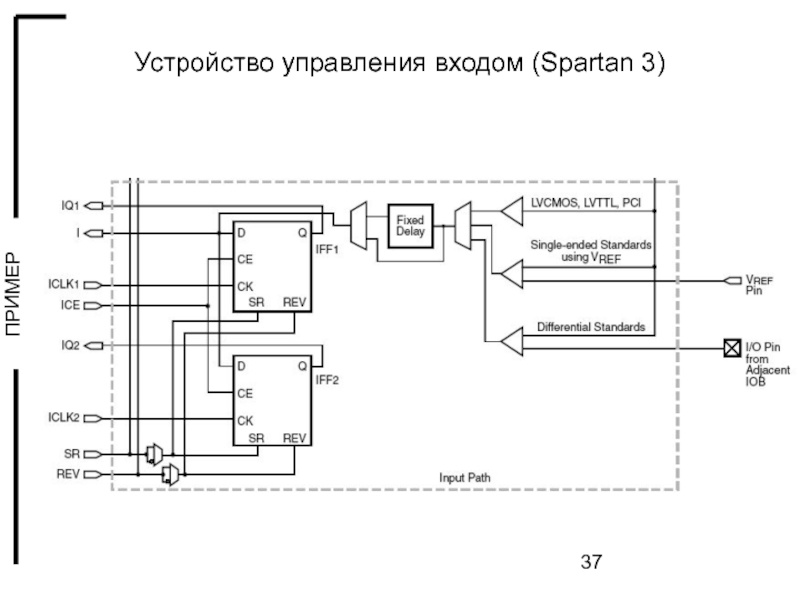

- 34. Блок ввода/вывода FPGA Регистр DDR

- 35. Схема управления выходом с третьим состоянием

- 36. Устройство управления выходом

- 37. Устройство управления входом (Spartan 3)

- 38. Матрица коммутации КЛБ (Spartan 3)

- 39. Конфигурация ПЛИС (на примере Spartan 3) Конфигурация

- 40. Последовательная конфигурация (Master Serial) Схема конфигурирования по JTAG интерфейсу (3.3 V)

- 41. SPI конфигурация с внутренней Flash (Master SPI

- 42. BPI конфигурация (Master BPI) Параллельная конфигурация (Master Parallel)

- 43. Последовательная конфигурация (Slave Serial) JTAG конфигурация (JTAG) Параллельная конфигурация (SelectMap)

- 44. Архитектура ПЛИС типа SOPC Варианты реализации библиотечных

- 45. Преимущества систем на плате: – использование

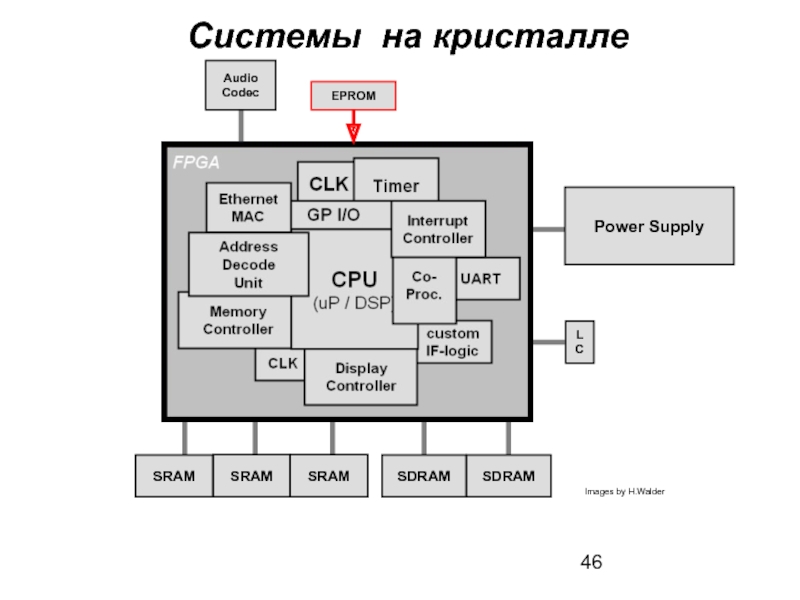

- 46. Системы на кристалле

- 47. –возможность получения более высоких технических показателей (производительность,

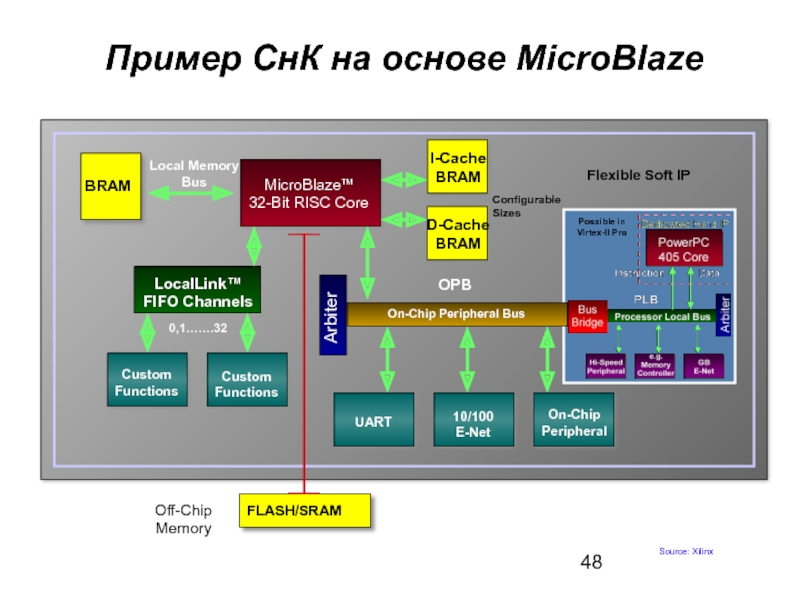

- 48. Пример СнК на основе MicroBlaze

Слайд 1II.Средства проектирования цифровых устройств с использованием программируемых логических интегральных схем

Архитектура

Основы языка VHDL и Verilog.

Процесс проектирования цифровых устройств с использованием ПЛИС.

Слайд 2V.I Архитектура интегральных схем с программируемой структурой (ПЛИС)

Список дополнительной литературы:

Грушвицкий Р.

Сергиенко А. М. VHDL для проектирования вычислительных устройств – К ЧП «Корнейчук», ООО «ТИД «ДС», 2003 – 208 с.

Зотов В. Ю. Проектирование цифровых устройств на основе ПЛИС фирмы Xilinx в САПР WebPACK ISE. – М.: Горячая линия - Телеком, 2003. – 624 с.

IEEE VHDL-93 Standard 2000 Revision

Xilinx ISE Help

Spartan-3 FPGA Family: Complete Data Sheet. Xilinx Inc.

XC9500 CPLD Family: Complete Data Sheet. Xilinx Inc.

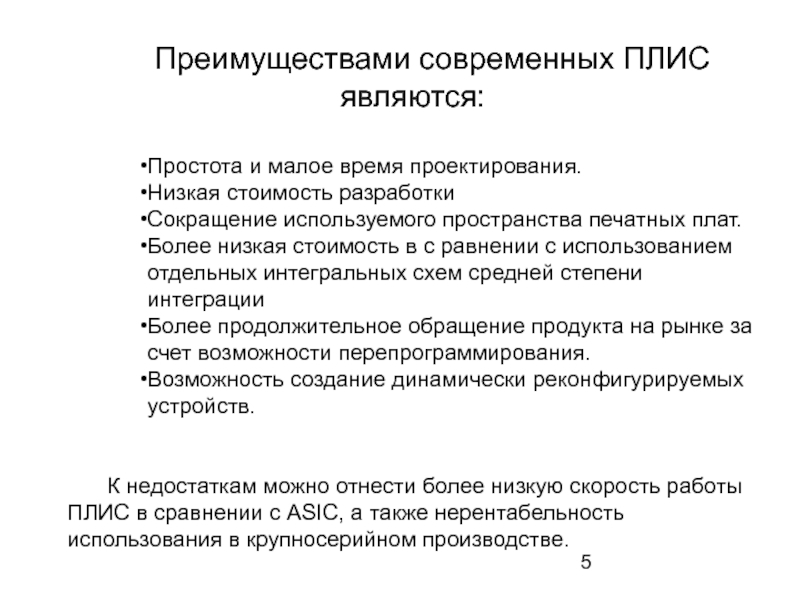

Слайд 5Преимуществами современных ПЛИС являются:

Простота и малое время проектирования.

Низкая стоимость разработки

Сокращение используемого

Более низкая стоимость в с равнении с использованием отдельных интегральных схем средней степени интеграции

Более продолжительное обращение продукта на рынке за счет возможности перепрограммирования.

Возможность создание динамически реконфигурируемых устройств.

К недостаткам можно отнести более низкую скорость работы ПЛИС в сравнении с ASIC, а также нерентабельность использования в крупносерийном производстве.

Слайд 9Расширение функциональных возможностей ПЛМ и ПМЛ возможно с использованием:

введения обратных

введения элементов памяти, что позволяет проектировать на ПМЛ и ПЛМ синхронные цифровые автоматы;

программирования выходных буферов для выдачи выходных сигналов в прямом или инверсном виде;

использования мультиплексоров для выбора альтернативных путей прохождения сигналов;

репрограммируемых точек связи и памяти конфигурации, позволяющим перепрограммировать функциональность и связность частей ПЛМ и ПМЛ.

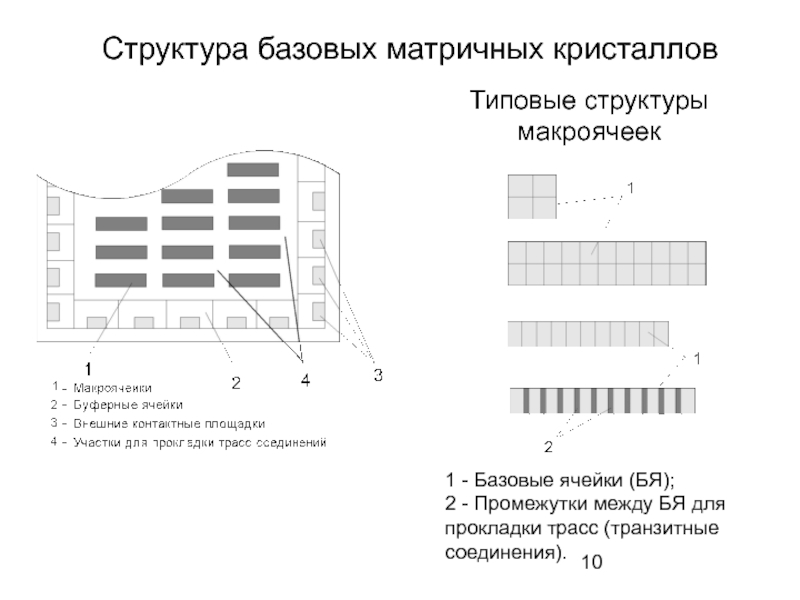

Слайд 10 Структура базовых матричных кристаллов

Типовые структуры макроячеек

1 - Базовые ячейки (БЯ);

2

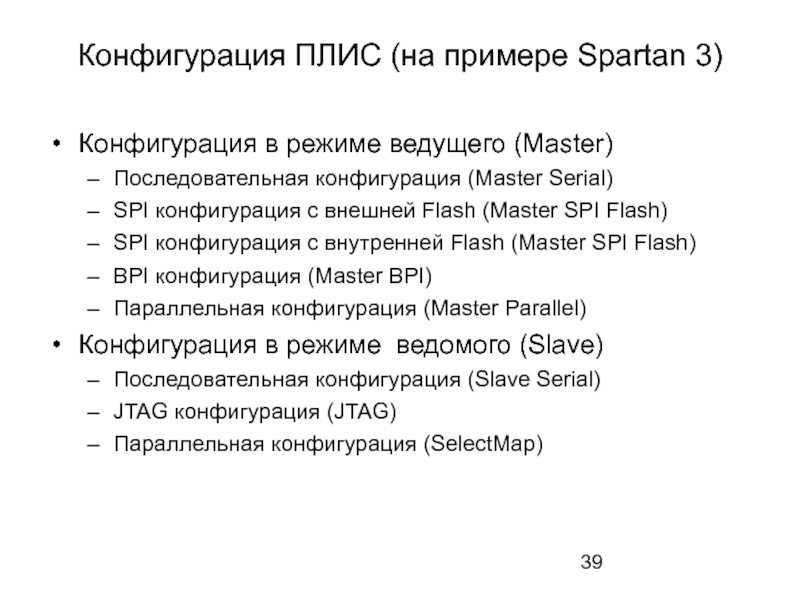

Слайд 39Конфигурация ПЛИС (на примере Spartan 3)

Конфигурация в режиме ведущего (Master)

Последовательная конфигурация

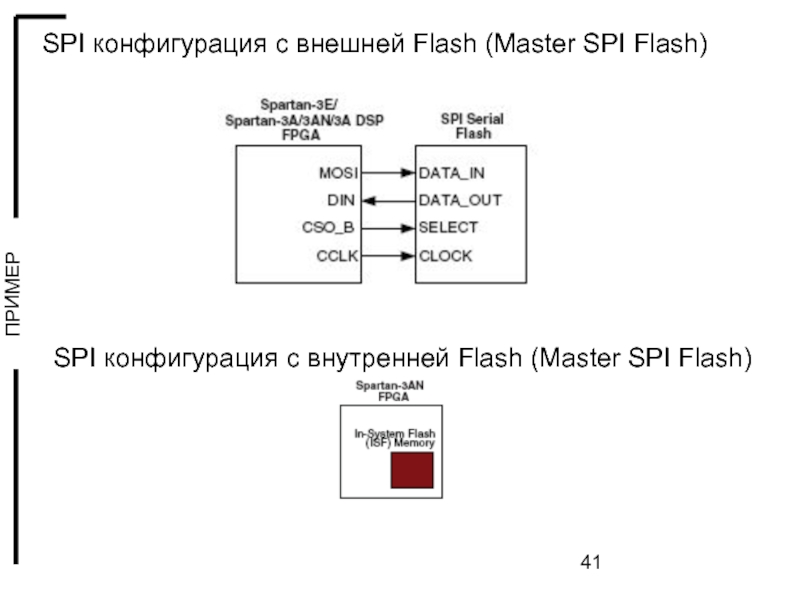

SPI конфигурация с внешней Flash (Master SPI Flash)

SPI конфигурация с внутренней Flash (Master SPI Flash)

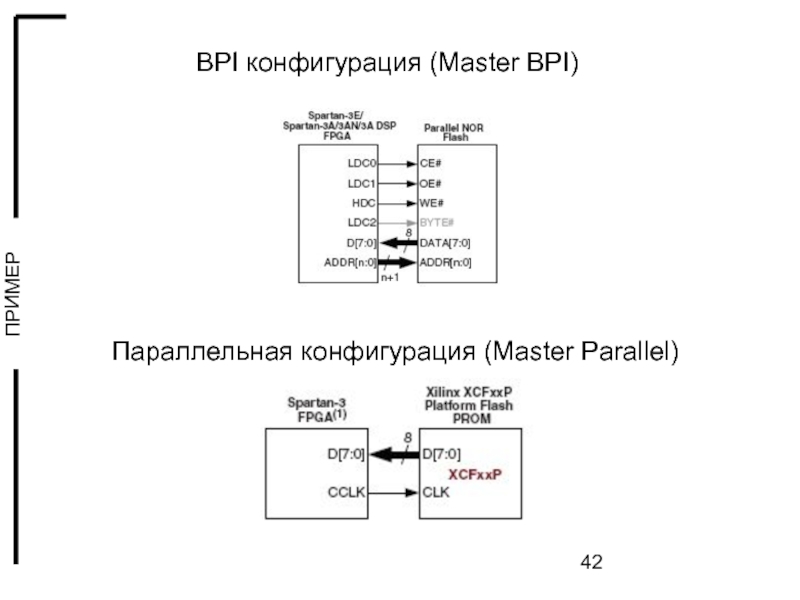

BPI конфигурация (Master BPI)

Параллельная конфигурация (Master Parallel)

Конфигурация в режиме ведомого (Slave)

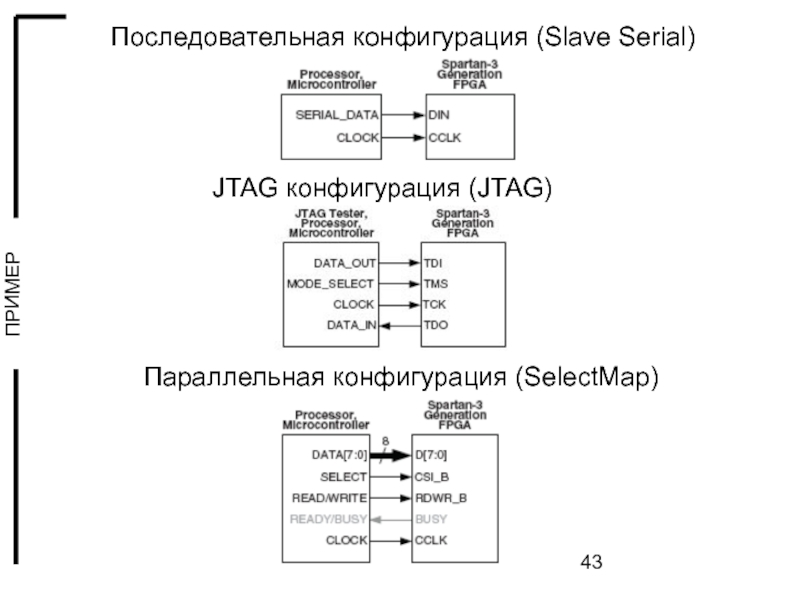

Последовательная конфигурация (Slave Serial)

JTAG конфигурация (JTAG)

Параллельная конфигурация (SelectMap)

Слайд 40Последовательная конфигурация (Master Serial)

Схема конфигурирования по JTAG интерфейсу (3.3 V)

Слайд 41SPI конфигурация с внутренней Flash (Master SPI Flash)

SPI конфигурация с внешней

Слайд 43Последовательная конфигурация (Slave Serial)

JTAG конфигурация (JTAG)

Параллельная конфигурация (SelectMap)

Слайд 44Архитектура ПЛИС типа SOPC

Варианты реализации библиотечных блоков:

Soft - ядра.

Firm

Назначение ядер:

Память (ОЗУ, FIFO, кэш- память, …).

АЛУ (умножители, …).

Интерфейсная логика (JTAG, PCI, SPI, UART, …).

МП и МК.

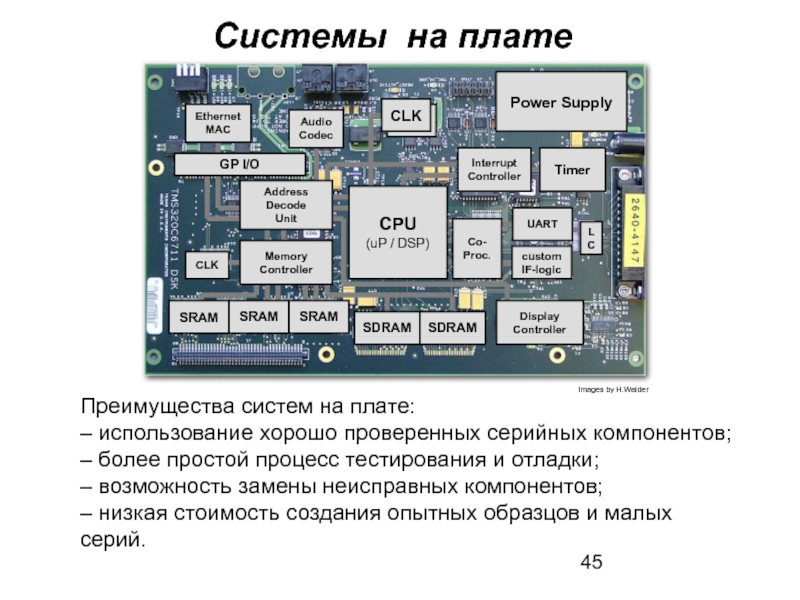

Слайд 45

Преимущества систем на плате:

– использование хорошо проверенных серийных компонентов;

– более простой

– возможность замены неисправных компонентов;

– низкая стоимость создания опытных образцов и малых серий.

Системы на плате

Слайд 47–возможность получения более высоких технических показателей (производительность, энергопотребление, массогабаритные характеристики);

– более

– малые затраты на разработку и создание опытных образцов;

– возможность многократной коррекции проекта, меньше вероятность переделки платы;

– использование хорошо проверенных серийных изделий;

– более простой процесс тестирования и отладки (возможность реализации и отладки «по частям»).

Преимущества систем на кристалле: