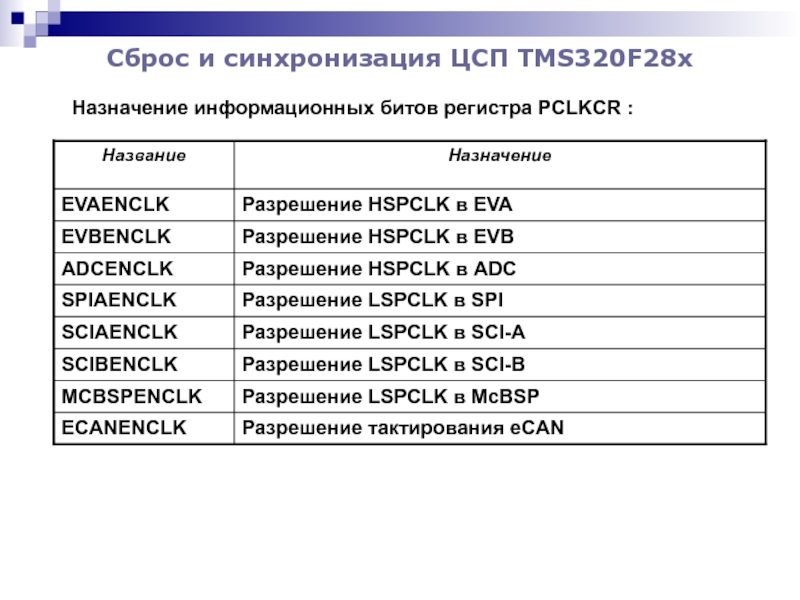

Модуль eCAN

Низкоскоростные периферийные устройства (SCI-A,B, SPI, McBSP)

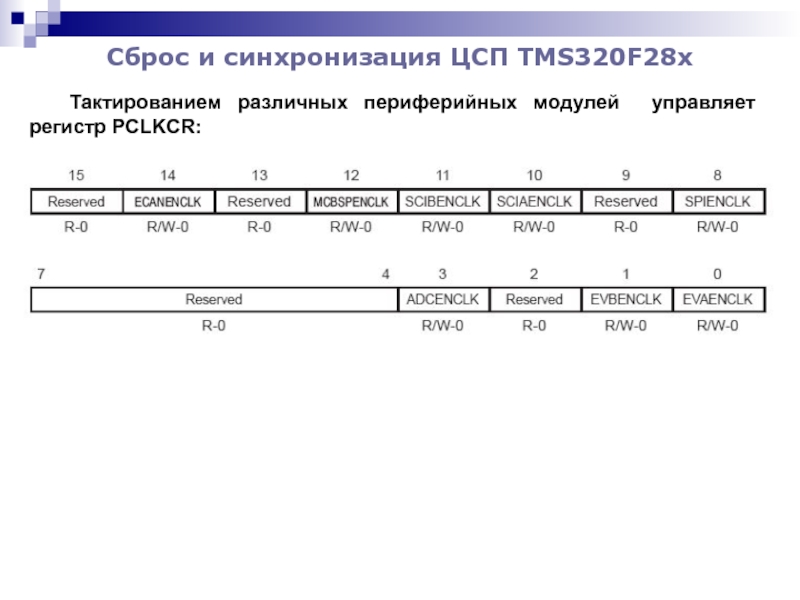

Разрешение тактирования

Высокоскоростные периферийные устройства (Менеджеры событий A,B)

АЦП (12 бит)

16 входов АЦП

Линии I/O

Регистры управления системой

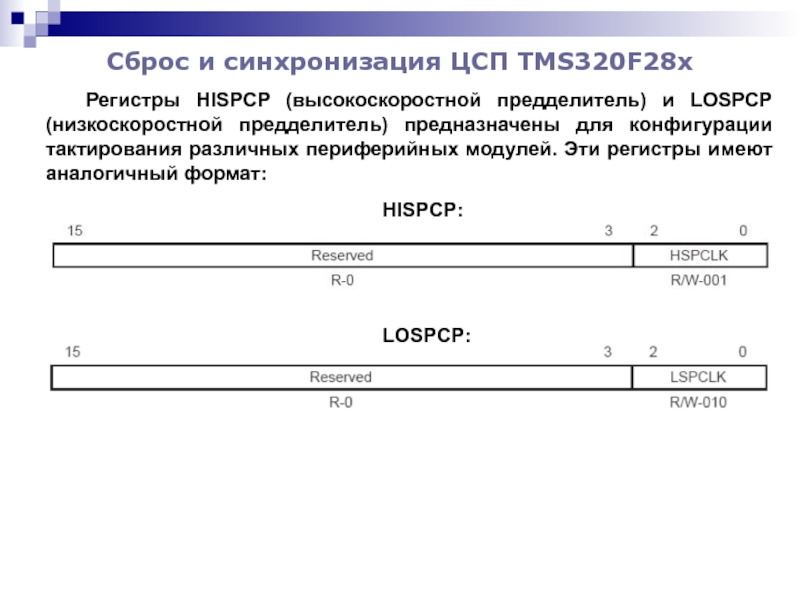

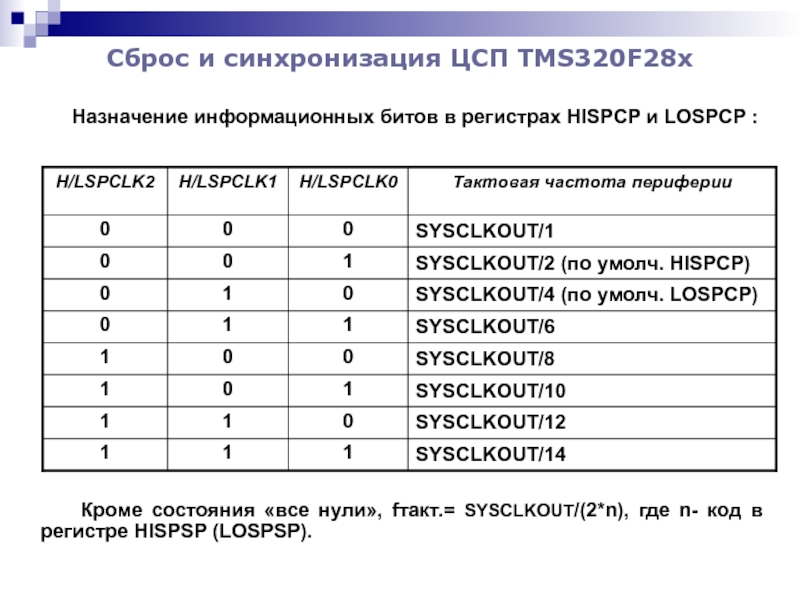

Низкоскоростной предделитель

Высокоскоростной предделитель

Регистры периферии

Регистры периферии

Регистры периферии

Регистры АЦП