- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

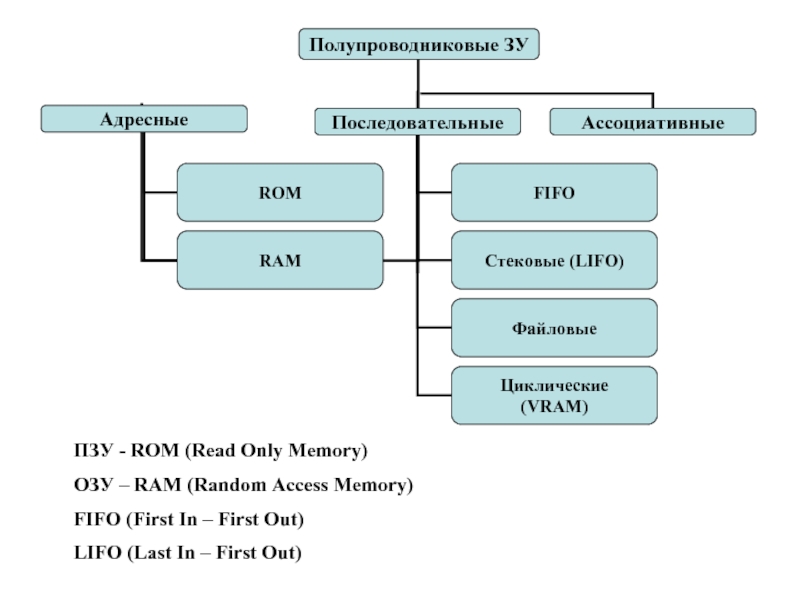

Полупроводниковые ЗУ презентация

Содержание

- 1. Полупроводниковые ЗУ

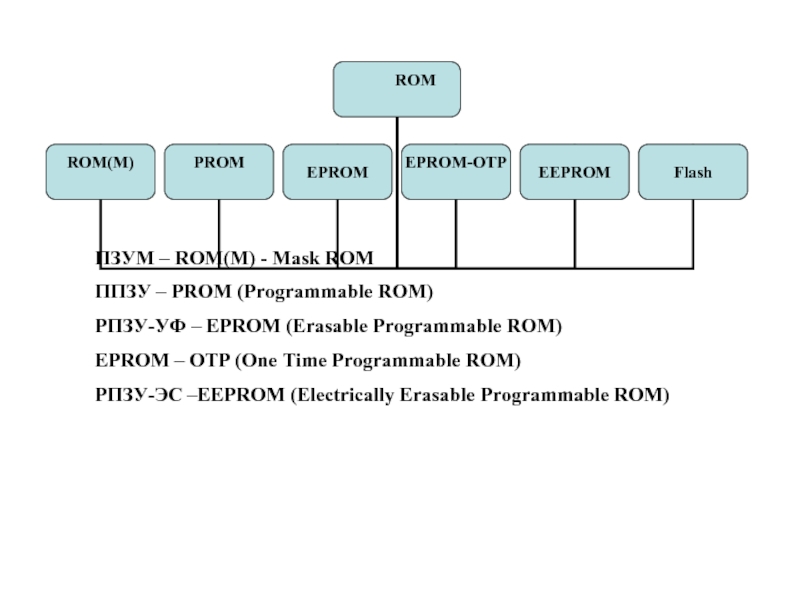

- 2. ПЗУМ – ROM(M) - Mask ROM ППЗУ

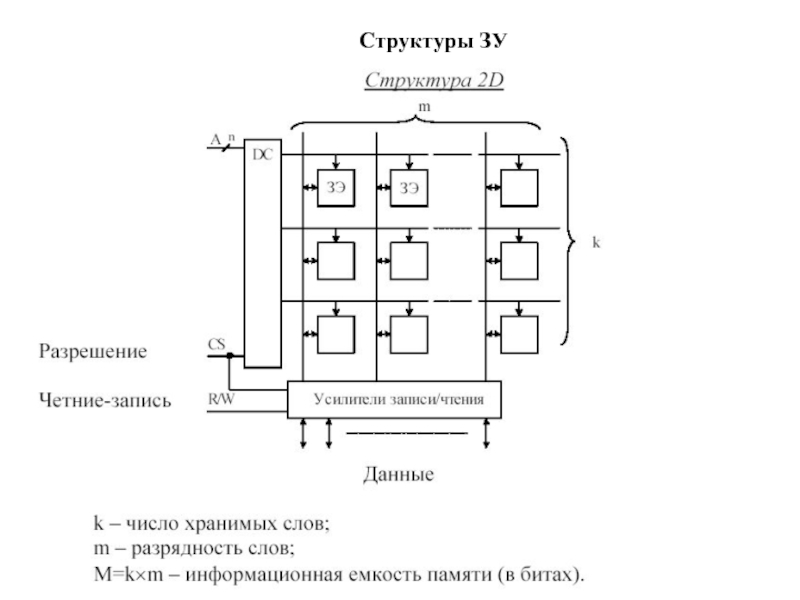

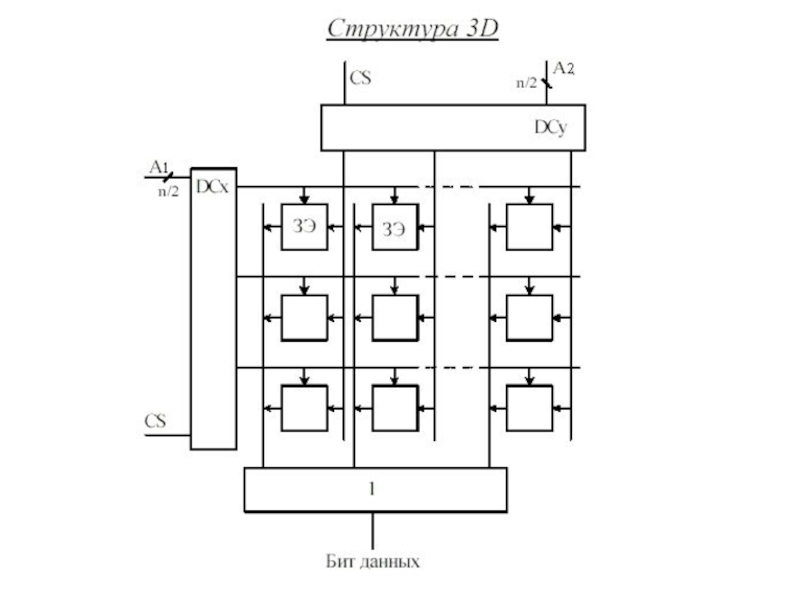

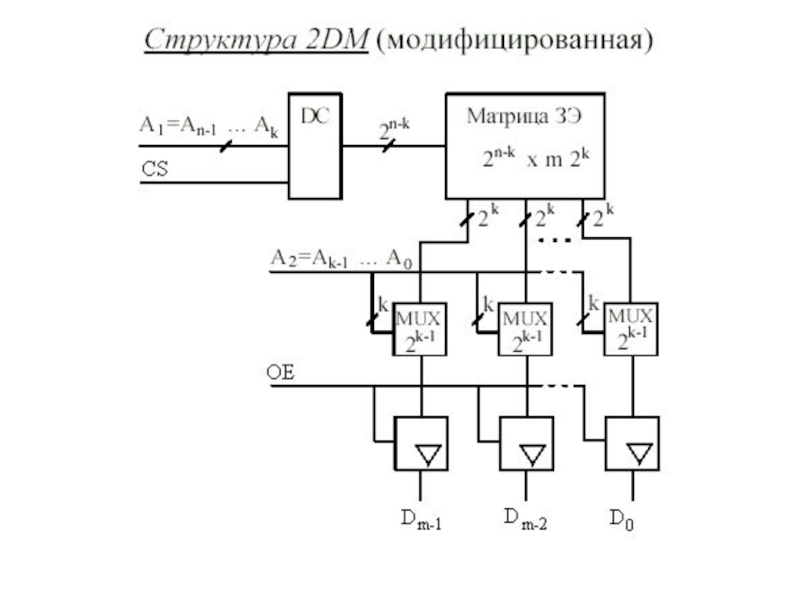

- 4. Структуры ЗУ

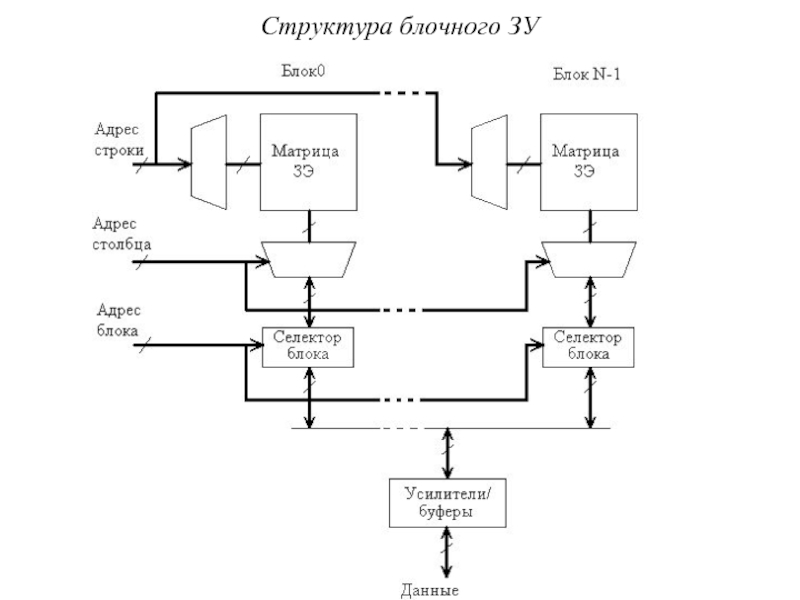

- 7. Структура блочного ЗУ

- 8. Память с последовательным доступом Структура VRAM

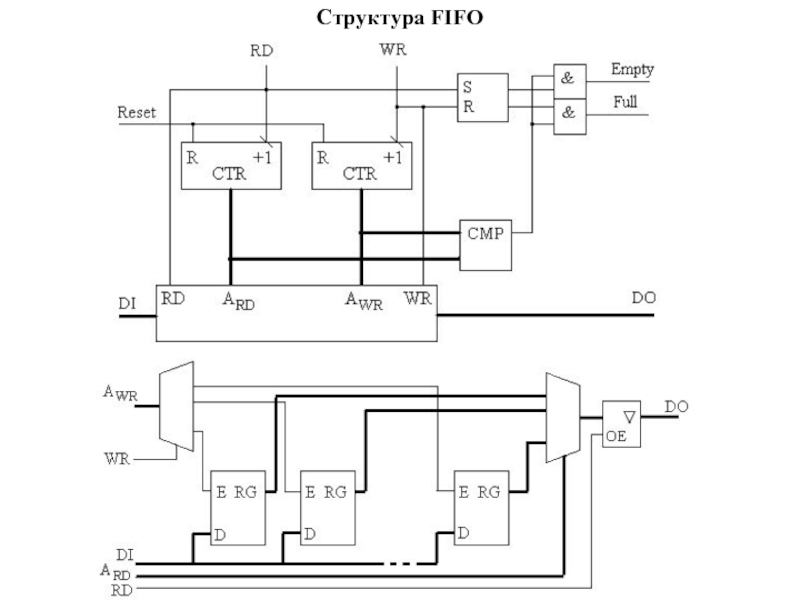

- 9. Структура FIFO

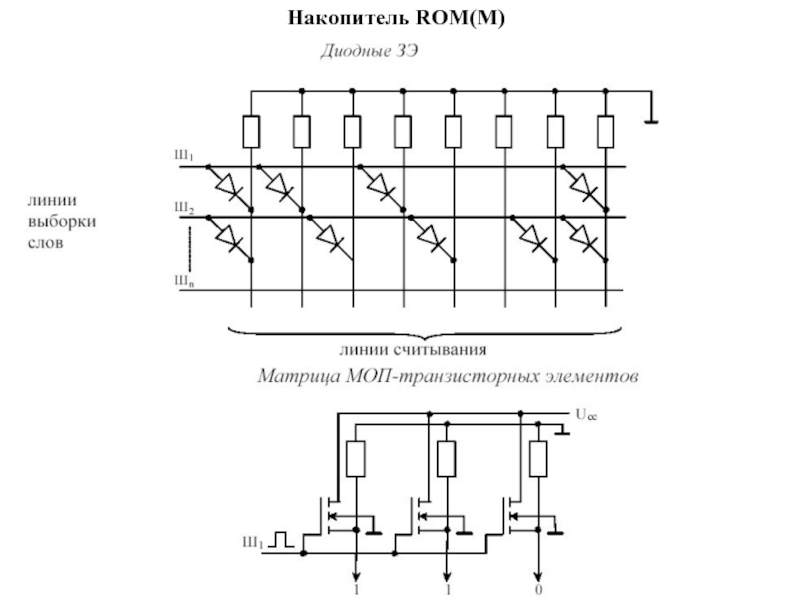

- 10. Накопитель ROM(M)

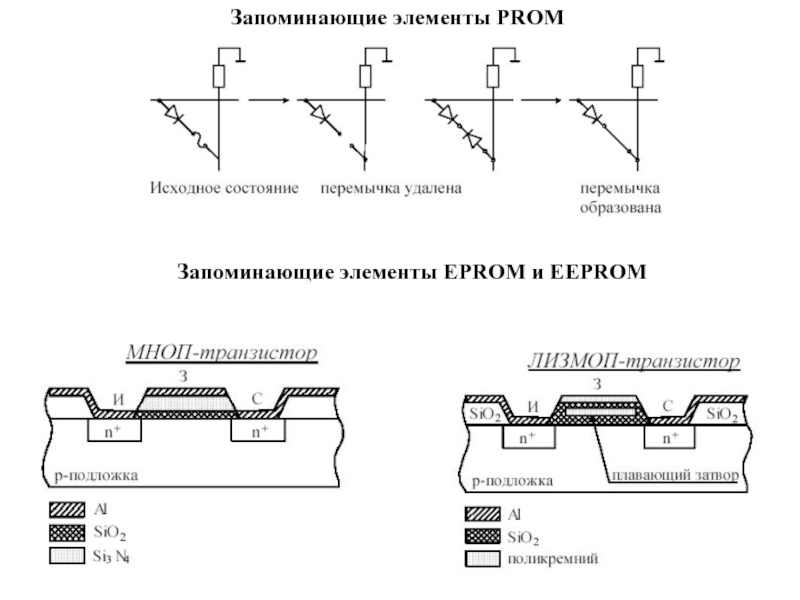

- 11. Запоминающие элементы PROM Запоминающие элементы EPROM и EEPROM

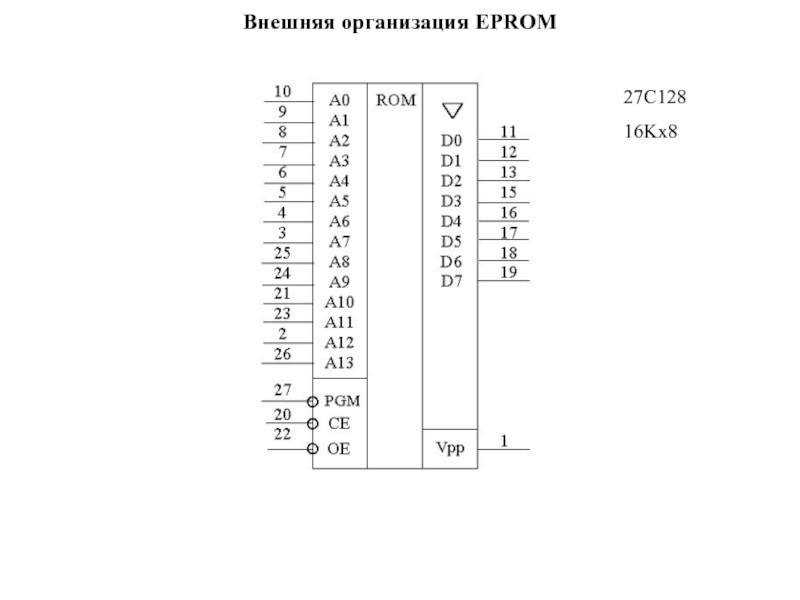

- 12. Внешняя организация EPROM 27C128 16Kx8

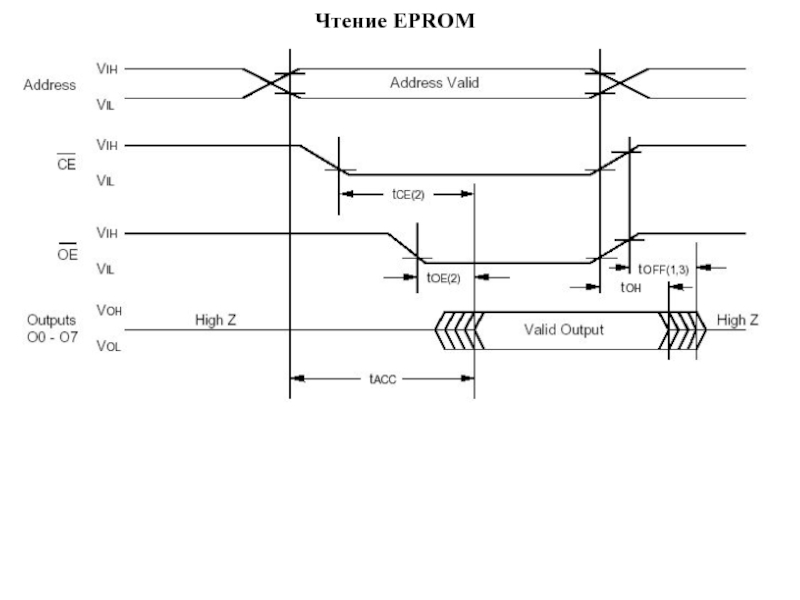

- 13. Чтение EPROM

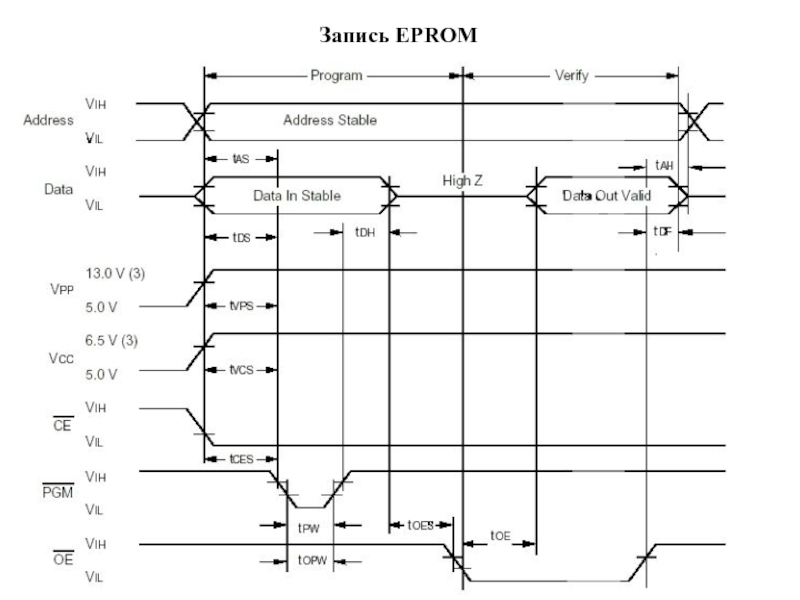

- 14. Запись EPROM

- 15. Внешняя организация EEPROM 28С64 8Кх8

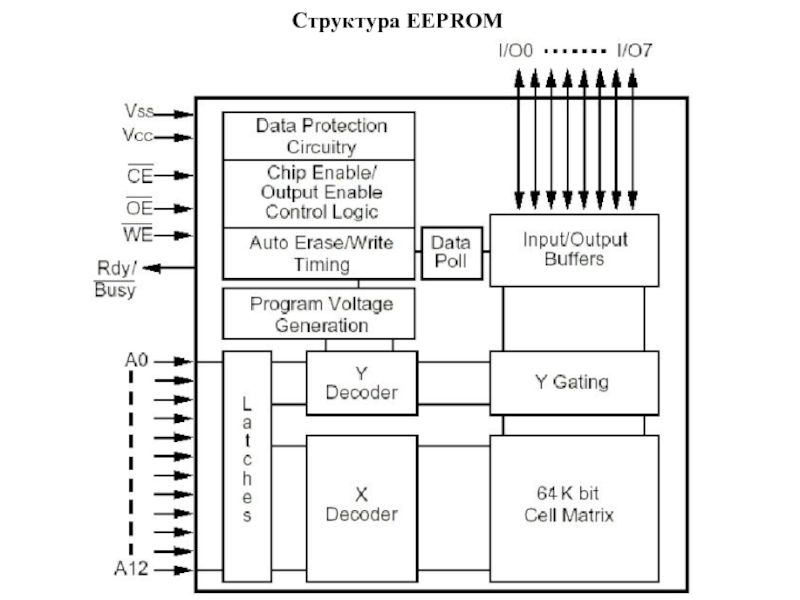

- 16. Структура EEPROM

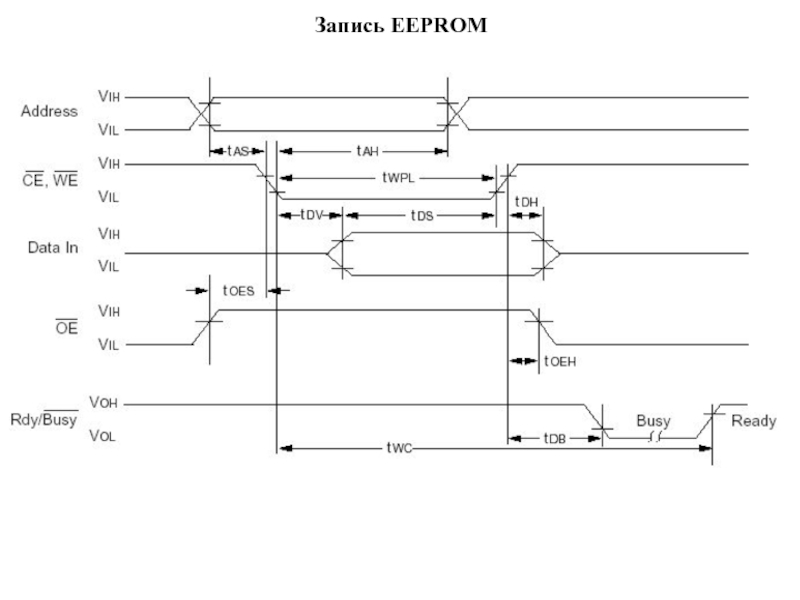

- 17. Запись EEPROM

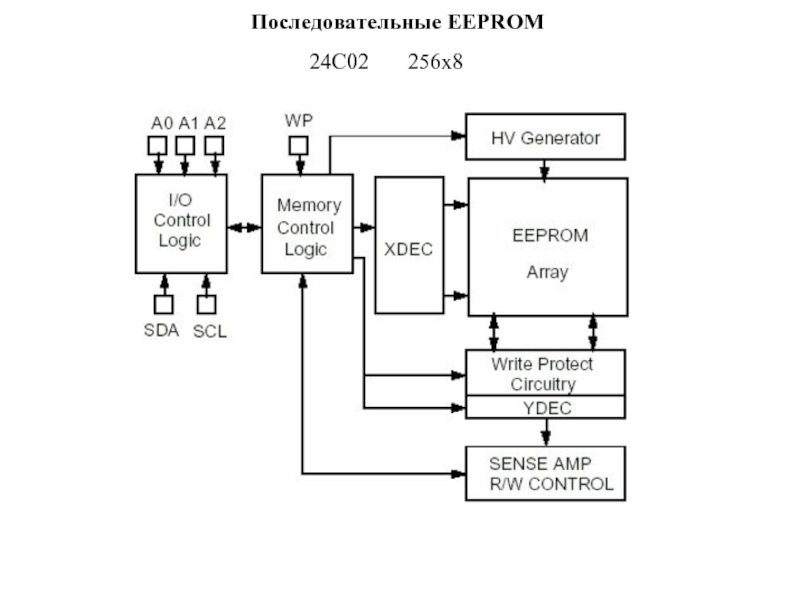

- 18. Последовательные EEPROM 24С02 256х8

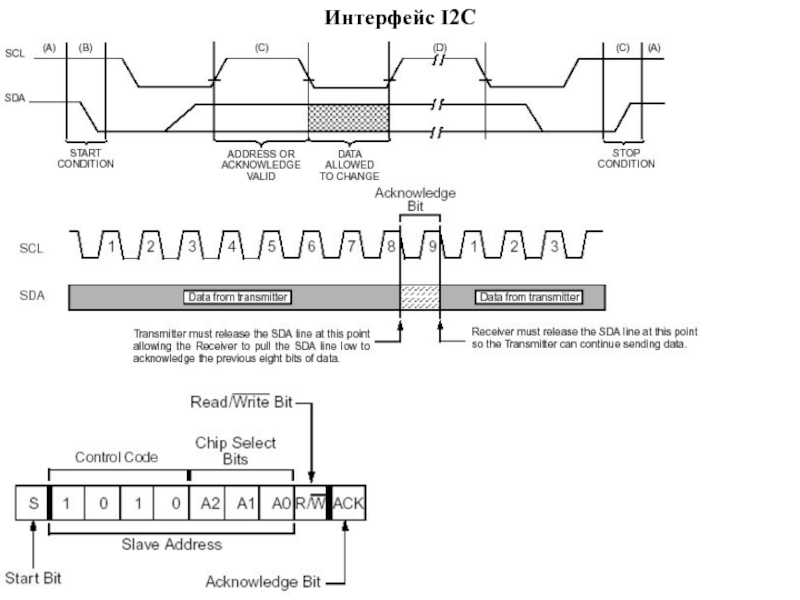

- 19. Интерфейс I2C

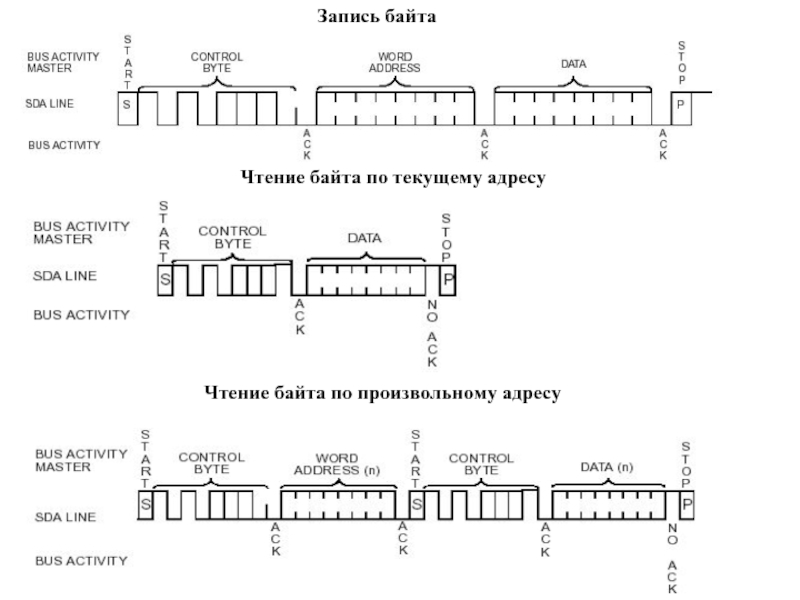

- 20. Запись байта Чтение байта по текущему адресу Чтение байта по произвольному адресу

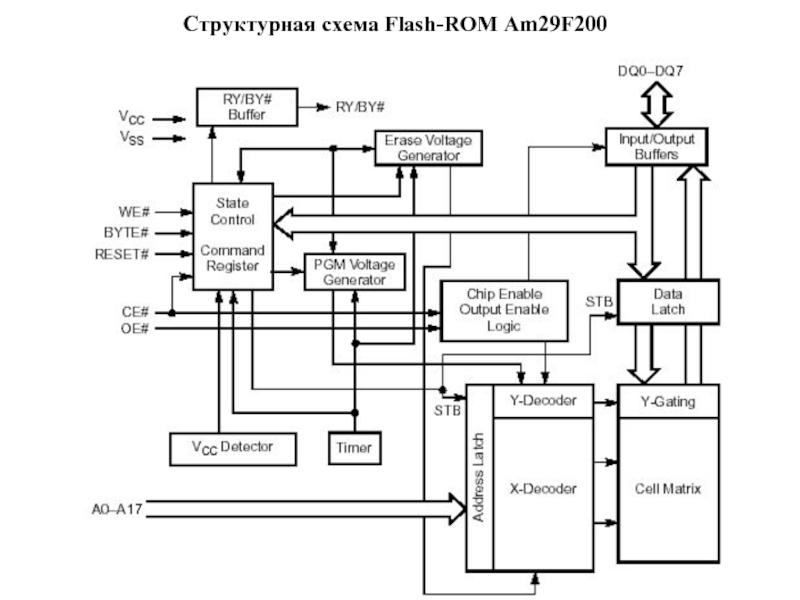

- 21. Структурная схема Flash-ROM Am29F200

- 22. Режимы работы Flash ROM SA0 00000h –

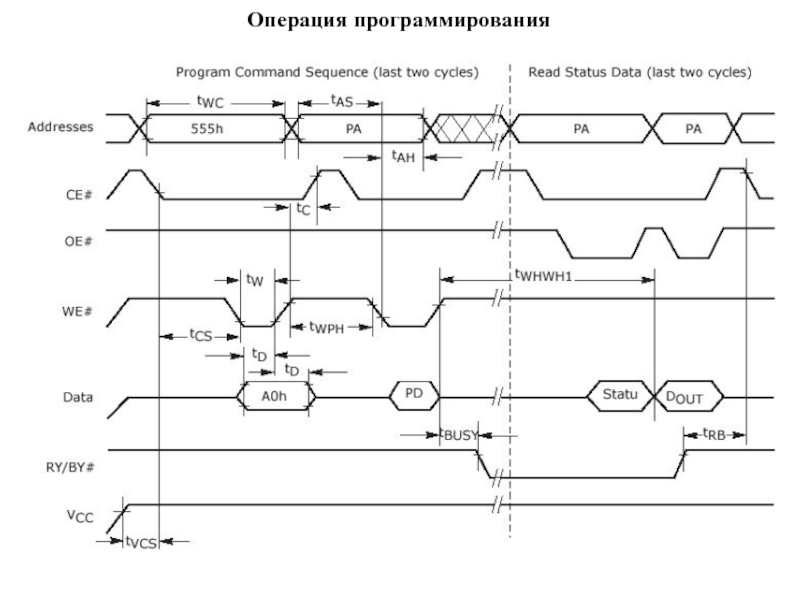

- 23. Операция программирования

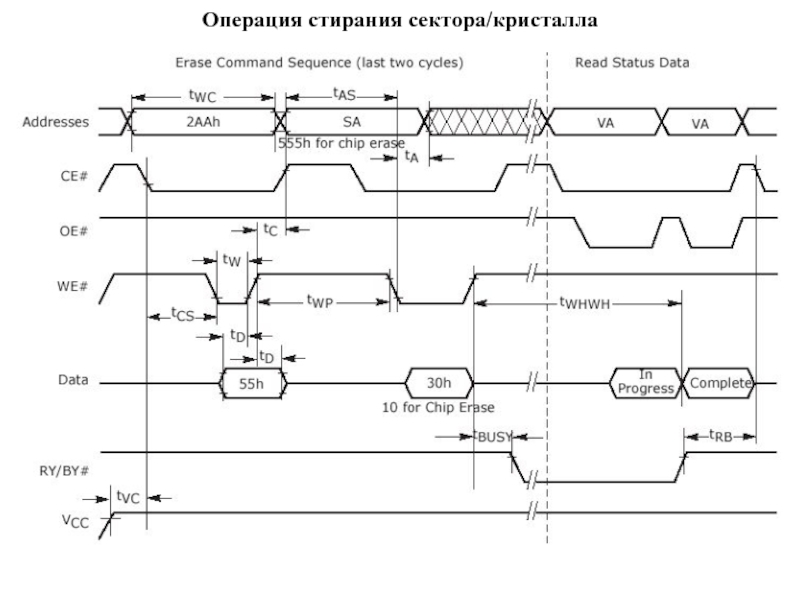

- 24. Операция стирания сектора/кристалла

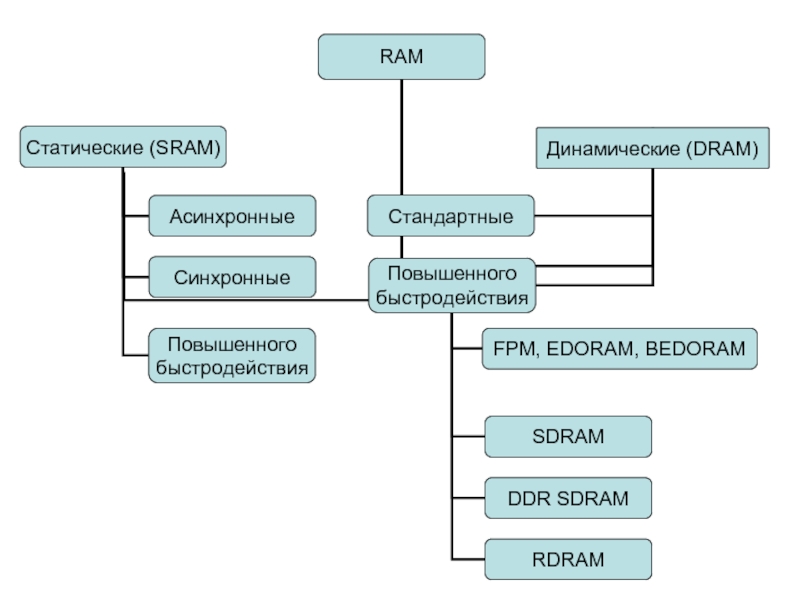

- 25. Запоминающие элементы n-МОП КМОП Статические ЗУ

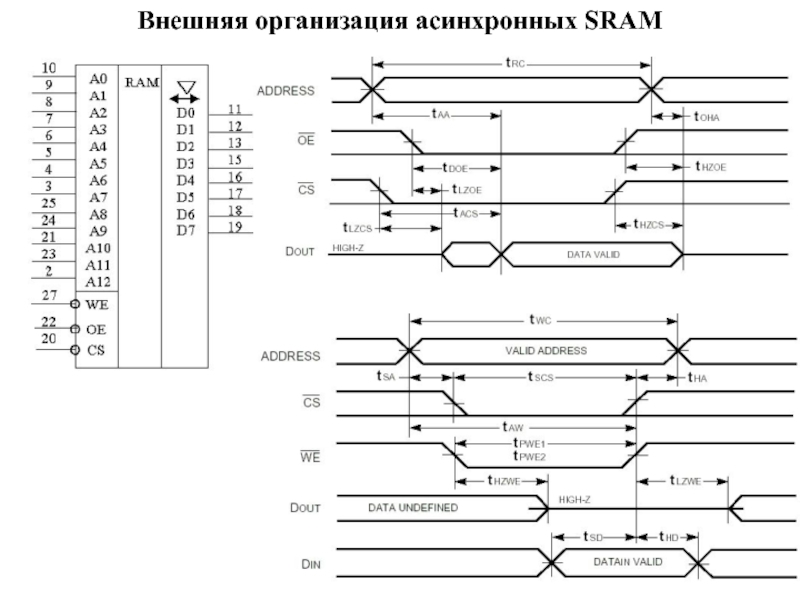

- 26. Внешняя организация асинхронных SRAM

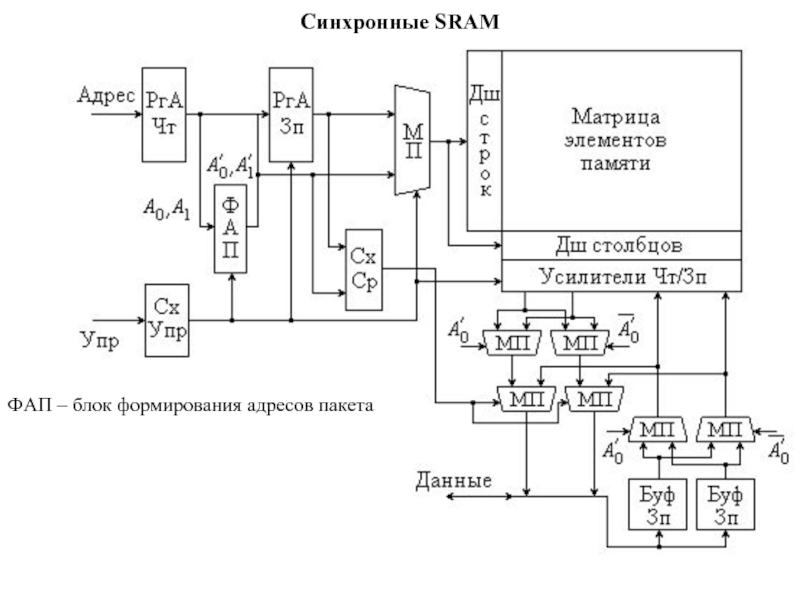

- 27. Синхронные SRAM ФАП – блок формирования адресов пакета

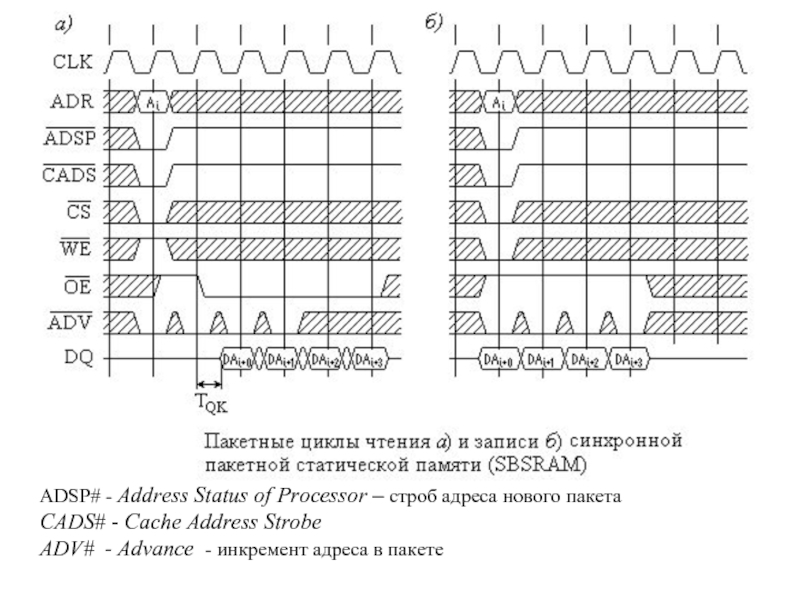

- 28. ADSP# - Address Status of Processor –

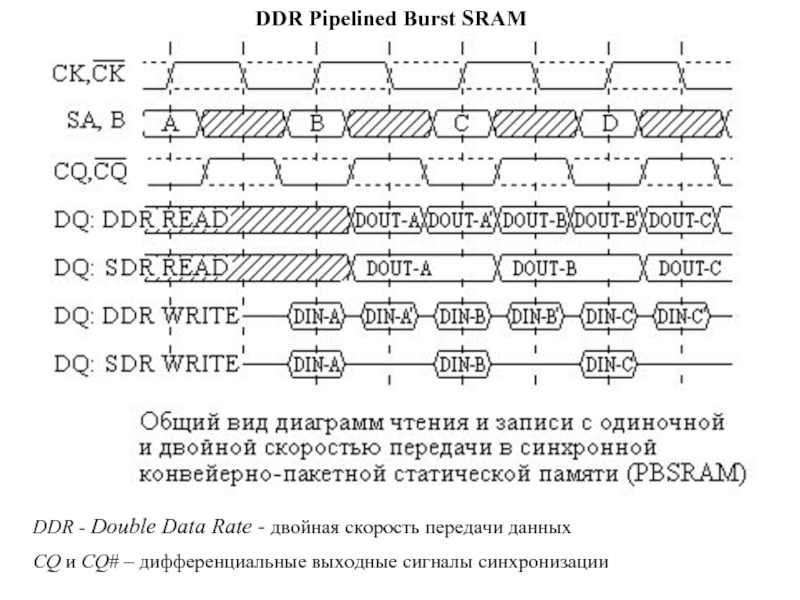

- 29. DDR Pipelined Burst SRAM DDR - Double

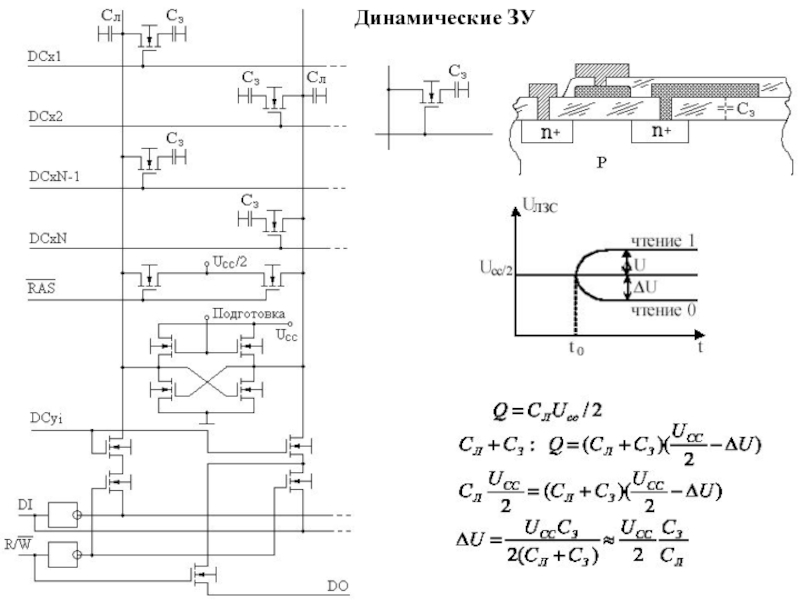

- 30. Динамические ЗУ

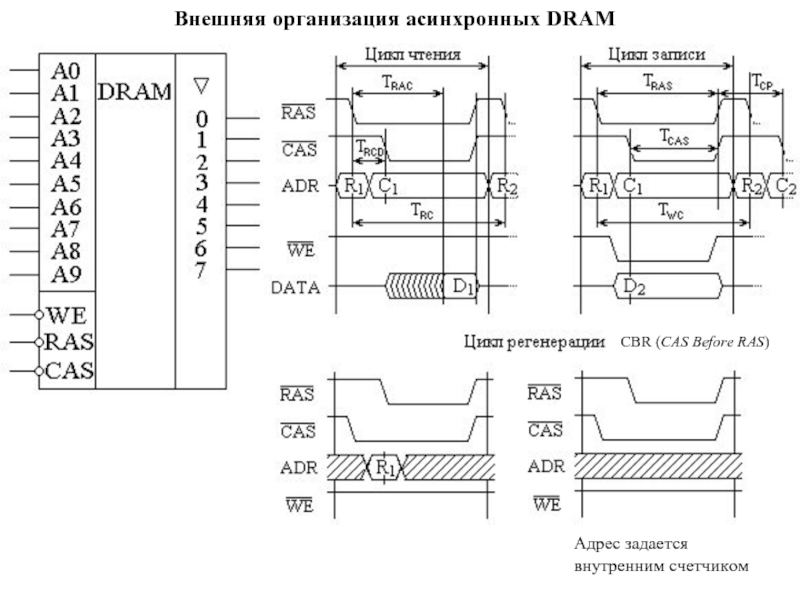

- 31. Внешняя организация асинхронных DRAM Адрес задается внутренним счетчиком CBR (CAS Before RAS)

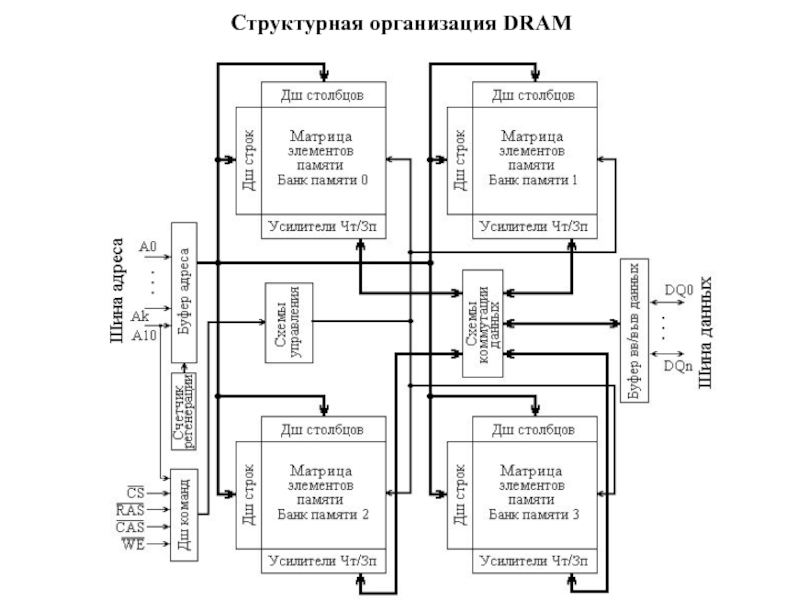

- 32. Структурная организация DRAM

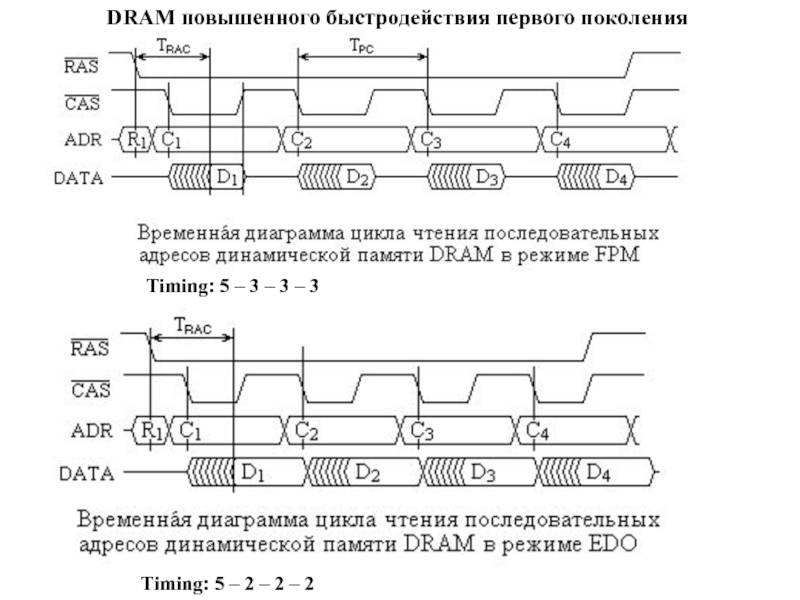

- 33. DRAM повышенного быстродействия первого поколения Timing: 5

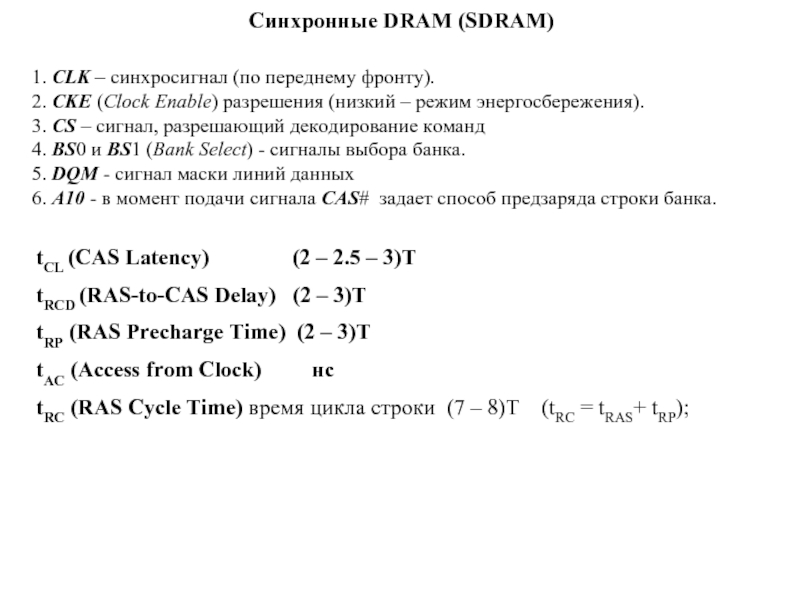

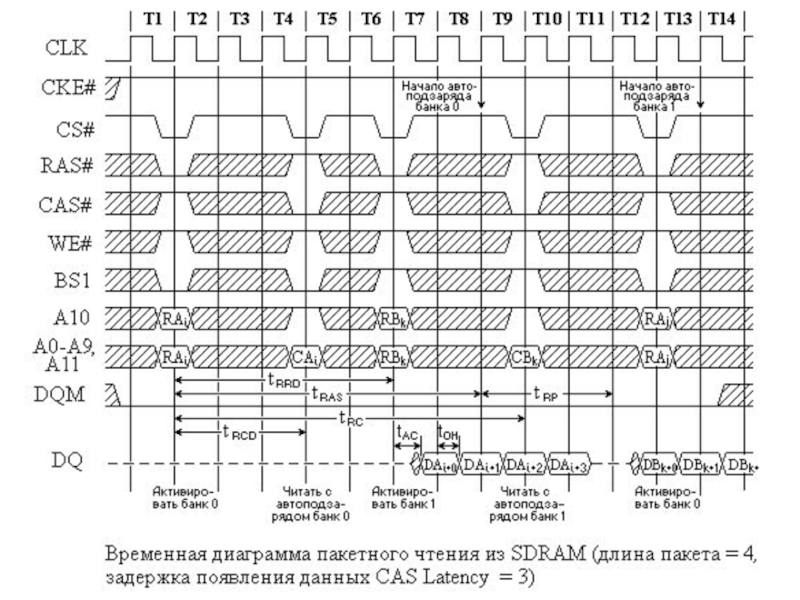

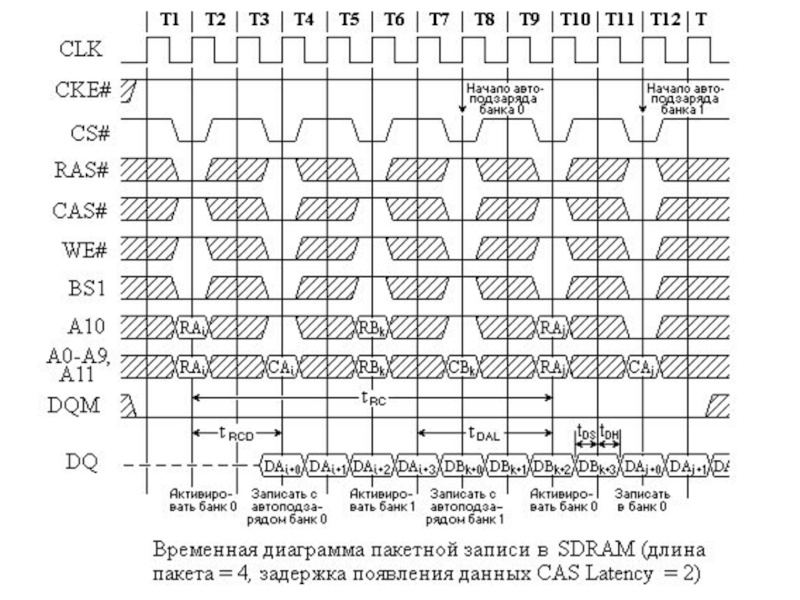

- 34. Синхронные DRAM (SDRAM) 1. CLK – синхросигнал

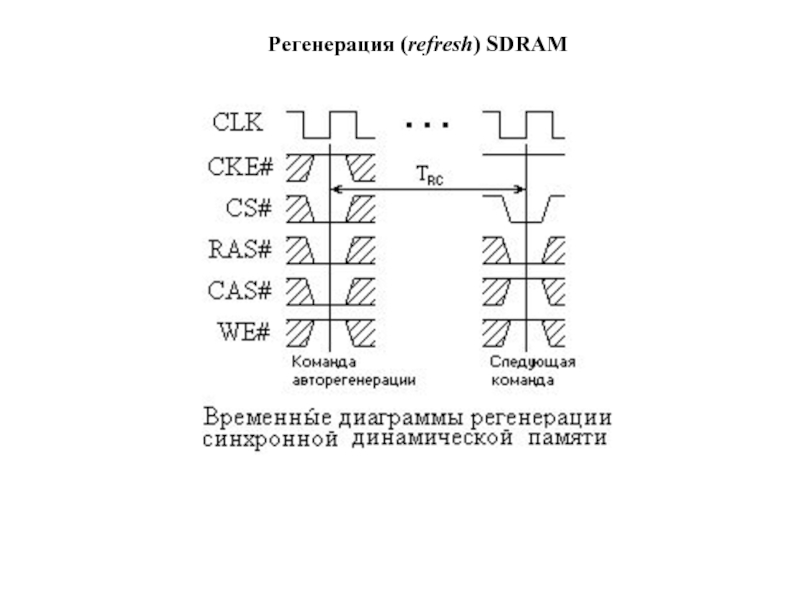

- 37. Регенерация (refresh) SDRAM

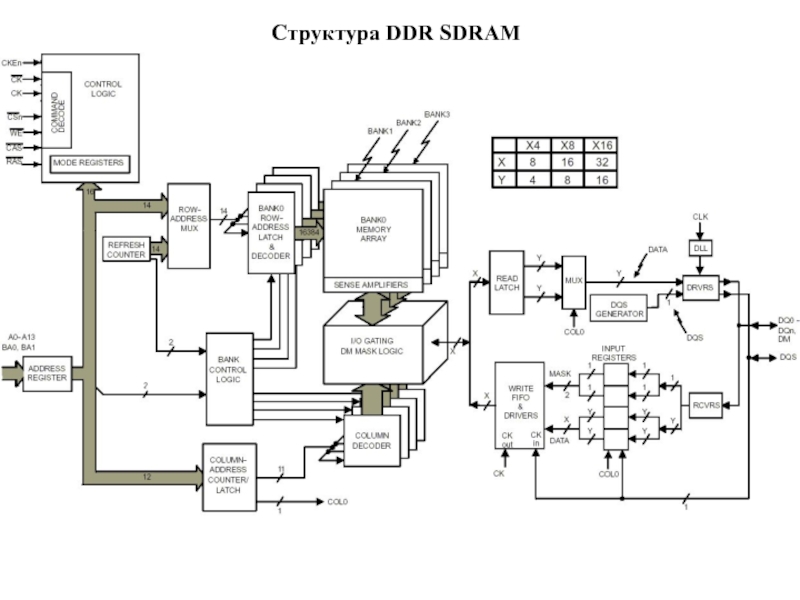

- 38. Структура DDR SDRAM

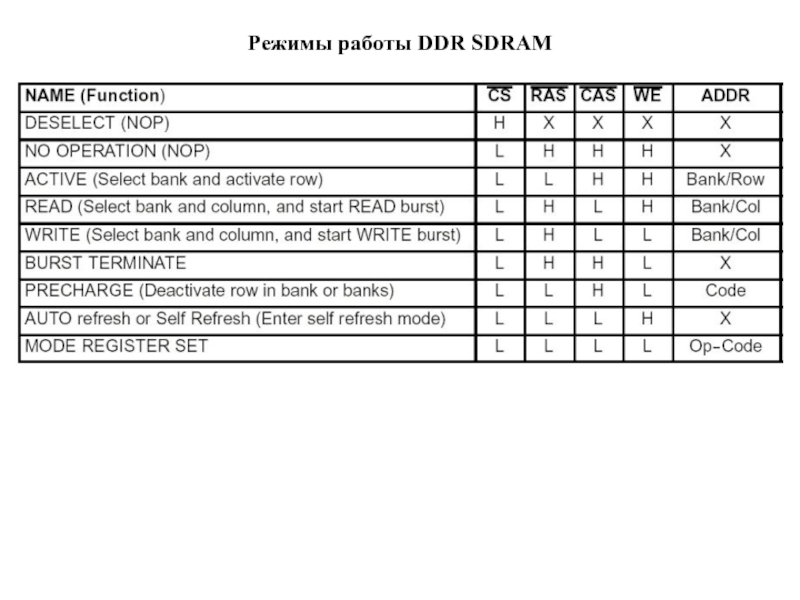

- 39. Режимы работы DDR SDRAM

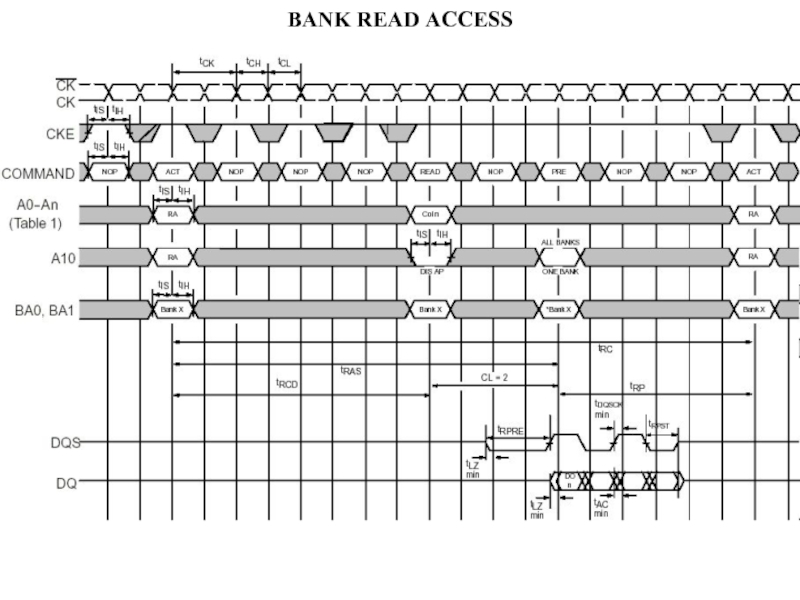

- 40. BANK READ ACCESS

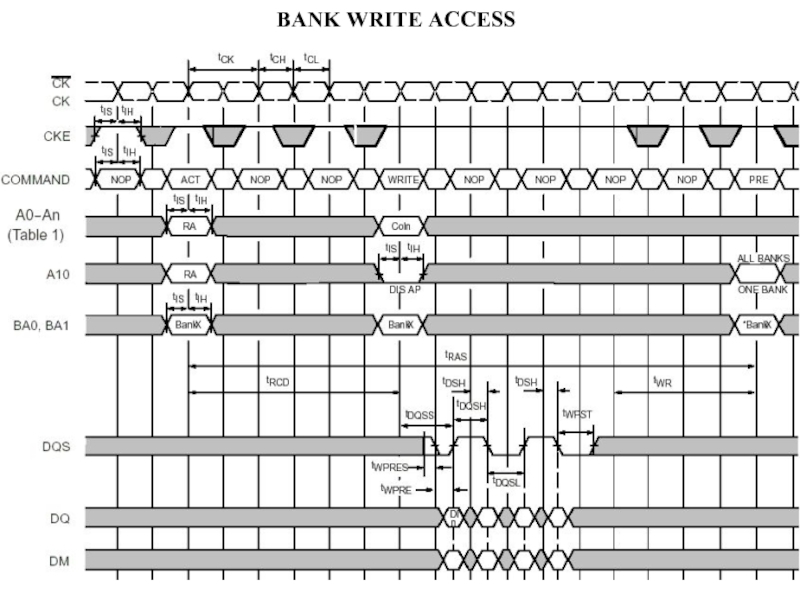

- 41. BANK WRITE ACCESS

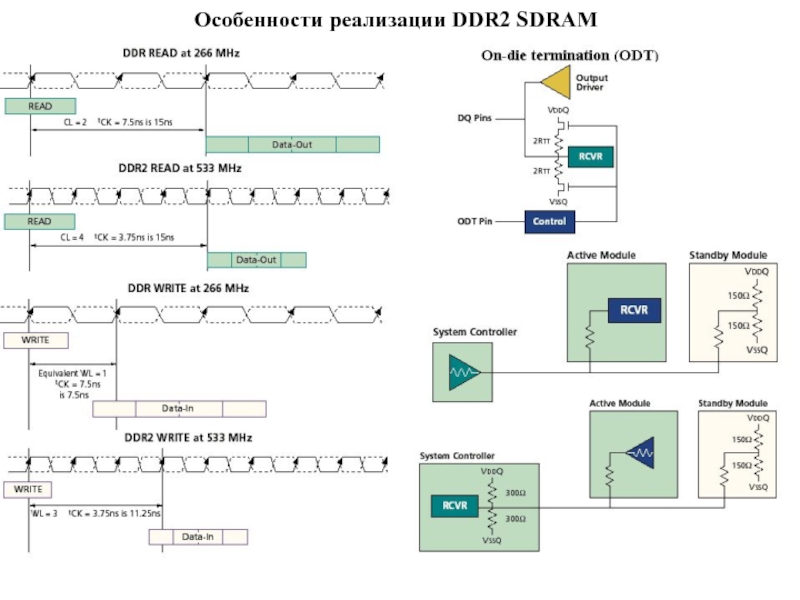

- 42. Особенности реализации DDR2 SDRAM

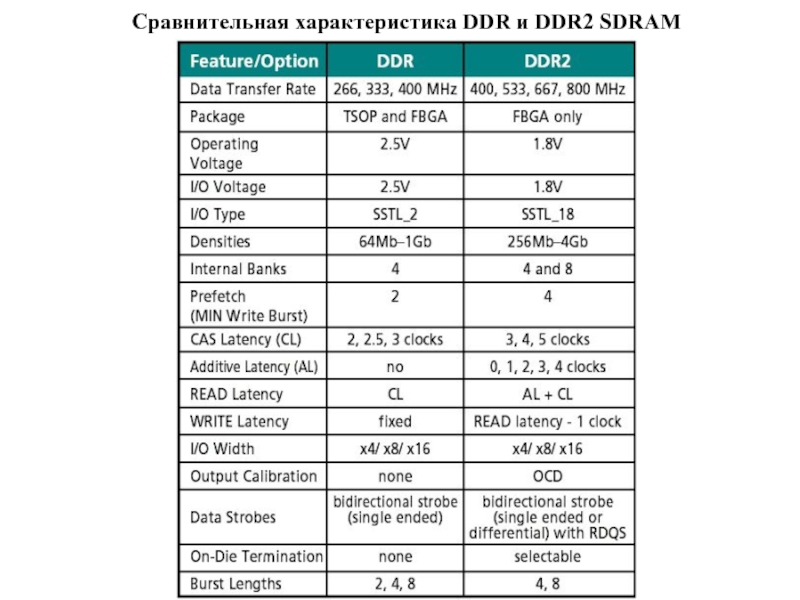

- 43. Сравнительная характеристика DDR и DDR2 SDRAM

- 44. Модули оперативной памяти SPD (Serial Presence Detect) - последовательный способ идентификации

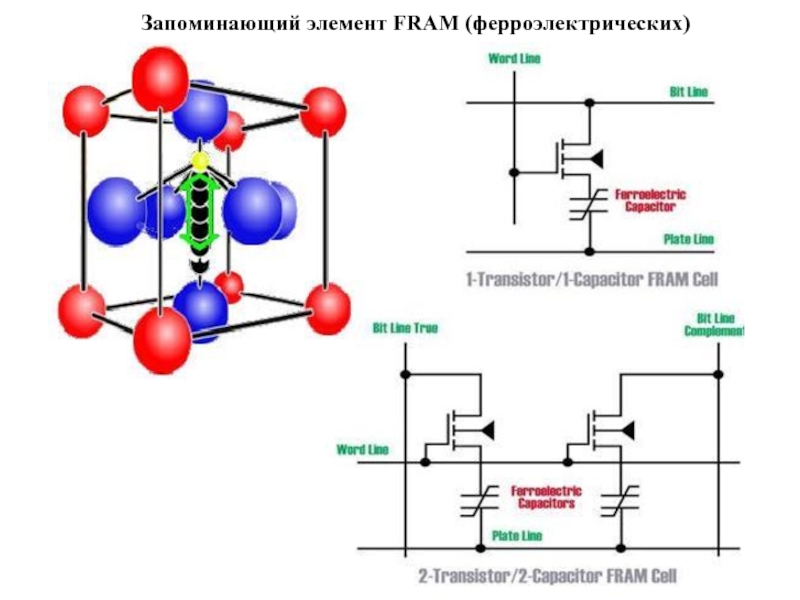

- 45. Запоминающий элемент FRAM (ферроэлектрических)

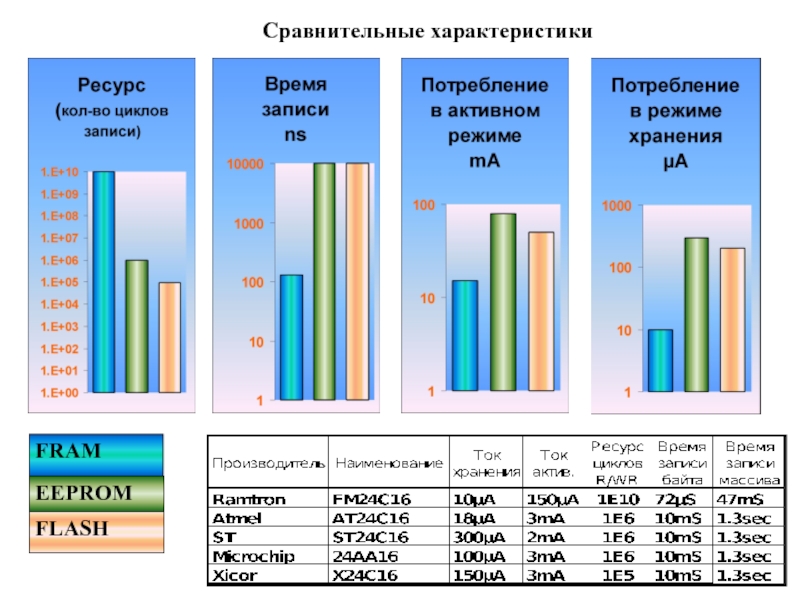

- 46. Сравнительные характеристики FRAM EEPROM FLASH

Слайд 1

ПЗУ - ROM (Read Only Memory)

ОЗУ – RAM (Random Access Memory)

FIFO

LIFO (Last In – First Out)

Слайд 2ПЗУМ – ROM(M) - Mask ROM

ППЗУ – PROM (Programmable ROM)

РПЗУ-УФ –

EPROM – OTP (One Time Programmable ROM)

РПЗУ-ЭС –EEPROM (Electrically Erasable Programmable ROM)

Слайд 22Режимы работы Flash ROM

SA0 00000h – 0FFFFh;

SA1 10000h – 1FFFFh;

SA2 20000h

SA3 30000h – 3FFFFh.

RA – адрес ячейки при чтении;

RD – считываемые данные;

PA – адрес ячейки при программировании (записи);

PD – записываемые данные;

SA – адрес стираемого сектора.

Слайд 28ADSP# - Address Status of Processor – строб адреса нового пакета

CADS#

ADV# - Advance - инкремент адреса в пакете

Слайд 29DDR Pipelined Burst SRAM

DDR - Double Data Rate - двойная скорость

CQ и CQ# – дифференциальные выходные сигналы синхронизации

Слайд 33DRAM повышенного быстродействия первого поколения

Timing: 5 – 3 – 3 –

Timing: 5 – 2 – 2 – 2

Слайд 34Синхронные DRAM (SDRAM)

1. CLK – синхросигнал (по переднему фронту).

2. CKE

3. CS – сигнал, разрешающий декодирование команд

4. BS0 и BS1 (Bank Select) - сигналы выбора банка.

5. DQM - сигнал маски линий данных

6. A10 - в момент подачи сигнала CAS# задает способ предзаряда строки банка.

tCL (CAS Latency) (2 – 2.5 – 3)T

tRCD (RAS-to-CAS Delay) (2 – 3)T

tRP (RAS Precharge Time) (2 – 3)T

tAC (Access from Clock) нс

tRC (RAS Cycle Time) время цикла строки (7 – 8)T (tRC = tRAS+ tRP);