- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Модели процессоров и их характеристики. (Лекция 4) презентация

Содержание

- 1. Модели процессоров и их характеристики. (Лекция 4)

- 2. Конвейер процессора Intel 8086. Микропроцессор Intel

- 3. История процессоров фирмы Intel началась

- 4. Процессор Intel 4004

- 5. Процессор Intel 8080 В 1974 году

- 6. На базе микропроцессора Intel 8080 компания

- 7. Процессор Intel 8085 Следующим этапом стал

- 8. Процессор Intel 8086 Первый 16-разрядный

- 9. Технический прогресс требовал (и сейчас требует)

- 10. Общие сведения о процессоре Intel 8086

- 11. Общие сведения о процессоре Intel 8086 Функциональные

- 12. Общие сведения о процессоре Intel 8086 Процессор

- 13. 4. Структура процессора Intel 8086 Блок-схема

- 14. Блок-схема микропроцессора Intel 8086

- 15. Процессор Intel 8086 Сигнал BHE в комбинации

- 16. Конвейер процессора Intel 8086 В процессорах применена

- 17. Очередь у процессора 8088 сокращена до

- 18. Регистры процессора Intel 8086 Процессор имеет 14-регистров

- 19. Регистры процессора Intel 8086 (2)

- 20. Регистры процессора Intel 8086 Если требуется использовать

- 21. Регистры процессора Intel 8086 В ряде

- 22. Регистры процессора Intel 8086 Регистр флагов

- 23. Регистры процессора Intel 8086 IF (Interrupt Flag)

- 24. Адресация памяти и ввода/вывода Процессор предусматривает

- 25. Формирование физического адреса Физический адрес памяти, поступающий

- 26. Ближний и дальний адрес Таким образом, при

- 27. Порядок L, H Все пространство памяти разбивается

- 28. Сегментация Сегментация памяти, которую использовали разработчики

- 29. Сегментация Каждая выполняющаяся программа для процессора

- 30. Сегментация Сегмент кода (Code Segment) – массив

- 31. Сегментация Реальный адрес требуемой ячейки памяти определяется

- 32. Сегментация Например, в регистре SS хранится номер

- 33. Адресация устройств ввода-вывода Пространство ввода/вывода (Input/Output

- 34. Система команд Набор команд 8086/88 включает следующие

- 35. Прерывания Архитектура процессоров Intel 8086 предусматривает

- 36. Внутренние прерывания или исключения –

- 37. Программные прерывания вызываются командой INT xx и

- 38. Особенности обмена по шине Цикл обмена

- 39. Функционирование модуля интерфейса шины Тактовый генератор на

- 40. Функционирование модуля интерфейса шины Микросхема 8284A

- 41. Математический сопроцессор 8087 Сопроцессор 8087,

- 42. Процессор 8088 Для процессора Intel 8086

- 43. Процессор 8088 Некоторые компании (в частности,

- 44. Процессоры 80186/80188 Процессоры i80186/80188 и их

- 45. Процессоры 80186/80188 (2) Встроенная периферия этих процессоров

- 46. Общие сведения о процессоре 80286 Процессор

- 47. Процессор может работать в двух

- 48. Переключение в защищённый режим осуществляется

- 49. Совместно с процессором 80286 предусмотрена

- 50. Регистры процессора 80286 Назначение внутренних

- 51. Регистр MSW управляет режимом процессора.

- 52. Организация памяти процессора 80286 Как

- 53. При вычислении физического адреса возможно возникновение

- 54. В защищённом режиме работают все режимы

- 55. Прерывания процессора 80286 Как и процессор

- 56. Каждому номеру прерывания соответствует свой элемент

- 57. Система команд процессора 80286 Система

- 58. Интерфейс процессора 80286 Процессоры

- 59. Функционирование процессора 80286 Основными компонентами системы

- 60. На адресную шину, состоящую из

- 61. Микропроцессор использует шинный контроллер для формирования

- 62. Чтение процессором слов из оперативной памяти

- 63. В начале 1987 г. на базе МП

- 64. Был введен новый «виртуальный режим» 8086 для

- 65. Процессор Intel 386 был первым архитектуры IA-32,

- 66. Было разработано несколько типов персональных компьютеров с

- 67. Следующим шагом в разработке компьютеров явилось использование

- 68. ЭВМ на базе процессора i486 появились в

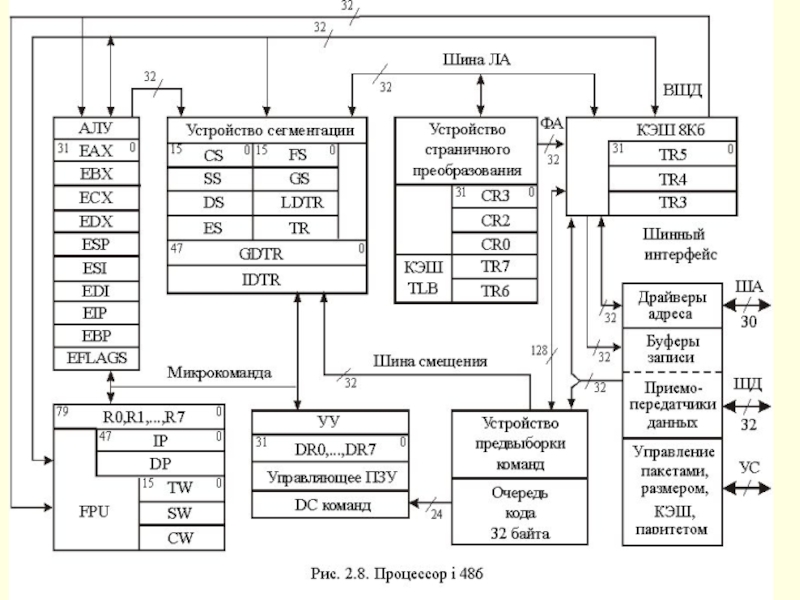

- 69. Схема процессора i486 представлена на рис. Он

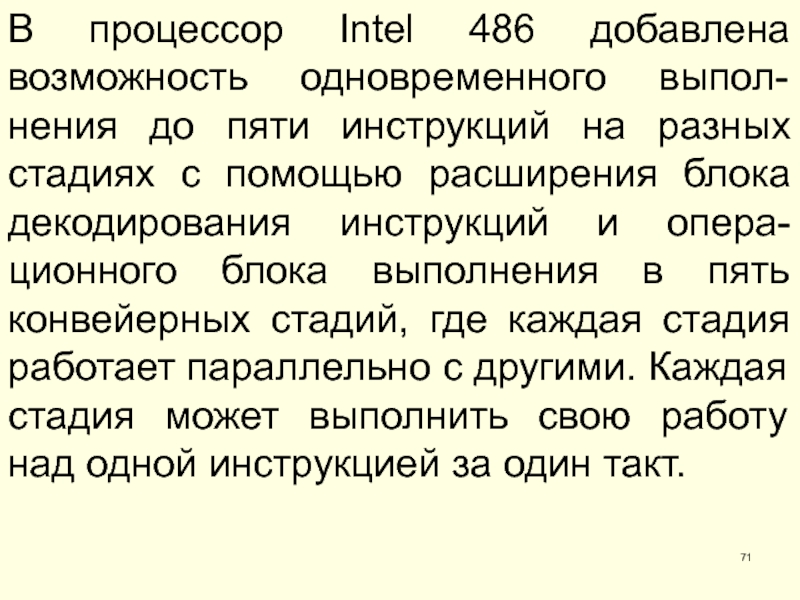

- 71. В процессор Intel 486 добавлена возможность одновременного

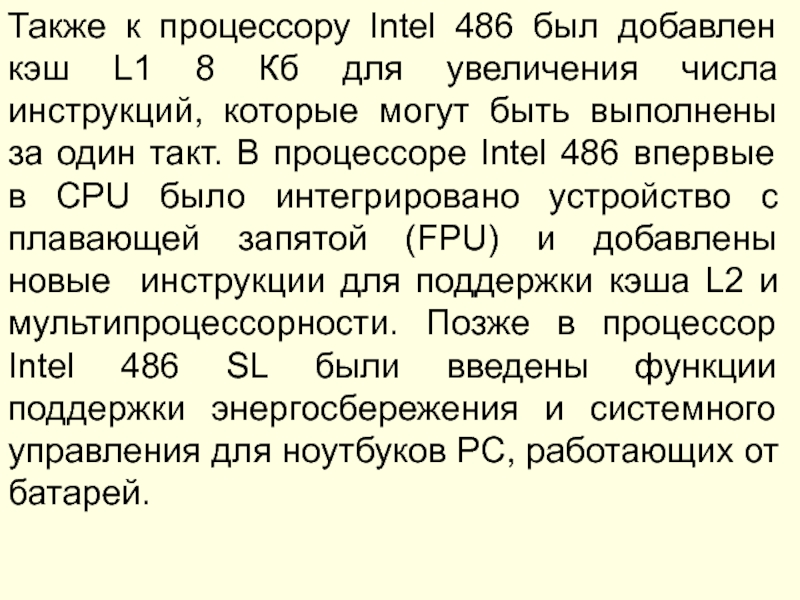

- 72. Также к процессору Intel 486 был

Слайд 2

Конвейер процессора Intel 8086.

Микропроцессор Intel 386 с архитектурой IA-32.

Процессор Intel 486-

CPU с плаваю-щей запятой (FPU).

Слайд 3

История процессоров фирмы Intel началась в 1971 году, когда был выпущен

первый микропроцессор – Intel 4004.

Разрядность данных 4 бита.

Способность адресовать 640 байт памяти.

Тактовая частота 108 кГц.

Производительность 0,06 MIPS.

2300 транзисторов.

Технология с разрешением 10 мкм.

Разрядность данных 4 бита.

Способность адресовать 640 байт памяти.

Тактовая частота 108 кГц.

Производительность 0,06 MIPS.

2300 транзисторов.

Технология с разрешением 10 мкм.

Слайд 5

Процессор Intel 8080

В 1974 году появился 8-разрядный процессор Intel 8080, ставший

весьма популярным устройством.

Процессор Intel 8080 был изготовлен по 10-микронной технологии, содержал 6000 транзисторов, имел частоту ядра целых 2 МГц, 16-битную адресную шину (у 8008 шина адреса была14-разрядной) и 8-битную шину данных.

Он был совместим с 8008 по набору команд. Чип 8080 требовал питания в +5 В, –5 В и +12 В.

Процессор Intel 8080 был изготовлен по 10-микронной технологии, содержал 6000 транзисторов, имел частоту ядра целых 2 МГц, 16-битную адресную шину (у 8008 шина адреса была14-разрядной) и 8-битную шину данных.

Он был совместим с 8008 по набору команд. Чип 8080 требовал питания в +5 В, –5 В и +12 В.

Слайд 6

На базе микропроцессора Intel 8080 компания MITS (Micro Instrumentation and Telemetry

Systems) создала в 1974 году первый в мире общедоступный персональ-ный компьютер Altair 8800.

На базе процессора Intel 8080 было построено множе-ство различных терминалов и контроллеров.

В нашей эхом Intel 8080 стали процессоры 580ИК80 и КР580ВМ80, на базе которых в начале и середине 80-х годов строилось много «самодельных» ПК.

На базе процессора Intel 8080 было построено множе-ство различных терминалов и контроллеров.

В нашей эхом Intel 8080 стали процессоры 580ИК80 и КР580ВМ80, на базе которых в начале и середине 80-х годов строилось много «самодельных» ПК.

Слайд 7

Процессор Intel 8085

Следующим этапом стал процессор Intel 8085 (5 Мгц, 0,37

MIPS, 6500 транзисторов, 3-мкм технология).

Он сохранил популярную регистровую архитектуру 8080 и программную совместимость, но в него добавился порт последовательного интерфейса, упразднили специальные ИС поддержки (тактового генератора и системного контроллера) и несколько изменили внешний интерфейс.

Главным подарком разработчикам аппаратуры стало одно питающее напряжение +5 В. Вариацию на тему 8080 и 8085 представляет процессор Z80 фирмы Zilog.

Сохранив программную совместимость с 8080, в него ввели дополнительные регистры, что позволило существенно повысить производительность. Результат оказался впечатляющим –популярные компьютеры Sinclair, построенные на Z80, демонстрировали на играх графику, не уступающему PC на16-разрядном процессоре Intel 80286.

Он сохранил популярную регистровую архитектуру 8080 и программную совместимость, но в него добавился порт последовательного интерфейса, упразднили специальные ИС поддержки (тактового генератора и системного контроллера) и несколько изменили внешний интерфейс.

Главным подарком разработчикам аппаратуры стало одно питающее напряжение +5 В. Вариацию на тему 8080 и 8085 представляет процессор Z80 фирмы Zilog.

Сохранив программную совместимость с 8080, в него ввели дополнительные регистры, что позволило существенно повысить производительность. Результат оказался впечатляющим –популярные компьютеры Sinclair, построенные на Z80, демонстрировали на играх графику, не уступающему PC на16-разрядном процессоре Intel 80286.

Слайд 8

Процессор Intel 8086

Первый 16-разрядный процессор Intel 8086 фирма Intel выпустила

в 1978 году.

Частота 5 МГц;

Производительность 0,33 MIPS, но инструкции уже с 16-битными операндами (позже появились процессоры 8 и 10 МГц).

Технология 3 мкм, 29 тыс. транзисторов.

Адресуемая память 1 Мб.

Регистровая архитектура и система команд существенно отличалась от 8080, но естественно прослеживаются общие идеи. Через год появился 8088 – тот же процессор, но с 8-битной шиной данных. С него началась история IBM PC, наложившая свой отпечаток на дальнейшее развитие этой линии процессоров Intel.

Массовое распространение и открытость архитектуры PC привили к лавинообразному появлению программного обеспечения, разрабатываемого крупными, средними и мелкими фирмами и энтузиастами-одиночками.

Частота 5 МГц;

Производительность 0,33 MIPS, но инструкции уже с 16-битными операндами (позже появились процессоры 8 и 10 МГц).

Технология 3 мкм, 29 тыс. транзисторов.

Адресуемая память 1 Мб.

Регистровая архитектура и система команд существенно отличалась от 8080, но естественно прослеживаются общие идеи. Через год появился 8088 – тот же процессор, но с 8-битной шиной данных. С него началась история IBM PC, наложившая свой отпечаток на дальнейшее развитие этой линии процессоров Intel.

Массовое распространение и открытость архитектуры PC привили к лавинообразному появлению программного обеспечения, разрабатываемого крупными, средними и мелкими фирмами и энтузиастами-одиночками.

Слайд 9

Технический прогресс требовал (и сейчас требует) развития процессоров, но груз программного

обес-печения PC , которое должно работать и на более новых процес-сорах, в свою очередь требовал обратной программной совместимости. Таким образом, все ново-введения в архитектуре последующих процес-соров должны были пристраиваться к суще-ствующему ядру.

Слайд 10 Общие сведения о процессоре Intel 8086

Процессоры 8086, выпущенные фирмой

Intel в 1978 году, относятся к первому поколению 16-битных процессоров. Годом позже появилась его модификация 8088.

Оба эти процессора выполняют 8/86-битные логические и арифметические операции, включая умножение и деление, операции с строками и операции ввода-вывода.

Процессоры имеют 20-разрядную шину адреса, которая позволяет адресовать до 1 Мб памяти.

Шина данных у 8086 16-разрядная, у 8088 разрядность внешней шины данных сокращена до 8 бит. Это сокращение, сделанное с целью удешевления системы в целом, оборачивается некоторым снижением производительности: 8086 за счет большей разрядности шины работает примерно на 20-60% быстрее, чем 8088 с той же тактовой частотой.

Оба эти процессора выполняют 8/86-битные логические и арифметические операции, включая умножение и деление, операции с строками и операции ввода-вывода.

Процессоры имеют 20-разрядную шину адреса, которая позволяет адресовать до 1 Мб памяти.

Шина данных у 8086 16-разрядная, у 8088 разрядность внешней шины данных сокращена до 8 бит. Это сокращение, сделанное с целью удешевления системы в целом, оборачивается некоторым снижением производительности: 8086 за счет большей разрядности шины работает примерно на 20-60% быстрее, чем 8088 с той же тактовой частотой.

Слайд 11Общие сведения о процессоре Intel 8086

Функциональные различия этих процессоров, обусловлены разной

разрядностью шины, появляются только в способе подключения 8- и 16-разрядных внешних устройств.

От родоначальника – процессора 8086 – пошло общее обозначения семейства: х86.

Процессоры поддерживают аппаратные и программные прерывания и допускают разделяемое использование шины совместно с другими процессорами или контроллерами (например к, прямого доступа к памяти – DMA). Также предусмотрено использование математического сопроцессора 8087, существенно повышающего производительность вычислений.

От родоначальника – процессора 8086 – пошло общее обозначения семейства: х86.

Процессоры поддерживают аппаратные и программные прерывания и допускают разделяемое использование шины совместно с другими процессорами или контроллерами (например к, прямого доступа к памяти – DMA). Также предусмотрено использование математического сопроцессора 8087, существенно повышающего производительность вычислений.

Слайд 12Общие сведения о процессоре Intel 8086

Процессор имеет 14 регистров разрядностью 16

бит, операнды могут иметь 8 или 16 бит и представлять знаковые и беззнаковые и двоично-десятичные числа.

Система команд имеет 24 режима адресации операндов.

Среднее время выполнения команды занимает 12 тактов синхронизации, один цикл обмена на внешней шине занимает 2 такта (без тактов ожидания).

Тактовая частота процессора 8088, применяемого в первых РС, была 4,77 МГц, в последствии появились процессоры с частотой 8 и 10 МГц (применялись в Turbo XT).

Система команд имеет 24 режима адресации операндов.

Среднее время выполнения команды занимает 12 тактов синхронизации, один цикл обмена на внешней шине занимает 2 такта (без тактов ожидания).

Тактовая частота процессора 8088, применяемого в первых РС, была 4,77 МГц, в последствии появились процессоры с частотой 8 и 10 МГц (применялись в Turbo XT).

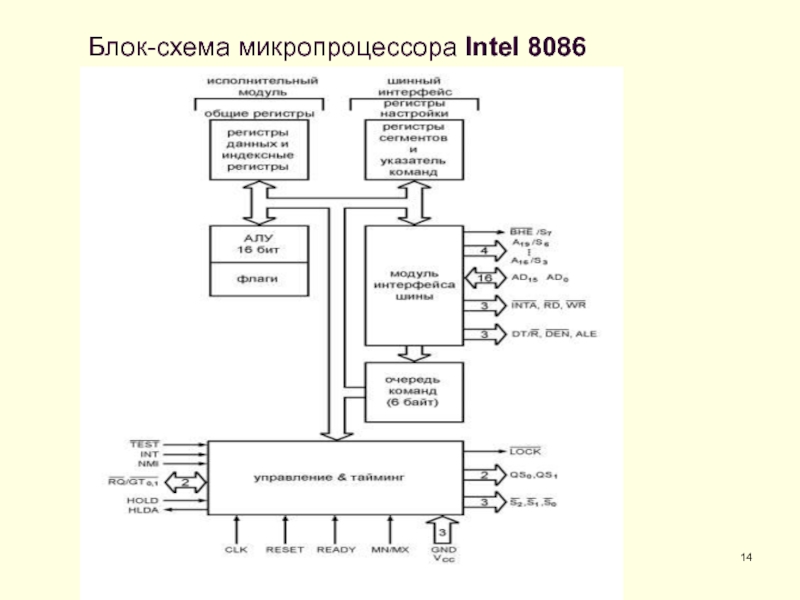

Слайд 134. Структура процессора Intel 8086

Блок-схема микропроцессора Intel 8086 представлена на

следующем слайде.

Процессор Intel 8086 имеет 16-битную шину данных (линии D0…D15) и 20-битную адресную шину (линии A0…A19).

Для сокращения количества выводов микросхемы процессора шины адреса и данных мультиплексированы.

Общая шина для адресов и данных была задействована еще в процессоре 8085. Хотя чип 8085 использовал 16 бит для пересылки адресов и 8 бит для пересылки данных, 40 выводов стандартного корпуса ему также не хватало. Поэтому по восьми линиям внешней шины чипа 8085 перебрасывались данные и часть адресных сигналов. Другие восемь линий шины полностью отдавались под вторую группу адресных сигналов. Поскольку процессор 8086 был значительно сложнее, чем 8085, то разработчики «реквизировали» все адресные линии для передачи данных или управляющих сигналов.

Процессор Intel 8086 имеет 16-битную шину данных (линии D0…D15) и 20-битную адресную шину (линии A0…A19).

Для сокращения количества выводов микросхемы процессора шины адреса и данных мультиплексированы.

Общая шина для адресов и данных была задействована еще в процессоре 8085. Хотя чип 8085 использовал 16 бит для пересылки адресов и 8 бит для пересылки данных, 40 выводов стандартного корпуса ему также не хватало. Поэтому по восьми линиям внешней шины чипа 8085 перебрасывались данные и часть адресных сигналов. Другие восемь линий шины полностью отдавались под вторую группу адресных сигналов. Поскольку процессор 8086 был значительно сложнее, чем 8085, то разработчики «реквизировали» все адресные линии для передачи данных или управляющих сигналов.

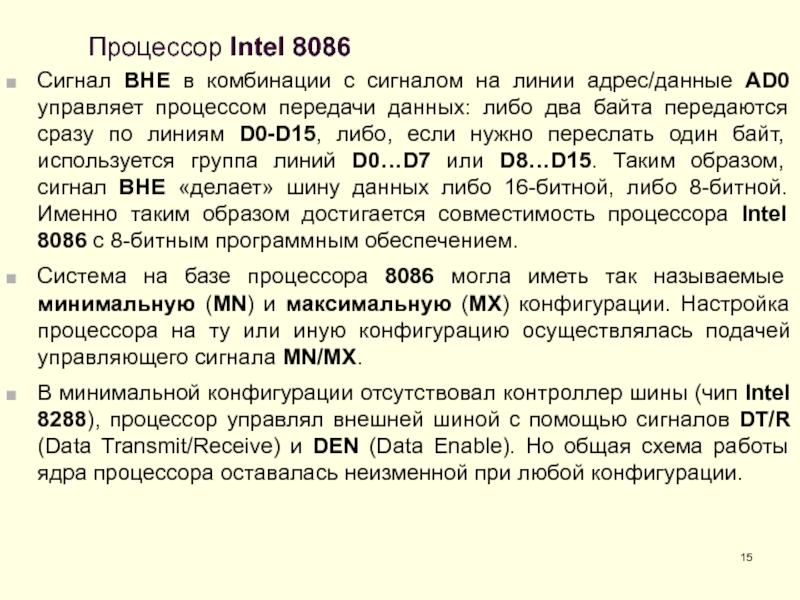

Слайд 15Процессор Intel 8086

Сигнал BHE в комбинации с сигналом на линии адрес/данные

AD0 управляет процессом передачи данных: либо два байта передаются сразу по линиям D0-D15, либо, если нужно переслать один байт, используется группа линий D0…D7 или D8…D15. Таким образом, сигнал BHE «делает» шину данных либо 16-битной, либо 8-битной. Именно таким образом достигается совместимость процессора Intel 8086 с 8-битным программным обеспечением.

Система на базе процессора 8086 могла иметь так называемые минимальную (MN) и максимальную (MX) конфигурации. Настройка процессора на ту или иную конфигурацию осуществлялась подачей управляющего сигнала MN/MX.

В минимальной конфигурации отсутствовал контроллер шины (чип Intel 8288), процессор управлял внешней шиной с помощью сигналов DT/R (Data Transmit/Receive) и DEN (Data Enable). Но общая схема работы ядра процессора оставалась неизменной при любой конфигурации.

Система на базе процессора 8086 могла иметь так называемые минимальную (MN) и максимальную (MX) конфигурации. Настройка процессора на ту или иную конфигурацию осуществлялась подачей управляющего сигнала MN/MX.

В минимальной конфигурации отсутствовал контроллер шины (чип Intel 8288), процессор управлял внешней шиной с помощью сигналов DT/R (Data Transmit/Receive) и DEN (Data Enable). Но общая схема работы ядра процессора оставалась неизменной при любой конфигурации.

Слайд 16Конвейер процессора Intel 8086

В процессорах применена конвейерная архитектура, позволяющая выполнить выборку

кодов инструкций из памяти их декодирование во время выполнения внутренних операций.

Конвейер повышает производительность процессора за счет сокращения времени простоя его операционных узлов.

В момент выполнения внутренних операций, одновременно с этим производится выборка кодов инструкций из памяти, их декодирование и постановка в очередь.

Конвейер процессора 8086 имеет 6-байтную внутреннюю очередь инструкций. Блок предварительной выборки при наличии 2 свободных байт в очереди старается ее заполнить в то время, когда внешняя шина процессора не занята операциями обмена.

Конвейер повышает производительность процессора за счет сокращения времени простоя его операционных узлов.

В момент выполнения внутренних операций, одновременно с этим производится выборка кодов инструкций из памяти, их декодирование и постановка в очередь.

Конвейер процессора 8086 имеет 6-байтную внутреннюю очередь инструкций. Блок предварительной выборки при наличии 2 свободных байт в очереди старается ее заполнить в то время, когда внешняя шина процессора не занята операциями обмена.

Слайд 17

Очередь у процессора 8088 сокращена до 4 байт, а предварительная выборка

осуществляется уже при наличии одного свободного байта. Это отличия оптимизируют конвейер с учетом разрядности шины данных.

Очередь обнуляется при выполнении любой команды передачи управления, даже при переходе на следующий адрес. Этим свойством часто пользуются при программировании управления устройствами ввода-вывода, требующими задержки между соседними операциями обмена.

Среднее время выполнения команды занимает 12 тактов синхронизации, один цикл обмена на внешней шине длится 4 такта (без тактов ожидания).

Очередь обнуляется при выполнении любой команды передачи управления, даже при переходе на следующий адрес. Этим свойством часто пользуются при программировании управления устройствами ввода-вывода, требующими задержки между соседними операциями обмена.

Среднее время выполнения команды занимает 12 тактов синхронизации, один цикл обмена на внешней шине длится 4 такта (без тактов ожидания).

Слайд 18Регистры процессора Intel 8086

Процессор имеет 14-регистров разрядностью 16 бит, объединенных в

несколько групп.

Основа набора – регистры общего назначения:

AX (аккумулятор),

BX (база),

CX (счетчик) и

DX (данные).

Размерность каждого из них – 16 бит, но для совместимости с программным обеспечением процессоров 8080 и 8085 к регистрам общего назначения программа могла обращаться и как к 8-битным. Для этого каждый регистр был разделен на две части: старший байт (High) и младший (Low).

Если к регистру необходимо обратиться к регистру как к 16-разрядному, то после имени регистра (A, B, C или D) ставится символ X (AX, BX, CX, DX).

Основа набора – регистры общего назначения:

AX (аккумулятор),

BX (база),

CX (счетчик) и

DX (данные).

Размерность каждого из них – 16 бит, но для совместимости с программным обеспечением процессоров 8080 и 8085 к регистрам общего назначения программа могла обращаться и как к 8-битным. Для этого каждый регистр был разделен на две части: старший байт (High) и младший (Low).

Если к регистру необходимо обратиться к регистру как к 16-разрядному, то после имени регистра (A, B, C или D) ставится символ X (AX, BX, CX, DX).

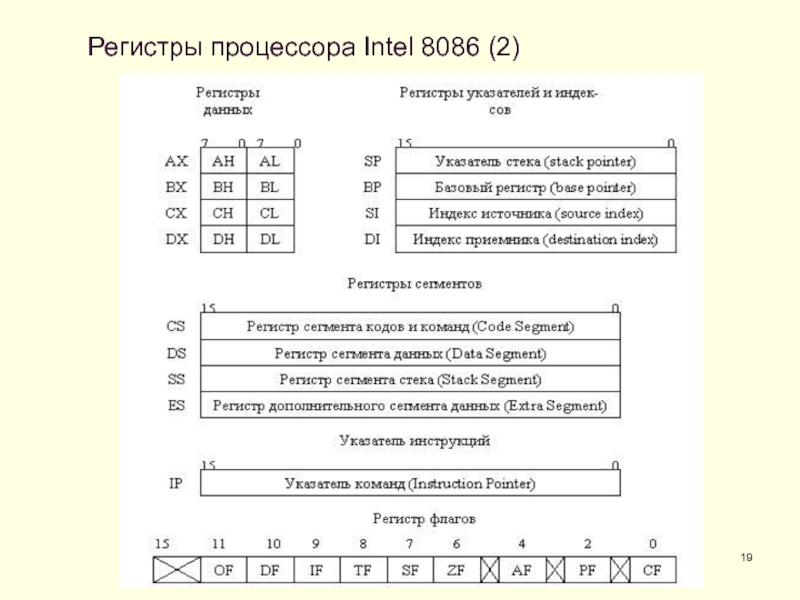

Слайд 20Регистры процессора Intel 8086

Если требуется использовать регистры общего назначения как 8-битные,

то к имени регистра прибавляется литера H или L в зависимости от того, к какому байту регистра (старшему или младшему) нужно обратиться. Это позволяет легко адаптировать старое 8-битное ПО, поскольку литеры A, B, C и D (но без второй буквы) в качестве имен регистров применялись еще в процессоре 8085.

Регистры данных или регистры общего назначения AX, BX, CX, DX состоят из двух восьмибайтных половинок с именами AH, BH, CH, DH (старшие байты – High) и AL, BL, CL, DL (младшие байты - Low). Таким образом, используя регистры данных можно оперировать как 8-, так 16-разрядными данными.

16-разрядные регистры-указатели сегментов могут модифицироваться только командами их непосредственной загрузки. Использование сегментных регистров определяется типом обращения к памяти.

Регистры данных или регистры общего назначения AX, BX, CX, DX состоят из двух восьмибайтных половинок с именами AH, BH, CH, DH (старшие байты – High) и AL, BL, CL, DL (младшие байты - Low). Таким образом, используя регистры данных можно оперировать как 8-, так 16-разрядными данными.

16-разрядные регистры-указатели сегментов могут модифицироваться только командами их непосредственной загрузки. Использование сегментных регистров определяется типом обращения к памяти.

Слайд 21Регистры процессора Intel 8086

В ряде команд принято использовать те или

иные регистры. Например:

АХ – умножение, деление, ввод и вывод слова;

AL – умножение. деление, ввод и вывод байта, десятичная арифметика;

AH – умножение и деление байта;

CX – счетчик циклов и указатель длины строковых операций;

DX – умножение и деление слова, ввод и вывод с косвенной адресацией;

SP – операции со стеком;

SI, DI – строковые операции.

АХ – умножение, деление, ввод и вывод слова;

AL – умножение. деление, ввод и вывод байта, десятичная арифметика;

AH – умножение и деление байта;

CX – счетчик циклов и указатель длины строковых операций;

DX – умножение и деление слова, ввод и вывод с косвенной адресацией;

SP – операции со стеком;

SI, DI – строковые операции.

Слайд 22Регистры процессора Intel 8086

Регистр флагов FLAGS хранит признаки результатов выполнения

арифметических и логических операций, а также управляющие биты:

CF (Carry Flag) – флаг переноса (заёма) старшего бита в арифметических операциях;

PF (Parity Flag) – флаг паритета, устанавливается при чётном количестве единиц результата;

AF (Auxiliary Flag) – флаг дополнительного переноса (заёма) в операциях с двоичной арифметикой;

ZF (Zero Flag) – флаг нулевого результата;

SF (Sign Flag) – флаг знака. В установленном состоянии свидетельствует об отрицательном значении результата;

TF (Trap Flag) – флаг трассировки (пошагового режима). При его установке после выполнения каждой команды вызывается внутреннее прерывание INT 1.

CF (Carry Flag) – флаг переноса (заёма) старшего бита в арифметических операциях;

PF (Parity Flag) – флаг паритета, устанавливается при чётном количестве единиц результата;

AF (Auxiliary Flag) – флаг дополнительного переноса (заёма) в операциях с двоичной арифметикой;

ZF (Zero Flag) – флаг нулевого результата;

SF (Sign Flag) – флаг знака. В установленном состоянии свидетельствует об отрицательном значении результата;

TF (Trap Flag) – флаг трассировки (пошагового режима). При его установке после выполнения каждой команды вызывается внутреннее прерывание INT 1.

Слайд 23Регистры процессора Intel 8086

IF (Interrupt Flag) – флаг управления прерываниями. При

единичном значении разрешается выполнение маскируемых аппаратных прерываний.

DF (Direction Flag) – флаг управления направлениями в строковых операциях. При единичном значении индексные регистры, участвующие в строковых операциях, автоматически декрементируются на указанное количество байт операнда, при нулевом – инкрементируются.

OF (Overflow Flag) – флаг переполнения. Устанавливается, если результат арифметической операции не умещается в операнде назначения.

DF (Direction Flag) – флаг управления направлениями в строковых операциях. При единичном значении индексные регистры, участвующие в строковых операциях, автоматически декрементируются на указанное количество байт операнда, при нулевом – инкрементируются.

OF (Overflow Flag) – флаг переполнения. Устанавливается, если результат арифметической операции не умещается в операнде назначения.

Слайд 24 Адресация памяти и ввода/вывода

Процессор предусматривает разделение пространств памяти и ввода/вывода.

Пространство

памяти (Memory Space) предназначено для хранения кодов инструкций и данных, для доступа к которым имеется богатый выбор способов адресации (24 режима).

Память для процессоров 8086/8088 представляется в виде линейной последовательности байт. Для обращения к памяти процессор (совместно со внешней схемой) формирует шинные сигналы MEMWR# (Memory Write) и MEMRD# (Memory Read) для операций записи и чтения соответственно.

20 разрядов шины адреса обеспечивают охват адресного пространства размером 1 Мб.

Логически память разбивается на сегменты размером 64 Кб.

Память для процессоров 8086/8088 представляется в виде линейной последовательности байт. Для обращения к памяти процессор (совместно со внешней схемой) формирует шинные сигналы MEMWR# (Memory Write) и MEMRD# (Memory Read) для операций записи и чтения соответственно.

20 разрядов шины адреса обеспечивают охват адресного пространства размером 1 Мб.

Логически память разбивается на сегменты размером 64 Кб.

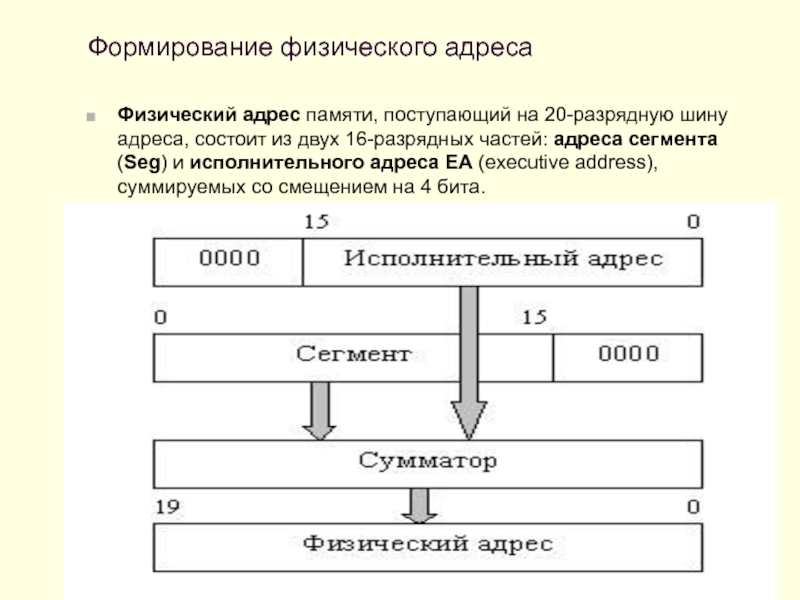

Слайд 25Формирование физического адреса

Физический адрес памяти, поступающий на 20-разрядную шину адреса, состоит

из двух 16-разрядных частей: адреса сегмента (Seg) и исполнительного адреса EA (executive address), суммируемых со смещением на 4 бита.

Слайд 26Ближний и дальний адрес

Таким образом, при любом значении 16-битного исполнительного адреса,

физический адрес не перекроет границу 64 Кб сегмента, на начало которого указывает текущий сегментный указатель.

С одной стороны, это свойство обеспечивает некоторую защиту сегментов друг от друга, а с другой – сегментация памяти является существенным неудобством при написании больших программных модулей.

С сегментацией связаны понятия ближнего и дальнего адреса.

При ближнем (Near) или внутрисегментном обращении указывается только смещение, а адрес сегмента определяется текущим содержимым соответствующего регистра сегмента.

При дальнем (Far) или межсегментном обращении указывается полный адрес, содержащий 16-битное значение сегмента (загружаемое в соответствующий сегментный регистр) и 16-битное смещение.

С сегментацией связаны понятия ближнего и дальнего адреса.

При ближнем (Near) или внутрисегментном обращении указывается только смещение, а адрес сегмента определяется текущим содержимым соответствующего регистра сегмента.

При дальнем (Far) или межсегментном обращении указывается полный адрес, содержащий 16-битное значение сегмента (загружаемое в соответствующий сегментный регистр) и 16-битное смещение.

Слайд 27Порядок L, H

Все пространство памяти разбивается на параграфы – области из

16 смежных байт, начиная с нулевого адреса. Очевидно, что любой сегмент может начинаться только с границы параграфа

(т.к. четыре младших бита адреса сегмента нулевые).

Процессор может обращаться к одному байту памяти, так и слову, или двойному слову.

При размещении слова в памяти с адресом, соответствующим адресу слова, содержит его младшую часть (Low), следующий байт содержит старшую часть (High). Слово может размещаться в памяти как по чётному (Even), так и по не нечётному (Odd) адресу. Двойное слово обычно используется для хранения полного адреса, и в нем располагается сначала слово смещения (в порядке L, H), а затем сегмента (в том же порядке).

Сегментация памяти в порядке L, H являются характерной чертой процессоров Intel.

Процессор может обращаться к одному байту памяти, так и слову, или двойному слову.

При размещении слова в памяти с адресом, соответствующим адресу слова, содержит его младшую часть (Low), следующий байт содержит старшую часть (High). Слово может размещаться в памяти как по чётному (Even), так и по не нечётному (Odd) адресу. Двойное слово обычно используется для хранения полного адреса, и в нем располагается сначала слово смещения (в порядке L, H), а затем сегмента (в том же порядке).

Сегментация памяти в порядке L, H являются характерной чертой процессоров Intel.

Слайд 28Сегментация

Сегментация памяти, которую использовали разработчики Intel, казавшаяся на тот момент

изящной, позднее подвергалась страшным проклятиям. Основной смысл введения сегментации заключается в том, что необходимо было добиться частичной совместимости нового чипа с ПО для 8-битных процессоров (8080, 8085 и Z80). Именно поэтому разработчики не стали отказываться от 16-битной схемы адресации памяти (в предыдущих чипах для хранения адресов памяти применялись 16-битные регистры). Однако 16-битный адрес позволяет использовать максимум 64 кбайт памяти. Такой объём уже не мог удовлетворить серьёзного пользователя ПК.

Количество сегментов в оперативной памяти ограничивается размерностью регистров (16 бит) и не может превышать 65 535; каждый сегмент отстоит от другого на 16 байт.

Количество сегментов в оперативной памяти ограничивается размерностью регистров (16 бит) и не может превышать 65 535; каждый сегмент отстоит от другого на 16 байт.

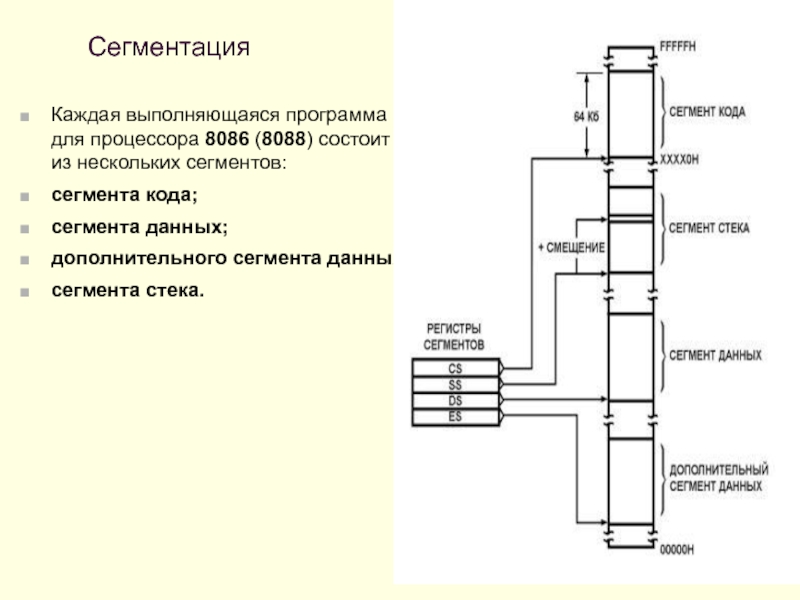

Слайд 29Сегментация

Каждая выполняющаяся программа для процессора 8086 (8088) состоит из нескольких

сегментов:

сегмента кода;

сегмента данных;

дополнительного сегмента данных;

сегмента стека.

сегмента кода;

сегмента данных;

дополнительного сегмента данных;

сегмента стека.

Слайд 30Сегментация

Сегмент кода (Code Segment) – массив команд, предназначенных для выполнения.

Сегмент данных

(Data Segment) содержит информацию, подлежащую обработке.

Если одного сегмента данных недостаточно, программист может задействовать дополнительный сегмент данных (Extra Segment).

Практически каждая программа включает в себя сегмент стека (Stack Segment) для временного хранения данных и для обмена параметрами между подпрограммами.

Для хранения номеров этих сегментов в процессоре 8086 есть кодовые регистры: CS, DS, ES и SS.

Каждый из сегментных регистров (их имена являются аббревиатурами названий соответствующих сегментов) должен хранить ссылку только на сегмент своего типа.

Например, в регистре SS может содержаться только номер стекового сегмента.

Если одного сегмента данных недостаточно, программист может задействовать дополнительный сегмент данных (Extra Segment).

Практически каждая программа включает в себя сегмент стека (Stack Segment) для временного хранения данных и для обмена параметрами между подпрограммами.

Для хранения номеров этих сегментов в процессоре 8086 есть кодовые регистры: CS, DS, ES и SS.

Каждый из сегментных регистров (их имена являются аббревиатурами названий соответствующих сегментов) должен хранить ссылку только на сегмент своего типа.

Например, в регистре SS может содержаться только номер стекового сегмента.

Слайд 31Сегментация

Реальный адрес требуемой ячейки памяти определяется по схеме

СЕГМЕНТ:СМЕЩЕНИЕ

на основании значений в

двух регистрах: регистре сегмента и регистрах-указателях: справа к значению адреса сегмента (СЕГМЕНТ) приписывается четыре нуля, и к полученному числу прибавляется значение смещения (СМЕЩЕНИЕ).

Смещение внутри сегмента выбирается из регистров-указателей SP, BP, SI, DI или регистра IP (указателя команд – Instruction Pointer).

Смещение внутри сегмента выбирается из регистров-указателей SP, BP, SI, DI или регистра IP (указателя команд – Instruction Pointer).

Слайд 32Сегментация

Например, в регистре SS хранится номер сегмента 0000 0011 0000 1111,

а в регистре SP – номер ячейки внутри этого сегмента, скажем, 0000 0000 0000 0101.

Тогда реальный адрес ячейки в общем массиве памяти вычисляется так:

сначала справа к значению SS приписывается четыре нуля (все биты сдвигаются влево на четыре позиции), в результате имеем 0000 0011 0000 11111 0000;

затем к полученному числу прибавляется значение из SP; получается 20-битный адрес 0000 0011 0000 1111 0101, или 030F5 в шестнадцатеричном виде.

Этот адрес процессор использует для доступа к нужной ячейке памяти.

Тогда реальный адрес ячейки в общем массиве памяти вычисляется так:

сначала справа к значению SS приписывается четыре нуля (все биты сдвигаются влево на четыре позиции), в результате имеем 0000 0011 0000 11111 0000;

затем к полученному числу прибавляется значение из SP; получается 20-битный адрес 0000 0011 0000 1111 0101, или 030F5 в шестнадцатеричном виде.

Этот адрес процессор использует для доступа к нужной ячейке памяти.

Слайд 33 Адресация устройств ввода-вывода

Пространство ввода/вывода (Input/Output Space) предназначено для обращения к

регистрам внешних (по отношению к процессору) электронных схем.

Его размер ограничен 64 Кб, а способов адресации всего два.

Для обращения к устройствам ввода/вывода процессор имеет отдельные инструкции IN и OUT, результатом выполнения которых является формирование шинных сигналов IORD# (Input/Output Read) и IOWR# (Input/Output Write) для чтения или записи одного или двух байт.

Данные при чтении могут помещаться только в регистры AL или AX и выводятся из тех же регистров.

Адрес устройства задаётся либо в команде, либо берётся из регистра DX.

Его размер ограничен 64 Кб, а способов адресации всего два.

Для обращения к устройствам ввода/вывода процессор имеет отдельные инструкции IN и OUT, результатом выполнения которых является формирование шинных сигналов IORD# (Input/Output Read) и IOWR# (Input/Output Write) для чтения или записи одного или двух байт.

Данные при чтении могут помещаться только в регистры AL или AX и выводятся из тех же регистров.

Адрес устройства задаётся либо в команде, либо берётся из регистра DX.

Слайд 34Система команд

Набор команд 8086/88 включает следующие основные группы:

инструкции пересылки данных;

арифметические и

логические инструкции;

инструкции работы со строками;

инструкции передачи управления;

инструкции управления процессором.

Каждая команда имеет один или два байта инструкции, за которыми может следовать 1, 2 или 4 байты операнда.

Перед кодом инструкции возможно применение префиксов CS;, DS;, ES;, SS;, указывающих на использование заданных сегментных регистров вместо обычного, префикса REP, указывающего на необходимость повтора инструкции указанное в регистре СХ число раз, и префикса LOCK, блокирующего системную шину на время выполнения инструкции.

С позиции сегодняшнего дня можно считать, что система команд 16-разрядного процессора 8086/88 является подмножеством команд 32-разрядных процессоров 80х86.

инструкции работы со строками;

инструкции передачи управления;

инструкции управления процессором.

Каждая команда имеет один или два байта инструкции, за которыми может следовать 1, 2 или 4 байты операнда.

Перед кодом инструкции возможно применение префиксов CS;, DS;, ES;, SS;, указывающих на использование заданных сегментных регистров вместо обычного, префикса REP, указывающего на необходимость повтора инструкции указанное в регистре СХ число раз, и префикса LOCK, блокирующего системную шину на время выполнения инструкции.

С позиции сегодняшнего дня можно считать, что система команд 16-разрядного процессора 8086/88 является подмножеством команд 32-разрядных процессоров 80х86.

Слайд 35 Прерывания

Архитектура процессоров Intel 8086 предусматривает возможность прерываний – изменения последовательности

выполнения команд, предопределенной исполняемым программным кодом.

В случае возникновения прерывания процессор вызывает соответствующую процедуру (подпрограмму), по окончанию исполнения которой обычно возвращается к прерванному коду.

Процессор может выполнять прерывания 256 типов (номеров), каждом из которых соответствует свой вектор прерывания – двойное слово, содержащее дальний адрес (CS:IP) вызываемой процедуры.

По происхождению, прерывания делятся на внутренние (прерывания процессора) и аппаратные (вызываемые электрическими сигналами на соответствующих входах процессора).

В случае возникновения прерывания процессор вызывает соответствующую процедуру (подпрограмму), по окончанию исполнения которой обычно возвращается к прерванному коду.

Процессор может выполнять прерывания 256 типов (номеров), каждом из которых соответствует свой вектор прерывания – двойное слово, содержащее дальний адрес (CS:IP) вызываемой процедуры.

По происхождению, прерывания делятся на внутренние (прерывания процессора) и аппаратные (вызываемые электрическими сигналами на соответствующих входах процессора).

Слайд 36

Внутренние прерывания или исключения – вырабатываются процессором при особых условиях,

могущих возникнуть при исполнении текущей инструкции:

прерывание типа 0 вырабатывается в случае переполнения при операции деления на 0;

прерывание типа 1 вырабатывается после выполнения каждой команды при установленном флаге трассировки TF;

Прерывание типа 4 вырабатывается по команде INTO (Interrupt Overflow), если установлен флаг переполнения OF.

Аппаратные или внешние прерывания могут возникать асинхронно по отношению к выполняемой программе. Они подразделяются на маскируемые и немаскируемые.

Маскируемые – могут быть запрещены к исполнению на определённое время при помощи флага IF.

Немаскируемые прерывания – выполняются при любых условиях, независимо от флага IF.

прерывание типа 0 вырабатывается в случае переполнения при операции деления на 0;

прерывание типа 1 вырабатывается после выполнения каждой команды при установленном флаге трассировки TF;

Прерывание типа 4 вырабатывается по команде INTO (Interrupt Overflow), если установлен флаг переполнения OF.

Аппаратные или внешние прерывания могут возникать асинхронно по отношению к выполняемой программе. Они подразделяются на маскируемые и немаскируемые.

Маскируемые – могут быть запрещены к исполнению на определённое время при помощи флага IF.

Немаскируемые прерывания – выполняются при любых условиях, независимо от флага IF.

Слайд 37Программные прерывания вызываются командой INT xx и исполняются независимо от состояния

флага IF.

Программные прерывания позволяют легко и быстро вызывать часто используемые процедуры из любого сегмента без применения медленных дальних вызовов.

Кроме всего перечисленного, существуют ещё и программные прерывания (более корректное название – «программный вызов обработчика прерываний»).

Программные прерывания позволяют легко и быстро вызывать часто используемые процедуры из любого сегмента без применения медленных дальних вызовов.

Кроме всего перечисленного, существуют ещё и программные прерывания (более корректное название – «программный вызов обработчика прерываний»).

Слайд 38Особенности обмена по шине

Цикл обмена данными между процессором 8086 и

памятью состоит из пяти тактов: четырех рабочих (T1, T2, T3, T4) и одного такта ожидания (Twait).

На такте T1 передаётся адрес, а циклы T2, T3, Twait, T4 используются для обмена данными и передачи дополнительных управляющих сигналов S4…S0.

Сигналы S3…S4 посылаются одновременно с отправкой данных и несут информацию о типе сегмента, с которым происходит обмен данными.

Сигналы S2…S0 используются контроллером шины на системной плате (микросхема Intel 8288) для оповещения модулей памяти и портов ввода/вывода о начале операций по обмену данными:

001 – чтение из порта,

010 – запись в порт,

101 – чтение памяти,

110 – запись в память.

Узел процессора 8086, отвечавший за управление шиной адреса/данных, получил название «модуль интерфейса шины».

На такте T1 передаётся адрес, а циклы T2, T3, Twait, T4 используются для обмена данными и передачи дополнительных управляющих сигналов S4…S0.

Сигналы S3…S4 посылаются одновременно с отправкой данных и несут информацию о типе сегмента, с которым происходит обмен данными.

Сигналы S2…S0 используются контроллером шины на системной плате (микросхема Intel 8288) для оповещения модулей памяти и портов ввода/вывода о начале операций по обмену данными:

001 – чтение из порта,

010 – запись в порт,

101 – чтение памяти,

110 – запись в память.

Узел процессора 8086, отвечавший за управление шиной адреса/данных, получил название «модуль интерфейса шины».

Слайд 39Функционирование модуля интерфейса шины

Тактовый генератор на системной плате (микросхема Intel 8284A)

выдает первый импульс (сигнал T1), и блок управления (БУ) процессора посылает в модуль интерфейса шины некий адрес

Модуль интерфейса шины, который также получил импульс T1 и «знает», что на данном такте внешняя шина используется для передачи адреса, задействует линии с A0 по A19 для пересылки в память адреса.

С помощью сигнала ALE (Address Latch Enable) включается запрет на любое другое использование адресной шины на этом такте.

Затем микросхема 8284A вырабатывает следующий синхронизирующий импульс (процессор его воспринимает как сигнал о начале такта T2).

Модуль интерфейса шины путем посылки сигнала по линии BHE и AD0 настраивает шину (16-битная или 8-битная, а если 8-битная, то какая группа линий используется, старшие 8 бит или младшие 8 бит – D0:D7 или D8:D15). Одновременно модуль посылает сигнал RD или WR, исходя из того, какое действие с памятью хочет произвести процессор (прочитать или записать).

Модуль интерфейса шины, который также получил импульс T1 и «знает», что на данном такте внешняя шина используется для передачи адреса, задействует линии с A0 по A19 для пересылки в память адреса.

С помощью сигнала ALE (Address Latch Enable) включается запрет на любое другое использование адресной шины на этом такте.

Затем микросхема 8284A вырабатывает следующий синхронизирующий импульс (процессор его воспринимает как сигнал о начале такта T2).

Модуль интерфейса шины путем посылки сигнала по линии BHE и AD0 настраивает шину (16-битная или 8-битная, а если 8-битная, то какая группа линий используется, старшие 8 бит или младшие 8 бит – D0:D7 или D8:D15). Одновременно модуль посылает сигнал RD или WR, исходя из того, какое действие с памятью хочет произвести процессор (прочитать или записать).

Слайд 40Функционирование модуля интерфейса шины

Микросхема 8284A снова вырабатывает импульс (такт T3).

Если перед этим был послан сигнал WR (запись), то в оперативную память сразу же отправляются данные из какого-либо регистра общего назначения (в соответствии с настройками шины данных сигналом BHE: 8 бит или 16 бит).

Передача данных в память занимает целых три цикла, включая и цикл ожидания: T3, Twait и T4. Если же на втором такте был передан сигнал RD (чтение), то модуль интерфейса шины резервирует шину под прием данных и начинает приём данных в конце следующего цикла (Twait).

Если из памяти пришел код команды, то он отправляется в очередь команд, если данные, то они «уходят» в один из регистров общего назначения.

Передача данных в память занимает целых три цикла, включая и цикл ожидания: T3, Twait и T4. Если же на втором такте был передан сигнал RD (чтение), то модуль интерфейса шины резервирует шину под прием данных и начинает приём данных в конце следующего цикла (Twait).

Если из памяти пришел код команды, то он отправляется в очередь команд, если данные, то они «уходят» в один из регистров общего назначения.

Слайд 41 Математический сопроцессор 8087

Сопроцессор 8087, официально (фирмой Intel) называемый NPX

(Numeric Processor eXtension), предназначен для расширения вычислительных возможностей центрального процессора (CPU) 8086/8088, 80186/80188.

Применение сопроцессора 8087 к системе команд 8086 добавляет 68 мнемоник, включающих арифметические, тригонометрические, экспоненциальные и логарифмические.

Применение сопроцессора 8087 к системе команд 8086 добавляет 68 мнемоник, включающих арифметические, тригонометрические, экспоненциальные и логарифмические.

Слайд 42Процессор 8088

Для процессора Intel 8086 нужно было специально разрабатывать новую

системную плату с 16-битной шиной данных. А это неминуемо должно было привести к увеличению общей стоимости системы в целом и автоматическому ее выпадению из рыночного сегмента «16-битный персональный компьютер за 1500 долларов». Поэтому инженеры IBM для своего проекта 5150 (IBM PC) взяли за основу другую разработку Intel – чип 8088, появившийся в 1979 году.

Традиционным определением процессора Intel 8088 является следующая фраза: «Это процессор 8086 с 8-битной шиной данных». На такой характеристике настаивал в первую очередь маркетинговый отдел Intel. Но правильнее было бы назвать чип 8088 «процессором 8085 с набором команд x86 и регистрами Intel 8086».

Традиционным определением процессора Intel 8088 является следующая фраза: «Это процессор 8086 с 8-битной шиной данных». На такой характеристике настаивал в первую очередь маркетинговый отдел Intel. Но правильнее было бы назвать чип 8088 «процессором 8085 с набором команд x86 и регистрами Intel 8086».

Слайд 43 Процессор 8088

Некоторые компании (в частности, Godbout Electronics), выпуская клон 8088,

позиционировали его именно как решение из одной группы с чипом 8085 (их оригинальная документация так и называется – «CPU 8085/88 Technical Manual»).

Клон 8088 от компании Godbout Electronics имел даже синхронизацию, аналогичную 8085, и базовый четырёхтактный цикл (у оригинального 8088 от Intel базовый цикл равен пяти тактам). Для программистов, конечно, это особого значения не имело, поскольку и 8086, и 8088 располагали одним и тем же набором команд. Однако если быть совершенно беспристрастными, то оригинальный IBM PC нельзя назвать полноценной 16-битной машиной.

Клон 8088 от компании Godbout Electronics имел даже синхронизацию, аналогичную 8085, и базовый четырёхтактный цикл (у оригинального 8088 от Intel базовый цикл равен пяти тактам). Для программистов, конечно, это особого значения не имело, поскольку и 8086, и 8088 располагали одним и тем же набором команд. Однако если быть совершенно беспристрастными, то оригинальный IBM PC нельзя назвать полноценной 16-битной машиной.

Слайд 44Процессоры 80186/80188

Процессоры i80186/80188 и их модификации 80С186/80С188 не представляют нового

представления архитектуры: как и 8085/8088, они являются процессорами с 16-разрядной внутренней архитектурой и программно совместимыми с 8086.

Разрядность шины адреса – 20 бит, шины данных у 80186 – 16 бит, у 80188 – 8 бит.

Эти процессоры имеют встроенные периферийные контроллеры прерывания, прямого доступа к памяти, трёхканальный таймер и генератор синхронизации.

За счёт архитектурных улучшений сокращенно число тактов, требуемых для выполнения некоторых команд.

Процессоры 80С186/80С188 имеют средства управления энергопотреблением, есть их модификации со встроенными последовательными портами и контроллерами регенерации динамической памяти.

Разрядность шины адреса – 20 бит, шины данных у 80186 – 16 бит, у 80188 – 8 бит.

Эти процессоры имеют встроенные периферийные контроллеры прерывания, прямого доступа к памяти, трёхканальный таймер и генератор синхронизации.

За счёт архитектурных улучшений сокращенно число тактов, требуемых для выполнения некоторых команд.

Процессоры 80С186/80С188 имеют средства управления энергопотреблением, есть их модификации со встроенными последовательными портами и контроллерами регенерации динамической памяти.

Слайд 45Процессоры 80186/80188 (2)

Встроенная периферия этих процессоров имеет программный интерфейс, не совместимый

с IBM РС-спецификациями.

Эти процессоры используются во встраиваемых контроллерах и компьютерах, не требующих 100% IBM-совместимости (возможно обеспечение совместимости на уровне MS-DOS).

Эти процессоры используются во встраиваемых контроллерах и компьютерах, не требующих 100% IBM-совместимости (возможно обеспечение совместимости на уровне MS-DOS).

Слайд 46

Общие сведения о процессоре 80286

Процессор 80286, выпущенный в 1982 году,

представляет второе

поколение 16-разрядных

процессоров.

Процессор 80286 имеет специальные средства для работы в многопользова- тельских и многозадачных системах.

Наиболее существенным отличием от 8086/88 является механизм управления адресацией памяти, который обеспечивает четырёхуровневую систему защиты и поддержку виртуальной памяти.

Специальные средства предназначены для поддержки механизма переключения задач (Task switching).

Процессор имеет расширенную систему команд, которая кроме команд управления защитой включает все команды 8086 и несколько новых команд общего назначения.

Процессор 80286 имеет специальные средства для работы в многопользова- тельских и многозадачных системах.

Наиболее существенным отличием от 8086/88 является механизм управления адресацией памяти, который обеспечивает четырёхуровневую систему защиты и поддержку виртуальной памяти.

Специальные средства предназначены для поддержки механизма переключения задач (Task switching).

Процессор имеет расширенную систему команд, которая кроме команд управления защитой включает все команды 8086 и несколько новых команд общего назначения.

Слайд 47

Процессор может работать в двух режимах:

8086 Real Address Mode —

режим реальной адресации (или просто реальный режим — Real Mode), полностью совместимый с 8086. В этом режиме возможна адресация до 1 Мбайт физической памяти (на самом деле, за счет «удачной» ошибки, почти на 64 Кб больше).

Protected Virtual Address Mode — защищённый режим виртуальной адресации (или просто защищённый режим — Protected Mode). В этом режиме процессор позволяет адресовать до 16 Мб физической памяти, через которые при использовании механизма страничной адресации могут отображаться до 1 Гб виртуальной памяти каждой задачи. Система команд в этом режиме также включает набор команд 8086, расширенный для обеспечения аппаратной реализации функций супервизора многозадачной ОС и виртуальной памяти.

Protected Virtual Address Mode — защищённый режим виртуальной адресации (или просто защищённый режим — Protected Mode). В этом режиме процессор позволяет адресовать до 16 Мб физической памяти, через которые при использовании механизма страничной адресации могут отображаться до 1 Гб виртуальной памяти каждой задачи. Система команд в этом режиме также включает набор команд 8086, расширенный для обеспечения аппаратной реализации функций супервизора многозадачной ОС и виртуальной памяти.

Слайд 48

Переключение в защищённый режим осуществляется одной командой (с предварительно подготовленными таблицами

дескрипторов) достаточно быстро. Обратное переключение в реальный режим возможно только через аппаратный сброс процессора, что требует значительных затрат времени.

По составу и назначению в реальном режиме регистры 80286 в основном совпадают с регистрами 8086/88. Изменения касаются назначения разрядов регистра флагов и использования сегментных регистров в защищённом режиме.

Как и процессор 8086, процессор 80286 имеет 16-разрядную шину данных и очередь команд 6 байт.

За счёт совершенствования архитектуры сокращено время выполнения операций: процессор 80286 с тактовой частотой12,5 МГц работает более чем в 6 раз быстрее, чем 8086 с тактовой частотой 5 МГц.

По составу и назначению в реальном режиме регистры 80286 в основном совпадают с регистрами 8086/88. Изменения касаются назначения разрядов регистра флагов и использования сегментных регистров в защищённом режиме.

Как и процессор 8086, процессор 80286 имеет 16-разрядную шину данных и очередь команд 6 байт.

За счёт совершенствования архитектуры сокращено время выполнения операций: процессор 80286 с тактовой частотой12,5 МГц работает более чем в 6 раз быстрее, чем 8086 с тактовой частотой 5 МГц.

Слайд 49

Совместно с процессором 80286 предусмотрена возможность использования высокопроизво-дительного математического сопроцессора 80287,

программно совместимого с 8087.

Под управлением операционной системы MS DOS процессор 80286 обычно используют в реальном режиме работы.

Защищенный режим используют ОС типа XENIX, UNIX, OS/2, NetWare286 и оболочка MS Windows.

Хотя преимущества процессора 80286 в PC реализовались лишь частично (он в основном использовался как быстрый процессор 8086), именно с этим процессором связан настоящий «бум» на рынке PC.

Под управлением операционной системы MS DOS процессор 80286 обычно используют в реальном режиме работы.

Защищенный режим используют ОС типа XENIX, UNIX, OS/2, NetWare286 и оболочка MS Windows.

Хотя преимущества процессора 80286 в PC реализовались лишь частично (он в основном использовался как быстрый процессор 8086), именно с этим процессором связан настоящий «бум» на рынке PC.

Слайд 50

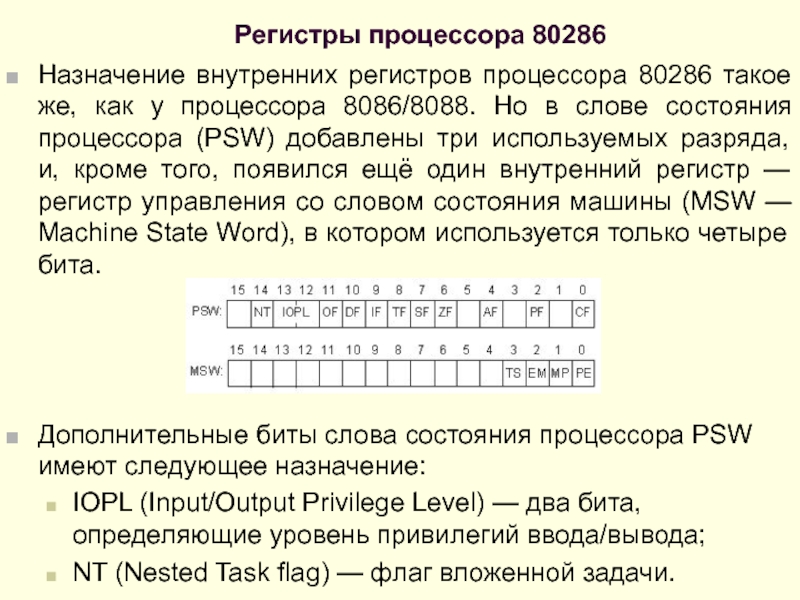

Регистры процессора 80286

Назначение внутренних регистров процессора 80286 такое же, как у

процессора 8086/8088. Но в слове состояния процессора (PSW) добавлены три используемых разряда, и, кроме того, появился ещё один внутренний регистр — регистр управления со словом состояния машины (MSW — Machine State Word), в котором используется только четыре бита.

Дополнительные биты слова состояния процессора PSW имеют следующее назначение:

IOPL (Input/Output Privilege Level) — два бита, определяющие уровень привилегий ввода/вывода;

NT (Nested Task flag) — флаг вложенной задачи.

Дополнительные биты слова состояния процессора PSW имеют следующее назначение:

IOPL (Input/Output Privilege Level) — два бита, определяющие уровень привилегий ввода/вывода;

NT (Nested Task flag) — флаг вложенной задачи.

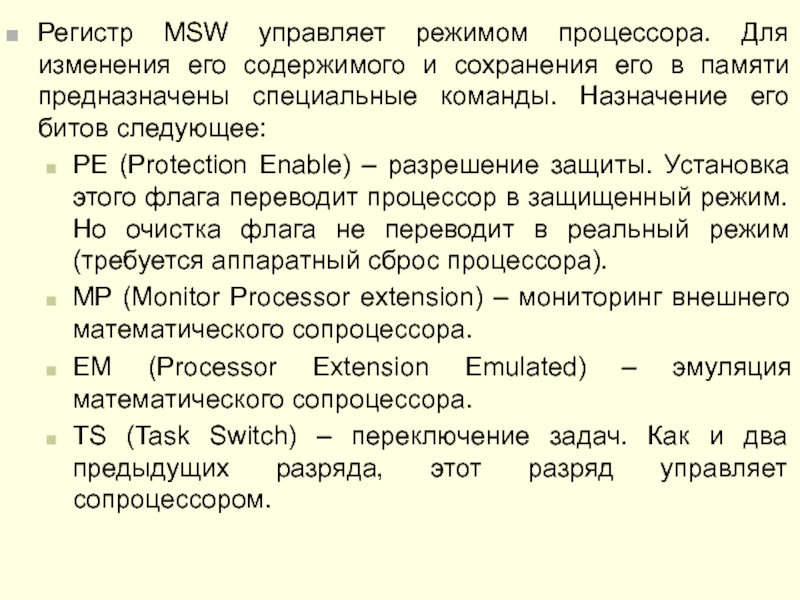

Слайд 51

Регистр MSW управляет режимом процессора. Для изменения его содержимого и сохранения

его в памяти предназначены специальные команды. Назначение его битов следующее:

PE (Protection Enable) – разрешение защиты. Установка этого флага переводит процессор в защищенный режим. Но очистка флага не переводит в реальный режим (требуется аппаратный сброс процессора).

MP (Monitor Processor extension) – мониторинг внешнего математического сопроцессора.

EM (Processor Extension Emulated) – эмуляция математического сопроцессора.

TS (Task Switch) – переключение задач. Как и два предыдущих разряда, этот разряд управляет сопроцессором.

PE (Protection Enable) – разрешение защиты. Установка этого флага переводит процессор в защищенный режим. Но очистка флага не переводит в реальный режим (требуется аппаратный сброс процессора).

MP (Monitor Processor extension) – мониторинг внешнего математического сопроцессора.

EM (Processor Extension Emulated) – эмуляция математического сопроцессора.

TS (Task Switch) – переключение задач. Как и два предыдущих разряда, этот разряд управляет сопроцессором.

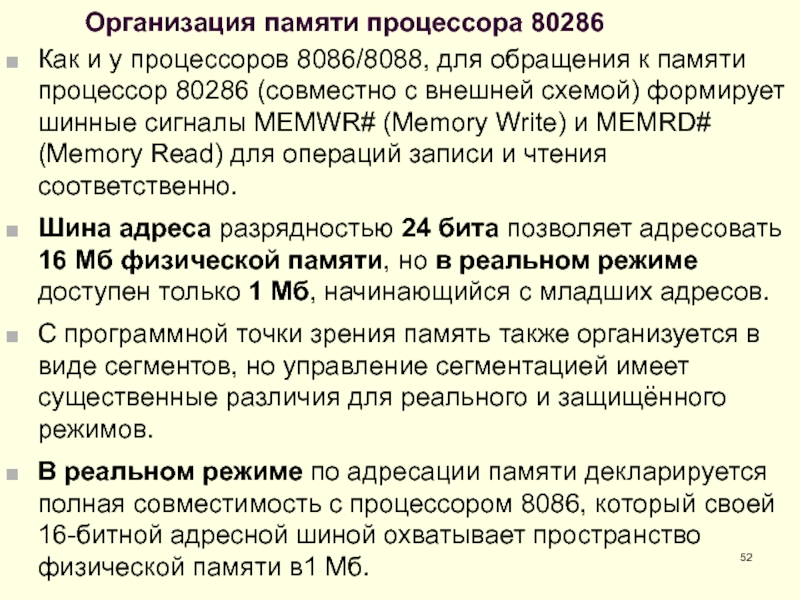

Слайд 52

Организация памяти процессора 80286

Как и у процессоров 8086/8088, для обращения

к памяти процессор 80286 (совместно с внешней схемой) формирует шинные сигналы MEMWR# (Memory Write) и MEMRD# (Memory Read) для операций записи и чтения соответственно.

Шина адреса разрядностью 24 бита позволяет адресовать 16 Мб физической памяти, но в реальном режиме доступен только 1 Мб, начинающийся с младших адресов.

С программной точки зрения память также организуется в виде сегментов, но управление сегментацией имеет существенные различия для реального и защищённого режимов.

В реальном режиме по адресации памяти декларируется полная совместимость с процессором 8086, который своей 16-битной адресной шиной охватывает пространство физической памяти в1 Мб.

Шина адреса разрядностью 24 бита позволяет адресовать 16 Мб физической памяти, но в реальном режиме доступен только 1 Мб, начинающийся с младших адресов.

С программной точки зрения память также организуется в виде сегментов, но управление сегментацией имеет существенные различия для реального и защищённого режимов.

В реальном режиме по адресации памяти декларируется полная совместимость с процессором 8086, который своей 16-битной адресной шиной охватывает пространство физической памяти в1 Мб.

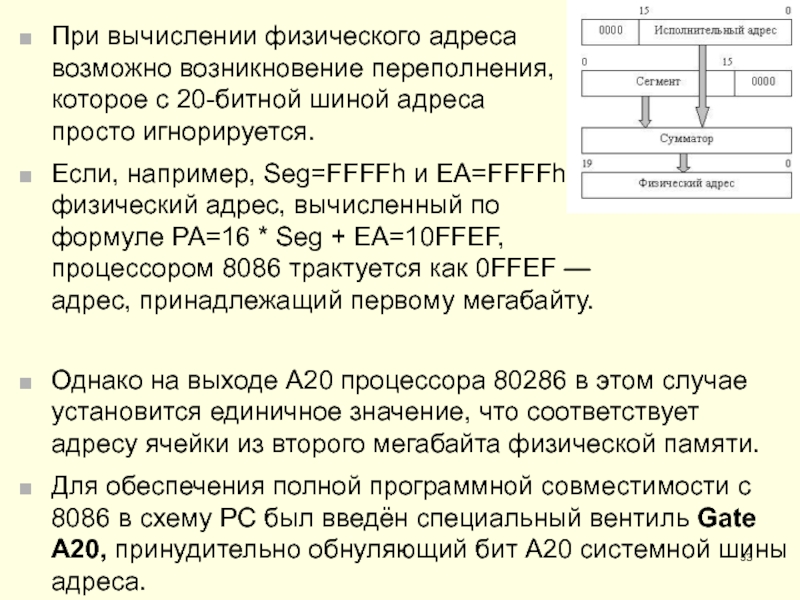

Слайд 53

При вычислении физического адреса

возможно возникновение переполнения,

которое с 20-битной шиной адреса

просто игнорируется.

Если,

например, Seg=FFFFh и EA=FFFFh,

физический адрес, вычисленный по

формуле РА=16 * Seg + EA=10FFEF,

процессором 8086 трактуется как 0FFEF —

адрес, принадлежащий первому мегабайту.

Однако на выходе А20 процессора 80286 в этом случае установится единичное значение, что соответствует адресу ячейки из второго мегабайта физической памяти.

Для обеспечения полной программной совместимости с 8086 в схему PC был введён специальный вентиль Gate A20, принудительно обнуляющий бит A20 системной шины адреса.

Однако на выходе А20 процессора 80286 в этом случае установится единичное значение, что соответствует адресу ячейки из второго мегабайта физической памяти.

Для обеспечения полной программной совместимости с 8086 в схему PC был введён специальный вентиль Gate A20, принудительно обнуляющий бит A20 системной шины адреса.

Слайд 54

В защищённом режиме работают все режимы адресации, допустимые для 8086 и

реального режима 80286. Отличия касаются определения сегментов:

сегментные регистры CS, DS, SS и ES хранят не сами базовые адреса сегментов, а селекторы, по которым из таблицы, хранящейся в ОЗУ, извлекаются дескрипторы сегментов;

дескриптор описывает базовый адрес, размер сегмента (1-64 Кб) и его атрибуты;

базовый адрес сегмента имеет разрядность 24 бита, что и обеспечивает адресацию 16 Мб физической памяти.

Селекторы, загружаемые в 16-разрядные сегментные регистры, имеют три поля RPL (биты 0, 1), TI (бит 2) и INDEX (биты 3-15):

RPL (Requested Privilege Level) – запрошенный уровень привилегий;

TI (Table Indicator) – индикатор использования GDT – глобальной (Т1==0) или LDT – локальной (Т1=1) таблицы дескрипторов;

INDEX — номер дескриптора в таблице.

сегментные регистры CS, DS, SS и ES хранят не сами базовые адреса сегментов, а селекторы, по которым из таблицы, хранящейся в ОЗУ, извлекаются дескрипторы сегментов;

дескриптор описывает базовый адрес, размер сегмента (1-64 Кб) и его атрибуты;

базовый адрес сегмента имеет разрядность 24 бита, что и обеспечивает адресацию 16 Мб физической памяти.

Селекторы, загружаемые в 16-разрядные сегментные регистры, имеют три поля RPL (биты 0, 1), TI (бит 2) и INDEX (биты 3-15):

RPL (Requested Privilege Level) – запрошенный уровень привилегий;

TI (Table Indicator) – индикатор использования GDT – глобальной (Т1==0) или LDT – локальной (Т1=1) таблицы дескрипторов;

INDEX — номер дескриптора в таблице.

Слайд 55

Прерывания процессора 80286

Как и процессор 8086, 80286 может обрабатывать до 256

типов прерываний.

Прерывания подразделяются три вида:

аппаратные (маскируемые или немаскируемые), вызываемые сигналами на входах процессора;

программные, вызываемые командой INT;

исключения инструкций.

При этом аппаратные и программные прерывания работают точно так же, как в 8086/8088.

Исключения инструкций (Instruction Exceptions) или просто исключения случаются при возникновении особых условий при выполнении операций (в 8086 аналогом исключений являлись внутренние прерывания процессора).

Обработка исключений проводится аналогично обработке прерываний.

Прерывания подразделяются три вида:

аппаратные (маскируемые или немаскируемые), вызываемые сигналами на входах процессора;

программные, вызываемые командой INT;

исключения инструкций.

При этом аппаратные и программные прерывания работают точно так же, как в 8086/8088.

Исключения инструкций (Instruction Exceptions) или просто исключения случаются при возникновении особых условий при выполнении операций (в 8086 аналогом исключений являлись внутренние прерывания процессора).

Обработка исключений проводится аналогично обработке прерываний.

Слайд 56

Каждому номеру прерывания соответствует свой элемент в таблице дескрипторов прерываний IDT

(Interrupt Descriptor Table).

В реальном режиме эта таблица организована так же, как у 8086/8088, то есть содержит двойные слова, определяющие адрес начала процедур обработки прерываний.

В защищенном режиме таблица содержит 8-байтные дескрипторы прерываний. Ее размер может быть от 32 до 256 дескрипторов, и располагаться она может в любом месте памяти.

В реальном режиме эта таблица организована так же, как у 8086/8088, то есть содержит двойные слова, определяющие адрес начала процедур обработки прерываний.

В защищенном режиме таблица содержит 8-байтные дескрипторы прерываний. Ее размер может быть от 32 до 256 дескрипторов, и располагаться она может в любом месте памяти.

Слайд 57

Система команд процессора 80286

Система команд процессора 80286 включает, помимо полного

набора команд процессора 8086, ряд дополнительных команд, например:

сохранение константы в стеке, сохранение в стеке и восстановление из стека всех регистров одной командой;

целочисленное умножение на константу;

сдвиги (включая циклические) на заданное в константе количество шагов;

вход и выход из процедур;

команды управления защитой.

Попытка выполнения недействительной команды (или попытка выполнения в реальном режиме команды, предназначенной только для защищенного режима) вызывает специальное исключение.

сохранение константы в стеке, сохранение в стеке и восстановление из стека всех регистров одной командой;

целочисленное умножение на константу;

сдвиги (включая циклические) на заданное в константе количество шагов;

вход и выход из процедур;

команды управления защитой.

Попытка выполнения недействительной команды (или попытка выполнения в реальном режиме команды, предназначенной только для защищенного режима) вызывает специальное исключение.

Слайд 58

Интерфейс процессора 80286

Процессоры 80286 выпускались в 68-выводных корпусах PLCC

и PGA. Их интерфейс отличается от 8086 применением раздельных шин адреса и данных, конвейерной адресации, а также составом и назначением управляющих сигналов.

Конвейерная адресация (Pipelined Addressing), применяемая в процессоре, предусматривает возможность начала (фазы идентификации и адресации) нового цикла, не дожидаясь завершения физического обмена данными предыдущего цикла. Это позволяет сократить число тактов ожидания, необходимых для согласования с относительно медленной памятью и портами, за счет более раннего начала выполнения дешифрации адреса устройством памяти или ввода-вывода. Конвейерный режим позволяет контроллерам памяти эффективно использовать быстрый страничный режим динамической памяти и чередование банков.

Конвейерная адресация (Pipelined Addressing), применяемая в процессоре, предусматривает возможность начала (фазы идентификации и адресации) нового цикла, не дожидаясь завершения физического обмена данными предыдущего цикла. Это позволяет сократить число тактов ожидания, необходимых для согласования с относительно медленной памятью и портами, за счет более раннего начала выполнения дешифрации адреса устройством памяти или ввода-вывода. Конвейерный режим позволяет контроллерам памяти эффективно использовать быстрый страничный режим динамической памяти и чередование банков.

Слайд 59

Функционирование процессора 80286

Основными компонентами системы на базе процессора 80286 являются:

собственно микропроцессор

80286;

синхрогенератор 82284;

шинный контроллер 82288.

Система использует три шины:

адреса,

данных,

управляющих сигналов.

Синхрогенератор генерирует тактовый сигнал CLK для синхронизации внутреннего функционирования процессора и других микросхем. Сигнал RESET производит сброс процессора в начальное состояние. Это состояние показано на рисунке упрощенно. Сигнал READY# также формируется с помощью синхрогенератора. Он предназначен для удлинения циклов при работе с медленными периферийными устройствами.

синхрогенератор 82284;

шинный контроллер 82288.

Система использует три шины:

адреса,

данных,

управляющих сигналов.

Синхрогенератор генерирует тактовый сигнал CLK для синхронизации внутреннего функционирования процессора и других микросхем. Сигнал RESET производит сброс процессора в начальное состояние. Это состояние показано на рисунке упрощенно. Сигнал READY# также формируется с помощью синхрогенератора. Он предназначен для удлинения циклов при работе с медленными периферийными устройствами.

Слайд 60

На адресную шину, состоящую из 24 линий, микропроцессор выставляет адрес байта

или слова, который будет пересылаться по шине данных в процессор или из него. Кроме того, шина адреса используется микропроцессором для указания адресов периферийных портов, с которыми производится обмен данными.

Шина данных состоит из 16 линий. по которым возможна передача как отдельных байтов. так и двухбайтовых слов. При пересылке байтов возможна передача и по старшим 8 линиям, и по младшим. Шина данных двунаправлена, так как передача байтов и слов может производится как в микропроцессор, так и из него.

Шина управления формируется сигналами, поступающими непосредственно от микропроцессора, сигналами от шинного контроллера, а также сигналами, идущими к микропроцессору от других микросхем и периферийных адаптеров.

Шина данных состоит из 16 линий. по которым возможна передача как отдельных байтов. так и двухбайтовых слов. При пересылке байтов возможна передача и по старшим 8 линиям, и по младшим. Шина данных двунаправлена, так как передача байтов и слов может производится как в микропроцессор, так и из него.

Шина управления формируется сигналами, поступающими непосредственно от микропроцессора, сигналами от шинного контроллера, а также сигналами, идущими к микропроцессору от других микросхем и периферийных адаптеров.

Слайд 61

Микропроцессор использует шинный контроллер для формирования управляющих сигналов, определяющих передачу данных

по шине.

Контроллер шины выставляет три сигнала (SO#, SI#, M/IO#), которые определяют тип цикла шины:

подтверждение прерывания,

чтение порта ввода/вывода,

останов,

чтение памяти,

запись в память.

На основании значений сигналов SO#, SI#, M/IO# шинный контроллер формирует управляющие сигналы, контролирующие динамику данного типа шины.

Контроллер шины выставляет три сигнала (SO#, SI#, M/IO#), которые определяют тип цикла шины:

подтверждение прерывания,

чтение порта ввода/вывода,

останов,

чтение памяти,

запись в память.

На основании значений сигналов SO#, SI#, M/IO# шинный контроллер формирует управляющие сигналы, контролирующие динамику данного типа шины.

Слайд 62

Чтение процессором слов из оперативной памяти происходит в течение 4 тактов

тактовой частоты CLK, или 2 состояний процессора (т.е. каждое состояние процессора длится 2 такта синхросигнала CLK).

Во время первого состояния процессор выставляет на адресную шину значение адреса, по которому будет читаться слово. Кроме того, он формирует на шине совместно с шинным контроллером соответствующие значения управляющих сигналов.

Эти сигналы и адрес обрабатываются схемой управления памятью, в результате чего, начиная с середины второго состояния процессора (т.е. в начале четвертого такта CLK) на шине данных появляется значение содержимого соответствующего слова из оперативной памяти.

Далее процессор считывает значение этого слова с шины данных.

На этом перенос (копирование) значения слова из памяти в процессор заканчивается.

Во время первого состояния процессор выставляет на адресную шину значение адреса, по которому будет читаться слово. Кроме того, он формирует на шине совместно с шинным контроллером соответствующие значения управляющих сигналов.

Эти сигналы и адрес обрабатываются схемой управления памятью, в результате чего, начиная с середины второго состояния процессора (т.е. в начале четвертого такта CLK) на шине данных появляется значение содержимого соответствующего слова из оперативной памяти.

Далее процессор считывает значение этого слова с шины данных.

На этом перенос (копирование) значения слова из памяти в процессор заканчивается.

Слайд 63В начале 1987 г. на базе МП 386DX фирма IBM выпустила

компьютер PS/2 модели 80 с тактовой частотой 20 МГц, который стал настоящей сенсацией из-за высокой производительности вычислений. Помимо высокого быстродействия достоинством МП 386 является возможность работать в реальном, защищенном и виртуальном режимах. Реальный режим, как и для 286-го процессора, это базовый режим совместимости с 8086. Компьютер в этом режиме (Turbo PC) быстрее осуществляет вычисления с ОЗУ 640 Кб и программами для DOS. В архитектуру процессоров Intel, начиная с 80386, для вычислений и адресации памяти вводятся 32-разрядные регистры (архитектура IA-32) общего назначения (GP), подходящие как для хранения адресов, так и для операндов. Часть каждого 32‑разрядного регистра для обеспечения совместимости имеет значение одного 16-разрядного регистра предыдущих двух поколений процессоров.

Слайд 64Был введен новый «виртуальный режим» 8086 для повышения быстродействия выполнения программ

на новой 32-разрядной машине, созданный ранее для процессоров 8086 и 8088. 32-разрядная адресация позволяет адресовать к 4 Гб адресного пространства, и также увеличить размер каждого сегмента до 4 Гб. Первоначальные инструкции х86 были расширены новыми инструкциями с 32‑разрядными операндами и формой адресации. В процессоре Intel 386 также вводится метод для управления виртуальной памятью и страничная организация памяти, с фиксированным размером страницы 4 Kб, и возможность определения сегментов размером в 4 Гб.

Слайд 65Процессор Intel 386 был первым архитектуры IA-32, в который включили 6

параллельно работающих блоков:

- шинный интерфейс (доступ к памяти и устройствам ввода/вывода других блоков);

- блок предварительной выборки кода (получает объект-ный код из шинного интерфейса и помещает его в 16‑байтную очередь);

- блок декодирования инструкций (декодирует объект-ный код из блока предварительной выборки в микрокод);

- блок выполнения (выполняет инструкции микрокода);

- сегментный блок (переводит логические адреса в линейные адреса и выполняет проверку защиты);

- блок страничного преобразования (переводит линейные адреса в физические, выполняет проверку страничной защиты и содержит кэш с информацией о 32 наиболее часто используемых страницах).

- шинный интерфейс (доступ к памяти и устройствам ввода/вывода других блоков);

- блок предварительной выборки кода (получает объект-ный код из шинного интерфейса и помещает его в 16‑байтную очередь);

- блок декодирования инструкций (декодирует объект-ный код из блока предварительной выборки в микрокод);

- блок выполнения (выполняет инструкции микрокода);

- сегментный блок (переводит логические адреса в линейные адреса и выполняет проверку защиты);

- блок страничного преобразования (переводит линейные адреса в физические, выполняет проверку страничной защиты и содержит кэш с информацией о 32 наиболее часто используемых страницах).

Слайд 66 Было разработано несколько типов персональных компьютеров с модифи-кациями МП 386 –

SX, SL, DX, работающих с таковыми частотами 16, 20, 25, 33 МГц и сопроцессором 80387, который устанавливался отдельно от МП на системной плате и выполнял операции с плавающей запятой парал-лельно процессору ЭВМ.

Слайд 67Следующим шагом в разработке компьютеров явилось использование в их составе МП

486 следующих разновидностей:

- 486 SX без сопроцессора;

- 486 DX со встроенным сопроцессором;

- 486 DX2 с удвоением внутренней частоты вычислений и сопроцессором;

- 486 DX4 с утроенным быстродействием и сопроцессором.

Тактовая частота первого МП 486 составляла 25 МГц, которая в более поздних МП увеличилась до 33, 50, 66 МГц. Структура процессора 486 подробно рассматривается ниже.

- 486 SX без сопроцессора;

- 486 DX со встроенным сопроцессором;

- 486 DX2 с удвоением внутренней частоты вычислений и сопроцессором;

- 486 DX4 с утроенным быстродействием и сопроцессором.

Тактовая частота первого МП 486 составляла 25 МГц, которая в более поздних МП увеличилась до 33, 50, 66 МГц. Структура процессора 486 подробно рассматривается ниже.

Слайд 68ЭВМ на базе процессора i486 появились в 1989 г., когда Intel

впервые продемонстрировала СБИС i486DX. Процессор i486 в дальнейшем был усовершенствован с использованием новой технологии и, как указывалось выше, имеет несколько модификаций. Наиболее важные его возможности следующие:

-совместимость с системой команд i86, i286, i386;

-32-битная шина адреса и 32-битная шина данных;

-совместимость FPU с сопроцессорами i87, i287, i387 и поддержка 32/64/80-битных форматов чисел;

-наличие кэш первого уровня с быстродействием регистров МП;

-конвейеризация команд, т.е. их параллельная подготовка к выполнению;

-пакетные циклы обмена, снижающие общее время вычислений и передачи данных между МП и DRAM с использованием внутренних буферов записи;

-совместимость с системой команд i86, i286, i386;

-32-битная шина адреса и 32-битная шина данных;

-совместимость FPU с сопроцессорами i87, i287, i387 и поддержка 32/64/80-битных форматов чисел;

-наличие кэш первого уровня с быстродействием регистров МП;

-конвейеризация команд, т.е. их параллельная подготовка к выполнению;

-пакетные циклы обмена, снижающие общее время вычислений и передачи данных между МП и DRAM с использованием внутренних буферов записи;

Слайд 69Схема процессора i486 представлена на рис. Он содержит устройство управления (УУ),

арифметико-логическое устройство (АЛУ), устройство с плавающей точкой (FPU), устройства сегментации и страничного преобразования, кэш-память (КЭШ), устройство предвыборки команд и шинный интерфейс. В составе устройств на схеме показаны все пользовательские и системные регистры процессора. Рассмотрим более подробно назначение устройств процессора.

Шинный интерфейс – это устройство связи i486 с шиной процессора и через контроллер шины с другими блоками ЭВМ. Он обеспечивает двунаправленную передачу данных и адресов, формирование управляющих сигналов (УС) для подключения внешних блоков к контроллеру шины. Передача данных и их прием осуществляется через буферные регистры интерфейса в режиме сквозной записи и пакетного обмена.

Шинный интерфейс – это устройство связи i486 с шиной процессора и через контроллер шины с другими блоками ЭВМ. Он обеспечивает двунаправленную передачу данных и адресов, формирование управляющих сигналов (УС) для подключения внешних блоков к контроллеру шины. Передача данных и их прием осуществляется через буферные регистры интерфейса в режиме сквозной записи и пакетного обмена.

Слайд 71В процессор Intel 486 добавлена возможность одновременного выпол-нения до пяти инструкций

на разных стадиях с помощью расширения блока декодирования инструкций и опера-ционного блока выполнения в пять конвейерных стадий, где каждая стадия работает параллельно с другими. Каждая стадия может выполнить свою работу над одной инструкцией за один такт.

Слайд 72

Также к процессору Intel 486 был добавлен кэш L1 8 Кб

для увеличения числа инструкций, которые могут быть выполнены за один такт. В процессоре Intel 486 впервые в CPU было интегрировано устройство с плавающей запятой (FPU) и добавлены новые инструкции для поддержки кэша L2 и мультипроцессорности. Позже в процессор Intel 486 SL были введены функции поддержки энергосбережения и системного управления для ноутбуков PC, работающих от батарей.