- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Кафедра “компьютерные системы и технологии” презентация

Содержание

- 1. Кафедра “компьютерные системы и технологии”

- 2. Тема 1.1. Основные принципы построения систем ввода вывода и интерфейсов

- 3. Роль и место систем ввода-вывода и интерфейсов в компьютере

- 4. Что такое система ввода-вывода, периферия и интерфейсы?

- 5. Периферийные устройства (внешние устройства) ПУ можно разделить

- 6. Функционально – модульная структура компьютера

- 9. Некоторые понятия интерфейсов Канал – среда передачи

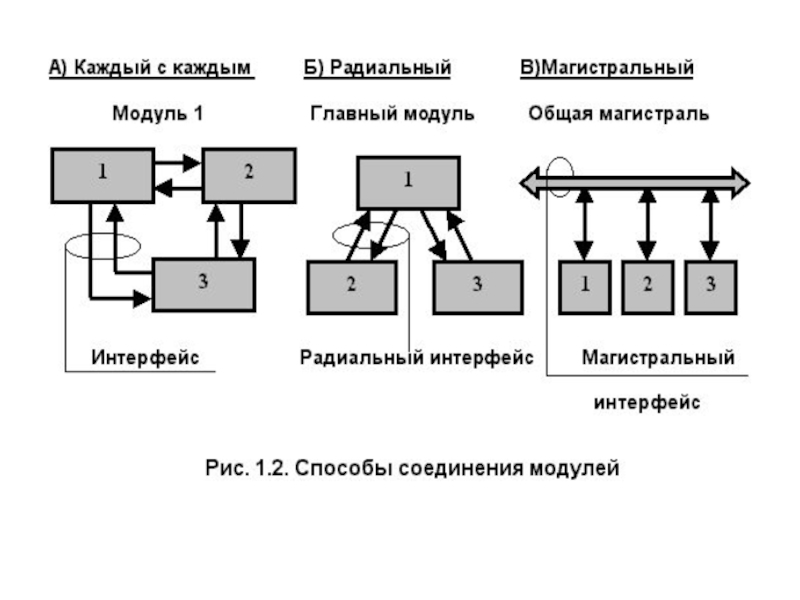

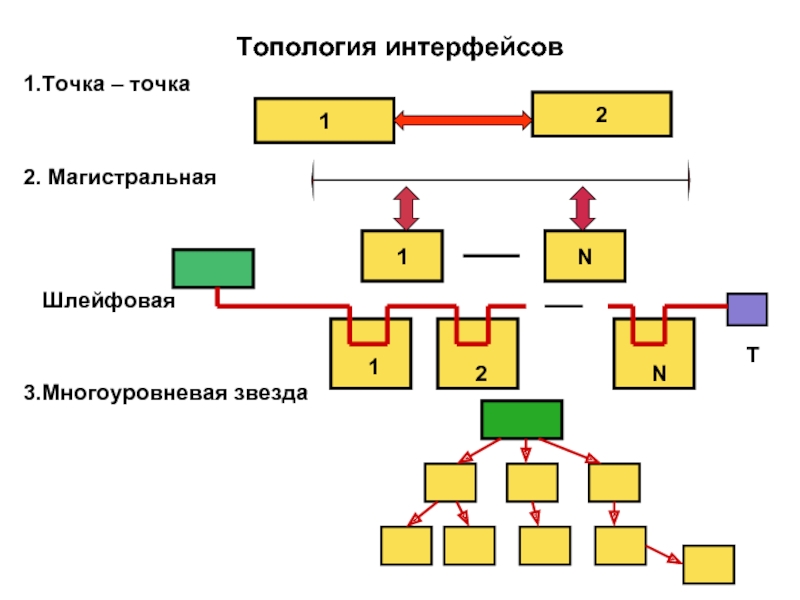

- 11. Топология интерфейсов 1.Точка – точка

- 12. Классификация интерфейсов Существует множество стандартных компьютерных интерфейсов

- 13. 2.По организации обмена. а) Симплексный

- 14. 3. ПО архитектуре интерфейсов.

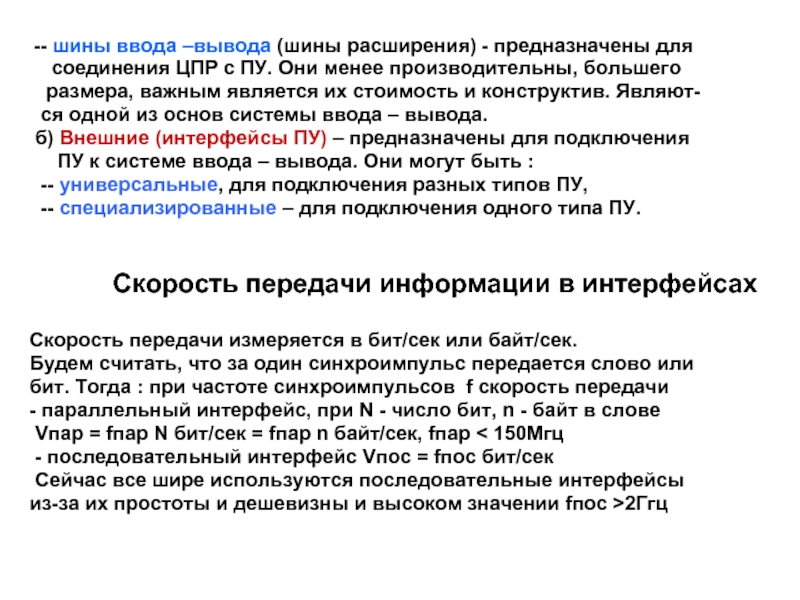

- 15. -- шины ввода –вывода (шины

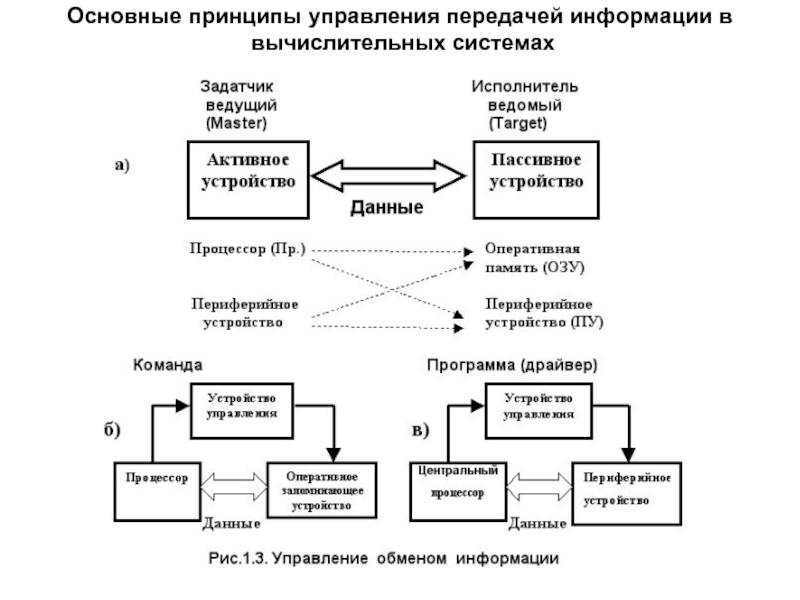

- 16. Основные принципы управления передачей информации в вычислительных системах

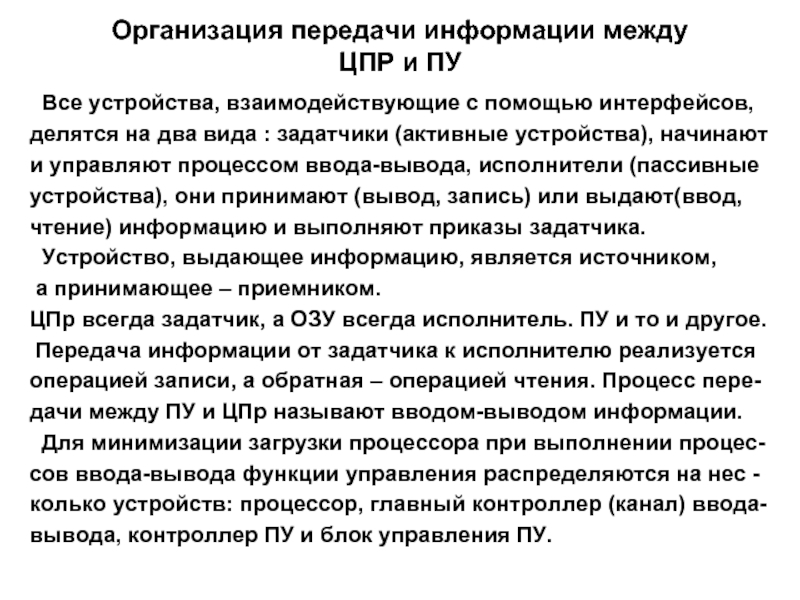

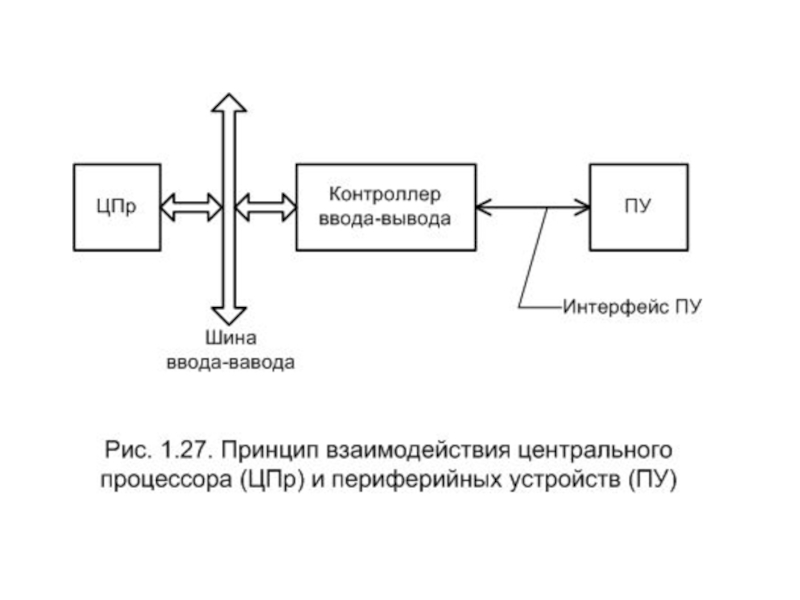

- 17. Организация передачи информации между ЦПР и ПУ

- 18. Многоуровневая организация процесса ввода - вывода

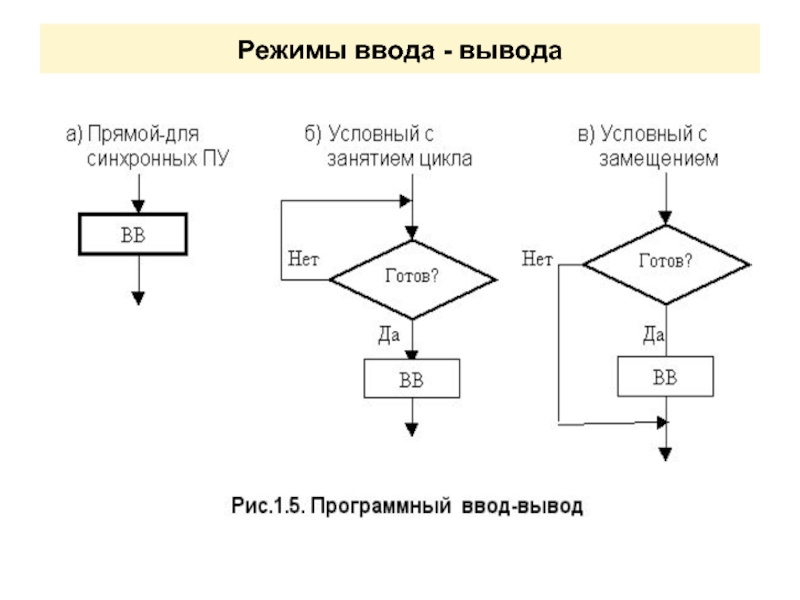

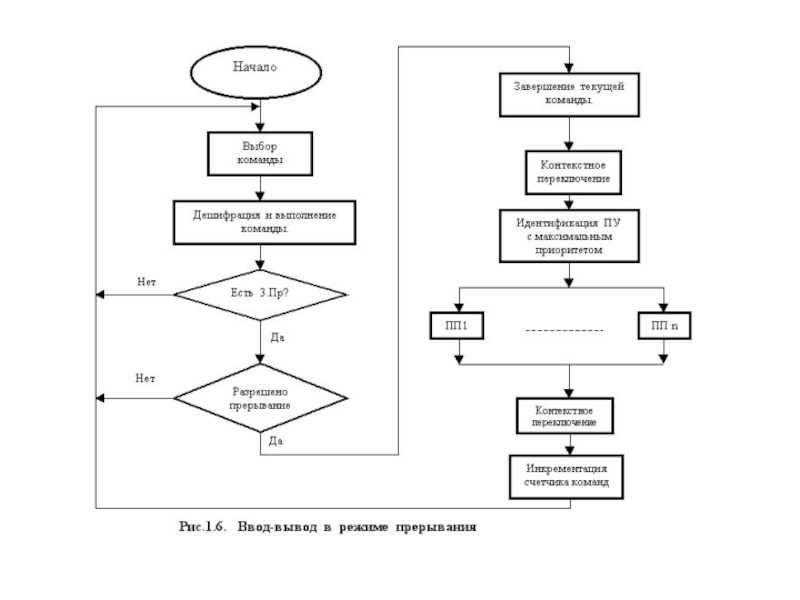

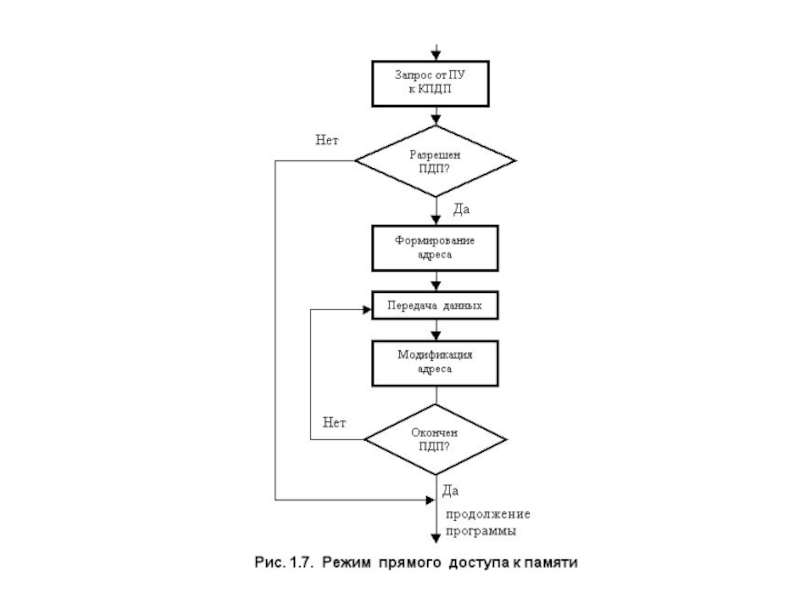

- 19. Режимы ввода - вывода

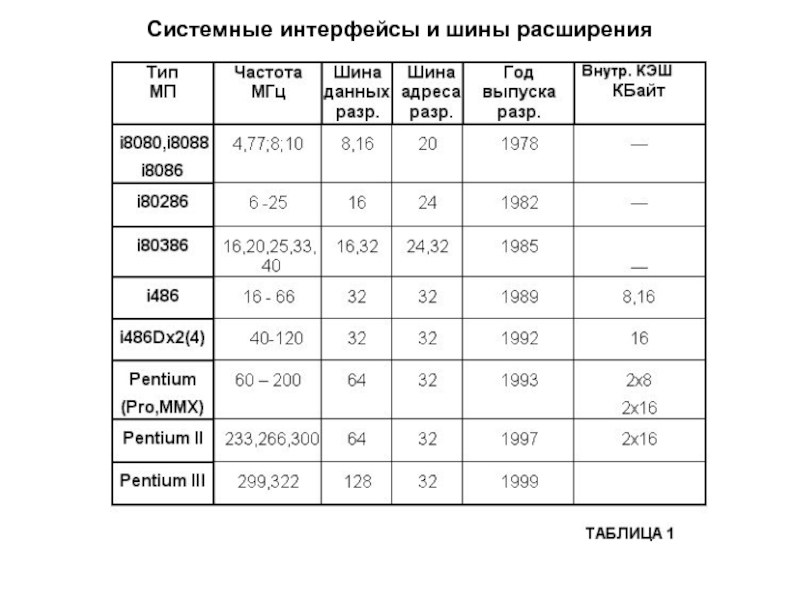

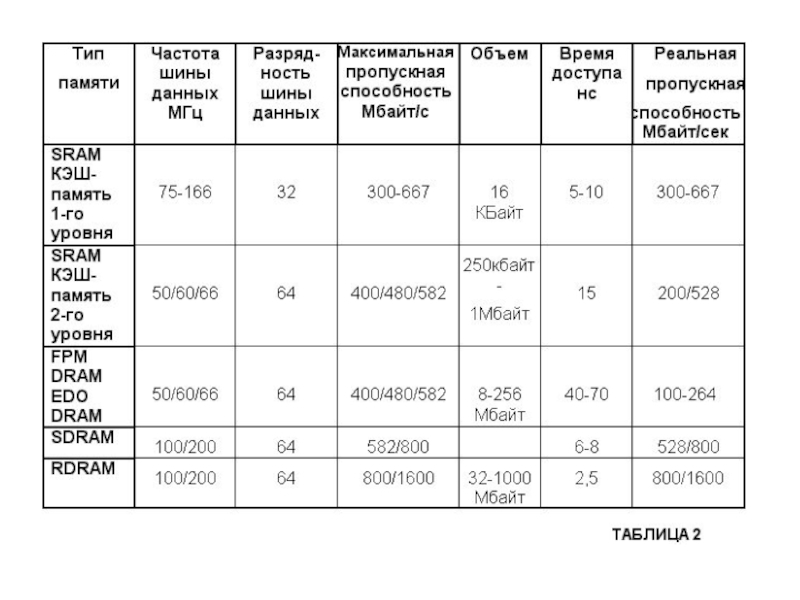

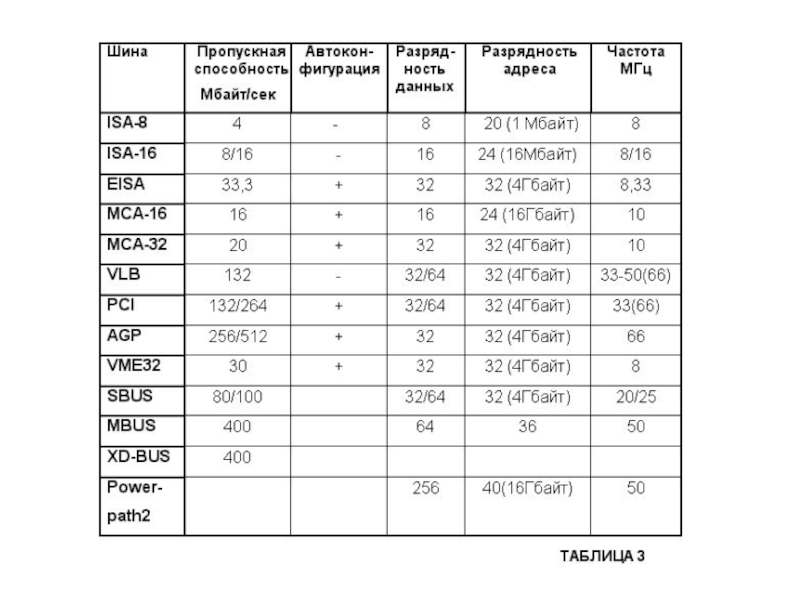

- 22. Системные интерфейсы и шины расширения

- 25. Интерфейсы периферийных устройств

- 26. Тема 1.2. Основные функции и принципы построения интерфейсов

- 27. Основные функции интерфейсов 1. Передача информации. 2.

- 28. Функция передача информации Главная задача интерфейса --

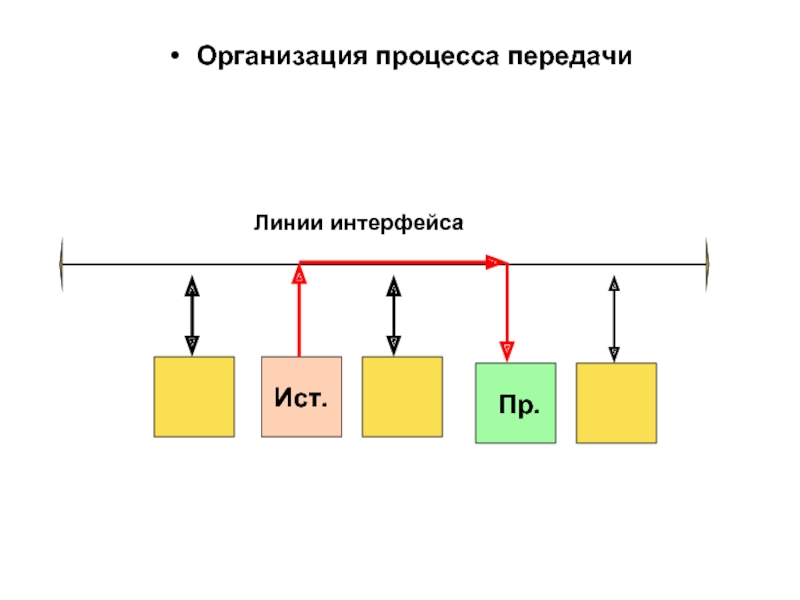

- 29. Организация процесса передачи Ист. Пр. Линии интерфейса

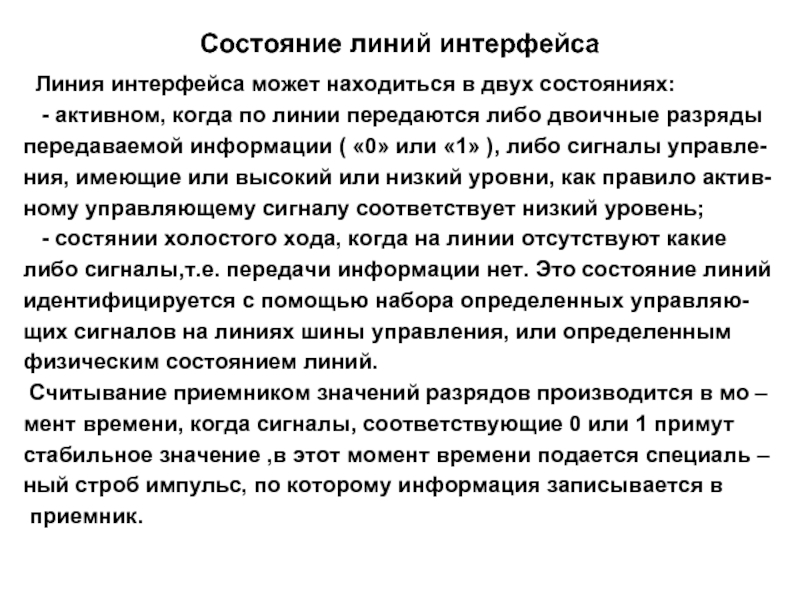

- 30. Состояние линий интерфейса Линия интерфейса может

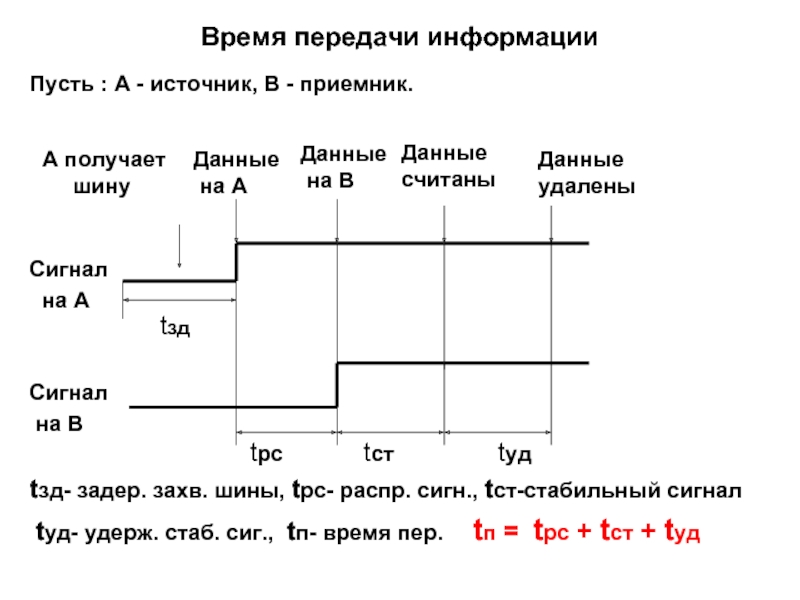

- 31. Время передачи информации Пусть : А -

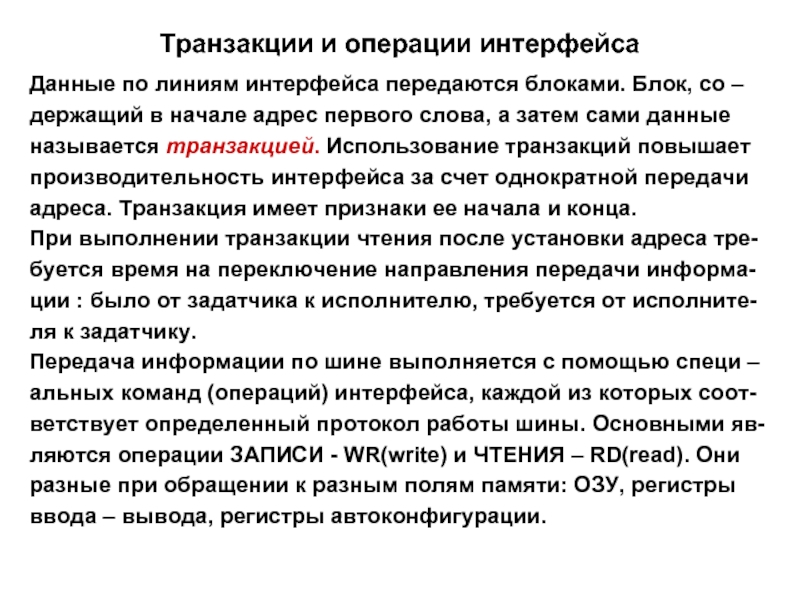

- 32. Транзакции и операции интерфейса Данные по линиям

- 33. Используются следующие принципы построения интерфейсов:

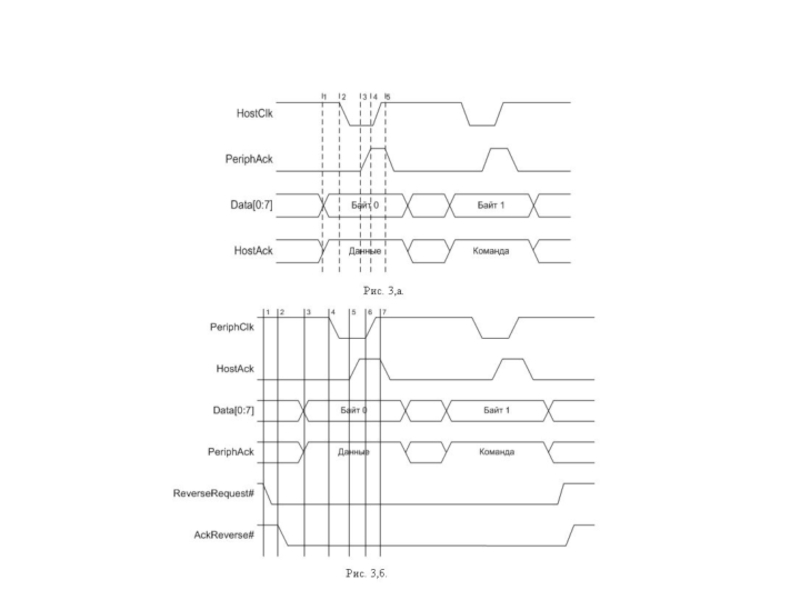

- 34. Функция синхронизации При передаче информации

- 35. Два основных принципа синхронизации:

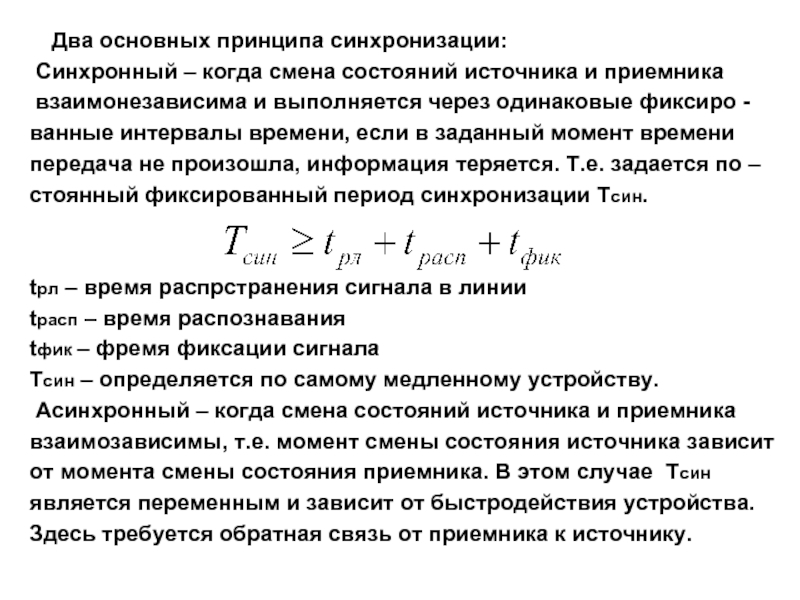

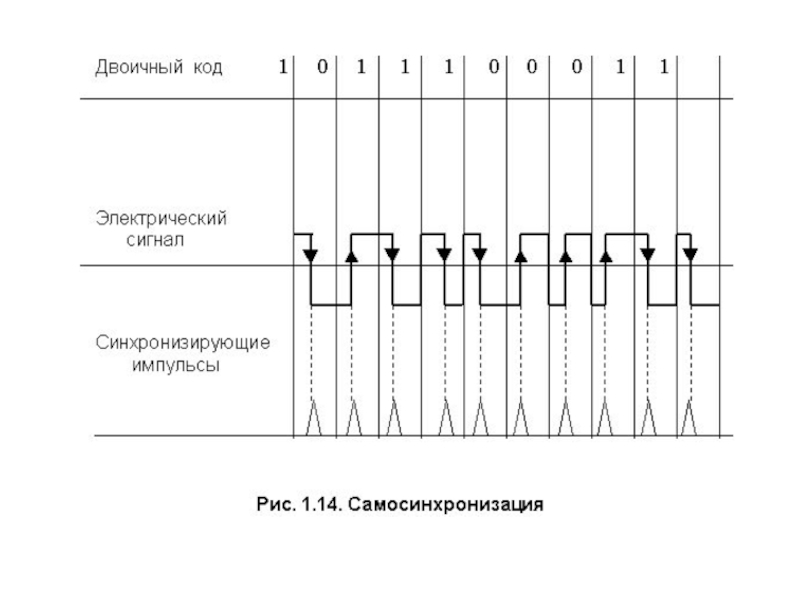

- 36. Последовательная передача данных Синхронный принцип синхронизации

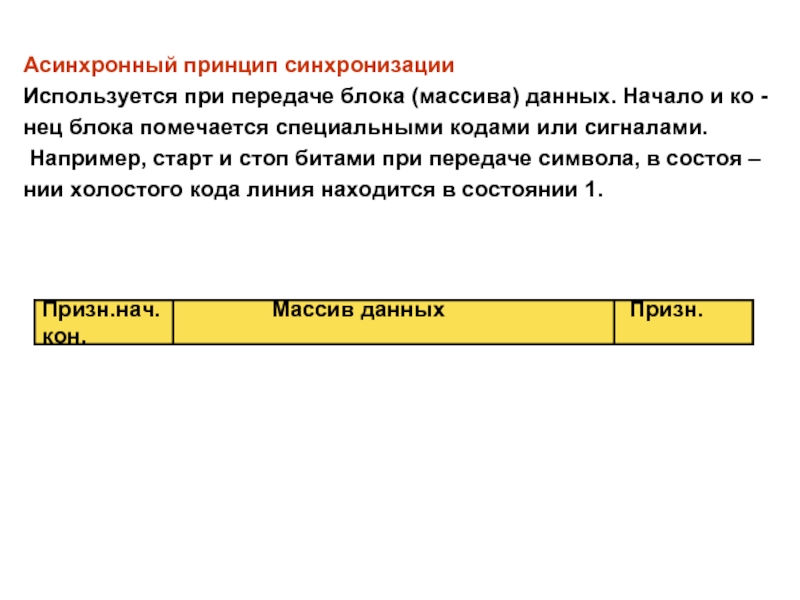

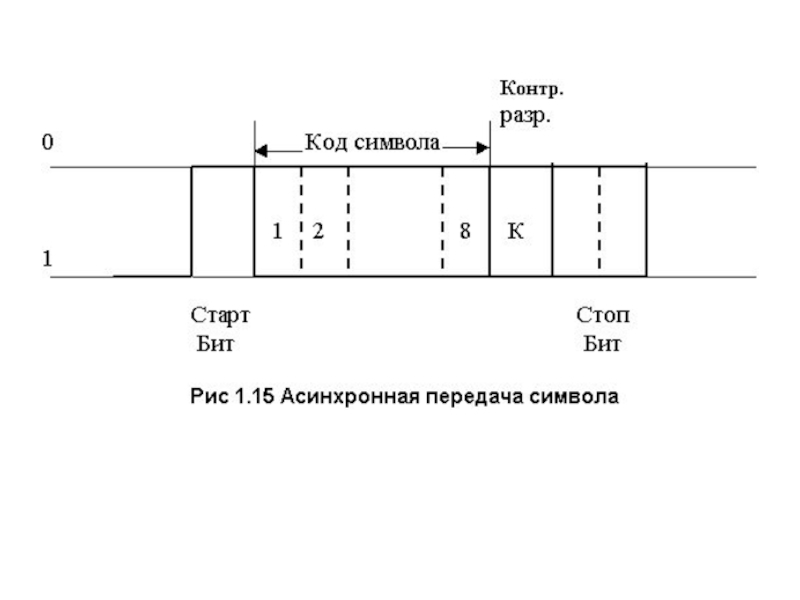

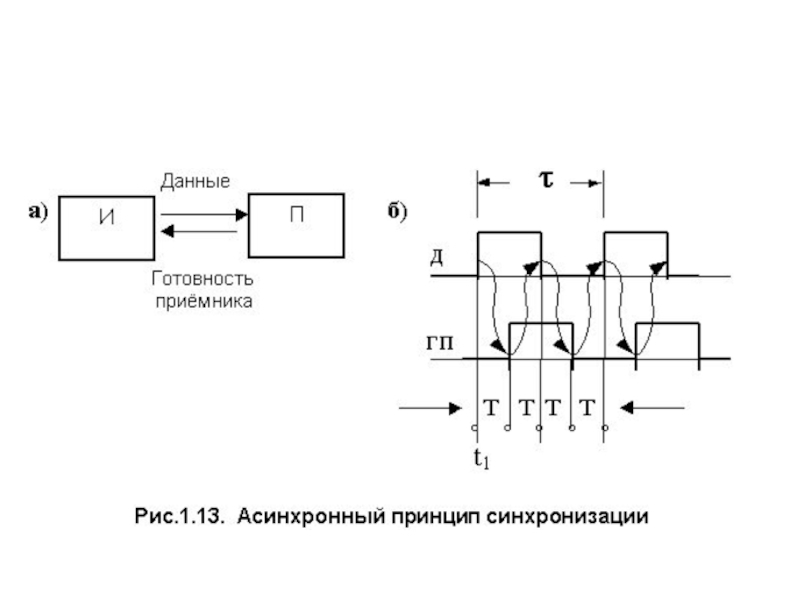

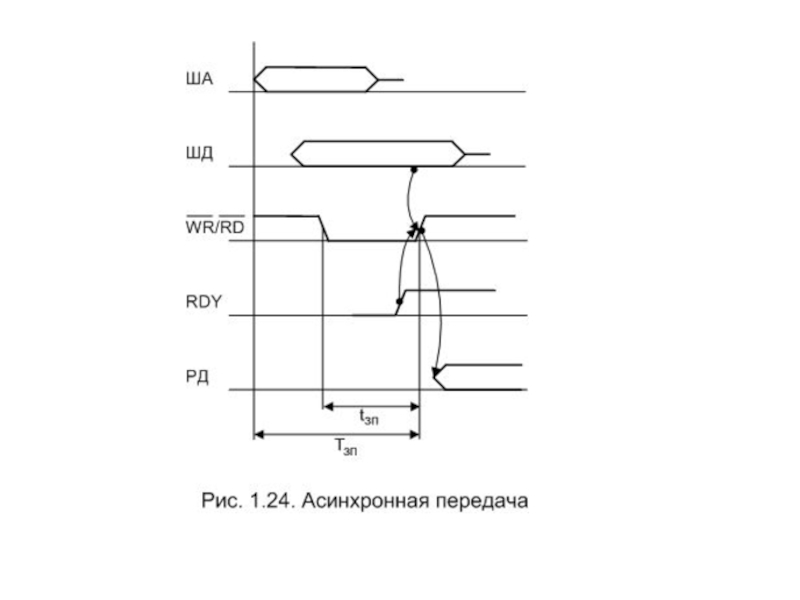

- 38. Асинхронный принцип синхронизации Используется при передаче

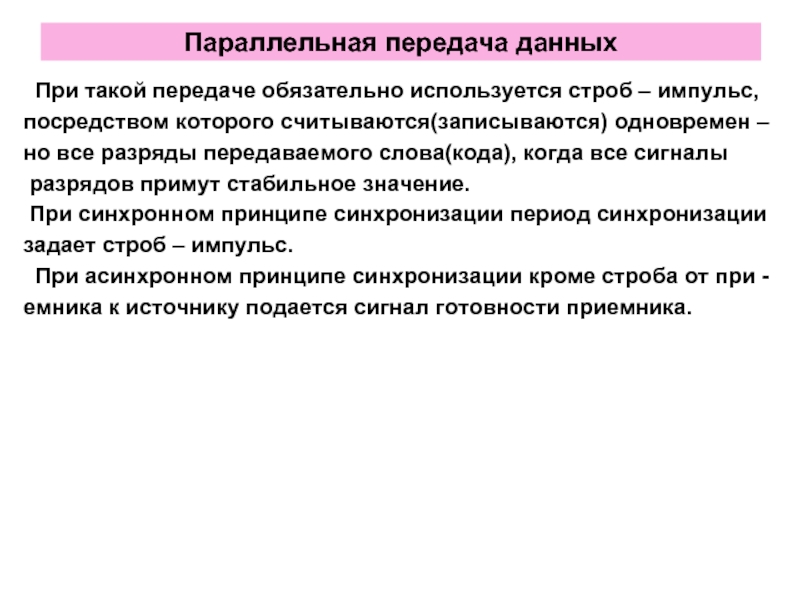

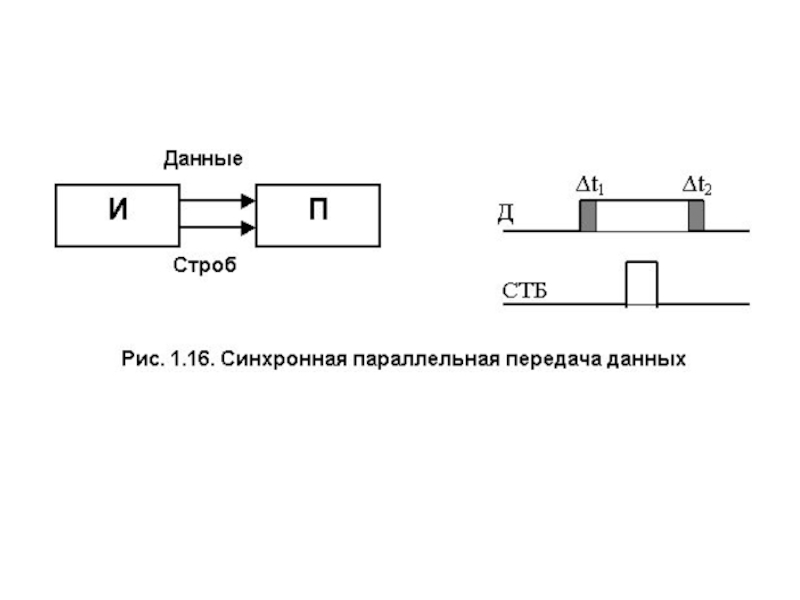

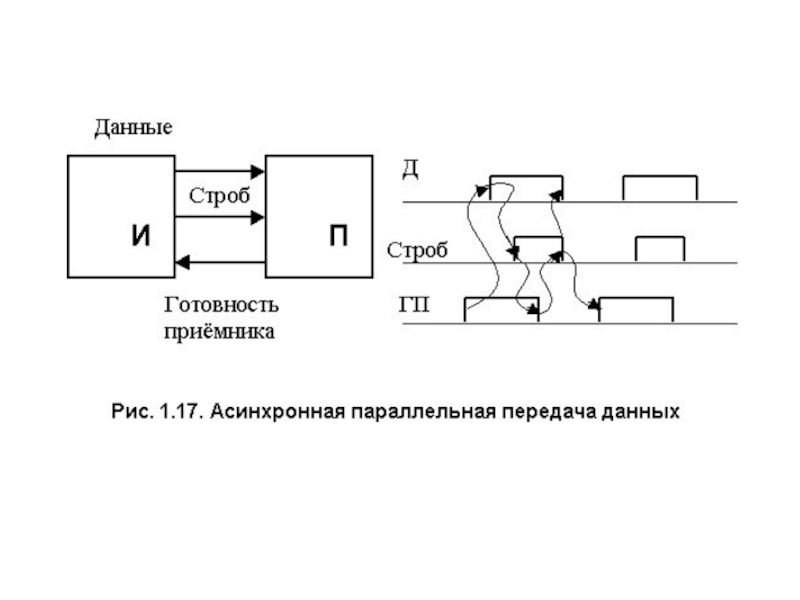

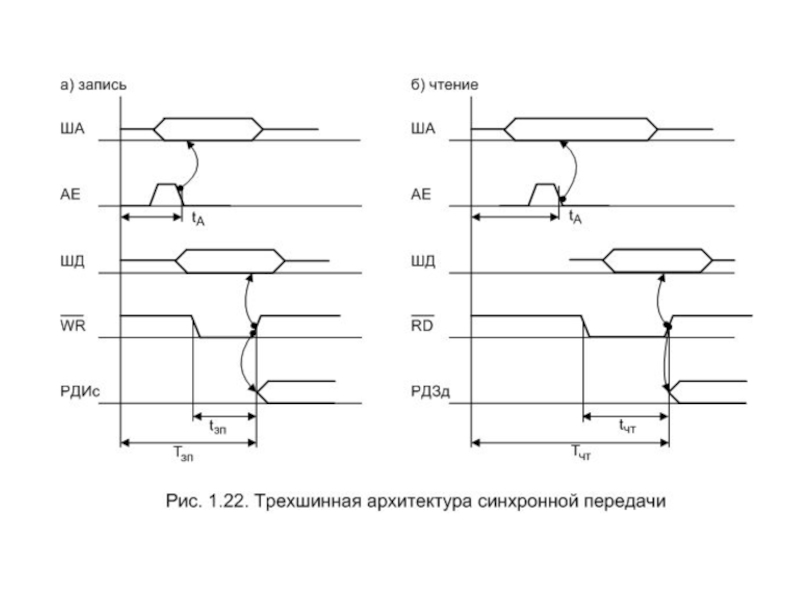

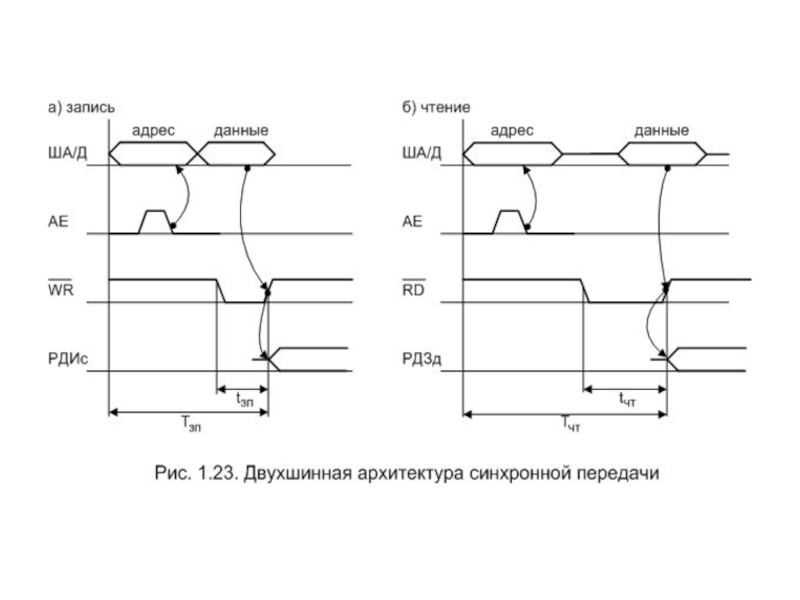

- 40. Параллельная передача данных При такой передаче

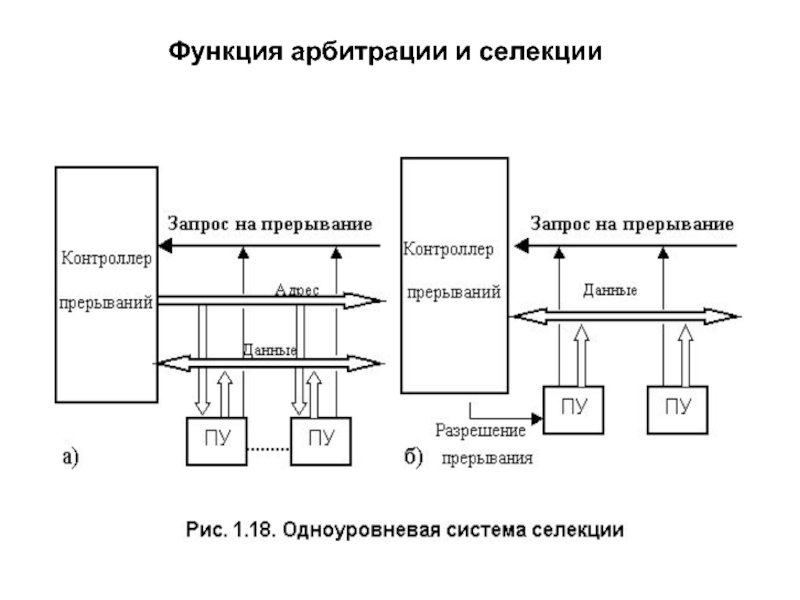

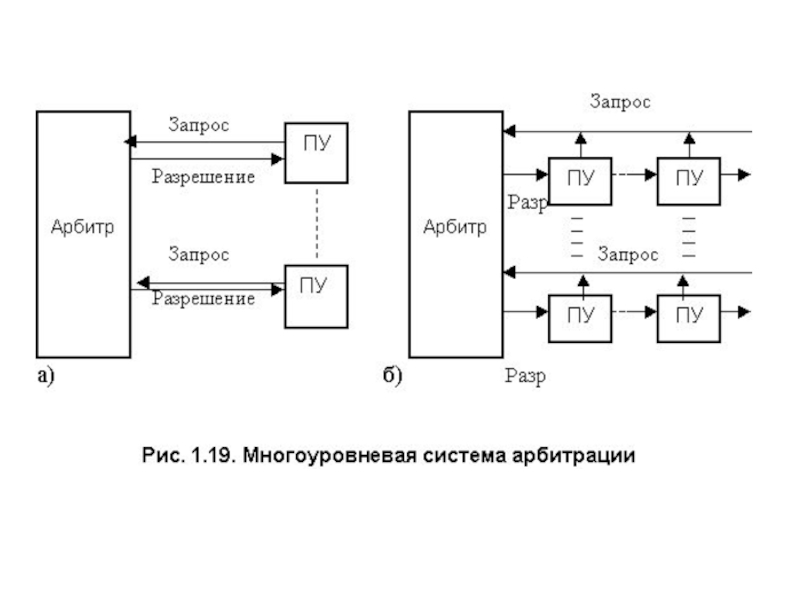

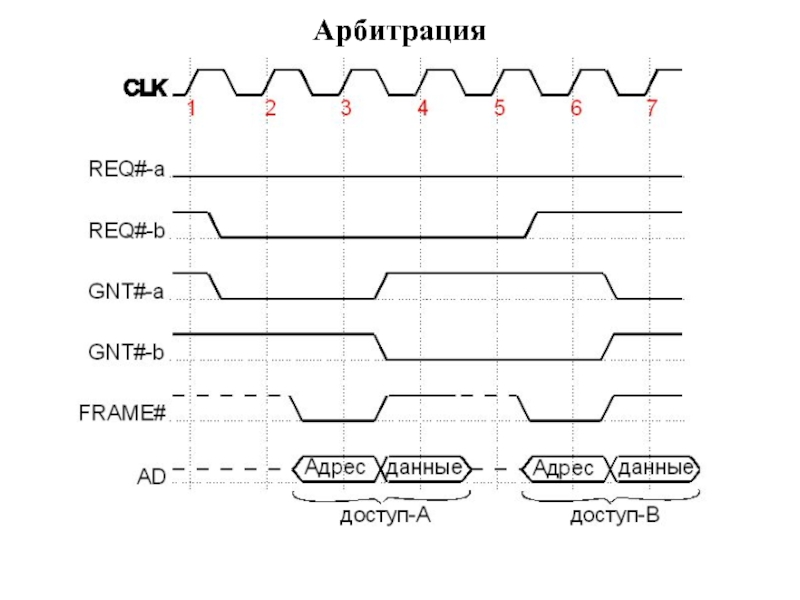

- 44. Функция арбитрации и селекции Способ разрешения

- 45. Функция арбитрации и селекции

- 47. Функция контроля: избыточное кодирование

- 48. Инициатива OnNow заключается в расширении состояния

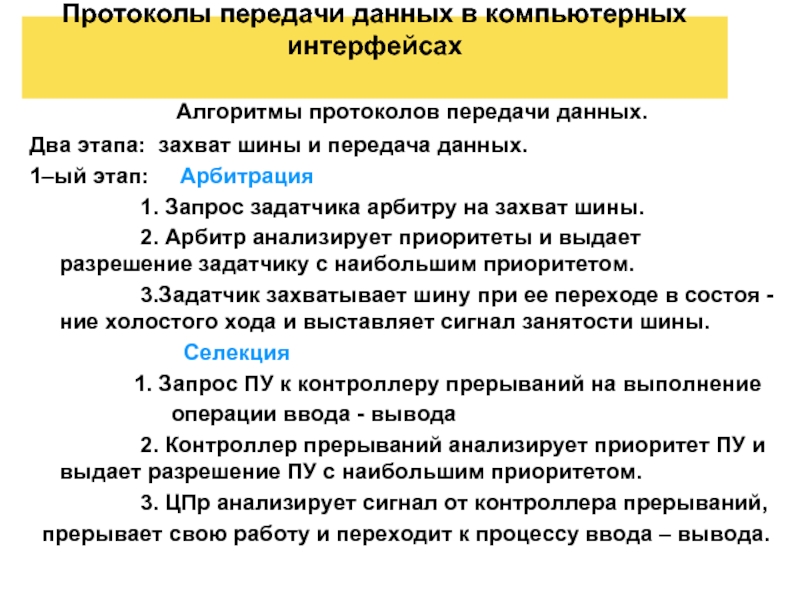

- 49. Протоколы передачи данных в компьютерных интерфейсах

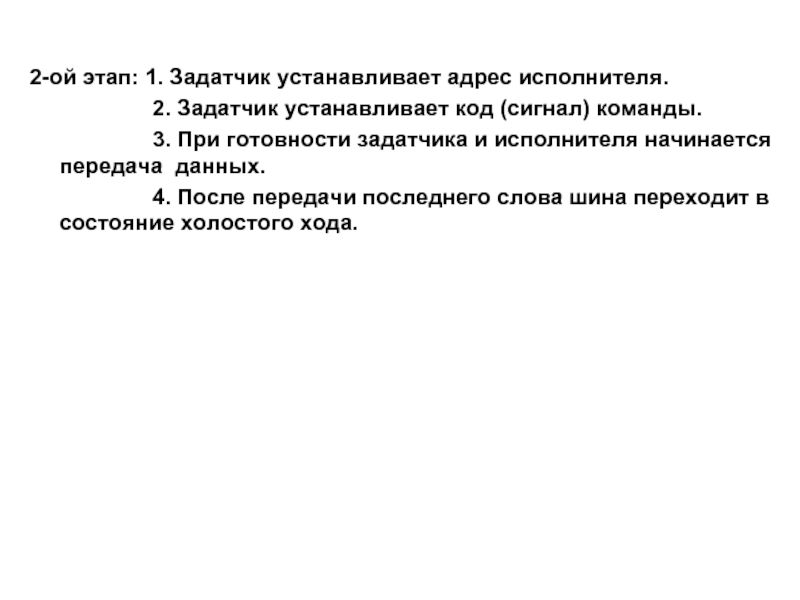

- 50. 2-ой этап: 1. Задатчик устанавливает

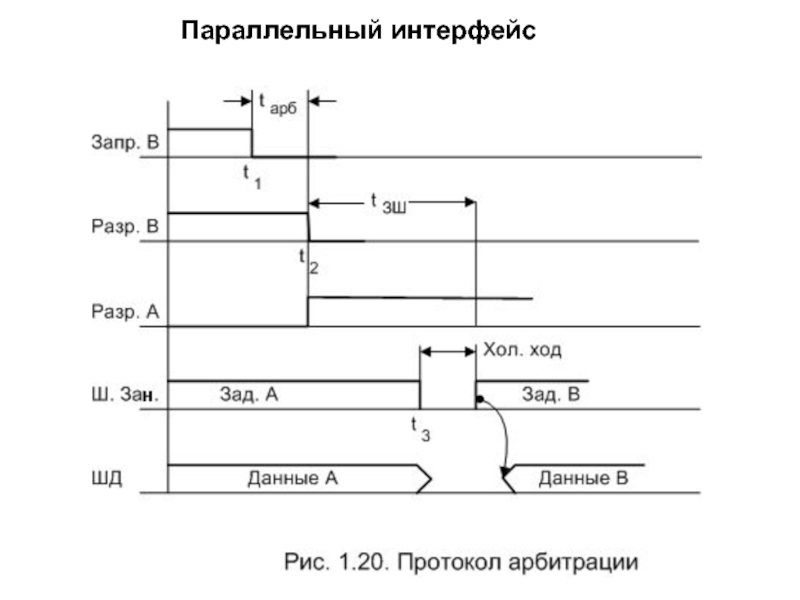

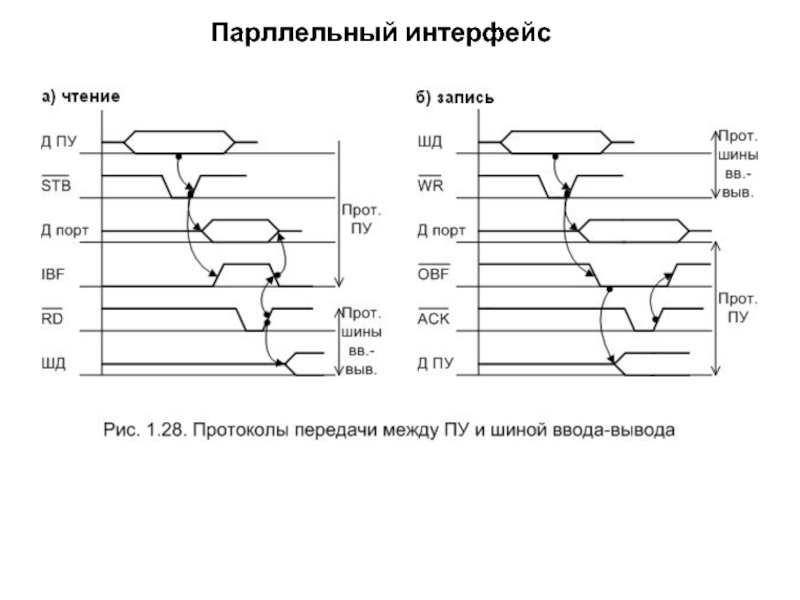

- 51. Параллельный интерфейс

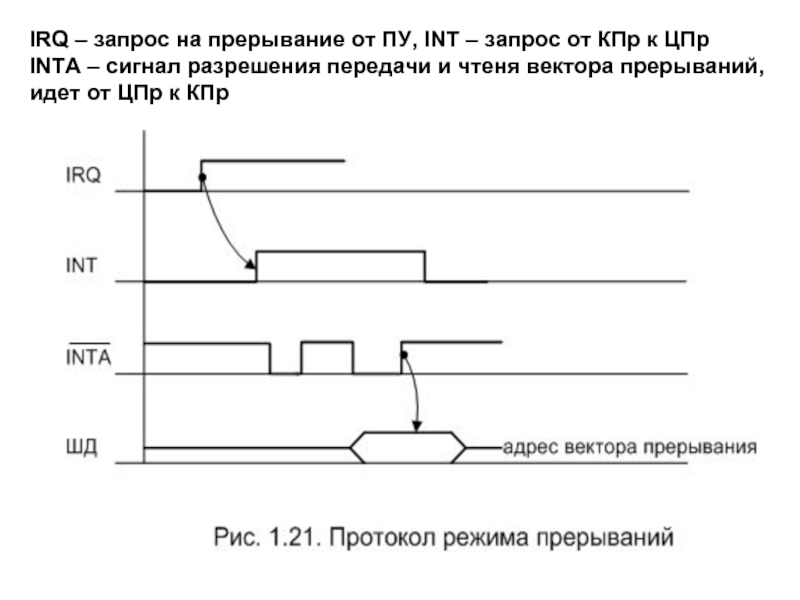

- 52. IRQ – запрос на прерывание от

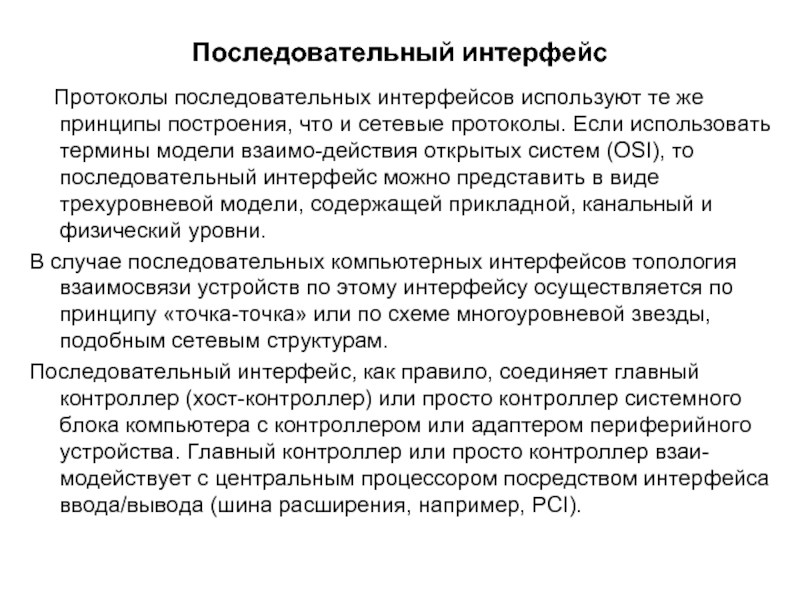

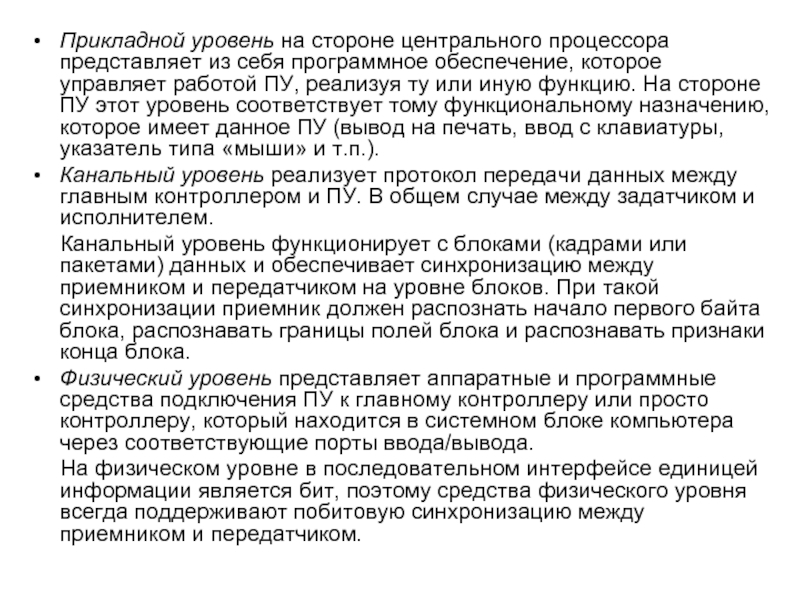

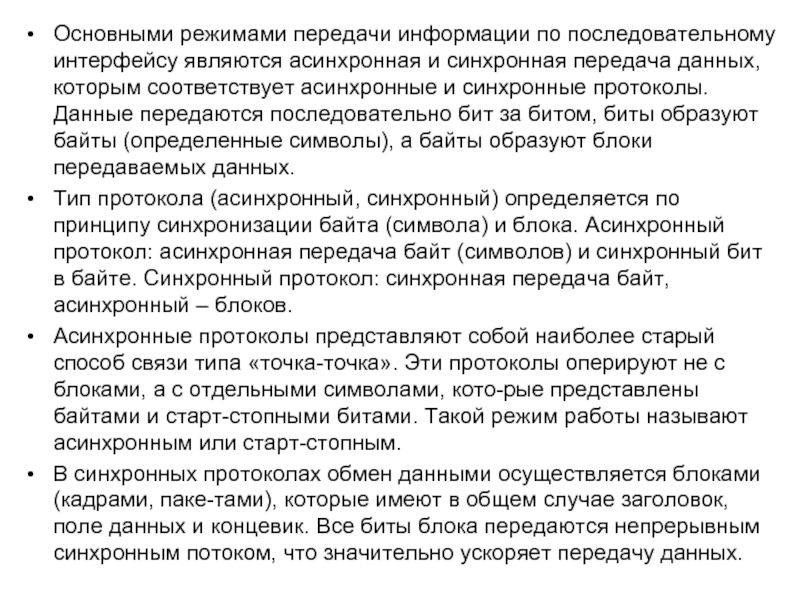

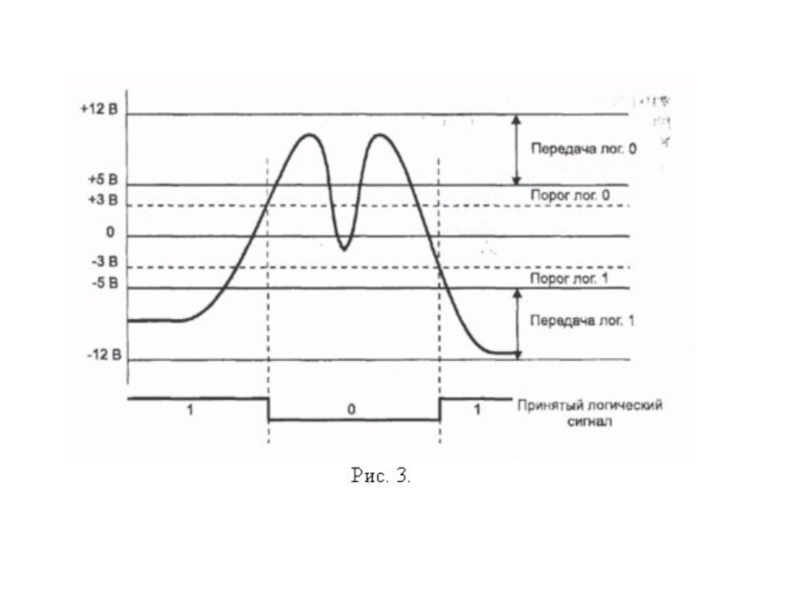

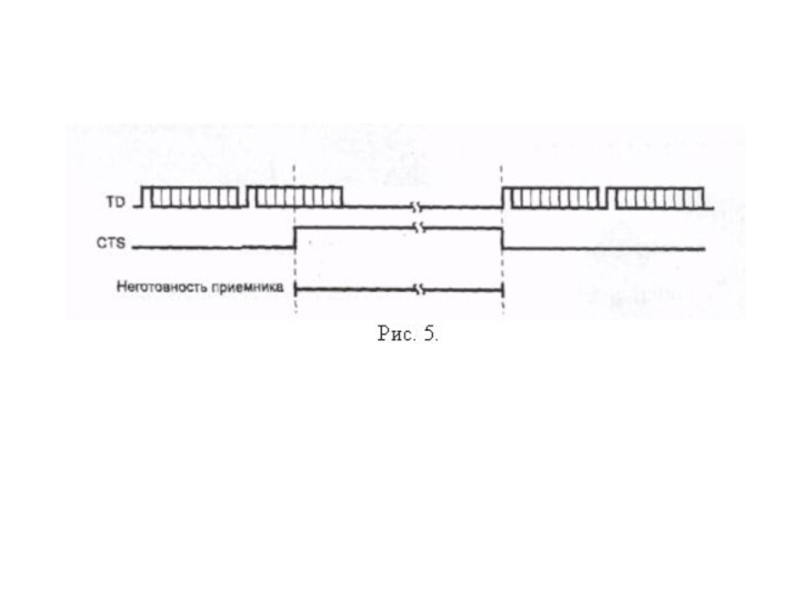

- 56. Последовательный интерфейс Протоколы последовательных интерфейсов

- 57. Прикладной уровень на стороне центрального процессора

- 58. Основными режимами передачи информации по последовательному

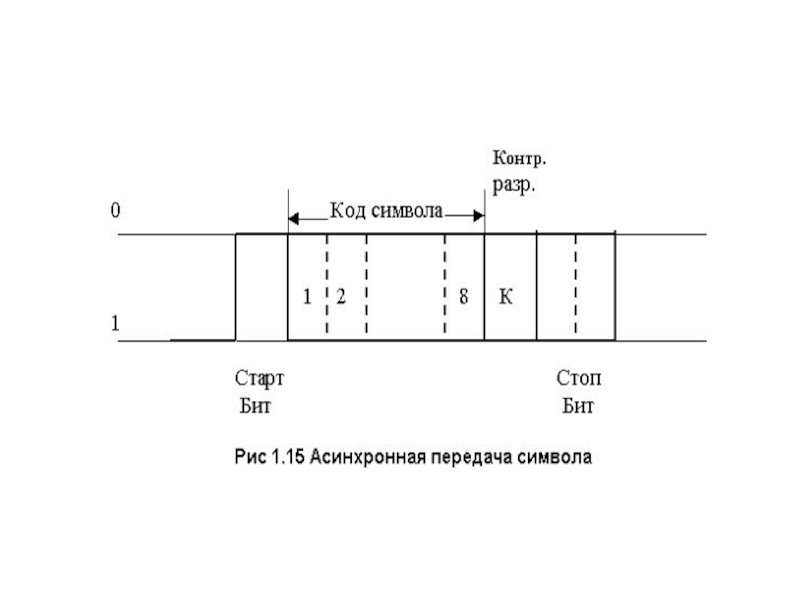

- 60. Синхронный протокол

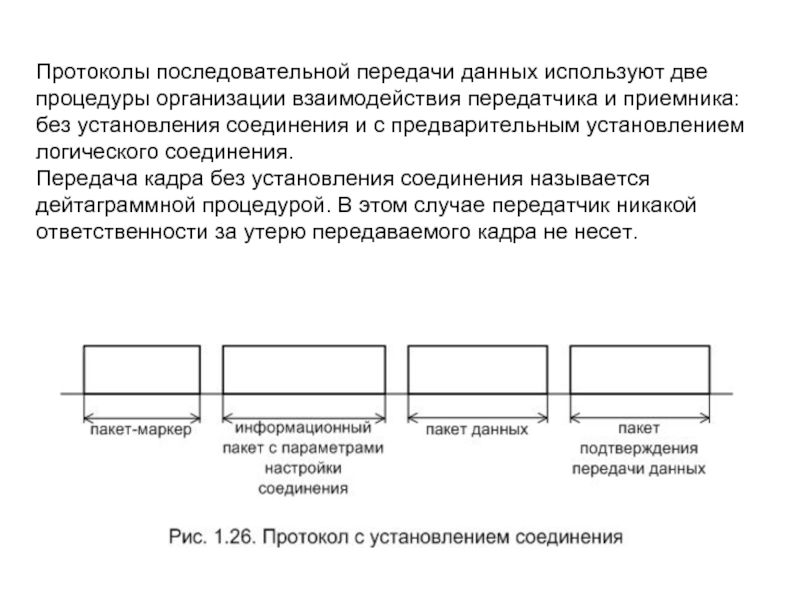

- 61. Протоколы последовательной передачи данных используют две процедуры

- 63. Парллельный интерфейс

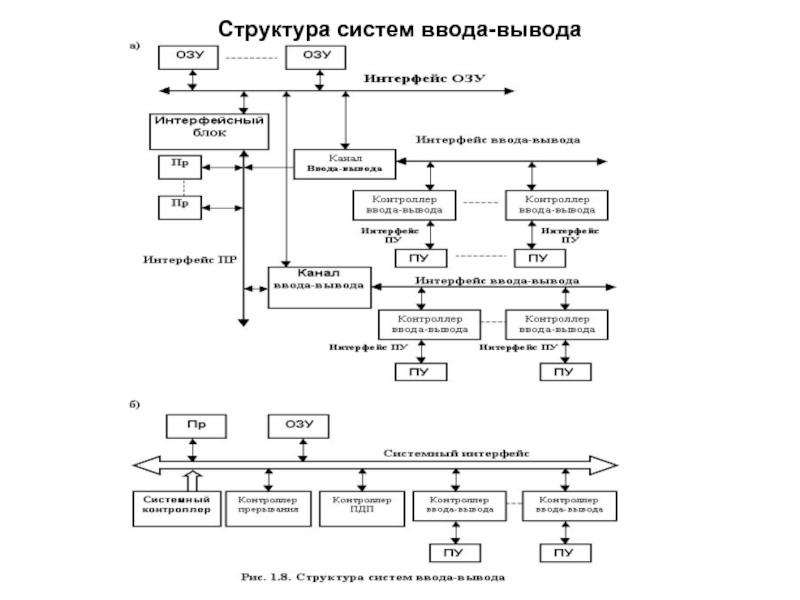

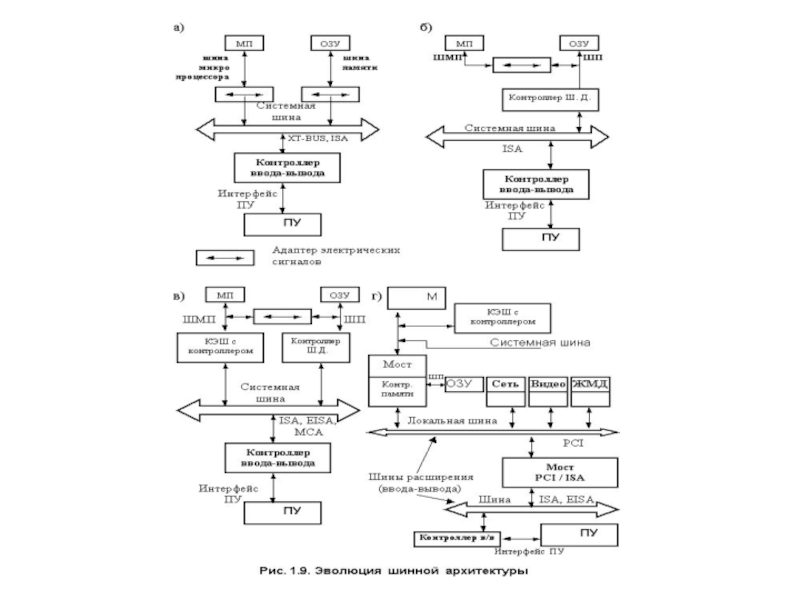

- 64. Структура систем ввода-вывода

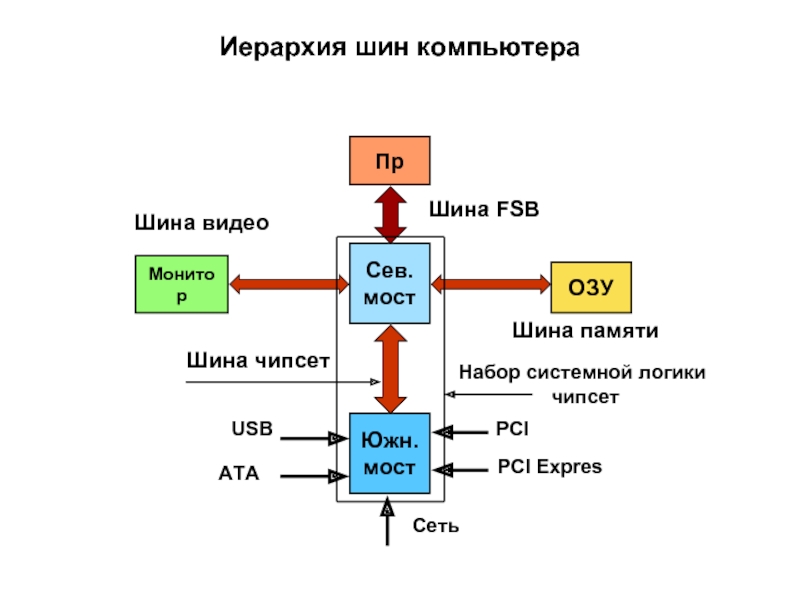

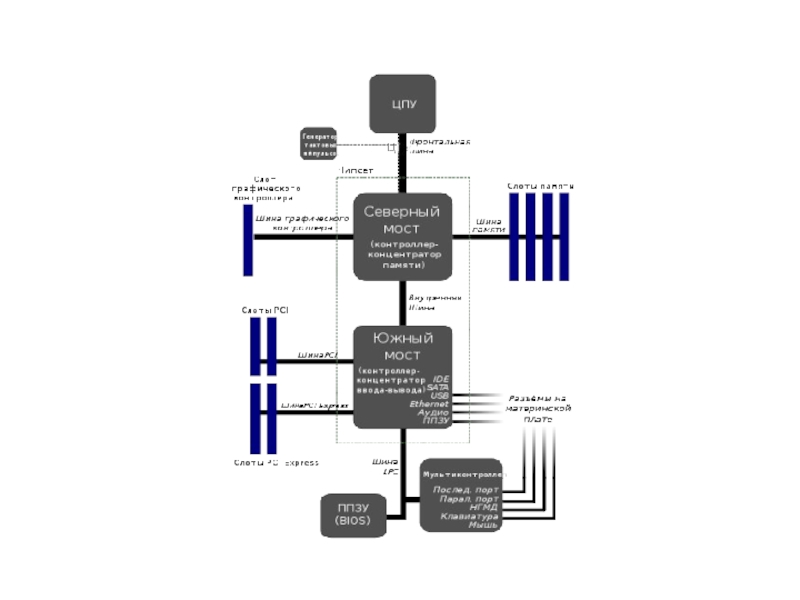

- 68. Иерархия шин компьютера Пр Сев. мост Южн.

- 70. Системные интерфейсы, шины расширения ТЕМА 1.3

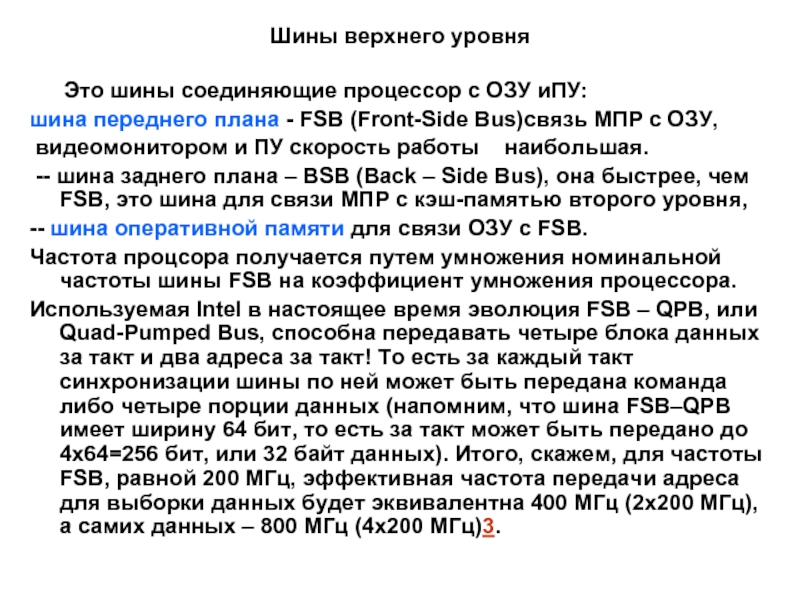

- 71. Шины верхнего уровня

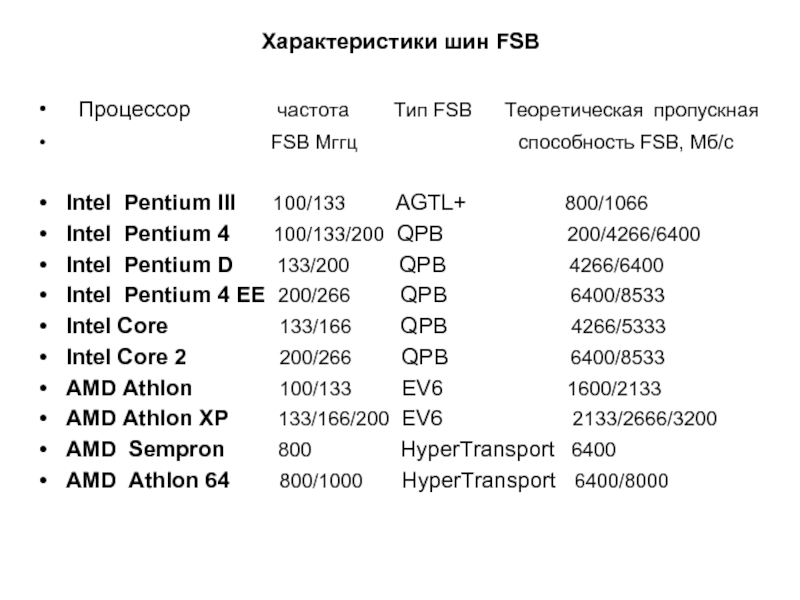

- 72. Характеристики шин FSB Процессор

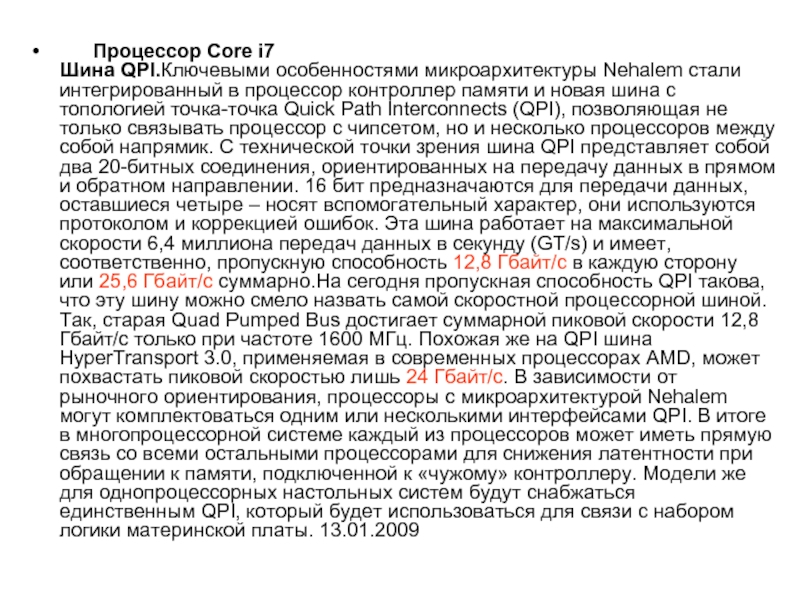

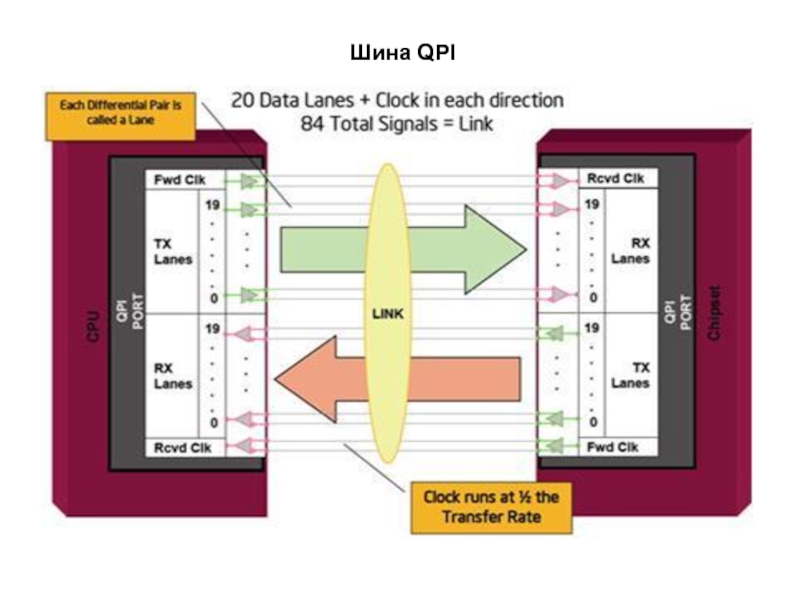

- 73. Процессор Core i7

- 74. Шина QPI

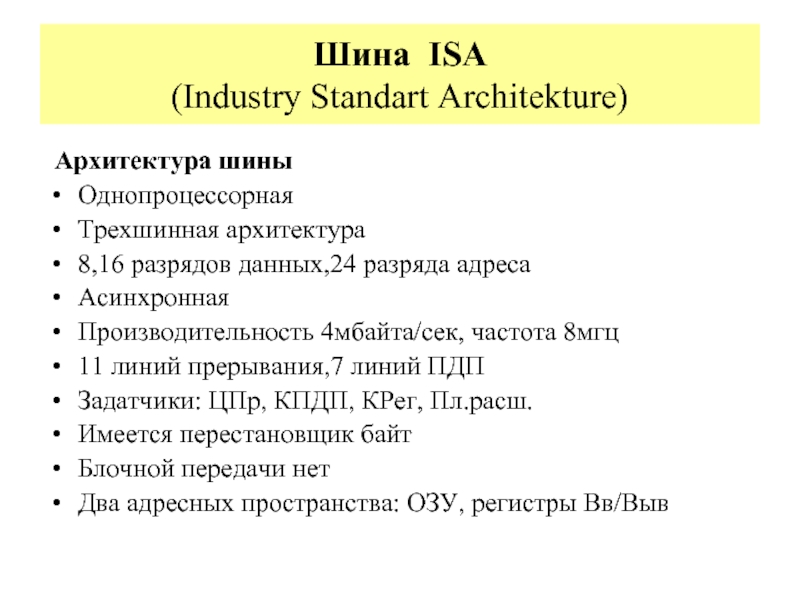

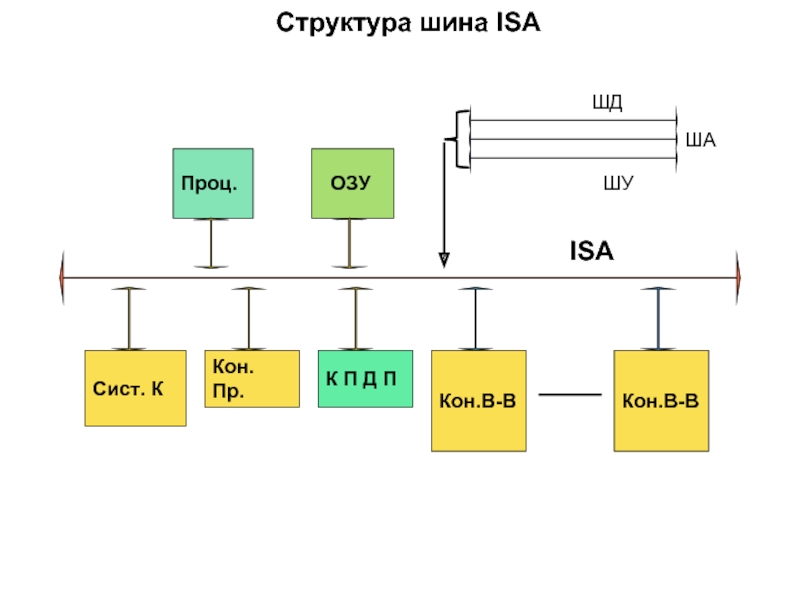

- 75. Шина ISA (Industry Standart Architekture)

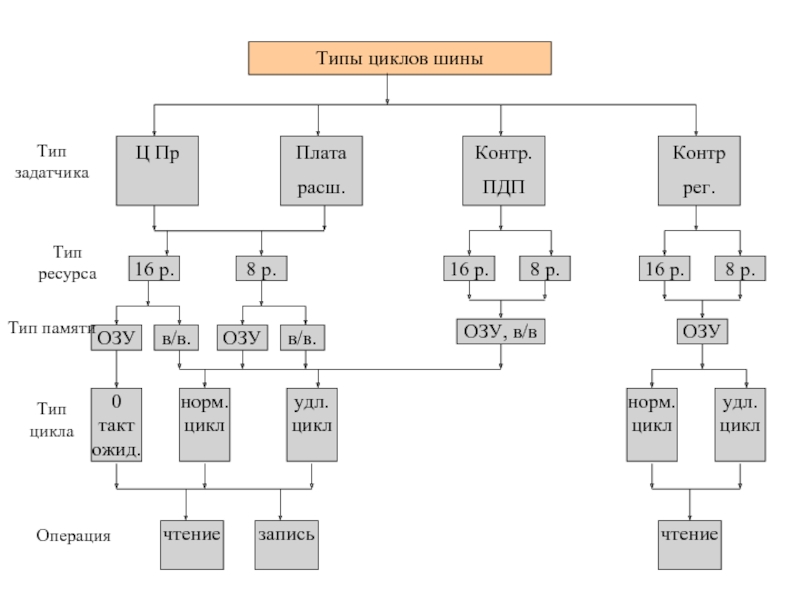

- 77. Типы циклов шины Ц Пр

- 78. Сигналы шины ISA Сигналы адреса и

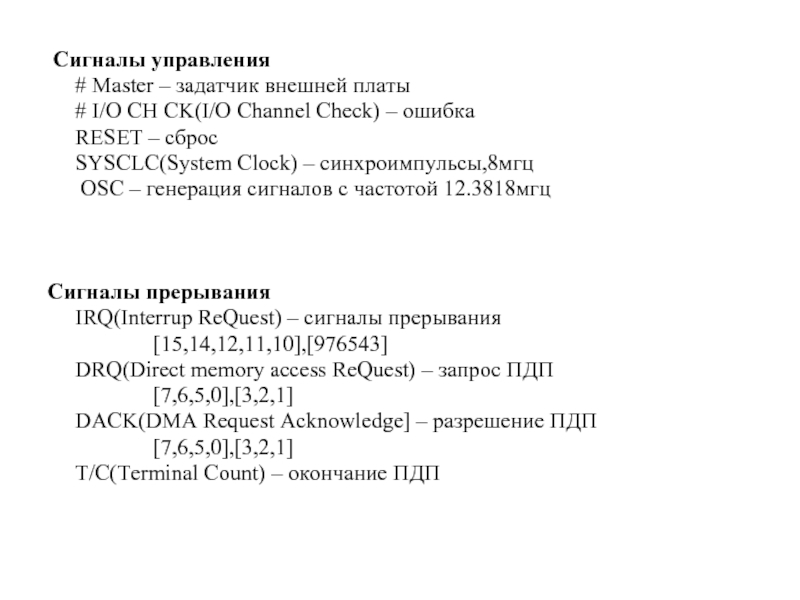

- 79. Сигналы управления #

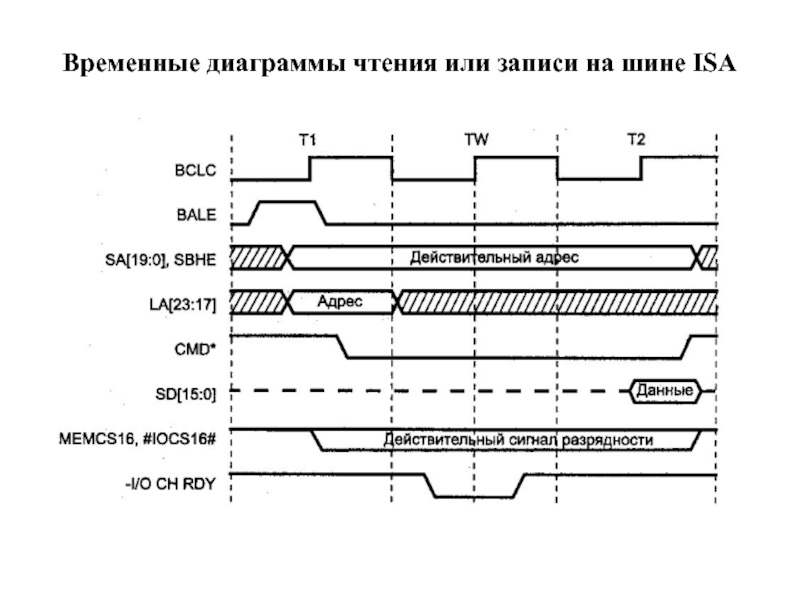

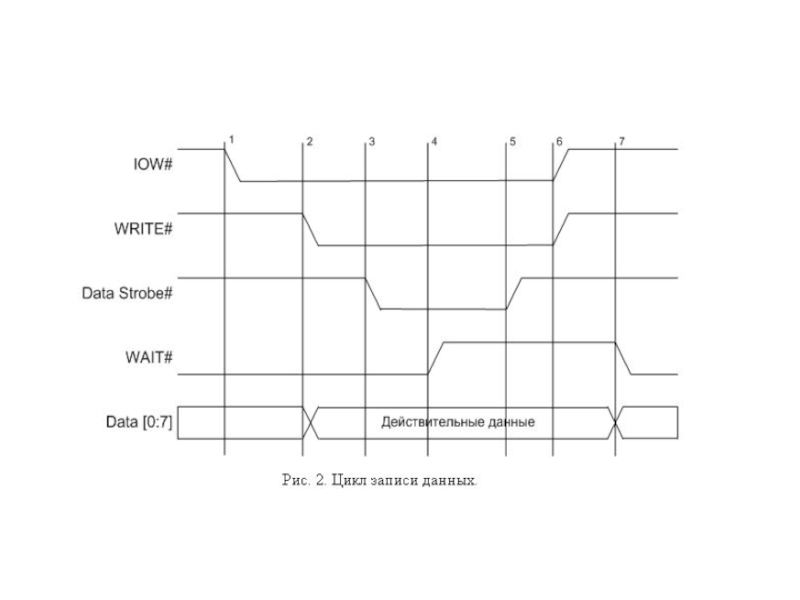

- 81. Временные диаграммы чтения или записи на шине ISA

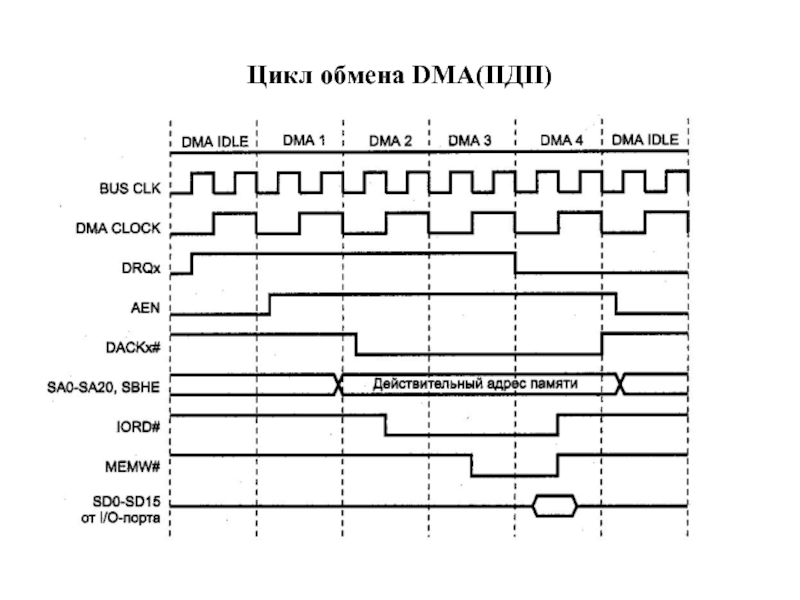

- 82. Цикл обмена DMA(ПДП)

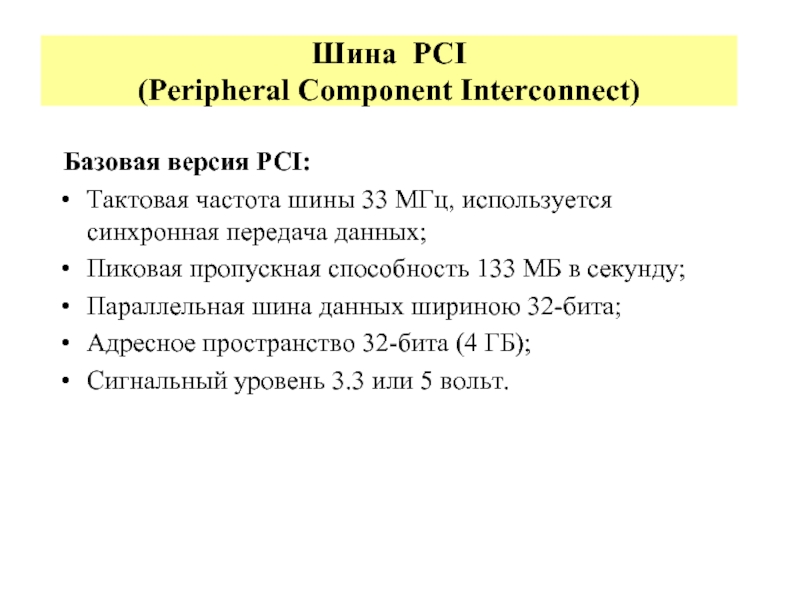

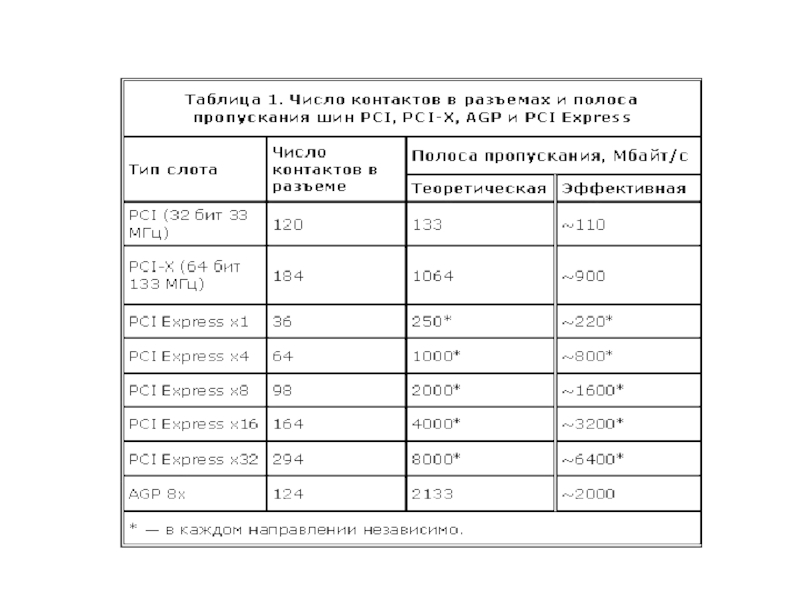

- 83. Шина PCI (Peripheral Component Interconnect) Базовая

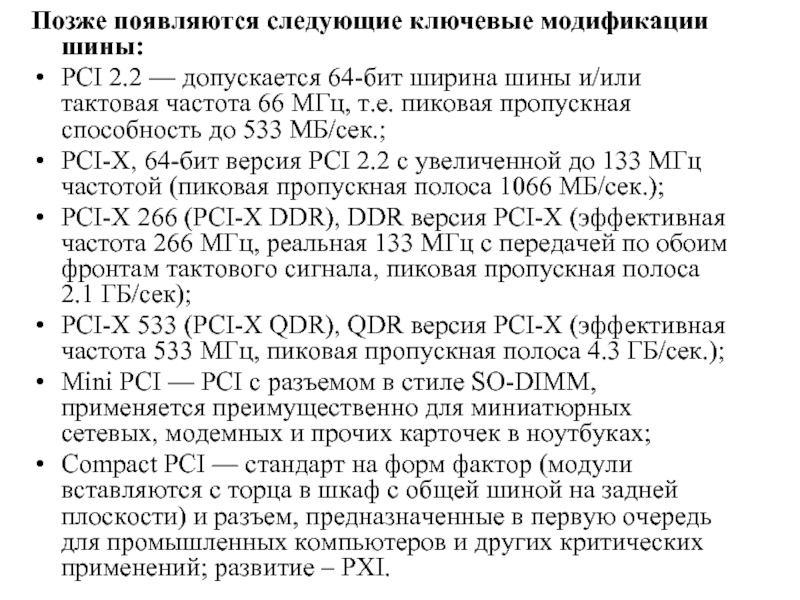

- 84. Позже появляются следующие ключевые модификации шины: PCI

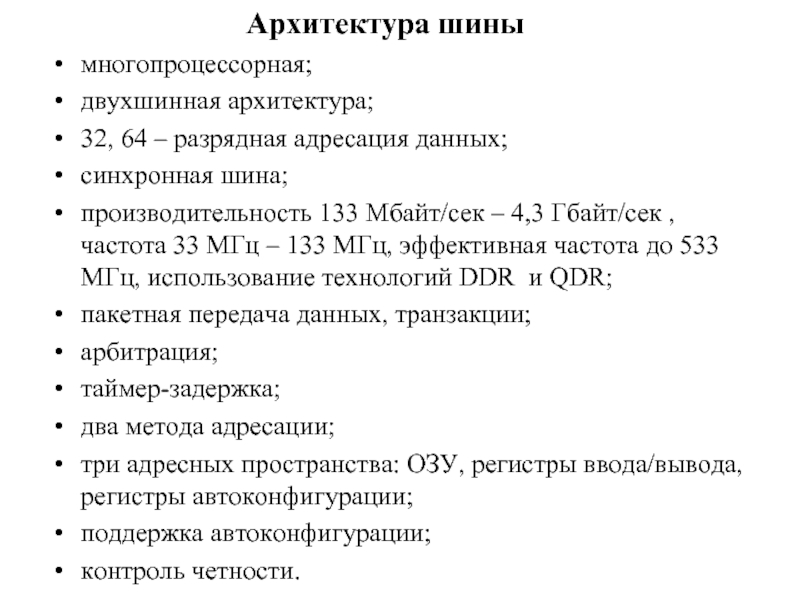

- 85. многопроцессорная; двухшинная архитектура; 32, 64 – разрядная

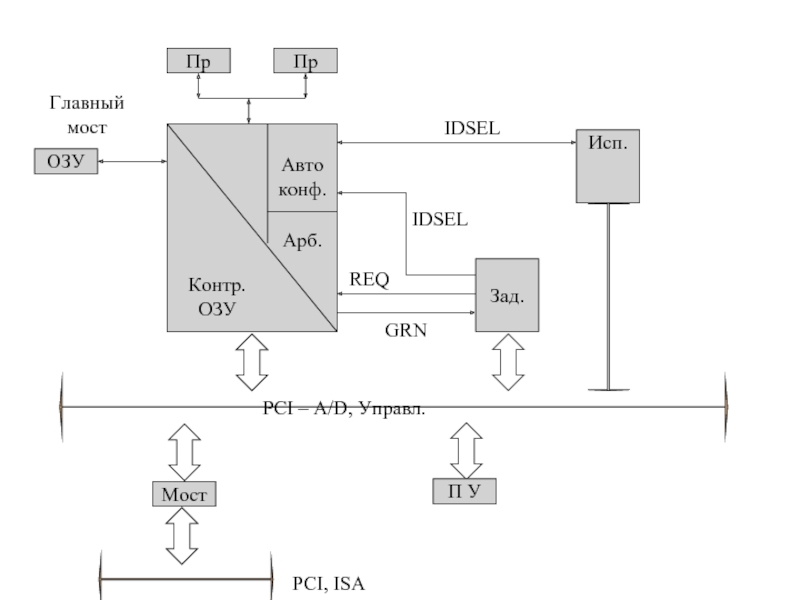

- 86. Пр Пр ОЗУ Контр. ОЗУ

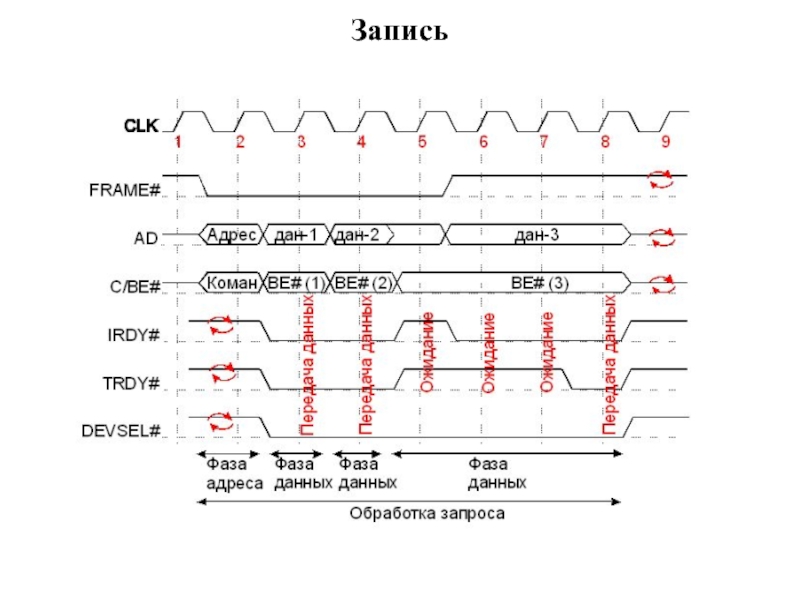

- 87. Базовые сигналы шины PCI AD[31-0] – адрес

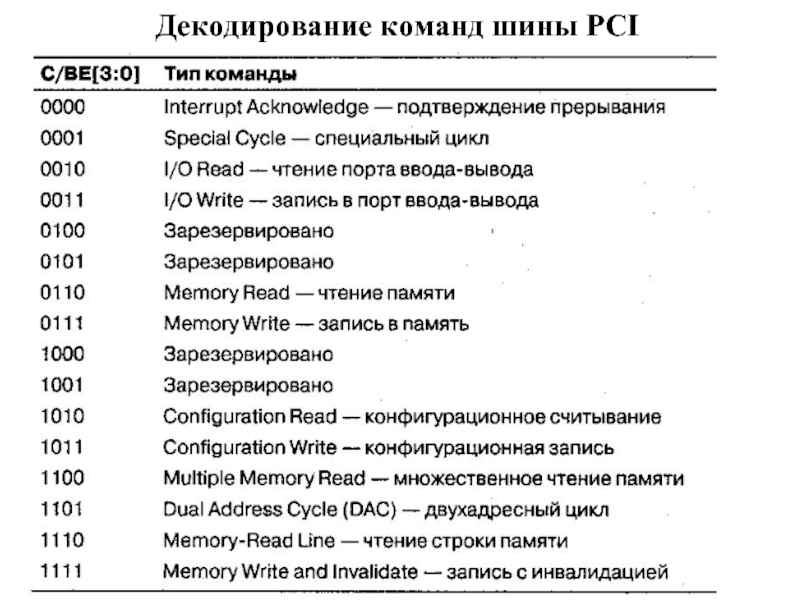

- 88. Декодирование команд шины PCI

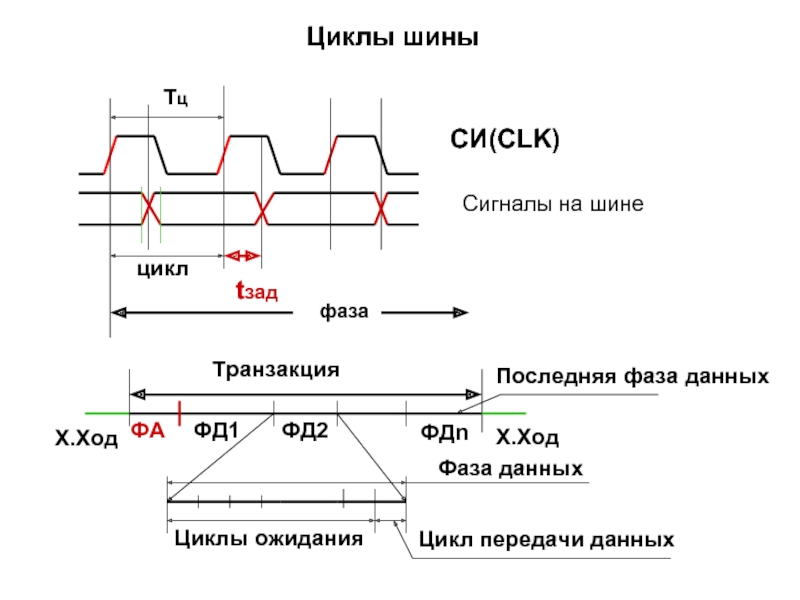

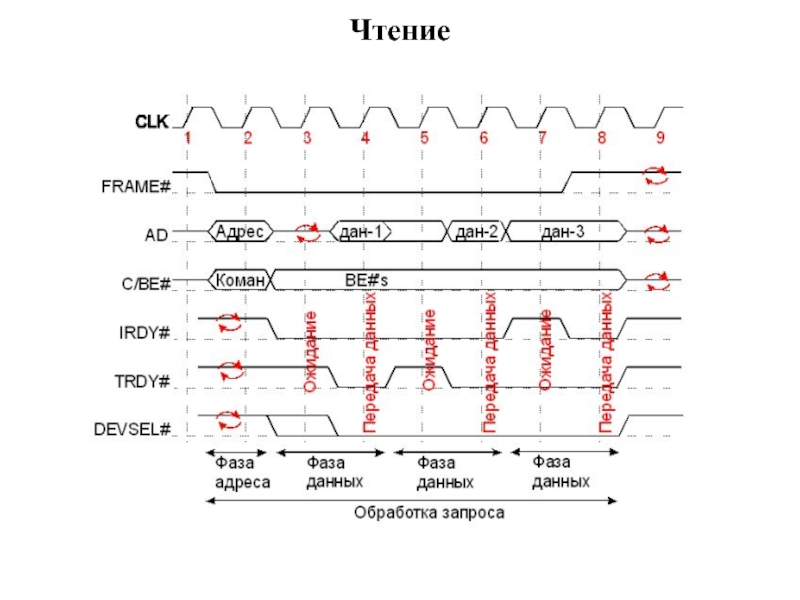

- 90. Чтение

- 91. Запись

- 92. Арбитрация

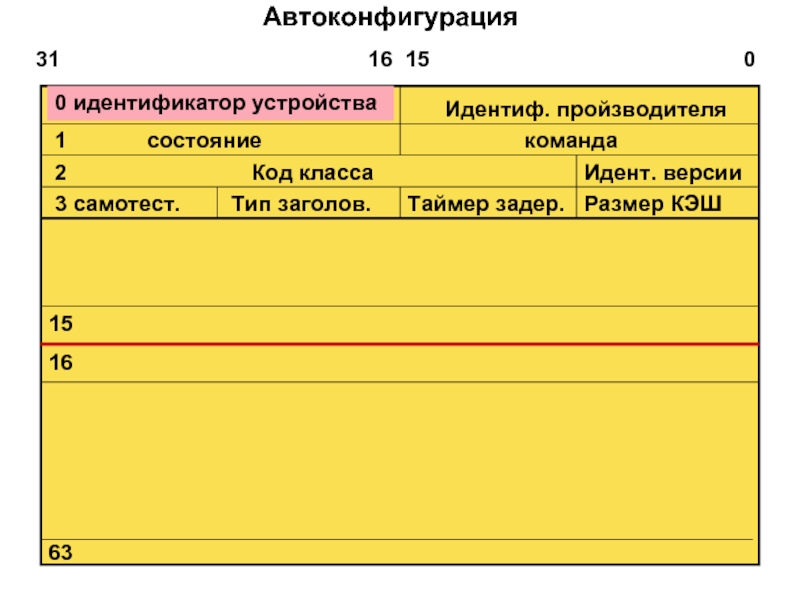

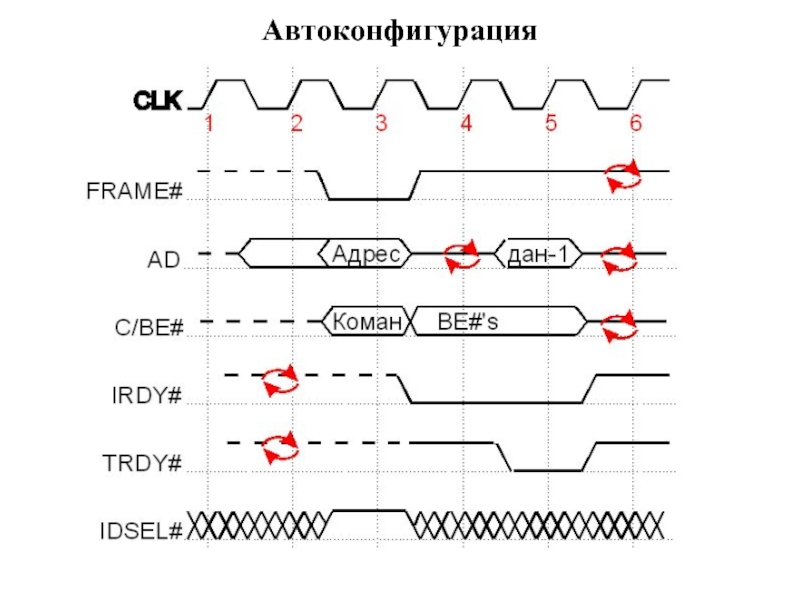

- 95. Автоконфигурация

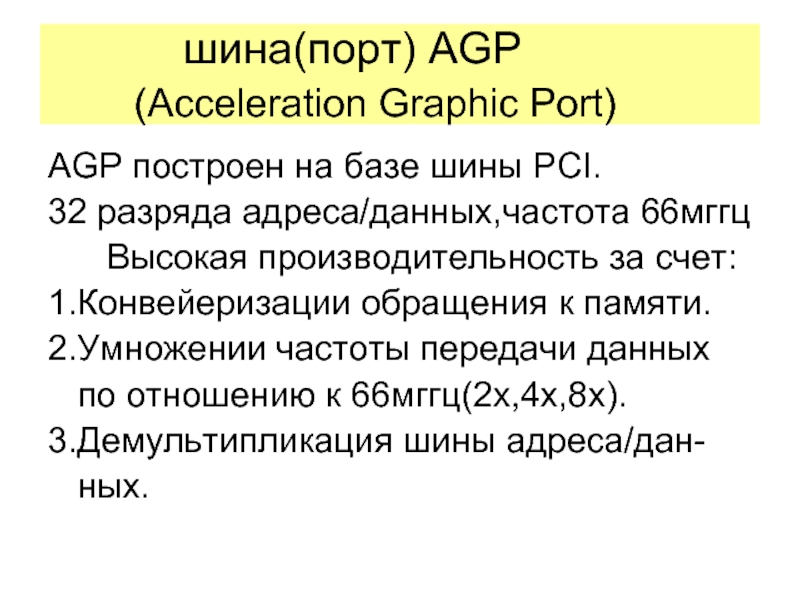

- 96. шина(порт)

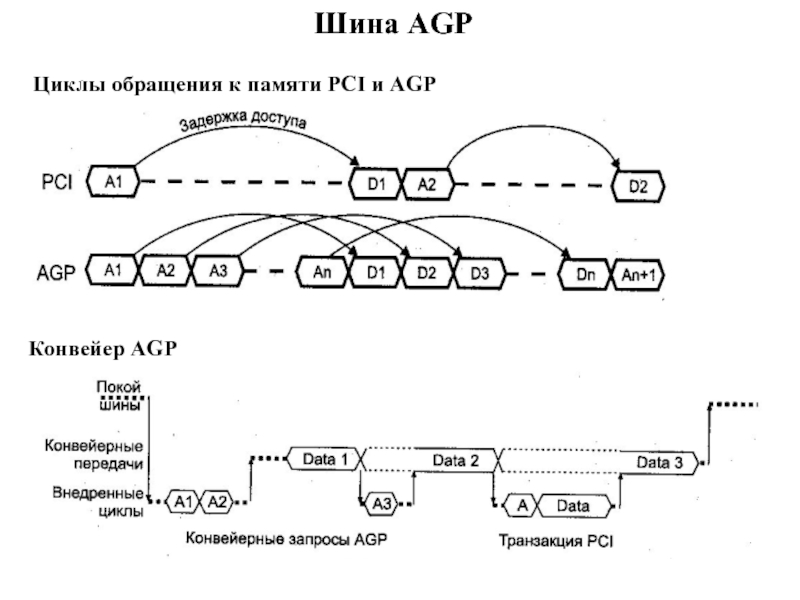

- 97. Шина AGP Циклы обращения к памяти PCI и AGP Конвейер AGP

- 98. Производительность шины AGP1х-266мбайт/сек

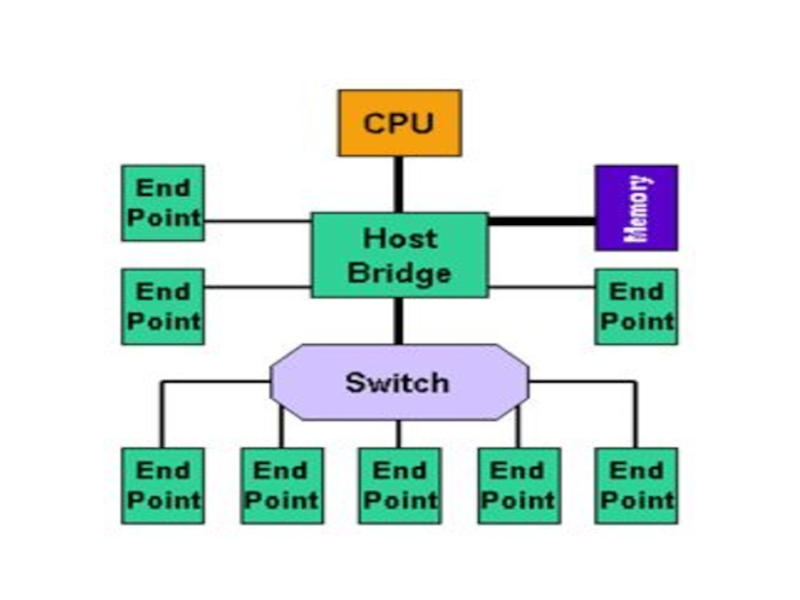

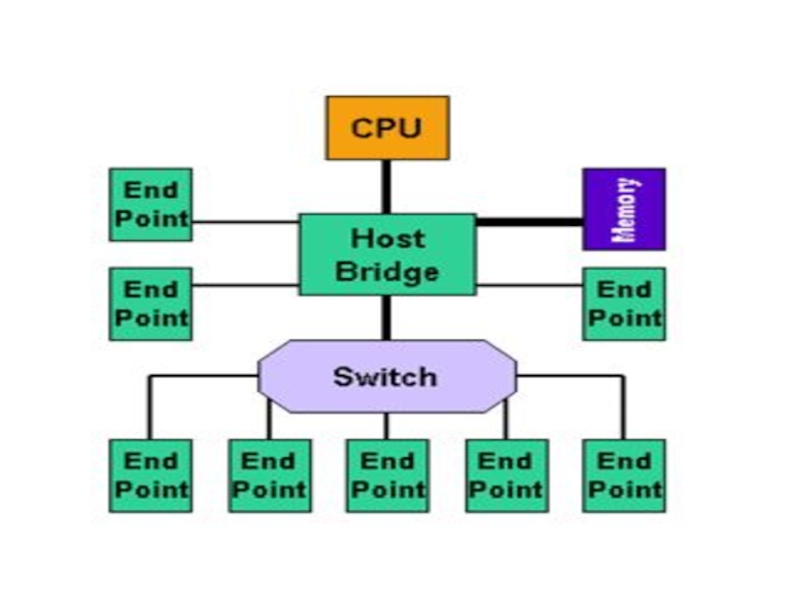

- 99. PCI Express, на стадии проектирования была также

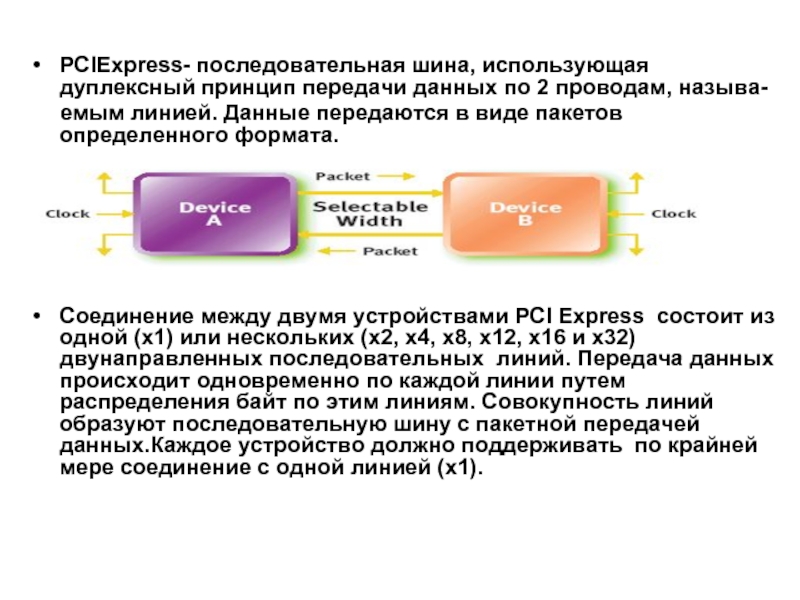

- 100. PCIExpress- последовательная шина, использующая дуплексный принцип

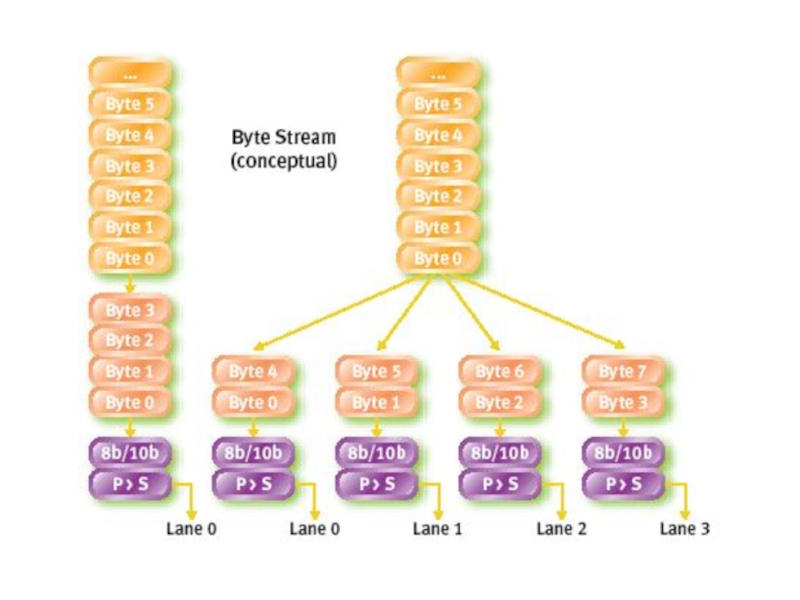

- 102. Каждый байт (8 бит) данных, по определенной

- 103. PCI Express относится к шинам класса

- 104. Вся контрольная информация передается по тем же

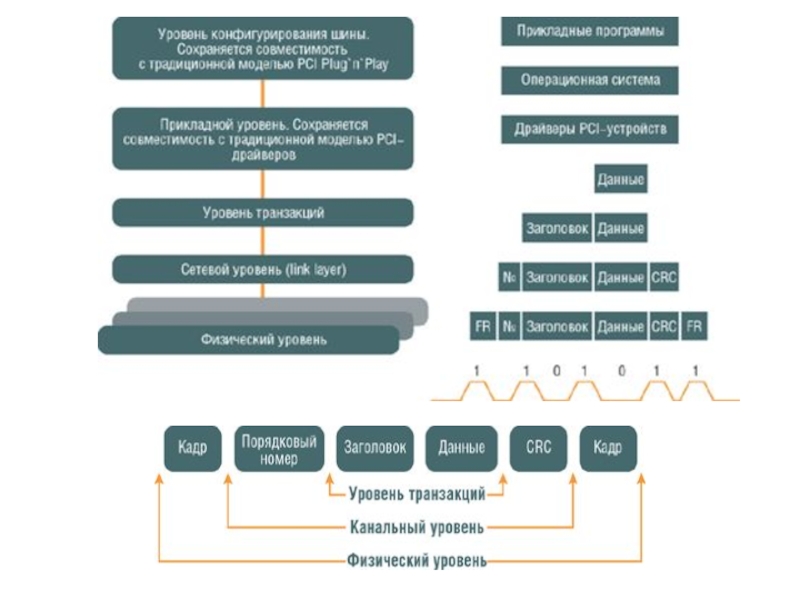

- 106. Многоуровневая модель шины PCIe PCI Express

- 108. Спуск еще на уровень по схеме

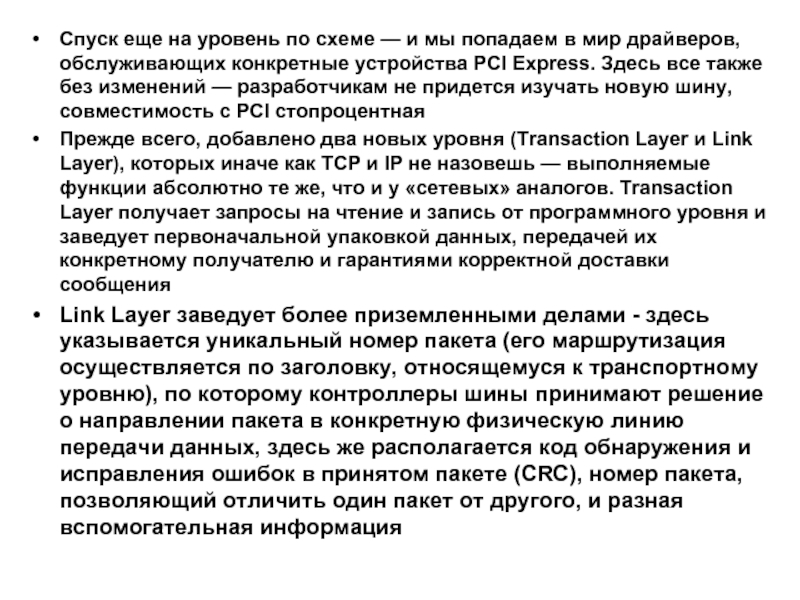

- 109. Frame — начальный и конечный

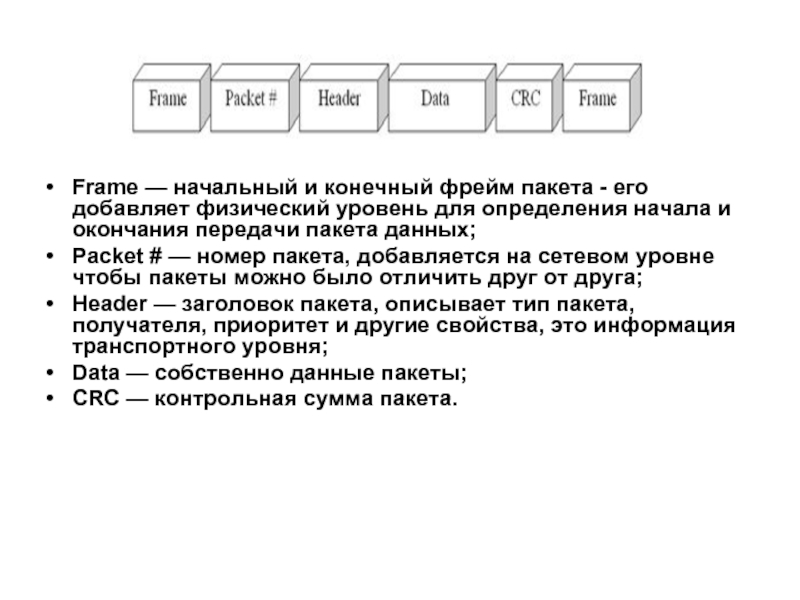

- 110. Fmt — указание типа заголовка (12 или

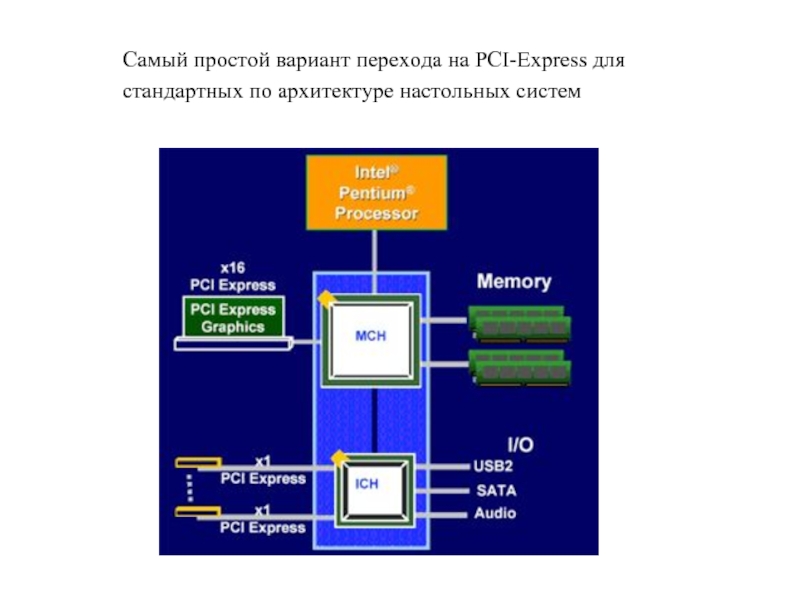

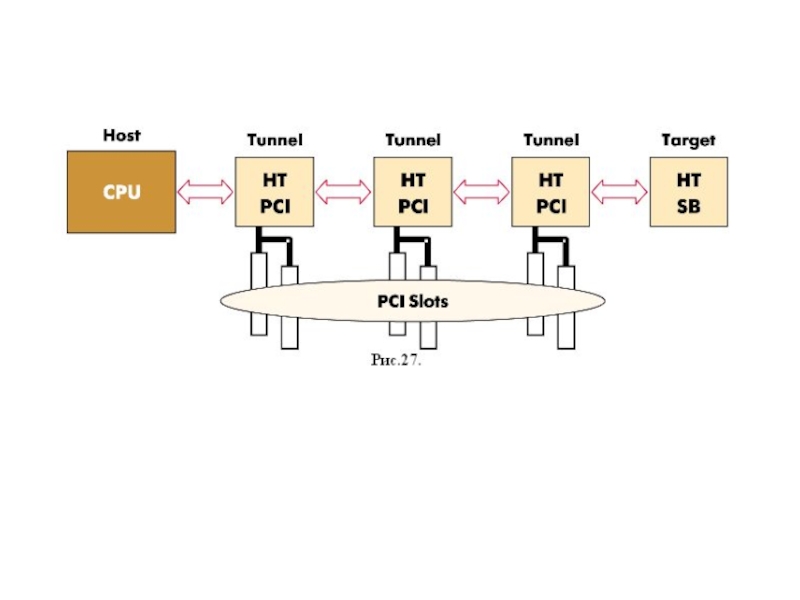

- 112. Самый простой вариант перехода на PCI-Express для стандартных по архитектуре настольных систем

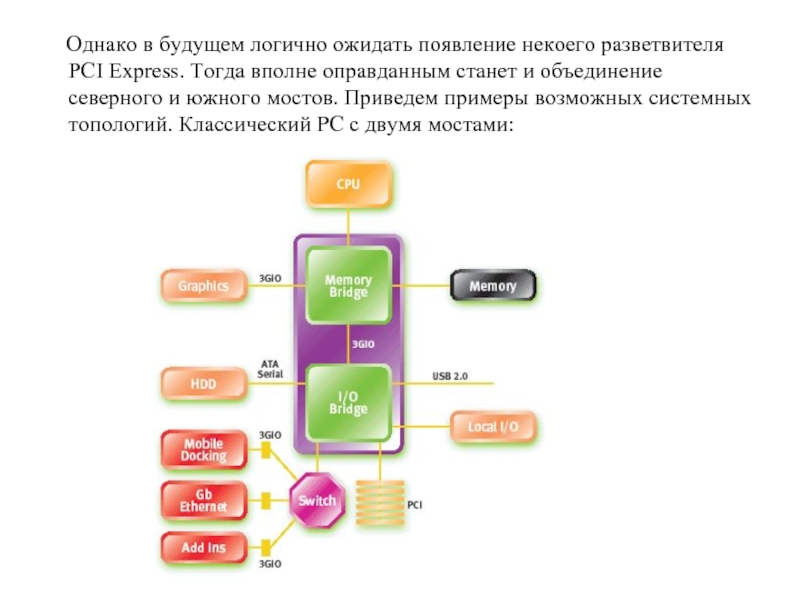

- 113. Однако в будущем логично

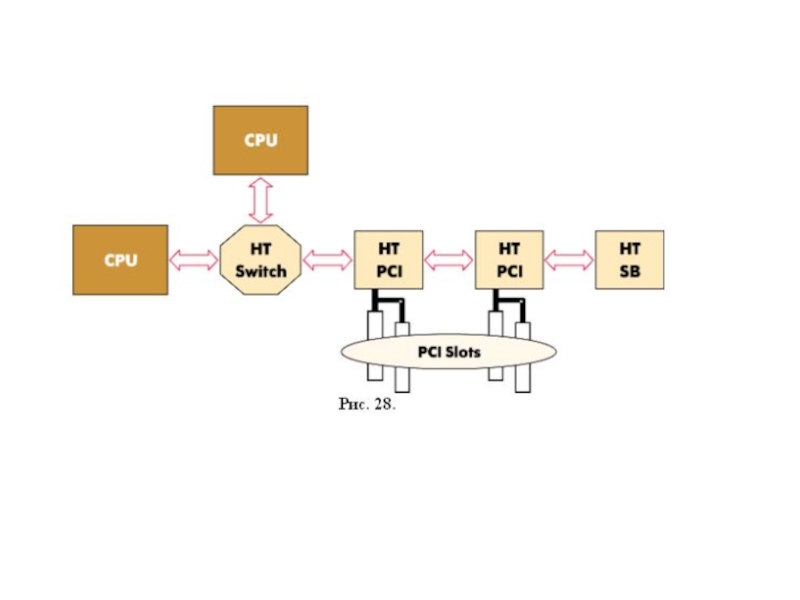

- 114. Более обобщенная (серверная) архитектура с одним мостом:

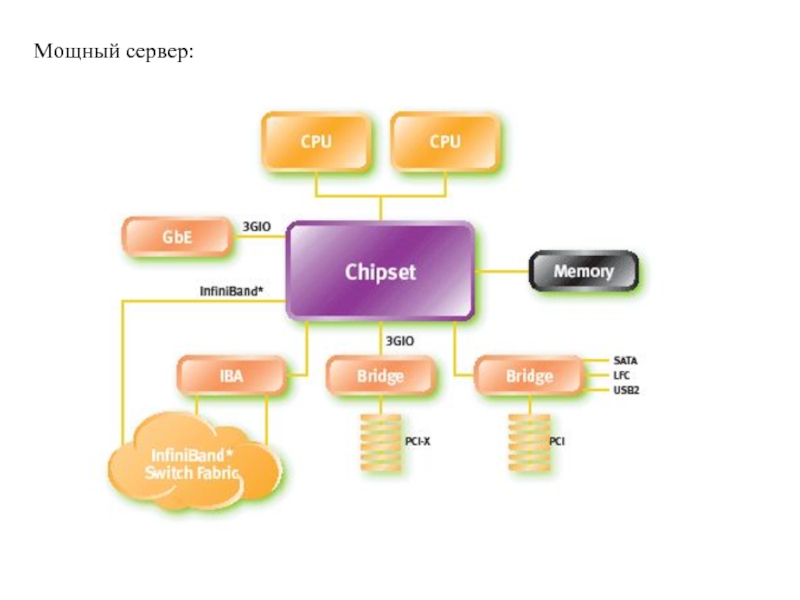

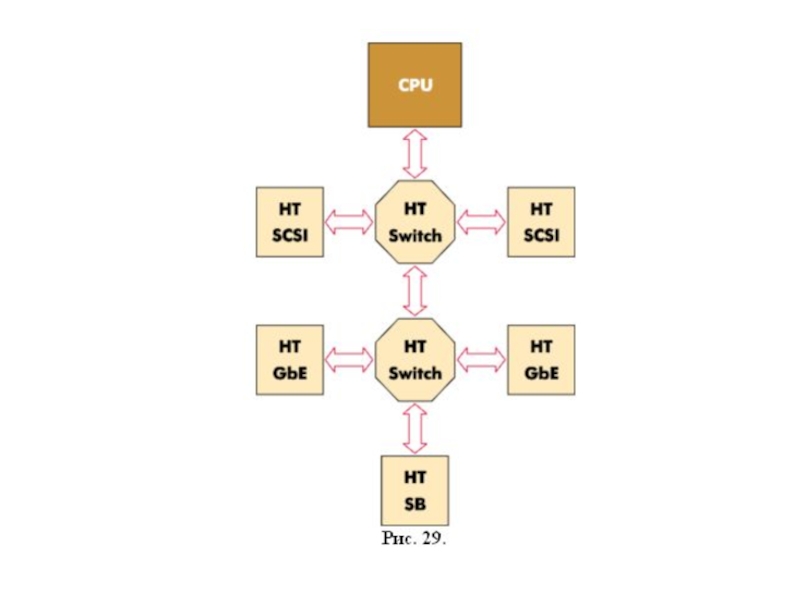

- 115. Мощный сервер:

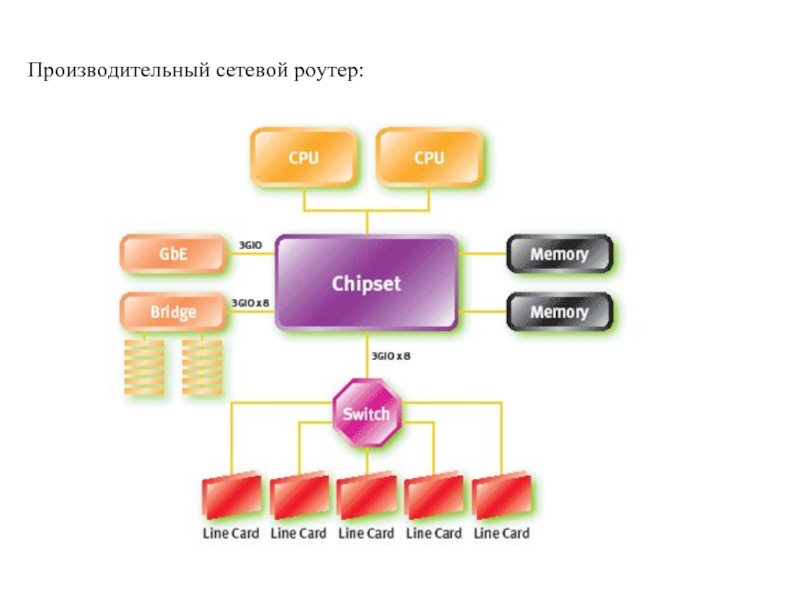

- 116. Производительный сетевой роутер:

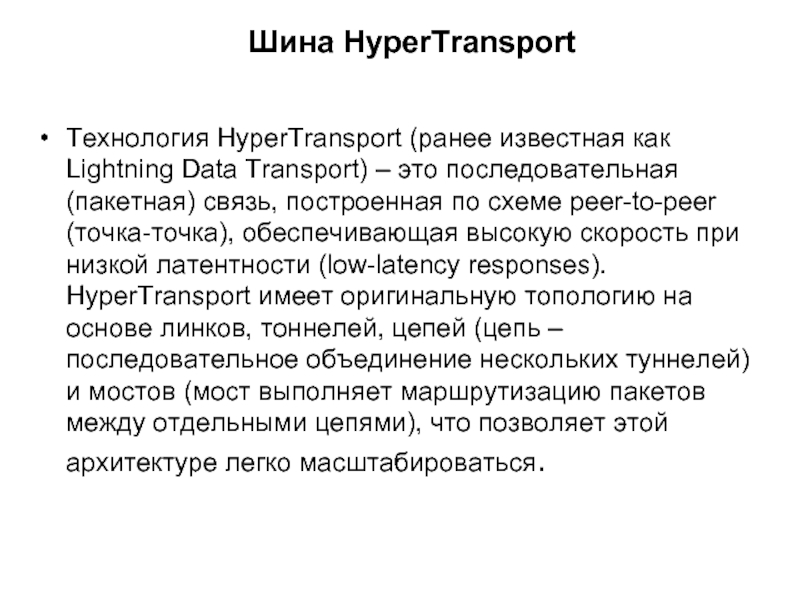

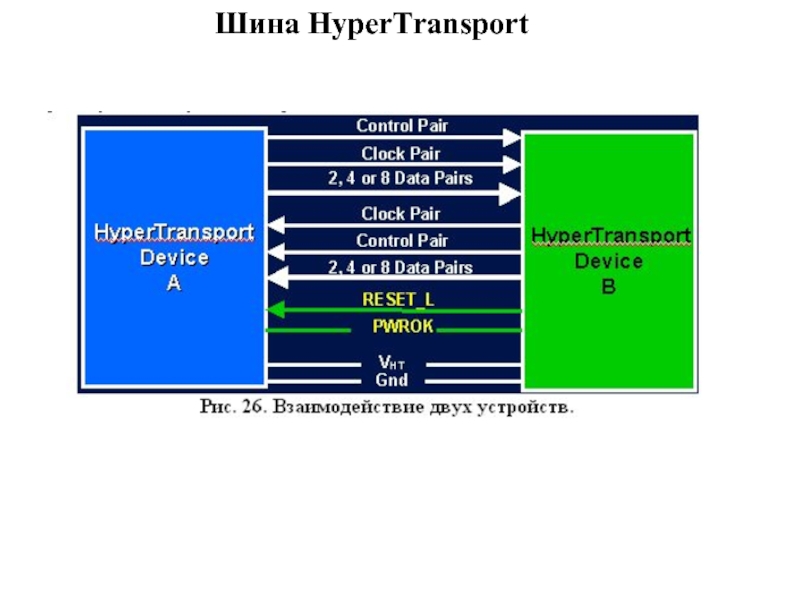

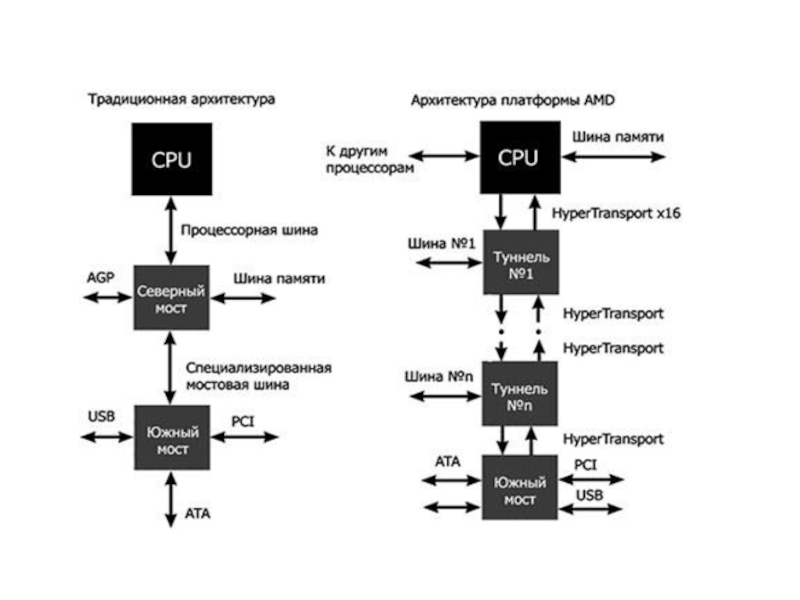

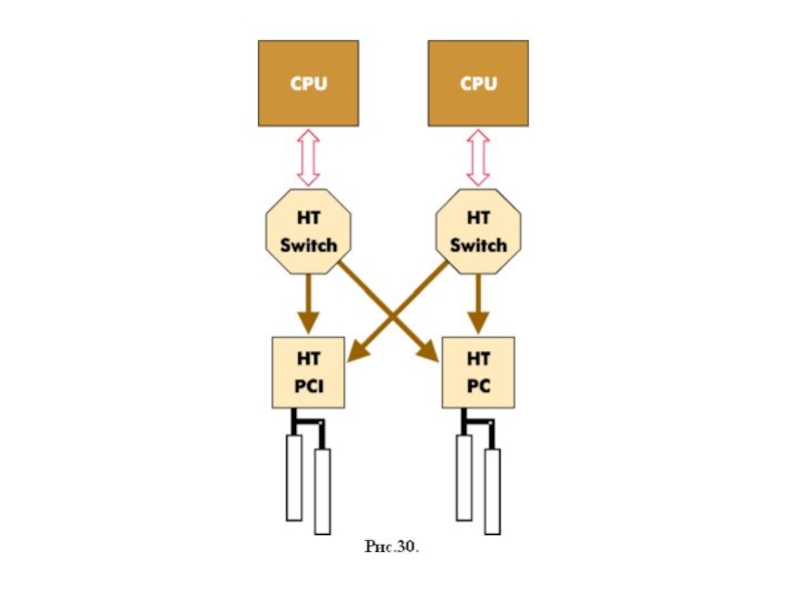

- 117. Шина HyperTransport Технология HyperTransport (ранее известная

- 118. Шина HyperTransport

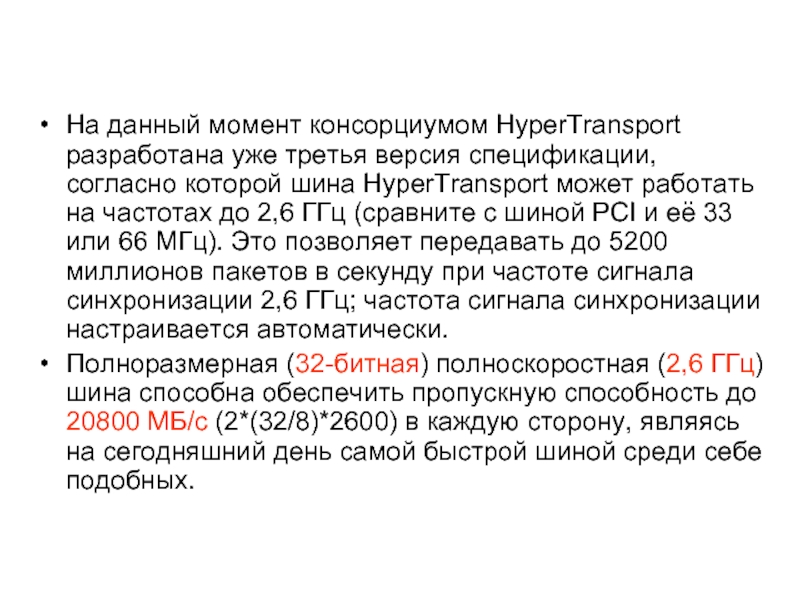

- 120. На данный момент консорциумом HyperTransport разработана

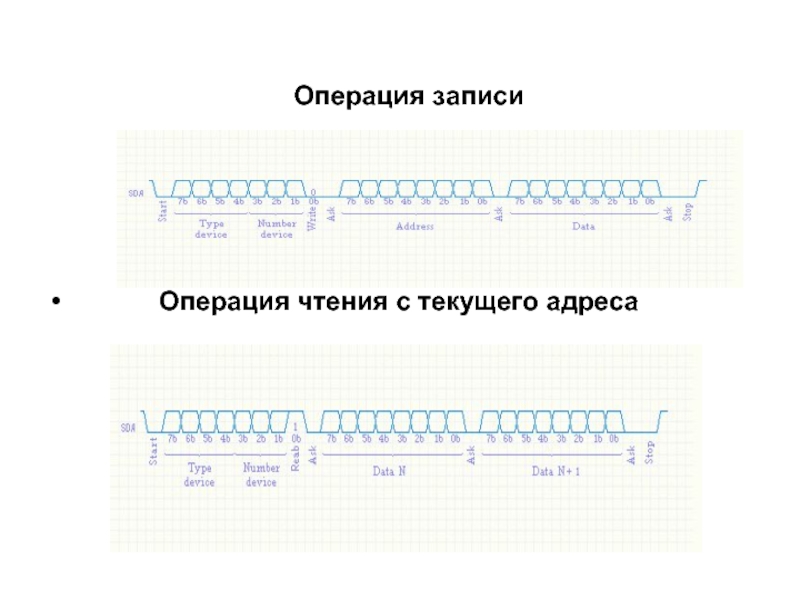

- 127. При помощи интерфейса I2C передача данных

- 128. Операция записи

- 129. Тема 1.4. Интерфейсы периферийных устройств (Centronics, RS232, SCSI, USB)

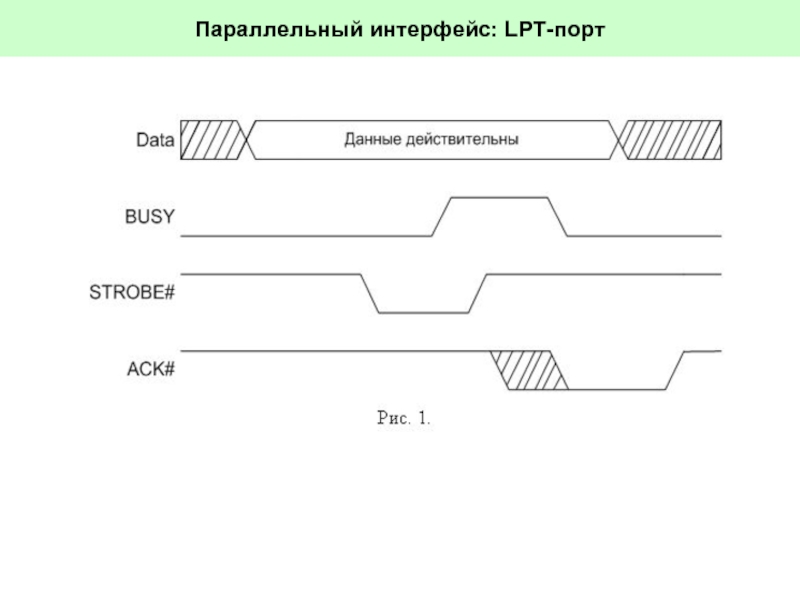

- 130. Параллельный интерфейс: LPT-порт

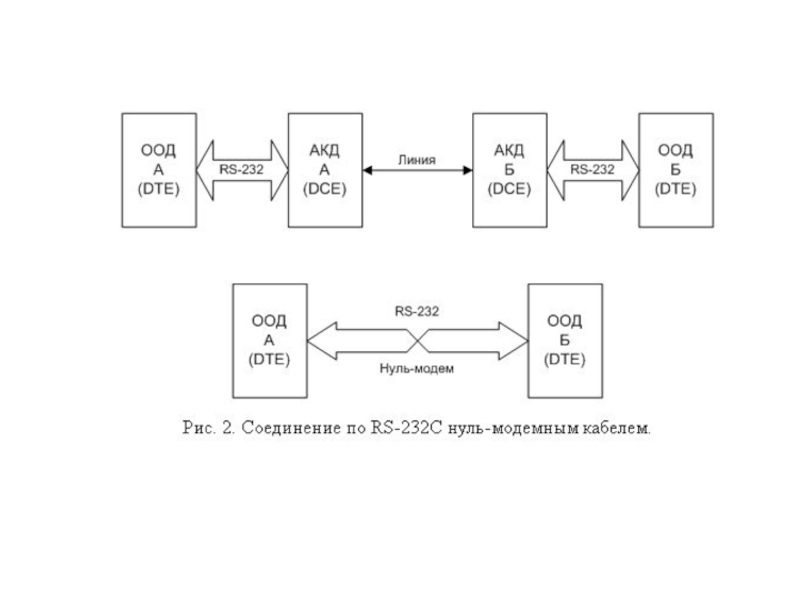

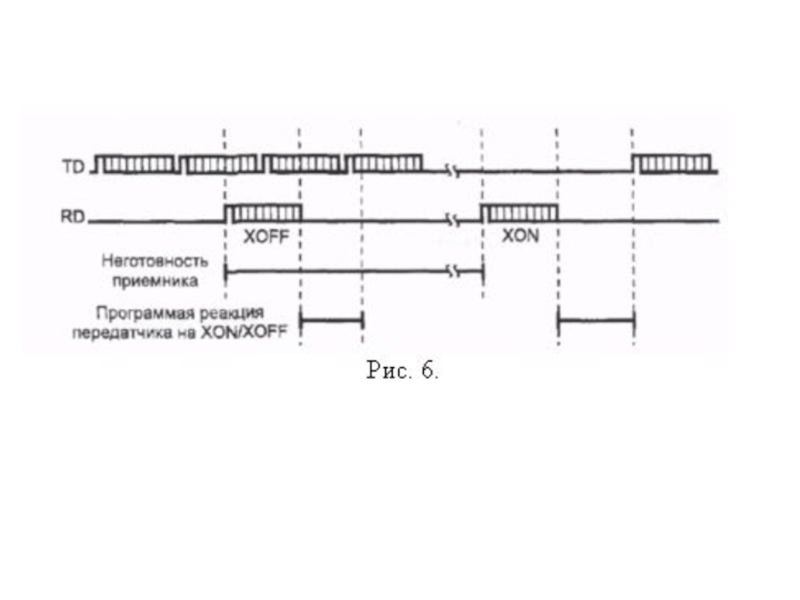

- 133. Последовательные интерфейсы: СОМ-порт

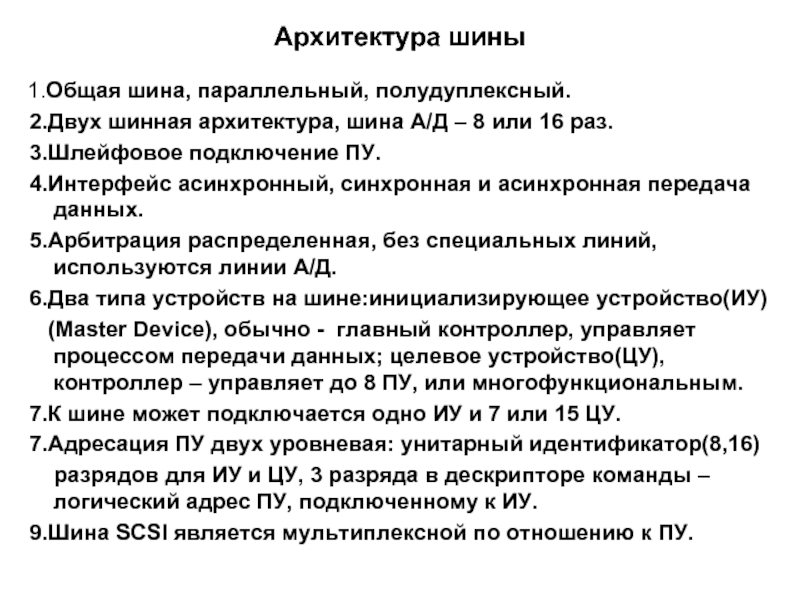

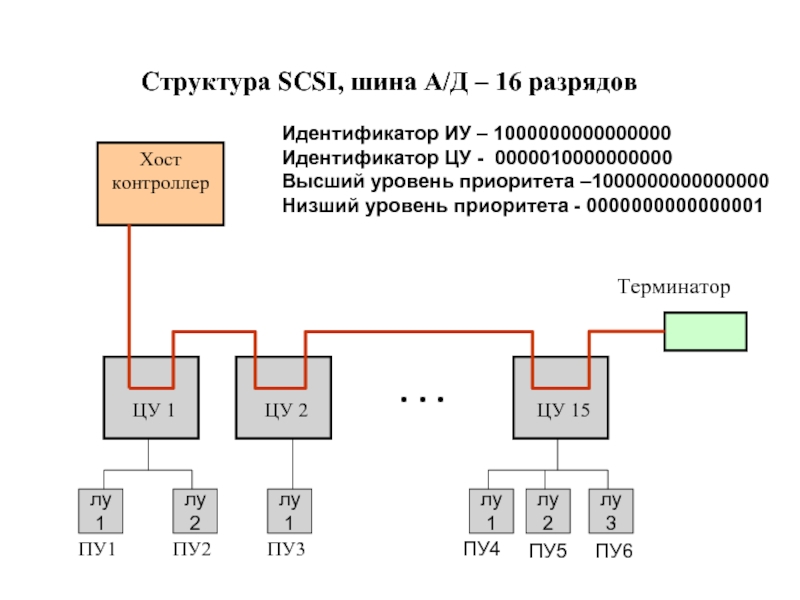

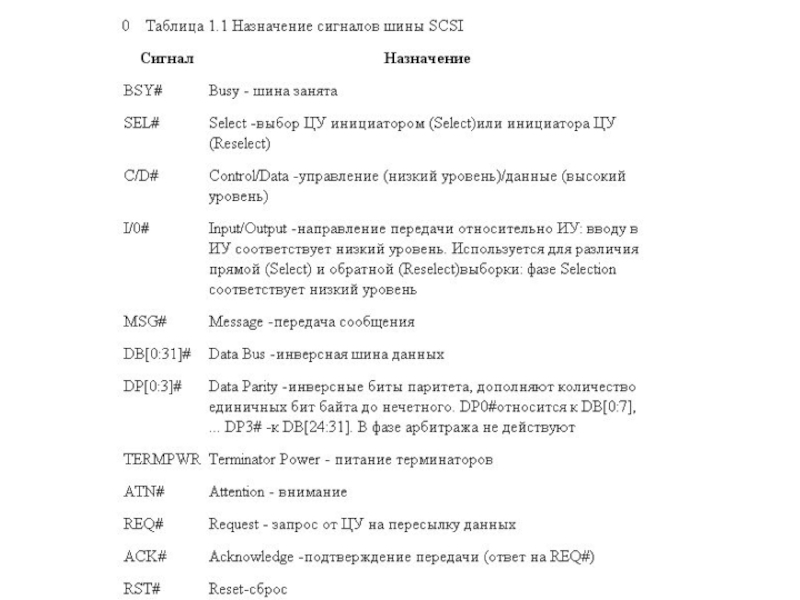

- 140. Архитектура шины 1.Общая шина, параллельный, полудуплексный.

- 141. Структура

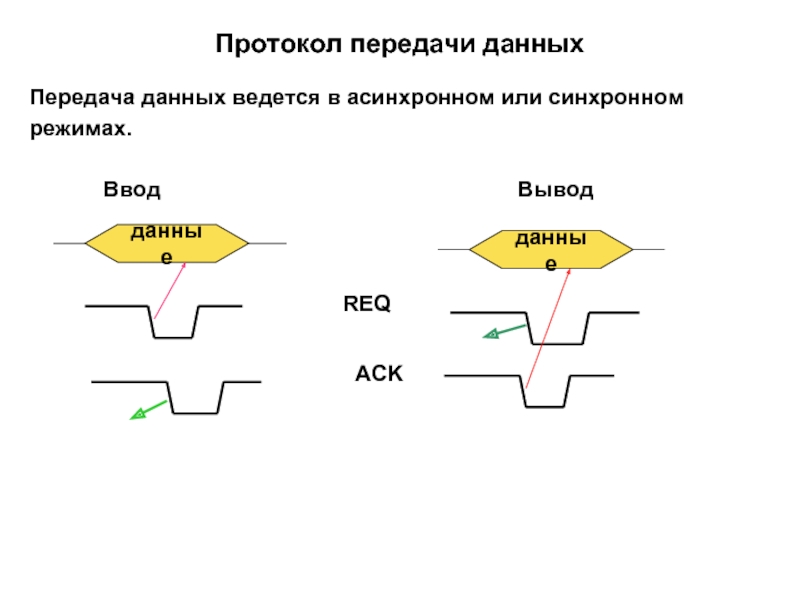

- 144. Протокол передачи данных Передача данных ведется в

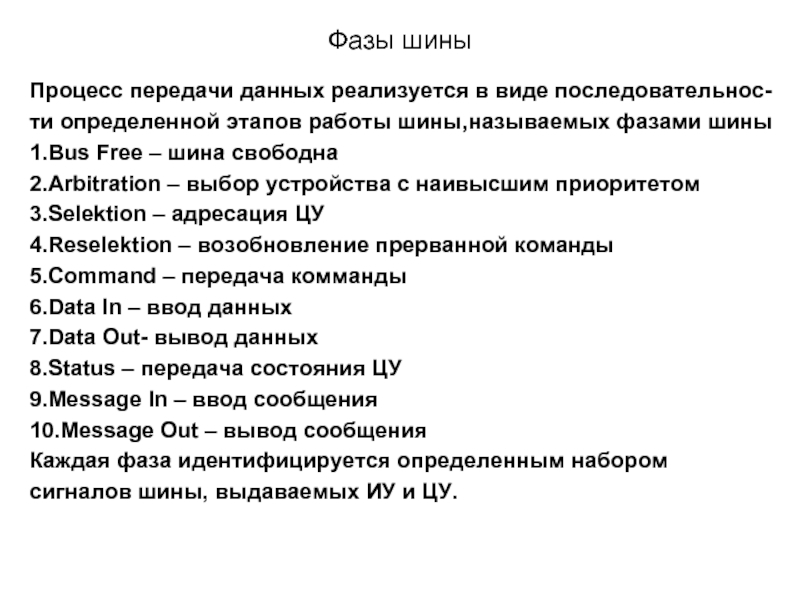

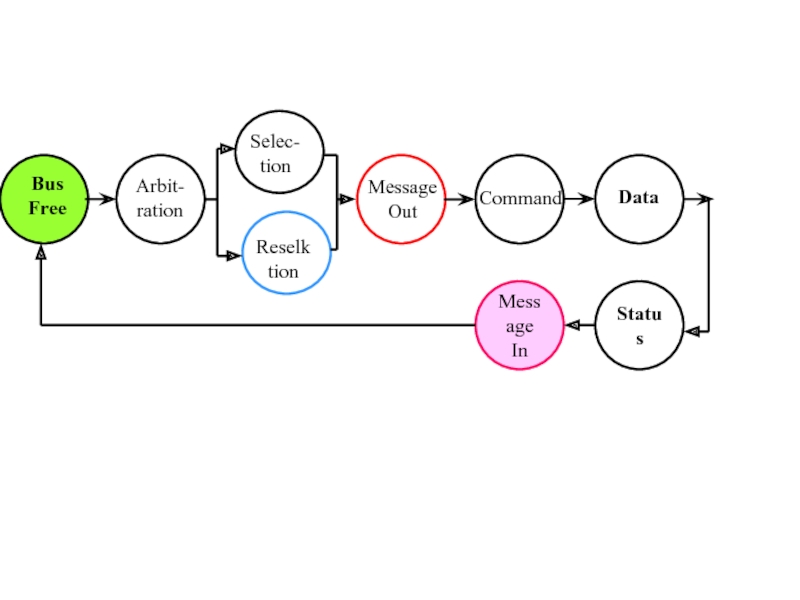

- 145. Фазы шины Процесс передачи данных реализуется в

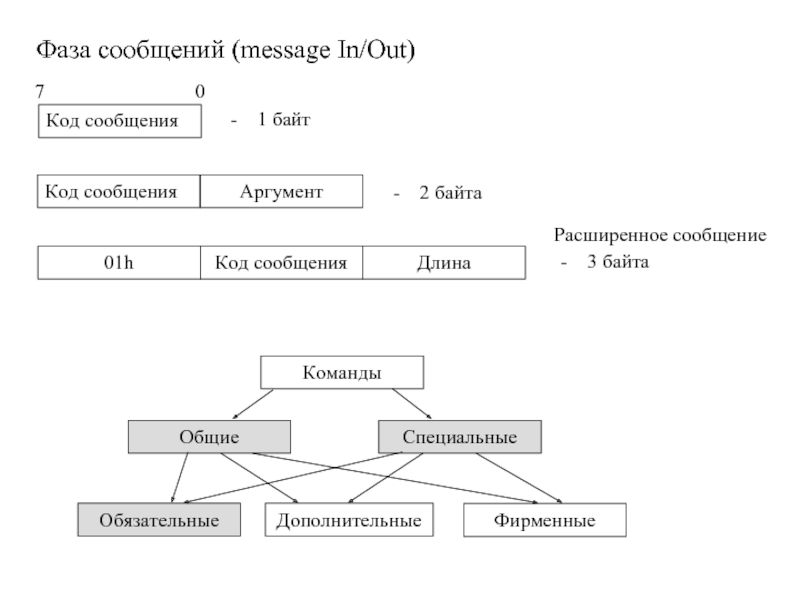

- 148. Фаза сообщений (message In/Out) Код сообщения -

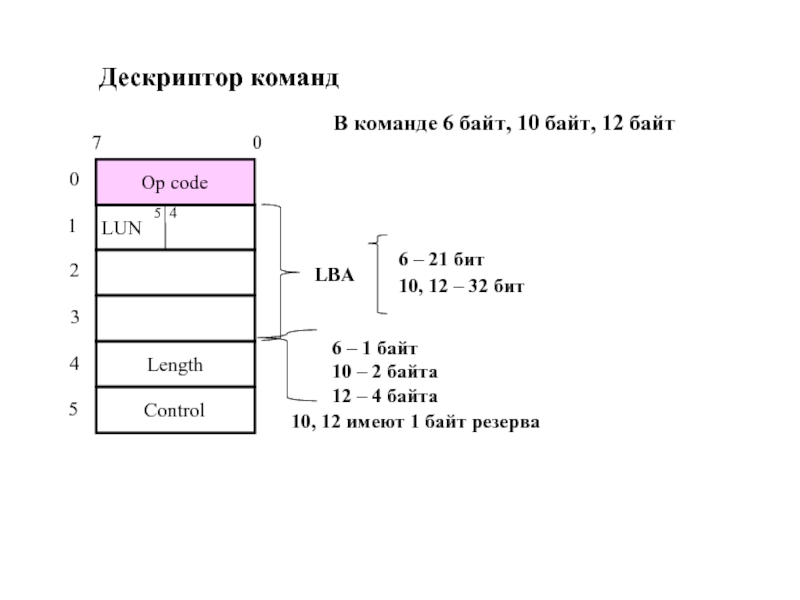

- 149. Дескриптор команд Op code 7 0

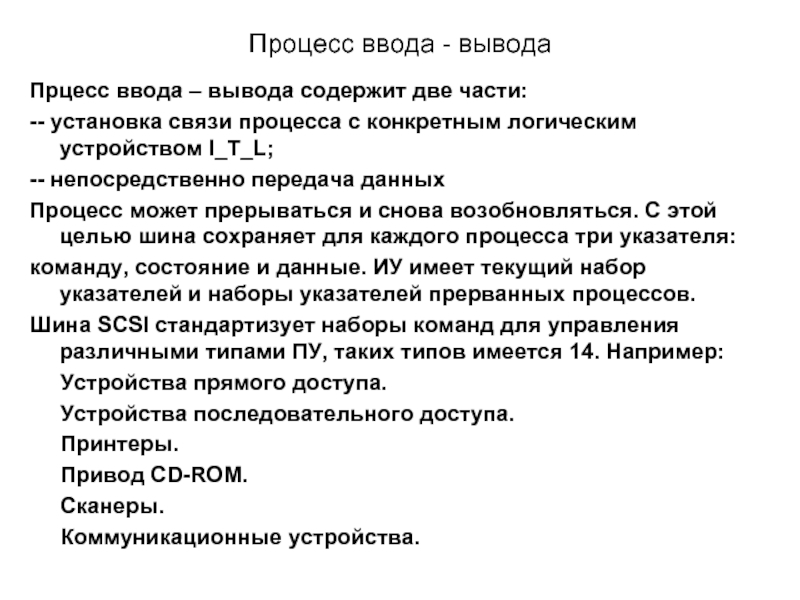

- 150. Процесс ввода - вывода Прцесс ввода –

- 151. Шина USB (Universal Systems Interface)

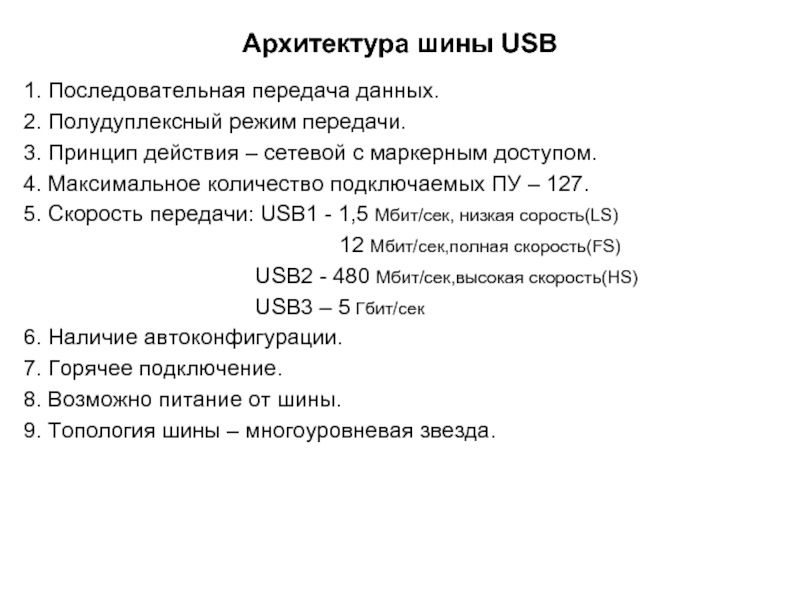

- 152. Архитектура шины USB 1. Последовательная передача данных.

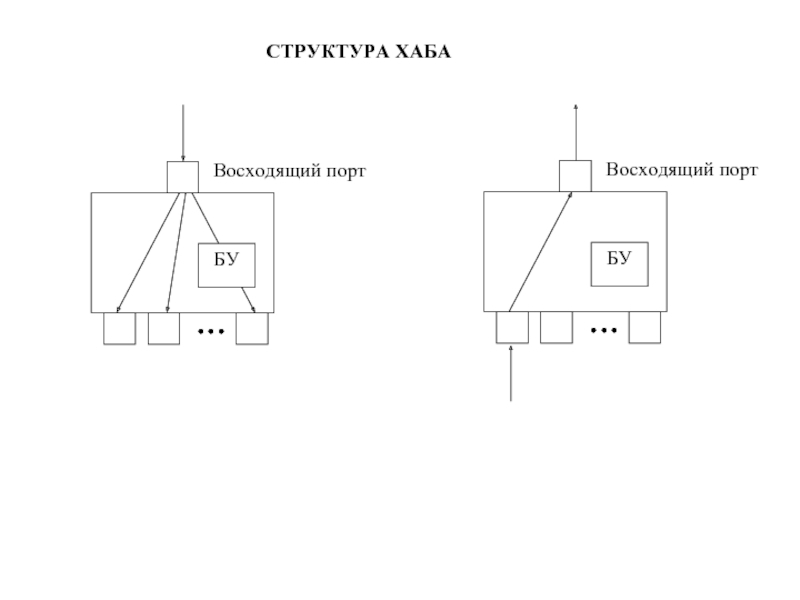

- 153. Структура шины В ней используются сетевые принципы

- 155. СТРУКТУРА ХАБА

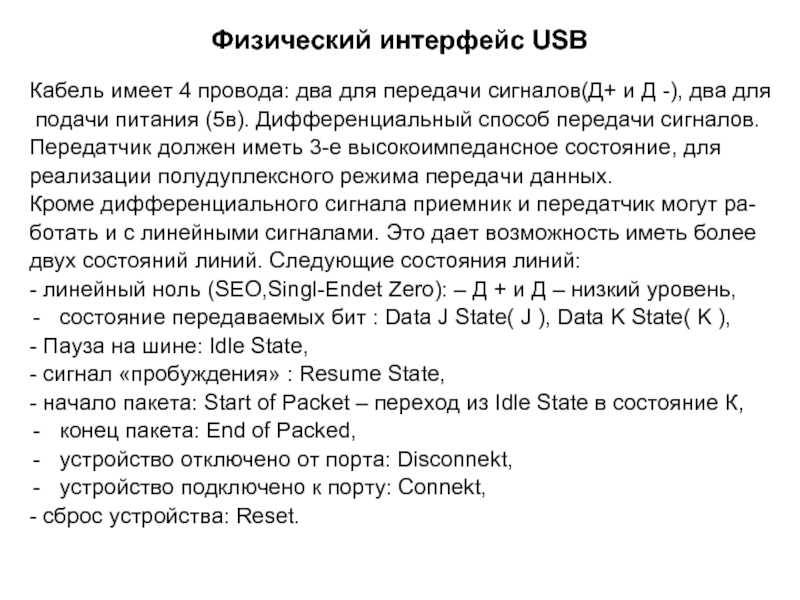

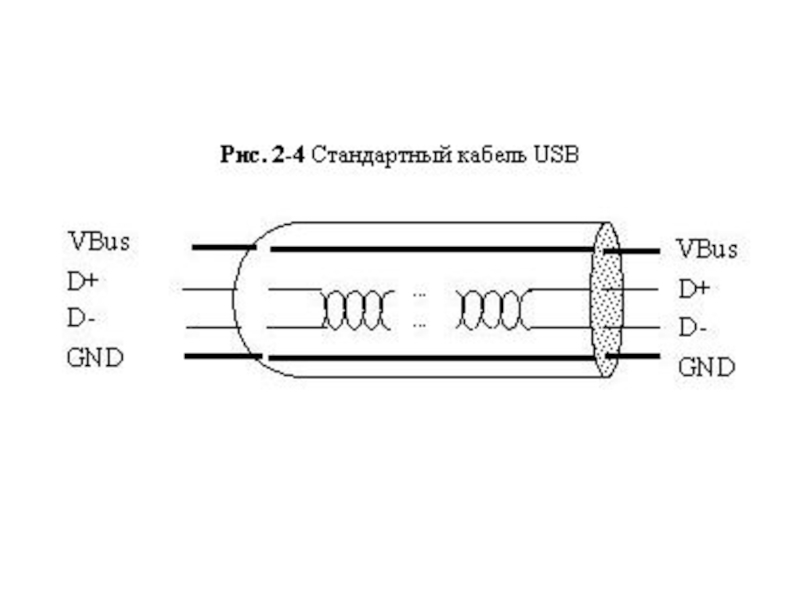

- 157. Физический интерфейс USB Кабель имеет 4 провода:

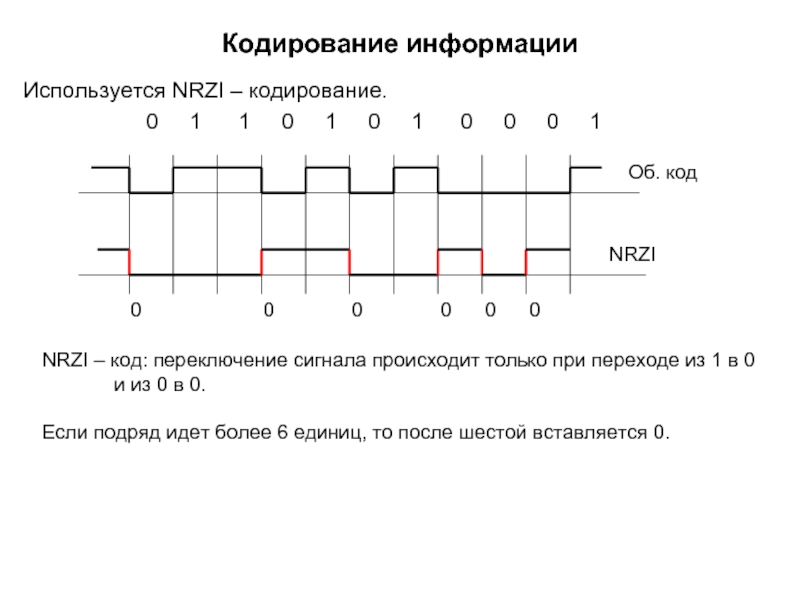

- 159. Кодирование информации Используется NRZI – кодирование.

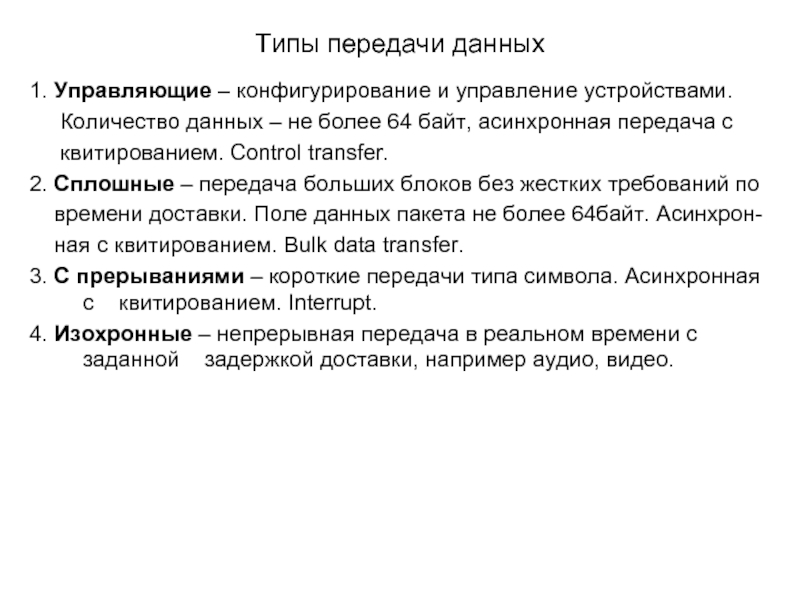

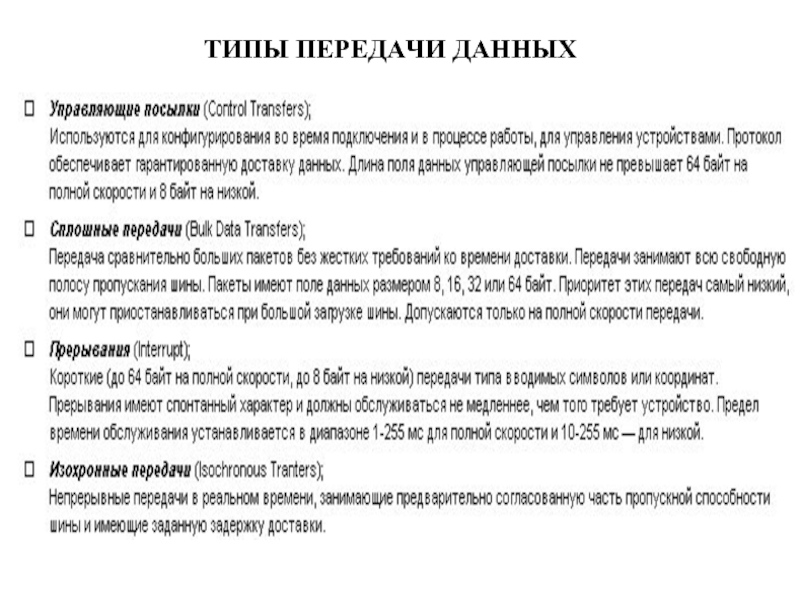

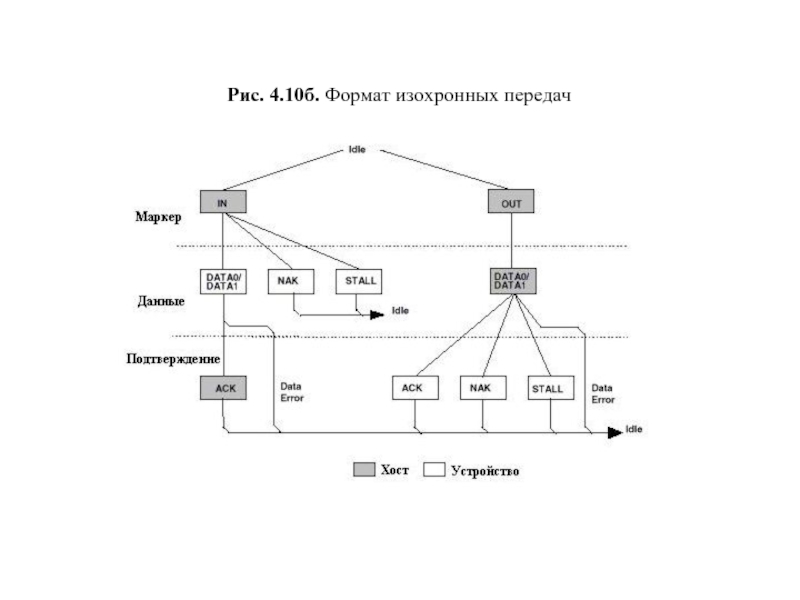

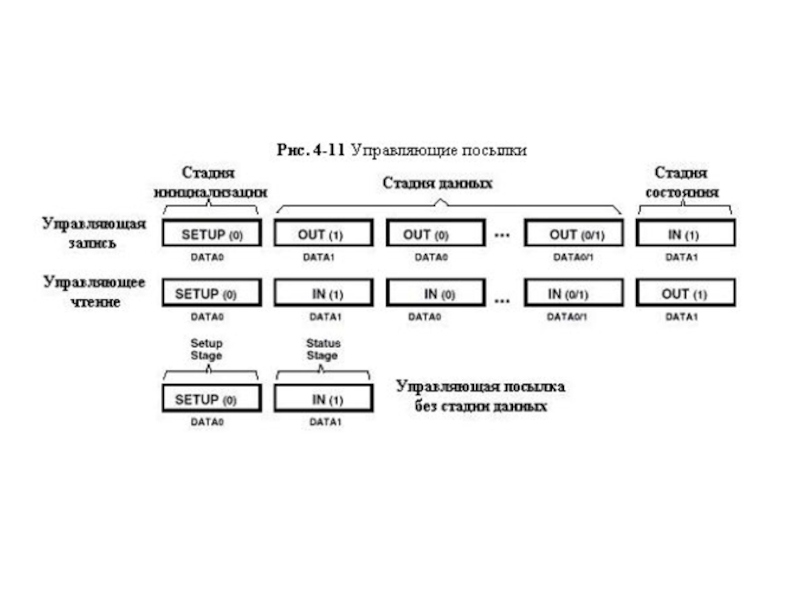

- 161. Типы передачи данных 1. Управляющие – конфигурирование

- 162. ТИПЫ ПЕРЕДАЧИ ДАННЫХ

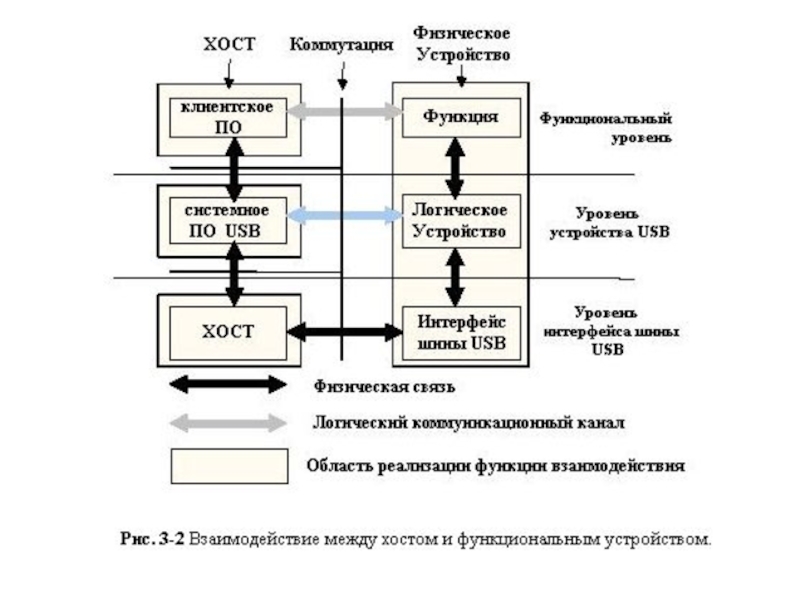

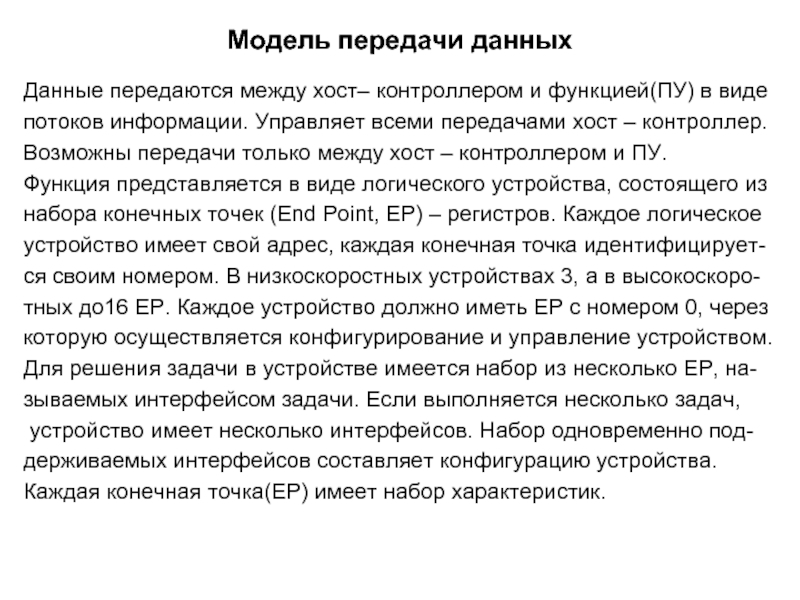

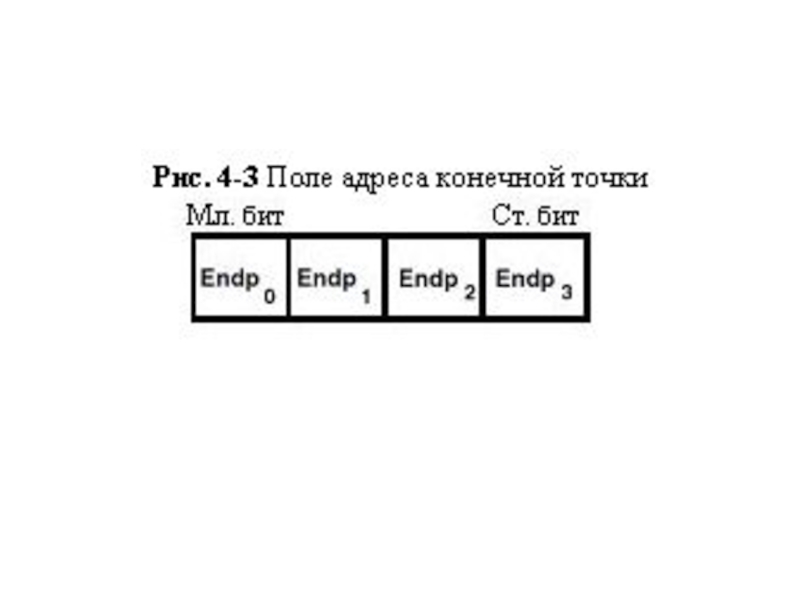

- 163. Модель передачи данных Данные передаются между хост–

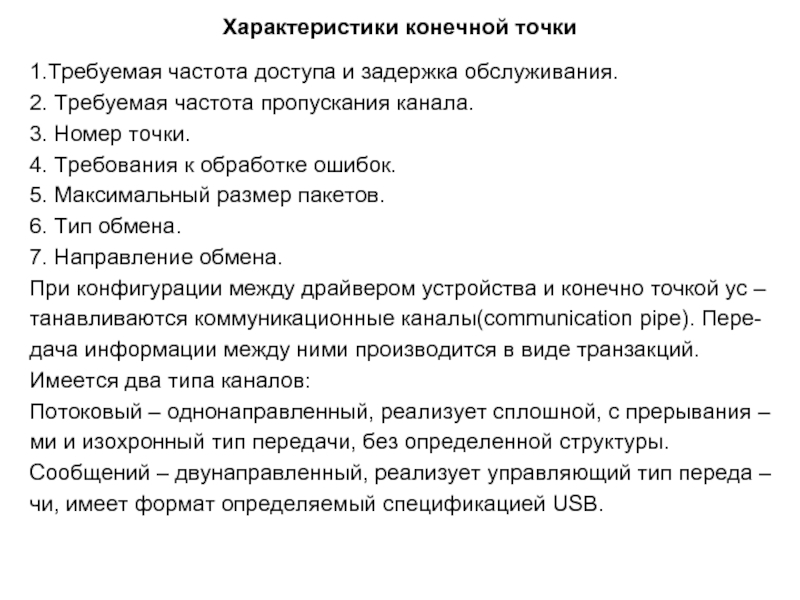

- 164. Характеристики конечной точки 1.Требуемая частота доступа и

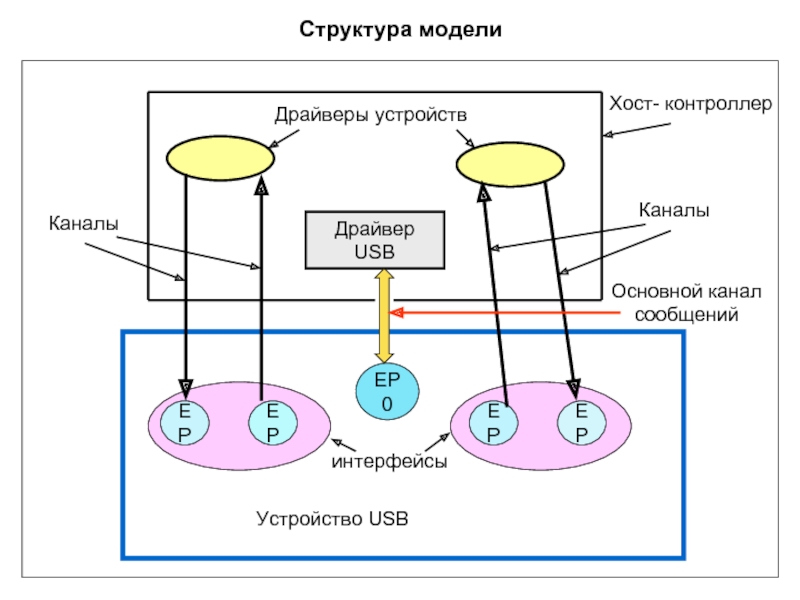

- 165. Структура модели Драйвер USB

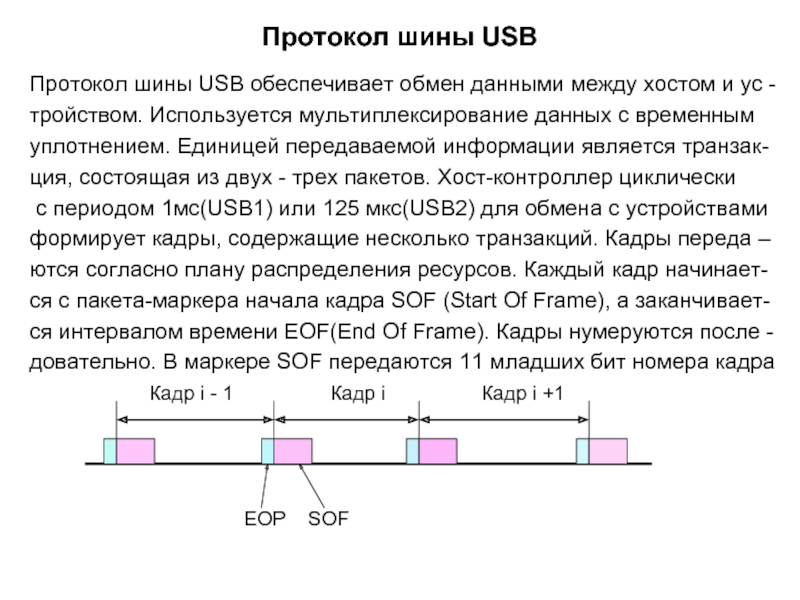

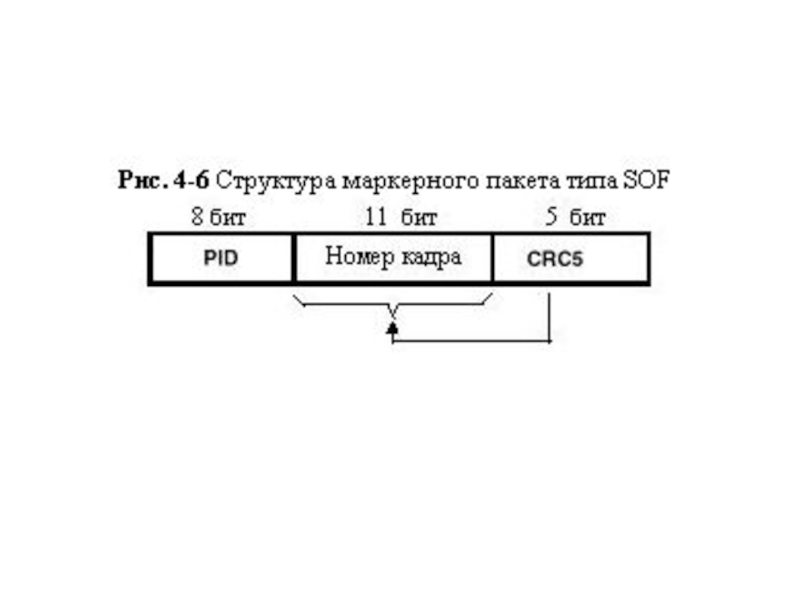

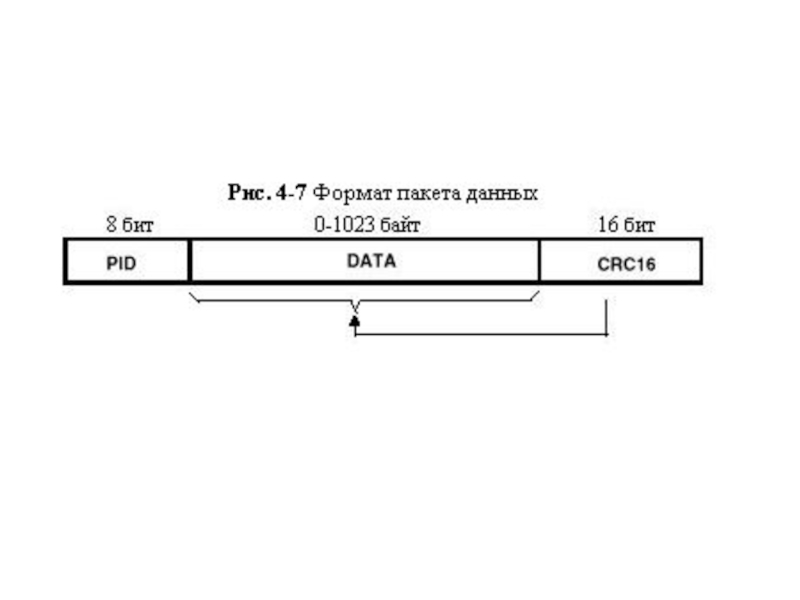

- 166. Протокол шины USB Протокол шины USB обеспечивает

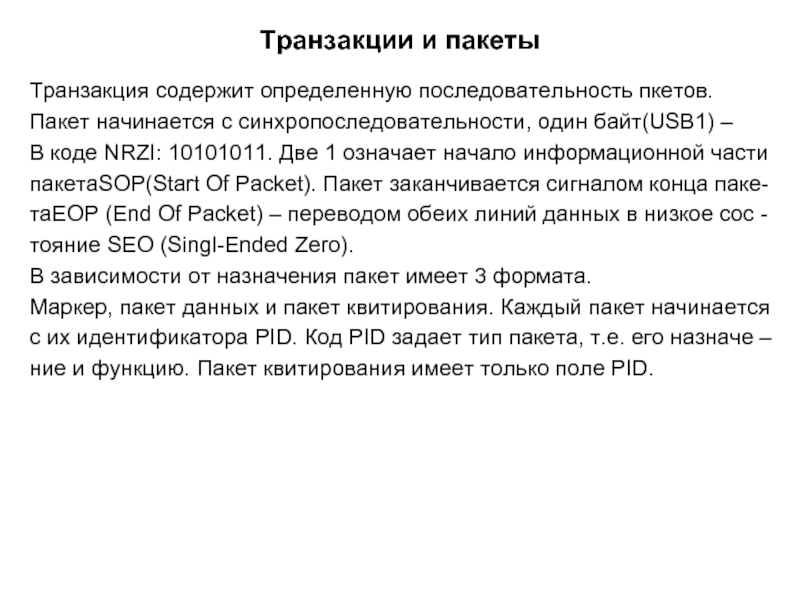

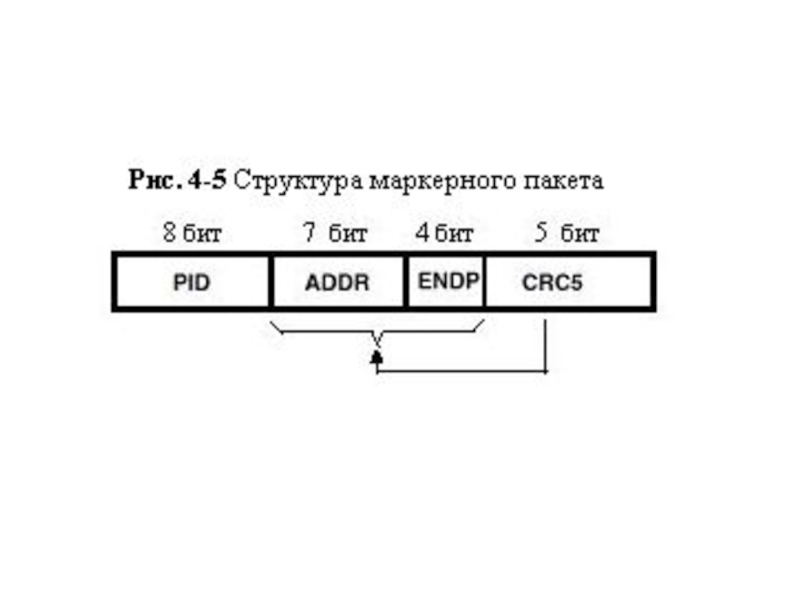

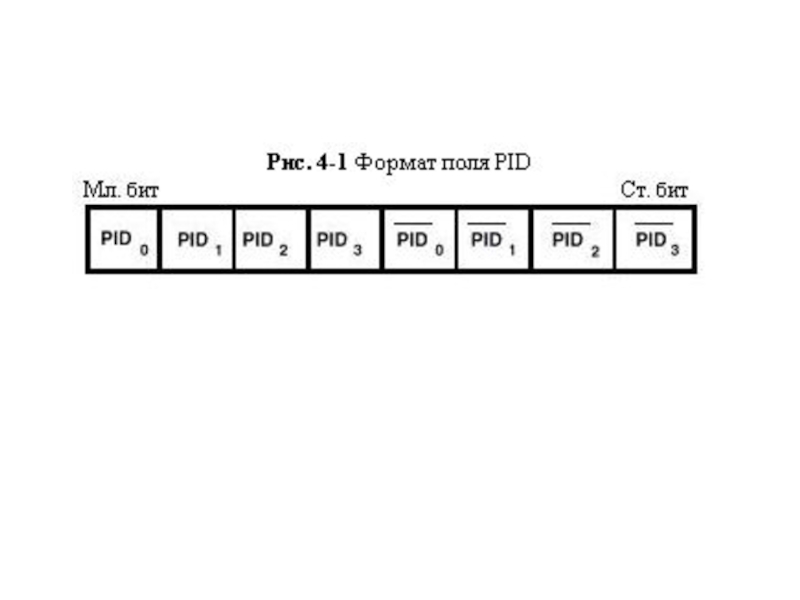

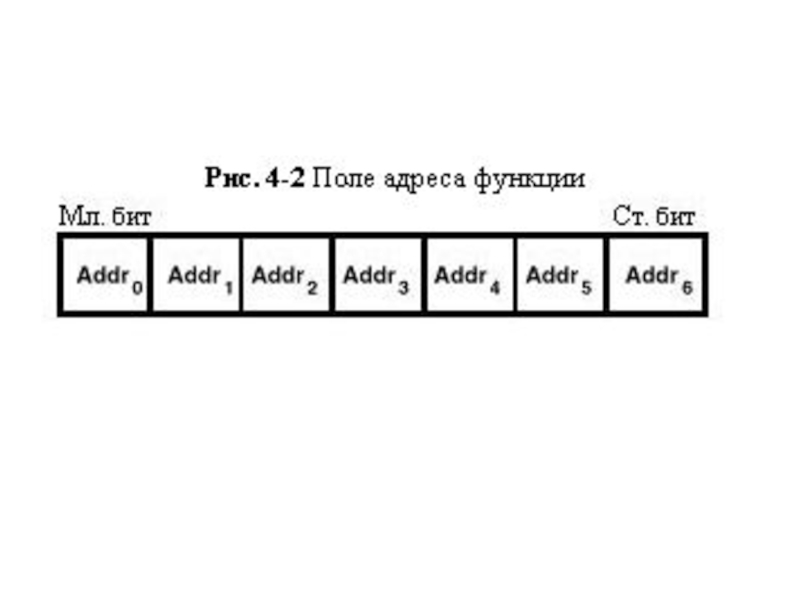

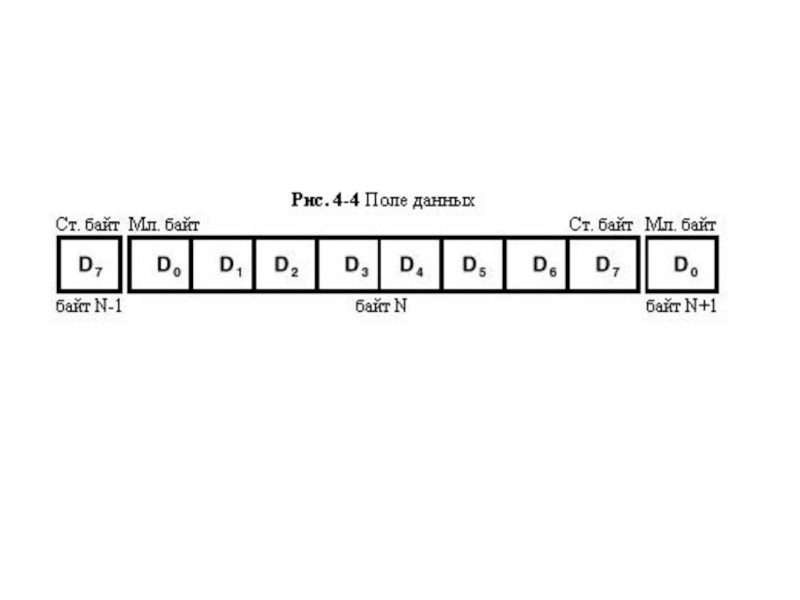

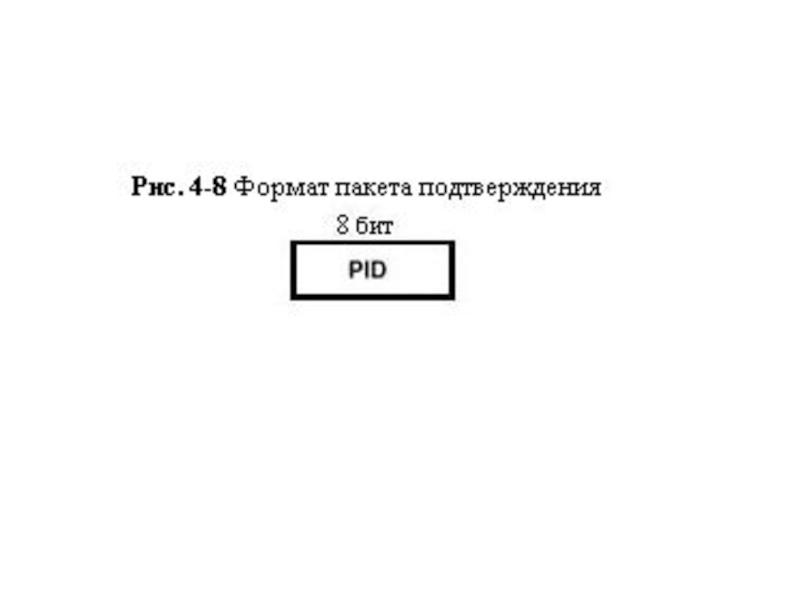

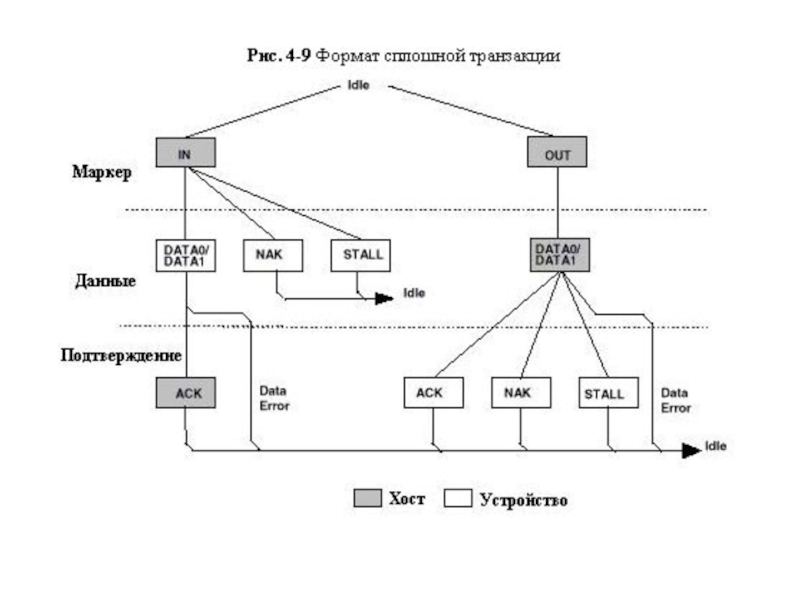

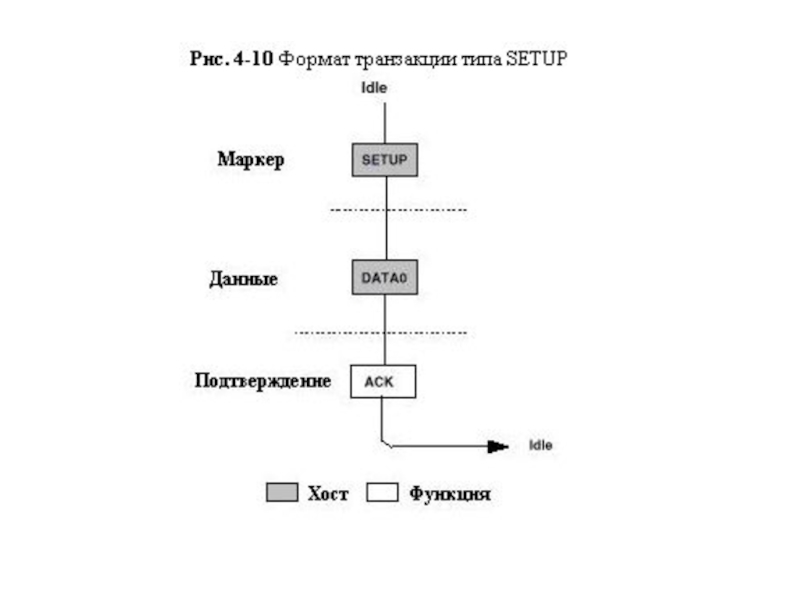

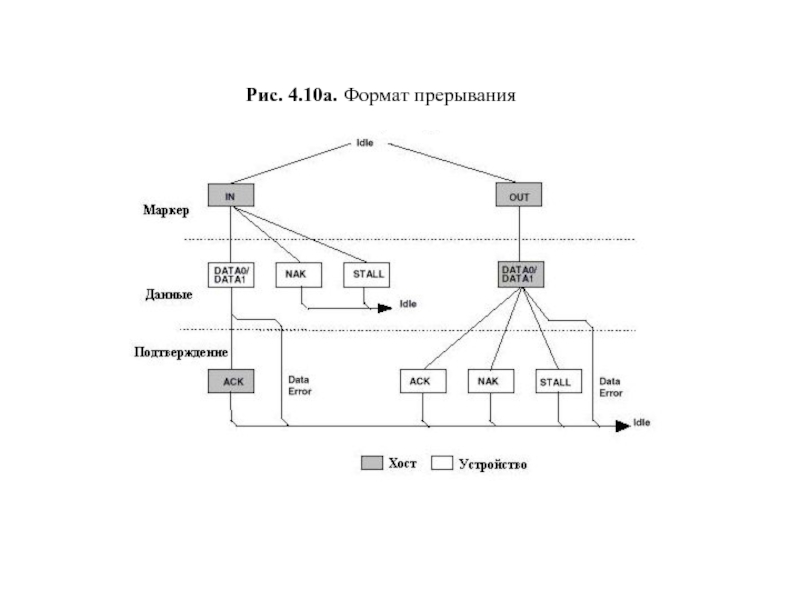

- 167. Транзакции и пакеты Транзакция содержит определенную последовательность

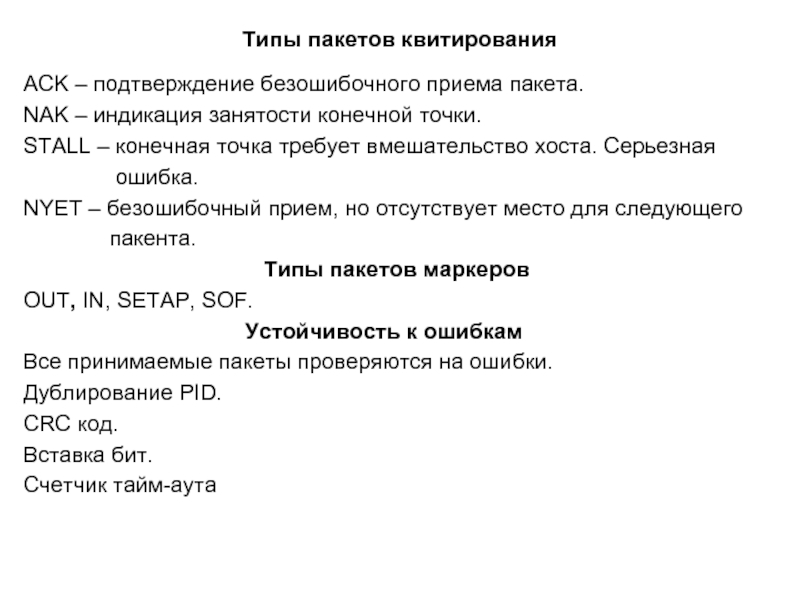

- 176. Типы пакетов квитирования ACK – подтверждение безошибочного

- 179. Рис. 4.10а. Формат прерывания

- 180. Рис. 4.10б. Формат изохронных передач

- 183. Интерфейсы устройств хранения (внешних запоминающих устройств –

- 184. Контроллер носителя как правило встроен в

- 185. Блок - схема ВЗУ, подключенного к хосту

- 186. Стандартные интерфейсы ВЗУ К

- 187. Интерфейс ATA / ATAPI

- 188. Сигналы шины АТА/ATAPI - 4 RESET# (Device

- 189. Режимы передачи данных Интерфейс ATA/ATAPI использует

- 190. Скорость передачи данных при различных режимах После

- 191. Интерфейс Serial ATA (SATA)

- 192. Четырехурвневая модель интерфейса SATA Имеется 4 уровня:

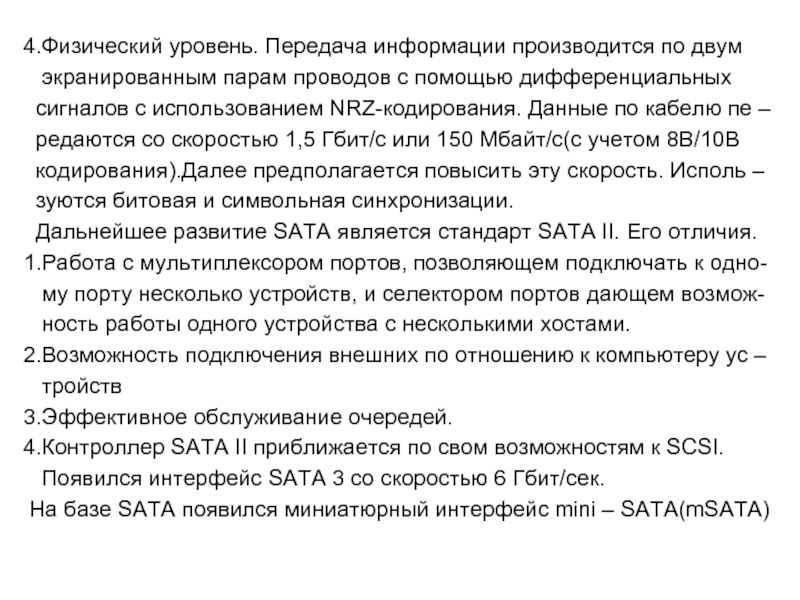

- 193. 4.Физический уровень. Передача информации производится по

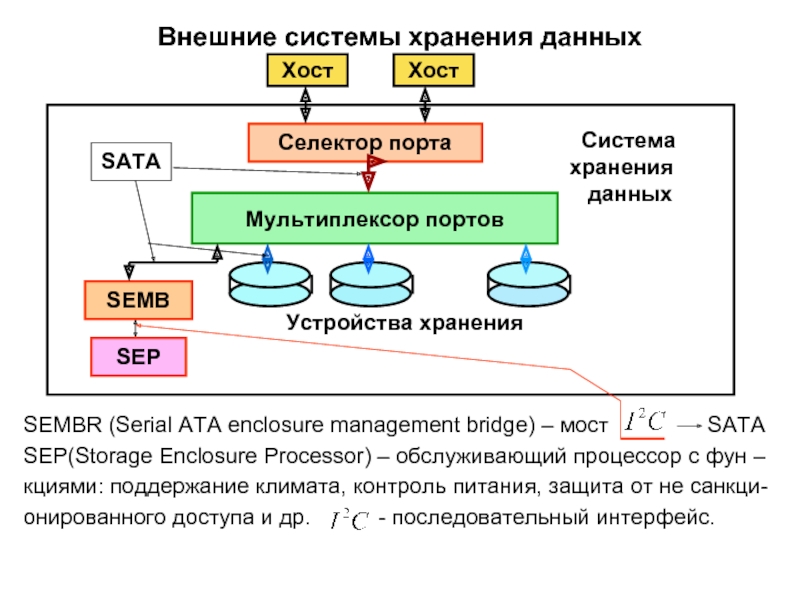

- 194. Внешние системы хранения данных SEMBR (Serial ATA

- 195. Интерфейсы флэш - памяти Для подключения USB

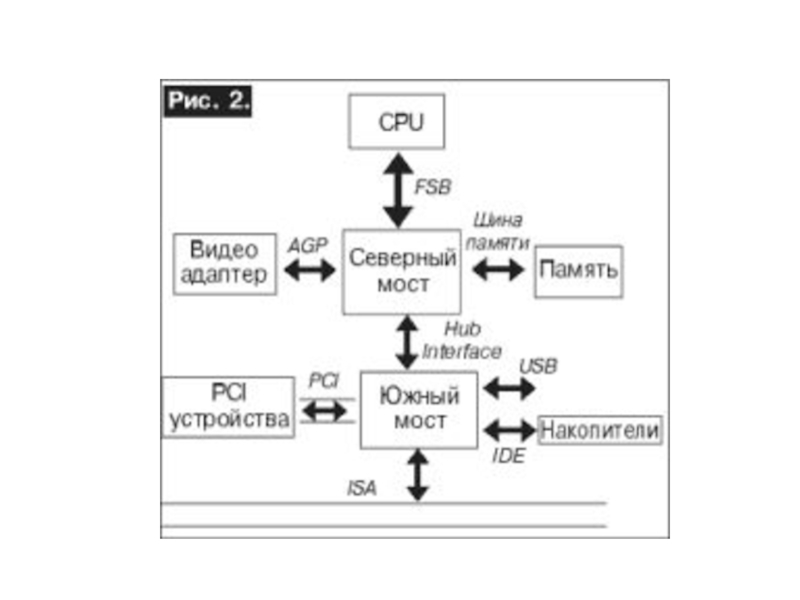

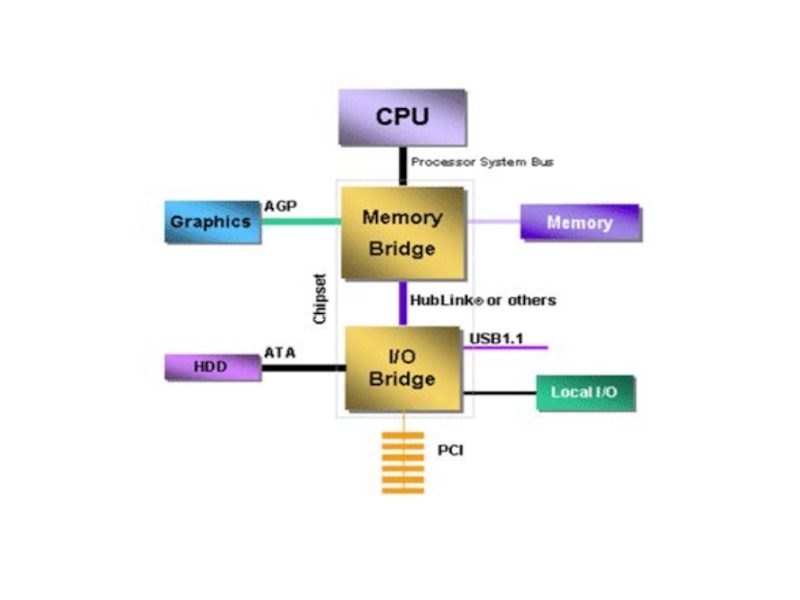

- 197. Чипсет(Chipset)

- 198. Чипсет ( Chipset ) – основа

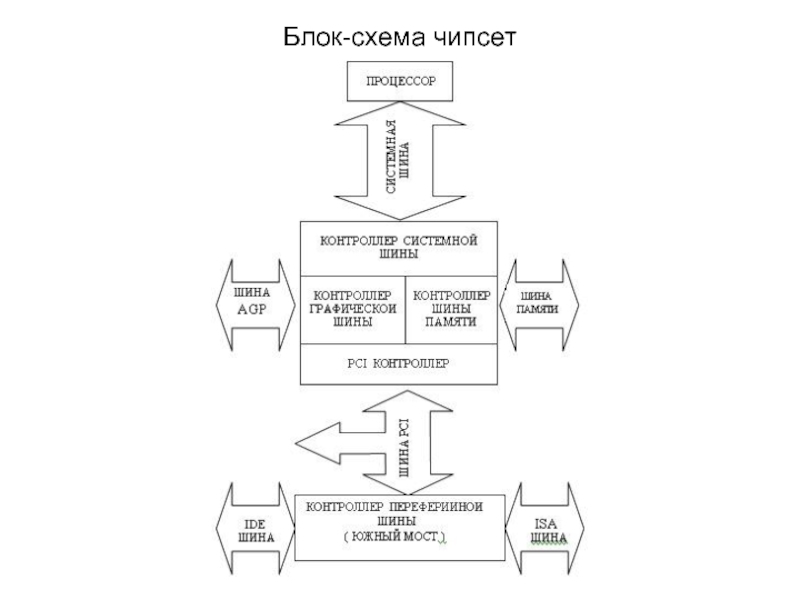

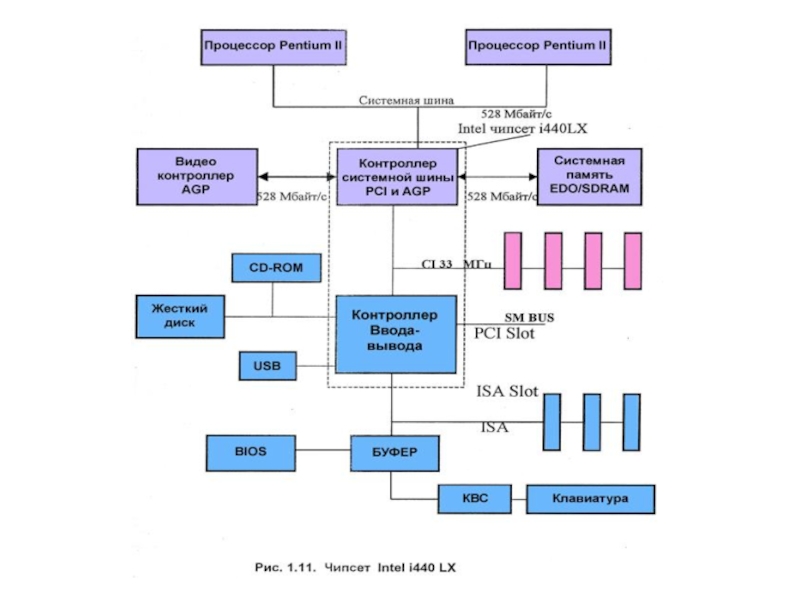

- 199. Блок-схема чипсет

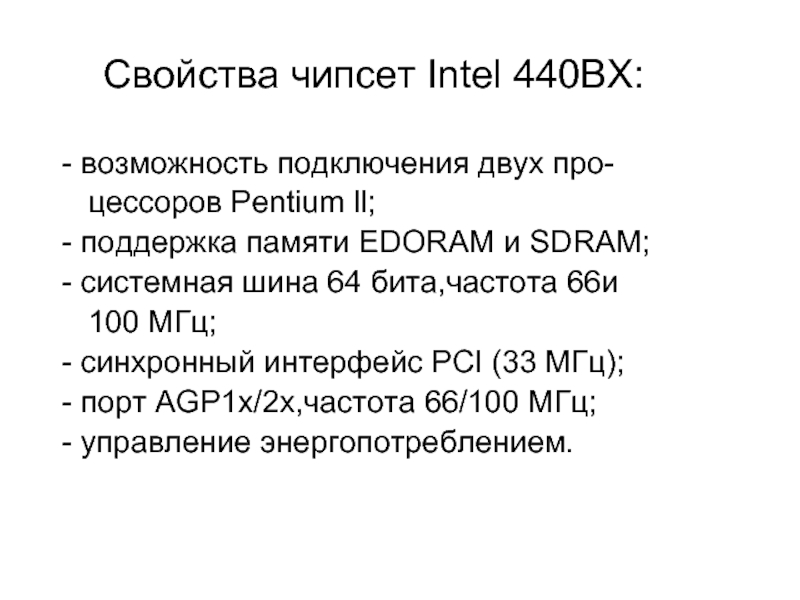

- 204. Свойства чипсет Intel 440BX:

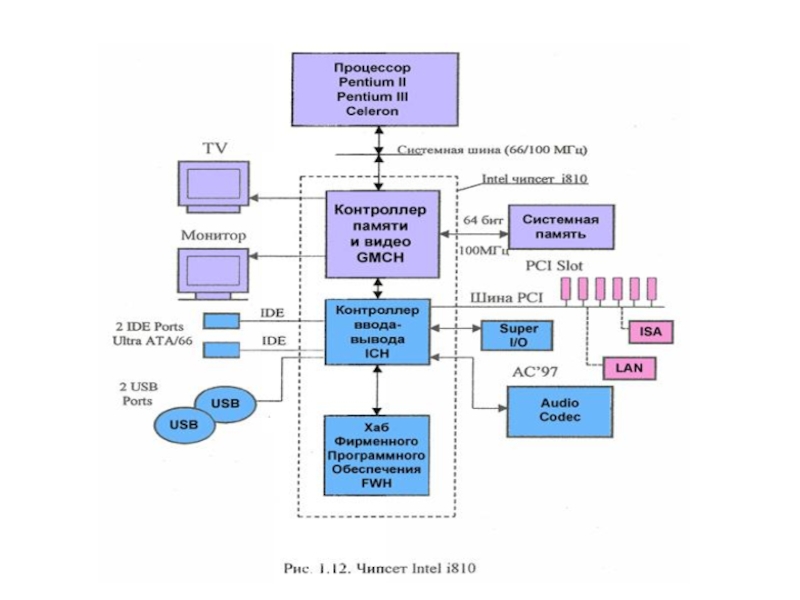

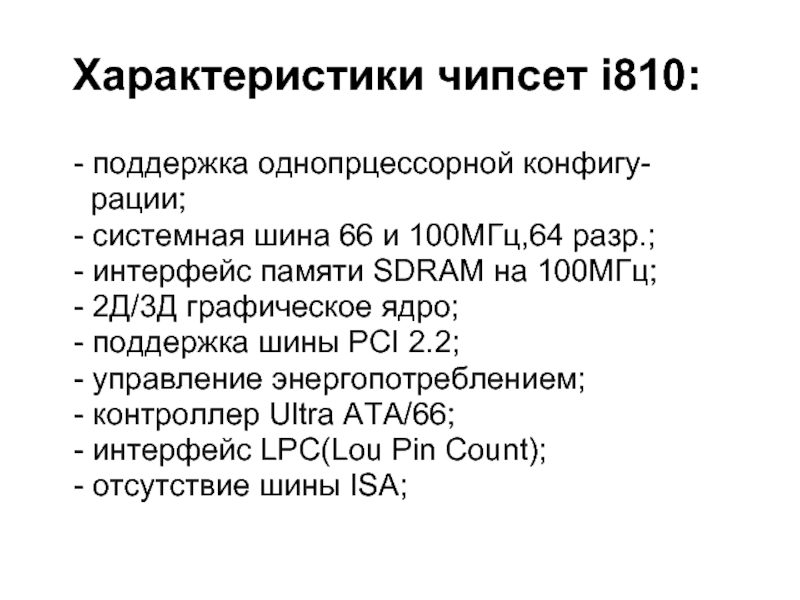

- 206. Характеристики чипсет i810: -

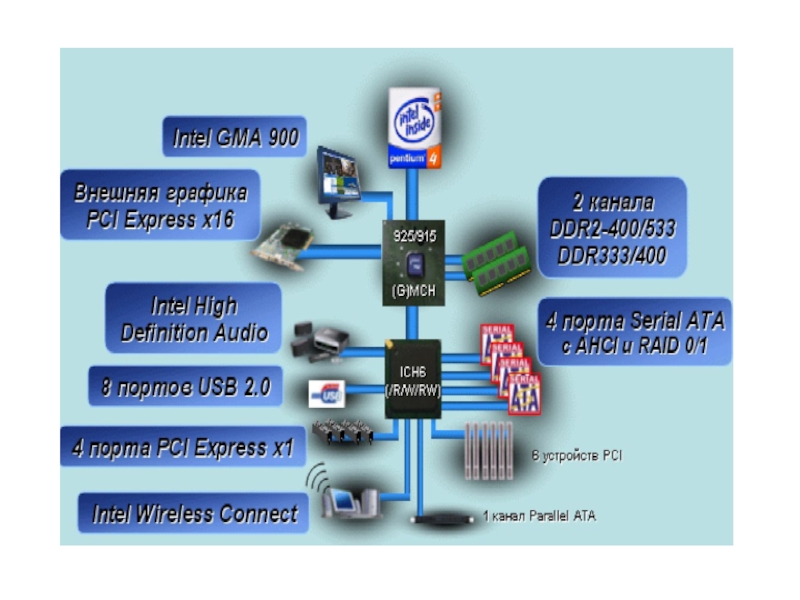

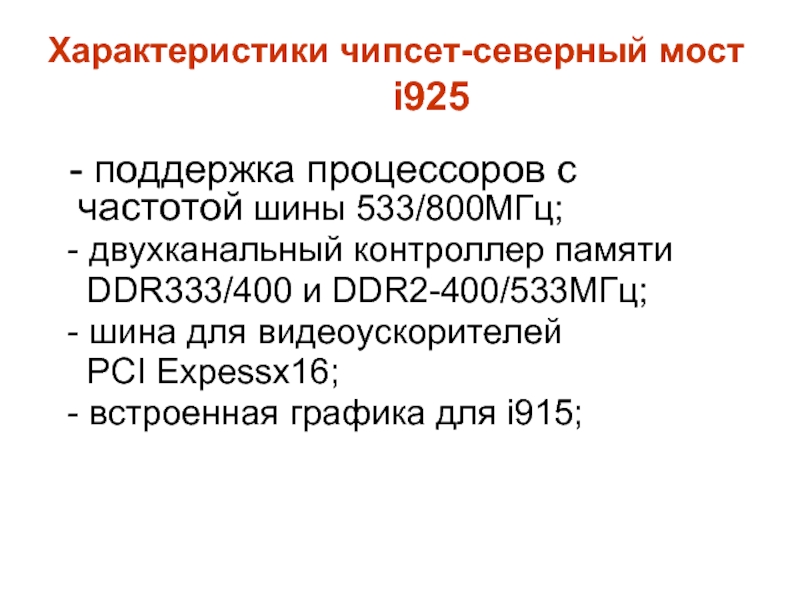

- 208. Характеристики чипсет-северный мост

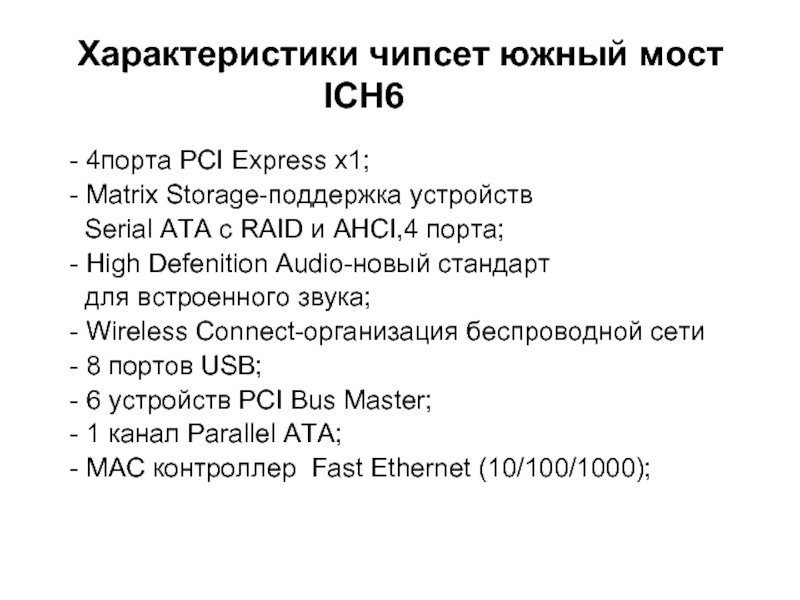

- 209. Характеристики чипсет южный мост

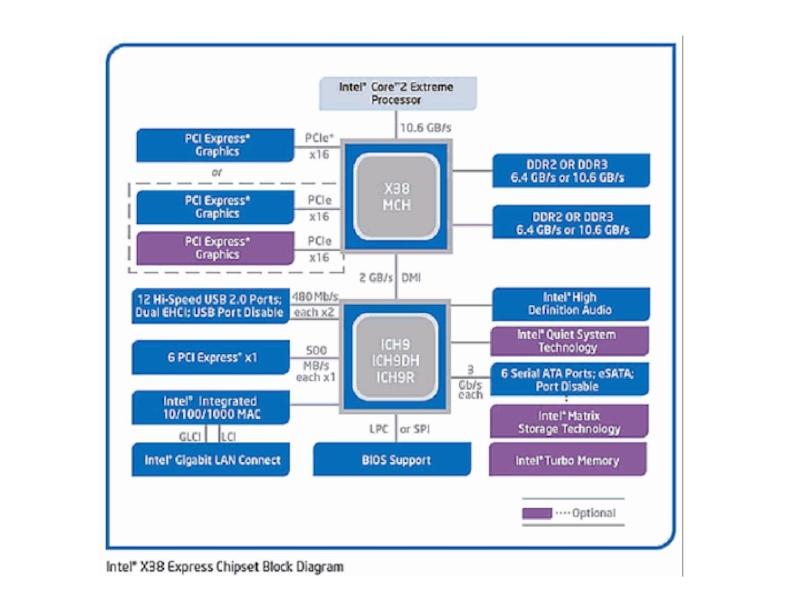

- 211. Северный мост -чипсет х38 Express -

- 212. Чипсет Intel ICH9-южный мост -

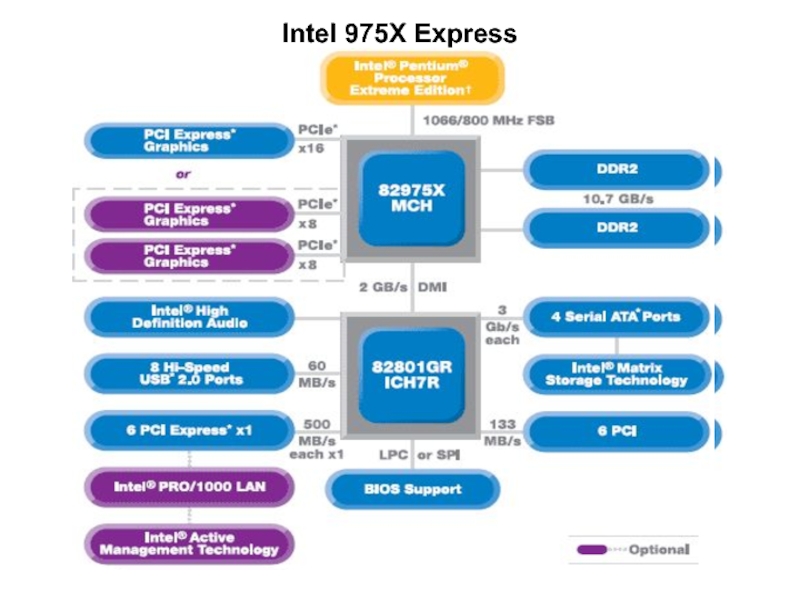

- 213. Intel 975X Express

- 214. Северный мост 975X: поддержка процессоров

- 215. процессоры на базе Nehalem, имеющие 4

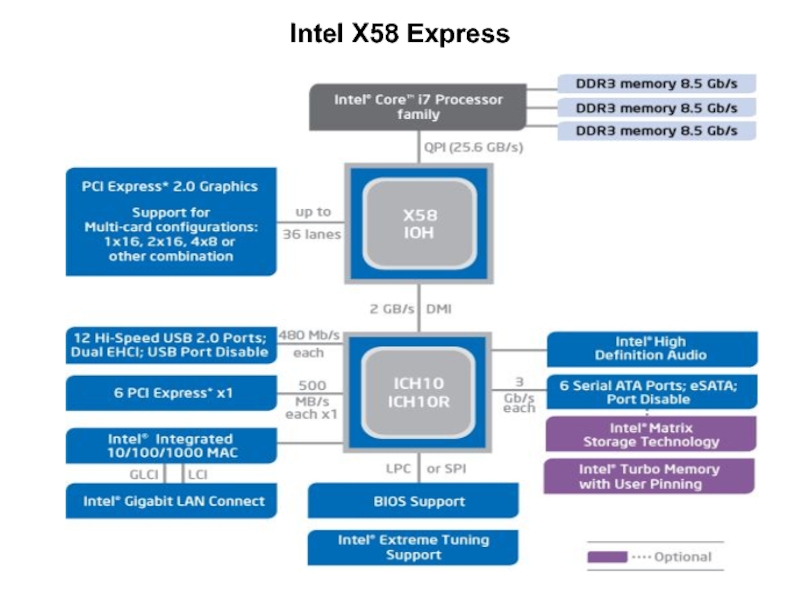

- 216. Intel X58 Express

- 217. поддержка новых процессоров (представленных на момент

- 218. Южный мост ICH10/R до 6 портов

- 219. Чипсет Intel P55 для новой платформы Socket

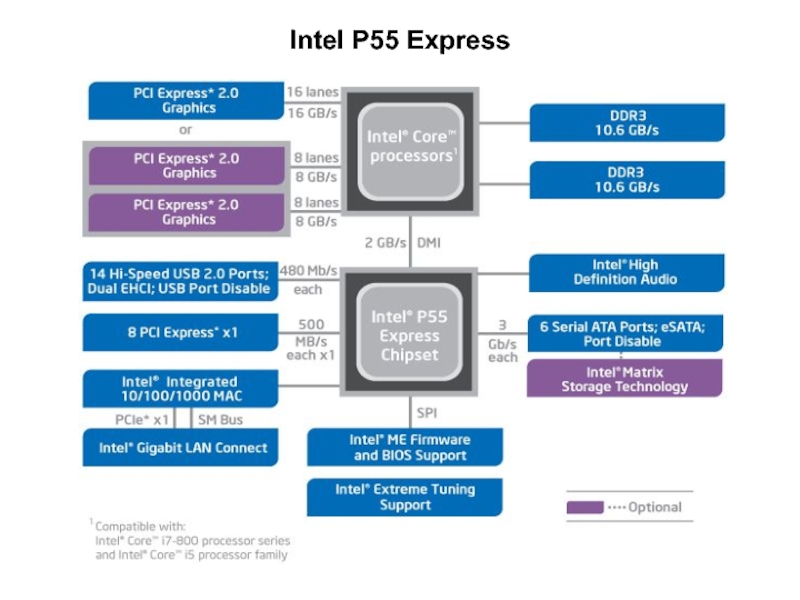

- 220. Intel P55 Express

- 221. характеристики чипсета P55 Express поддержка новых

Слайд 1 Кафедра “компьютерные системы и технологии”

Системы ввода-вывода, интерфейсы

и периферия компьютеров

часть 1

Системы ввода-вывода и интерфейсы

(конспект лекций)

Лектор профессор Чернышев Ю.А.

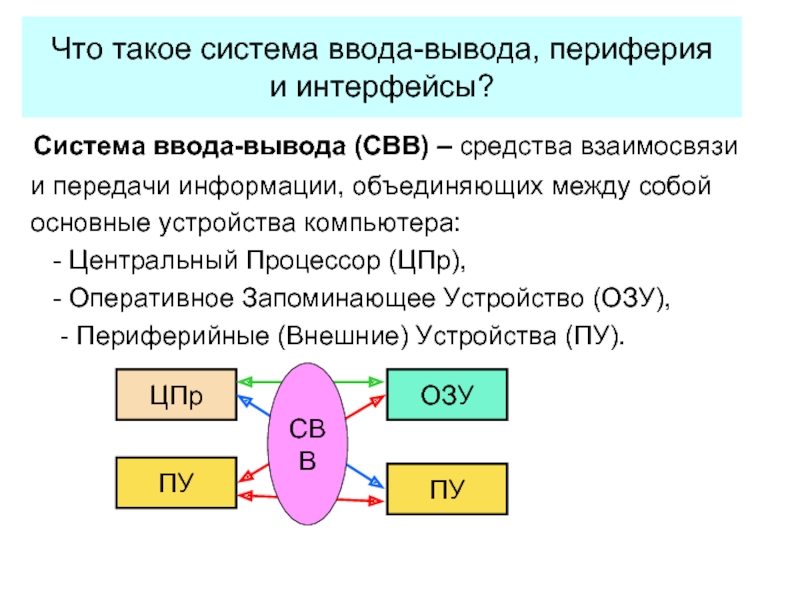

Слайд 4Что такое система ввода-вывода, периферия

и интерфейсы?

Система ввода-вывода (СВВ) – средства

и передачи информации, объединяющих между собой

основные устройства компьютера:

- Центральный Процессор (ЦПр),

- Оперативное Запоминающее Устройство (ОЗУ),

- Периферийные (Внешние) Устройства (ПУ).

ЦПр

ОЗУ

ПУ

ПУ

СВВ

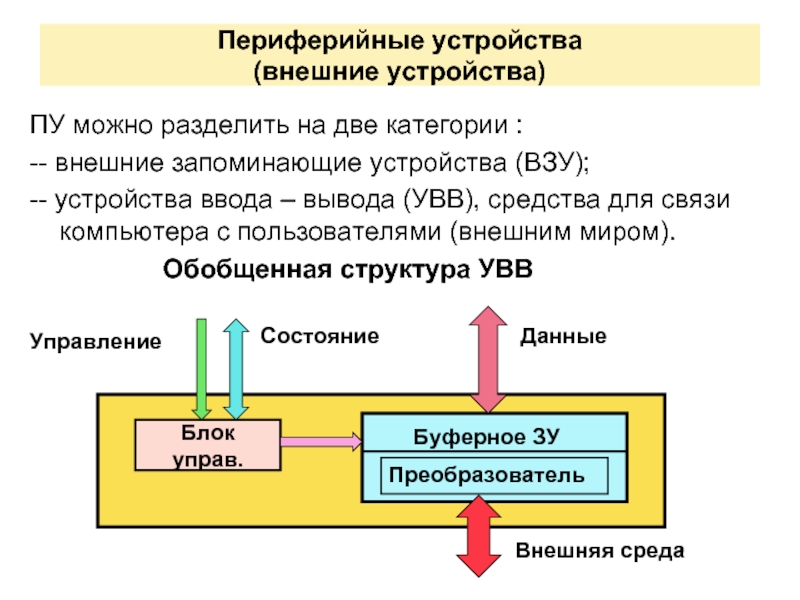

Слайд 5Периферийные устройства

(внешние устройства)

ПУ можно разделить на две категории :

-- внешние запоминающие

-- устройства ввода – вывода (УВВ), средства для связи компьютера с пользователями (внешним миром).

Обобщенная структура УВВ

Блок управ.

Буферное ЗУ

Преобразователь

Данные

Состояние

Управление

Внешняя среда

Слайд 6Функционально – модульная структура компьютера

Компьютер можно представить

взаимосвязанных функционально законченных и конструктивно

оформленных модулей : микропроцессора, ОЗУ, контроллеров

(БИС, платы расширения), ВЗУ, монитор, печать и другие ПУ.

Связь между ними должна осуществляться СВВ с помощью

стандартных технических средств и правил взаимодействия, т.е. стандартных интерфейсов.

Слайд 8 ИНТЕРФЕЙС

Средства

взаимосвязь устройств между собой,

называются интерфейсом.

В интерфейсе стандартизируются:

1.Назначение и количество линий интерфейса.

2.Параметры электрических сигналов.

3.Протоколы обмена информацией и выполнения

функций интерфейса.

4.Конструктивные параметры.

Физически интерфейс реализуется в виде электриче -

ских линий для передачи сигналов и набора микро -

схем, обеспечивающих выполнение основных функций

интерфейса.

Слайд 9Некоторые понятия интерфейсов

Канал – среда передачи информации, представляемой в виде определенных

Линия интерфейса – это электрический проводник (провод, линия печатного монтажа, контакт разъема платы), по которому распространяется электрический сигнал. При диффе-

ренциальном представлении сигналов линия содержид два проводника.

Магистраль – это совокупность всех линий интерфейса.

Шина – группа линий интерфейса, соответствующая определенному функциональному назначению (шина данных, шина адреса и т.п.)

В дальнейшем термин «магистраль» стали заменять термином «шина». В свою очередь понятие «шина» стало в определенной мере синонимом термина «интерфейс», хотя понятие шины более узкое, чем общее понятие интерфейса

Слайд 11Топология интерфейсов

1.Точка – точка

2. Магистральная

Шлейфовая

3.Многоуровневая звезда

1

2

1

N

1

2

N

T

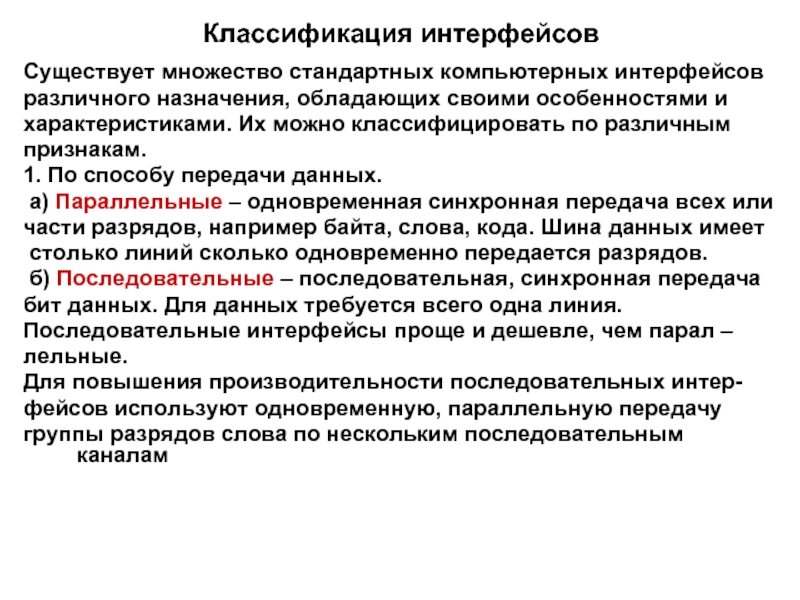

Слайд 12Классификация интерфейсов

Существует множество стандартных компьютерных интерфейсов

различного назначения, обладающих своими особенностями

характеристиками. Их можно классифицировать по различным

признакам.

1. По способу передачи данных.

а) Параллельные – одновременная синхронная передача всех или

части разрядов, например байта, слова, кода. Шина данных имеет

столько линий сколько одновременно передается разрядов.

б) Последовательные – последовательная, синхронная передача

бит данных. Для данных требуется всего одна линия.

Последовательные интерфейсы проще и дешевле, чем парал –

лельные.

Для повышения производительности последовательных интер-

фейсов используют одновременную, параллельную передачу

группы разрядов слова по нескольким последовательным каналам

Слайд 13

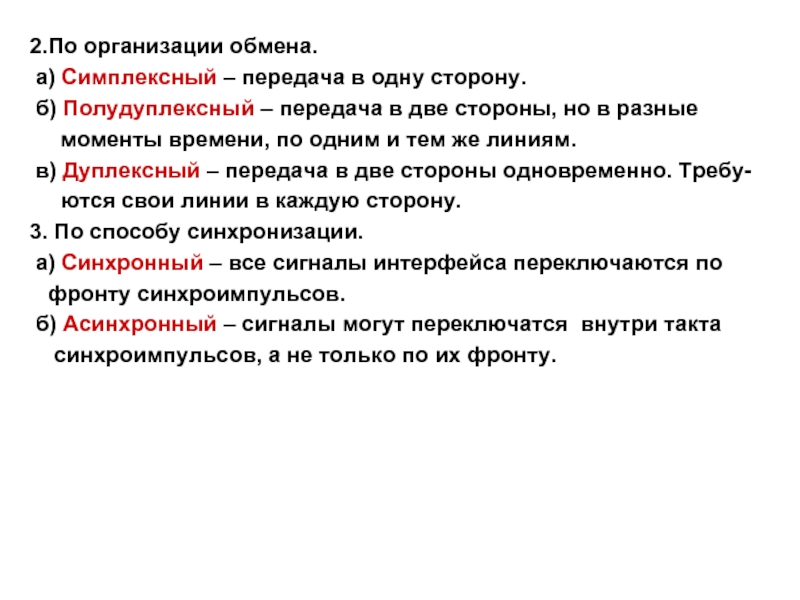

2.По организации обмена.

а) Симплексный – передача в одну сторону.

моменты времени, по одним и тем же линиям.

в) Дуплексный – передача в две стороны одновременно. Требу-

ются свои линии в каждую сторону.

3. По способу синхронизации.

а) Синхронный – все сигналы интерфейса переключаются по

фронту синхроимпульсов.

б) Асинхронный – сигналы могут переключатся внутри такта

синхроимпульсов, а не только по их фронту.

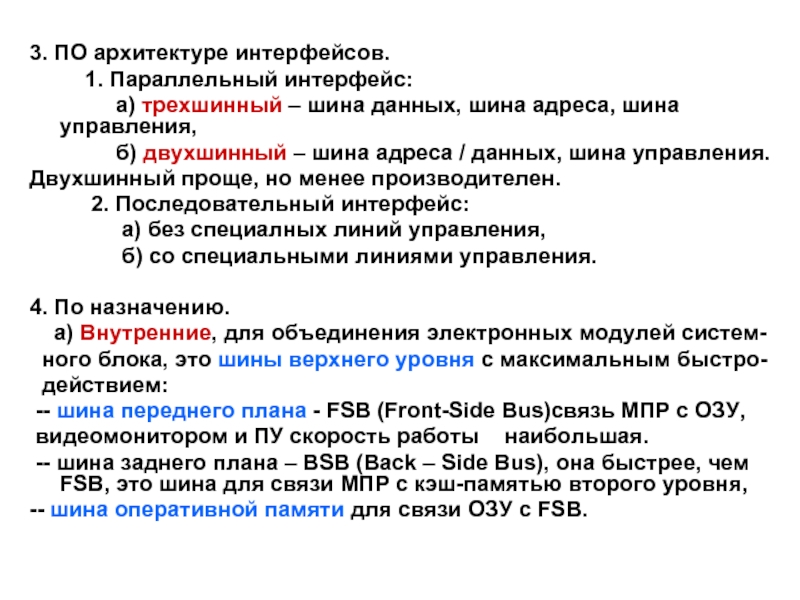

Слайд 14

3. ПО архитектуре интерфейсов.

1. Параллельный

а) трехшинный – шина данных, шина адреса, шина управления,

б) двухшинный – шина адреса / данных, шина управления.

Двухшинный проще, но менее производителен.

2. Последовательный интерфейс:

а) без специалных линий управления,

б) со специальными линиями управления.

4. По назначению.

а) Внутренние, для объединения электронных модулей систем-

ного блока, это шины верхнего уровня с максимальным быстро-

действием:

-- шина переднего плана - FSB (Front-Side Bus)связь МПР с ОЗУ,

видеомонитором и ПУ скорость работы наибольшая.

-- шина заднего плана – BSB (Back – Side Bus), она быстрее, чем FSB, это шина для связи МПР с кэш-памятью второго уровня,

-- шина оперативной памяти для связи ОЗУ с FSB.

Слайд 15

-- шины ввода –вывода (шины расширения) - предназначены для

размера, важным является их стоимость и конструктив. Являют-

ся одной из основ системы ввода – вывода.

б) Внешние (интерфейсы ПУ) – предназначены для подключения

ПУ к системе ввода – вывода. Они могут быть :

-- универсальные, для подключения разных типов ПУ,

-- специализированные – для подключения одного типа ПУ.

Скорость передачи информации в интерфейсах

Скорость передачи измеряется в бит/сек или байт/сек.

Будем считать, что за один синхроимпульс передается слово или

бит. Тогда : при частоте синхроимпульсов f скорость передачи

- параллельный интерфейс, при N - число бит, n - байт в слове

Vпар = fпар N бит/сек = fпар n байт/сек, fпар < 150Мгц

- последовательный интерфейс Vпос = fпос бит/сек

Сейчас все шире используются последовательные интерфейсы

из-за их простоты и дешевизны и высоком значении fпос >2Ггц

Слайд 17Организация передачи информации между

ЦПР и ПУ

Все устройства, взаимодействующие с помощью

делятся на два вида : задатчики (активные устройства), начинают

и управляют процессом ввода-вывода, исполнители (пассивные

устройства), они принимают (вывод, запись) или выдают(ввод,

чтение) информацию и выполняют приказы задатчика.

Устройство, выдающее информацию, является источником,

а принимающее – приемником.

ЦПр всегда задатчик, а ОЗУ всегда исполнитель. ПУ и то и другое.

Передача информации от задатчика к исполнителю реализуется

операцией записи, а обратная – операцией чтения. Процесс пере-

дачи между ПУ и ЦПр называют вводом-выводом информации.

Для минимизации загрузки процессора при выполнении процес-

сов ввода-вывода функции управления распределяются на нес -

колько устройств: процессор, главный контроллер (канал) ввода-

вывода, контроллер ПУ и блок управления ПУ.

Слайд 27Основные функции интерфейсов

1. Передача информации.

2. Синхронизация передачи информации.

3. Арбитрация, селекция.

4. Контроль

5. Преобразование информации.

6. Автоконфигурация.

7. Управление питанием.

8. Горячее подключение.

Слайд 28Функция передача информации

Главная задача интерфейса -- организация надежной передачи

информации

мени. Если к одному интерфейсу с помощью специальных

средств физически подключается множество взаимодействую-

щих между собой устройств, то в каждый момент времени переда

ча информации идет только между двумя устройствами от источ-

ника к приемнику, остальные отключены от шины.

Такая передача возможна, если между этими двумя устройствами

в данный момент времени включена электрическая цепь

(электрическая взаимосвязь), соединяющая выходы источника

со входами приемника, по которой передаются электрические

сигналы, соответствующие данной информации.

Таким образом в интерфейсах между двумя взаимосвязанными

устройствами постоянно существует логический канал, который

или открыт для передачи информации, образуя соединение типа

«точка-точка», или закрыт, отключая устройство от шины.

Для переключения логического канала из закрытого в открытый

и наоборот, а также для передачи и приема данных требуется

определенное время.

Слайд 30Состояние линий интерфейса

Линия интерфейса может находиться в двух состояниях:

передаваемой информации ( «0» или «1» ), либо сигналы управле-

ния, имеющие или высокий или низкий уровни, как правило актив-

ному управляющему сигналу соответствует низкий уровень;

- состянии холостого хода, когда на линии отсутствуют какие

либо сигналы,т.е. передачи информации нет. Это состояние линий

идентифицируется с помощью набора определенных управляю-

щих сигналов на линиях шины управления, или определенным

физическим состоянием линий.

Считывание приемником значений разрядов производится в мо –

мент времени, когда сигналы, соответствующие 0 или 1 примут

стабильное значение ,в этот момент времени подается специаль –

ный строб импульс, по которому информация записывается в

приемник.

Слайд 31Время передачи информации

Пусть : А - источник, В - приемник.

Сигнал

на

Сигнал

на В

tзд- задер. захв. шины, tрс- распр. сигн., tст-стабильный сигнал

tуд- удерж. стаб. сиг., tп- время пер. tп = tрс + tст + tуд

tзд

tрс tст tуд

А получает

шину

Данные

на А

Данные

на В

Данные

считаны

Данные

удалены

Слайд 32Транзакции и операции интерфейса

Данные по линиям интерфейса передаются блоками. Блок, со

держащий в начале адрес первого слова, а затем сами данные

называется транзакцией. Использование транзакций повышает

производительность интерфейса за счет однократной передачи

адреса. Транзакция имеет признаки ее начала и конца.

При выполнении транзакции чтения после установки адреса тре-

буется время на переключение направления передачи информа-

ции : было от задатчика к исполнителю, требуется от исполните-

ля к задатчику.

Передача информации по шине выполняется с помощью специ –

альных команд (операций) интерфейса, каждой из которых соот-

ветствует определенный протокол работы шины. Основными яв-

ляются операции ЗАПИСИ - WR(write) и ЧТЕНИЯ – RD(rеаd). Они

разные при обращении к разным полям памяти: ОЗУ, регистры

ввода – вывода, регистры автоконфигурации.

Слайд 33

Используются следующие принципы построения интерфейсов:

синхронный и асинхронный,с коммутацией цепей

Синхронный – все сигналы переключаются только по фронту

синхроимпульсов.

Асинхронный – возможно переключение сигналов и между синхроимпульсов.

С коммутацией цепей – шина занята на все время передачи транзакции между задатчиком и исполнителем. В этом случае

весьма вероятны простои шины из-за ожидания появления информации на шине.

С коммутацией пакетов – транзакция разбивается на два пакета:

пакет адреса и пакет данных, которые могут передаваться раздельно В этом случае, если на шине нет данных, она может использоваться другим задатчиком, что повышает производительность работы шины.

Слайд 34Функция синхронизации

При передаче информации источник должен знать, когда можно

начинать

редача информации. Это делается с помощью системы синхро –

низации.

Синхронизация – согласование процессов взаимодействия при

передаче информации от источника к приемнику.

В зависимости от типа единицы информации можно выделить три уровня синхронизации:

1. На уровне бит – реализуется аппаратно.

2. На уровне слов (байт) - реализуется аппаратно.

3. На уровне массивов – реализуется программно.

Слайд 35

Два основных принципа синхронизации:

Синхронный – когда смена состояний

взаимонезависима и выполняется через одинаковые фиксиро -

ванные интервалы времени, если в заданный момент времени

передача не произошла, информация теряется. Т.е. задается по –

стоянный фиксированный период синхронизации Тсин.

tрл – время распрстранения сигнала в линии

tрасп – время распознавания

tфик – фремя фиксации сигнала

Тсин – определяется по самому медленному устройству.

Асинхронный – когда смена состояний источника и приемника

взаимозависимы, т.е. момент смены состояния источника зависит

от момента смены состояния приемника. В этом случае Тсин

является переменным и зависит от быстродействия устройства.

Здесь требуется обратная связь от приемника к источнику.

Слайд 36Последовательная передача данных

Синхронный принцип синхронизации

Использование специальной линии синхронизации от генератора

синхроимпульсов

Использование двух ГСИ на источнике и приемнике, запускаемых

Одновременно при начале передачи данных

Использования принципа самосинхронизации. При этом сигналы

0 и 1 физически должны быть разными. Например 1 – изменение

сигнала от низкого до высокого уровня, а 0 – наоборот.

ГСИ

И

П

Данные

СИ

ГСИ

И

ГСИ

П

Данные

Слайд 38

Асинхронный принцип синхронизации

Используется при передаче блока (массива) данных. Начало и ко

нец блока помечается специальными кодами или сигналами.

Например, старт и стоп битами при передаче символа, в состоя –

нии холостого кода линия находится в состоянии 1.

Призн.нач. Массив данных Призн.кон.

Слайд 40Параллельная передача данных

При такой передаче обязательно используется строб – импульс,

посредством

но все разряды передаваемого слова(кода), когда все сигналы

разрядов примут стабильное значение.

При синхронном принципе синхронизации период синхронизации

задает строб – импульс.

При асинхронном принципе синхронизации кроме строба от при -

емника к источнику подается сигнал готовности приемника.

Слайд 44Функция арбитрации и селекции

Способ разрешения коллизий, возникающих при обращении

нескольких задатчиков

способ разрешения коллизий, возникающих при обращении

нескольких ПУ к ЦПр назовем селекцией. Принципы их реали -

зации одни и теже. Устройство для реализации функции арби-

трации – арбитр, для селекции – контроллер прерываний.

Слайд 47

Функция контроля: избыточное кодирование и режим тайм – аут.

Функция преобразования: из

Функция автоконфигурации: автоматическая конфигурация периферийных устройств при их подключении к компьютеру.

Функция управления питанием: управление электропотреблением

при разных состояниях компьютера, спецификация ACPI, технология OnNow

С точки зрения ACPI, всего имеется 4 состояния РС:

G0 – обычное рабочее состояние

G1 – suspend, спящий режим

G2 – soft-off, режим, когда питание отключено, но блок питания находится под напряжением, и машина готова включиться в любой момент

G3 – mechanical off – питание отключено напрочь

Слайд 48

Инициатива OnNow заключается в расширении состояния G1. Вместо простого засыпания, реализованного

S1: (standby 1) останавливаются тактовые генераторы CPU и всей системы, но при этом состояние памяти остается неизменным. Выход из

S1 осуществляется мгновенно.

S2: (standby 2) также останавливаются тактовые генераторы CPU и всей системы, но к тому же отключается питание кэша CPU и , а данные, хранившиеся там, сбрасываются в основную память. Включение также происходит достаточно быстро.

S3: (suspend-to-memory) по замыслу, именно этот режим должен был быть OnNow, но по воле разработчиков пока так не получилось. Должны обесточиваться все компоненты системы, кроме памяти, в которой сохраняются необходимые данные о состоянии CPU и кэша. Включение с восстановлением предыдущего состояния РС действительно происходит Now, т.е. практически сразу.

S4: (suspend-to-disk) то, что реализовано в каком-то виде сейчас. Все компоненты системы обесточиваются, данные о состоянии процессора и содержимое кэша и памяти записываются в специальное отведенное место на жестком диске. При этом пробуждение может занимать значительное время.

Функция горячего подключения ПУ. Эта функция позволяет отключать и подключать ПУ без остановки компьютера. При этом происходит автоконфигурирование включенного устройства без участия оператора.

Слайд 49Протоколы передачи данных в компьютерных интерфейсах

Два этапа: захват шины и передача данных.

1–ый этап: Арбитрация

1. Запрос задатчика арбитру на захват шины.

2. Арбитр анализирует приоритеты и выдает разрешение задатчику с наибольшим приоритетом.

3.Задатчик захватывает шину при ее переходе в состоя -ние холостого хода и выставляет сигнал занятости шины.

Селекция

1. Запрос ПУ к контроллеру прерываний на выполнение

операции ввода - вывода

2. Контроллер прерываний анализирует приоритет ПУ и выдает разрешение ПУ с наибольшим приоритетом.

3. ЦПр анализирует сигнал от контроллера прерываний,

прерывает свою работу и переходит к процессу ввода – вывода.

Слайд 50

2-ой этап: 1. Задатчик устанавливает адрес исполнителя.

3. При готовности задатчика и исполнителя начинается передача данных.

4. После передачи последнего слова шина переходит в состояние холостого хода.

Слайд 52

IRQ – запрос на прерывание от ПУ, INT – запрос от

INTA – сигнал разрешения передачи и чтеня вектора прерываний,

идет от ЦПр к КПр

Слайд 56Последовательный интерфейс

Протоколы последовательных интерфейсов используют те же принципы построения,

В случае последовательных компьютерных интерфейсов топология взаимосвязи устройств по этому интерфейсу осуществляется по принципу «точка-точка» или по схеме многоуровневой звезды, подобным сетевым структурам.

Последовательный интерфейс, как правило, соединяет главный контроллер (хост-контроллер) или просто контроллер системного блока компьютера с контроллером или адаптером периферийного устройства. Главный контроллер или просто контроллер взаимодействует с центральным процессором посредством интерфейса ввода/вывода (шина расширения, например, PCI).

Слайд 57

Прикладной уровень на стороне центрального процессора представляет из себя программное обеспечение,

Канальный уровень реализует протокол передачи данных между главным контроллером и ПУ. В общем случае между задатчиком и исполнителем.

Канальный уровень функционирует с блоками (кадрами или пакетами) данных и обеспечивает синхронизацию между приемником и передатчиком на уровне блоков. При такой синхронизации приемник должен распознать начало первого байта блока, распознавать границы полей блока и распознавать признаки конца блока.

Физический уровень представляет аппаратные и программные средства подключения ПУ к главному контроллеру или просто контроллеру, который находится в системном блоке компьютера через соответствующие порты ввода/вывода.

На физическом уровне в последовательном интерфейсе единицей информации является бит, поэтому средства физического уровня всегда поддерживают побитовую синхронизацию между приемником и передатчиком.

Слайд 58

Основными режимами передачи информации по последовательному интерфейсу являются асинхронная и синхронная

Тип протокола (асинхронный, синхронный) определяется по принципу синхронизации байта (символа) и блока. Асинхронный протокол: асинхронная передача байт (символов) и синхронный бит в байте. Синхронный протокол: синхронная передача байт, асинхронный – блоков.

Асинхронные протоколы представляют собой наиболее старый способ связи типа «точка-точка». Эти протоколы оперируют не с блоками, а с отдельными символами, которые представлены байтами и старт-стопными битами. Такой режим работы называют асинхронным или старт-стопным.

В синхронных протоколах обмен данными осуществляется блоками (кадрами, пакетами), которые имеют в общем случае заголовок, поле данных и концевик. Все биты блока передаются непрерывным синхронным потоком, что значительно ускоряет передачу данных.

Слайд 61Протоколы последовательной передачи данных используют две процедуры организации взаимодействия передатчика и

Передача кадра без установления соединения называется дейтаграммной процедурой. В этом случае передатчик никакой ответственности за утерю передаваемого кадра не несет.

Слайд 68Иерархия шин компьютера

Пр

Сев.

мост

Южн.

мост

Монитор

ОЗУ

Шина FSB

Шина памяти

Шина чипсет

Шина видео

PCI

PCI Expres

USB

ATA

Сеть

Набор системной логики

Слайд 71Шины верхнего уровня

Это шины соединяющие процессор с

шина переднего плана - FSB (Front-Side Bus)связь МПР с ОЗУ,

видеомонитором и ПУ скорость работы наибольшая.

-- шина заднего плана – BSB (Back – Side Bus), она быстрее, чем FSB, это шина для связи МПР с кэш-памятью второго уровня,

-- шина оперативной памяти для связи ОЗУ с FSB.

Частота процcора получается путем умножения номинальной частоты шины FSB на коэффициент умножения процессора.

Используемая Intel в настоящее время эволюция FSB – QPB, или Quad-Pumped Bus, способна передавать четыре блока данных за такт и два адреса за такт! То есть за каждый такт синхронизации шины по ней может быть передана команда либо четыре порции данных (напомним, что шина FSB–QPB имеет ширину 64 бит, то есть за такт может быть передано до 4х64=256 бит, или 32 байт данных). Итого, скажем, для частоты FSB, равной 200 МГц, эффективная частота передачи адреса для выборки данных будет эквивалентна 400 МГц (2х200 МГц), а самих данных – 800 МГц (4х200 МГц)3.

Слайд 72Характеристики шин FSB

Процессор частота

FSB Мггц способность FSB, Мб/с

Intel Pentium III 100/133 AGTL+ 800/1066

Intel Pentium 4 100/133/200 QPB 200/4266/6400

Intel Pentium D 133/200 QPB 4266/6400

Intel Pentium 4 EE 200/266 QPB 6400/8533

Intel Core 133/166 QPB 4266/5333

Intel Core 2 200/266 QPB 6400/8533

AMD Athlon 100/133 EV6 1600/2133

AMD Athlon XP 133/166/200 EV6 2133/2666/3200

AMD Sempron 800 HyperTransport 6400

AMD Athlon 64 800/1000 HyperTransport 6400/8000

Слайд 73

Процессор Core i7

Шина QPI.Ключевыми особенностями микроархитектуры Nehalem стали

Слайд 75Шина ISA

(Industry Standart Architekture)

Архитектура шины

Однопроцессорная

Трехшинная архитектура

8,16 разрядов данных,24 разряда

Асинхронная

Производительность 4мбайта/сек, частота 8мгц

11 линий прерывания,7 линий ПДП

Задатчики: ЦПр, КПДП, КРег, Пл.расш.

Имеется перестановщик байт

Блочной передачи нет

Два адресных пространства: ОЗУ, регистры Вв/Выв

Слайд 77Типы циклов шины

Ц Пр

Плата

расш.

Контр.

ПДП

Контр

рег.

16 р.

8 р.

16 р.

8 р.

16 р.

8 р.

ОЗУ

в/в.

ОЗУ

в/в.

ОЗУ,

ОЗУ

0 такт ожид.

норм. цикл

удл. цикл

норм. цикл

удл. цикл

чтение

запись

чтение

Тип задатчика

Тип ресурса

Тип памяти

Тип

цикла

Операция

Слайд 78Сигналы шины ISA

Сигналы адреса и данных

LA(Latchable Adres)[24-17] - адрес без «защелкивания»

SD(System data)[15-0] – данные

# SBHE(System Bus High Enable) – передача старшего байта

BALE(Bus Adres Latch Enable) – строб адреса

AEN(Adres Enable) – разрешение ПДП

Сигналы команд

# MEMR(Memory Read) – чтение ОЗУ

# MEMW(Memory Write) – запись ОЗУ

# I/OR(Input Output Read) – чтение Вв-Выв

# I/OU(Input Output Write) – запись Вв-Выв

# MEMCS16(Memory Cycle Select) – 16раз. ОЗУ

# I/OCS16(Input Output Cycle Select) – 16раз. Вв-Выв

I/OCHRDY(I/O Cannel Ready) – готовность Вв-Выв

#OWS(O Wite States) – 0 циклов ожидания

# REFRESH – регенерация ОЗУ

Слайд 79 Сигналы управления

# Master – задатчик внешней платы

RESET – сброс

SYSCLC(System Clock) – синхроимпульсы,8мгц

OSC – генерация сигналов с частотой 12.3818мгц

Сигналы прерывания

IRQ(Interrup ReQuest) – сигналы прерывания

[15,14,12,11,10],[976543]

DRQ(Direct memory access ReQuest) – запрос ПДП

[7,6,5,0],[3,2,1]

DACK(DMA Request Acknowledge] – разрешение ПДП

[7,6,5,0],[3,2,1]

T/C(Terminal Count) – окончание ПДП

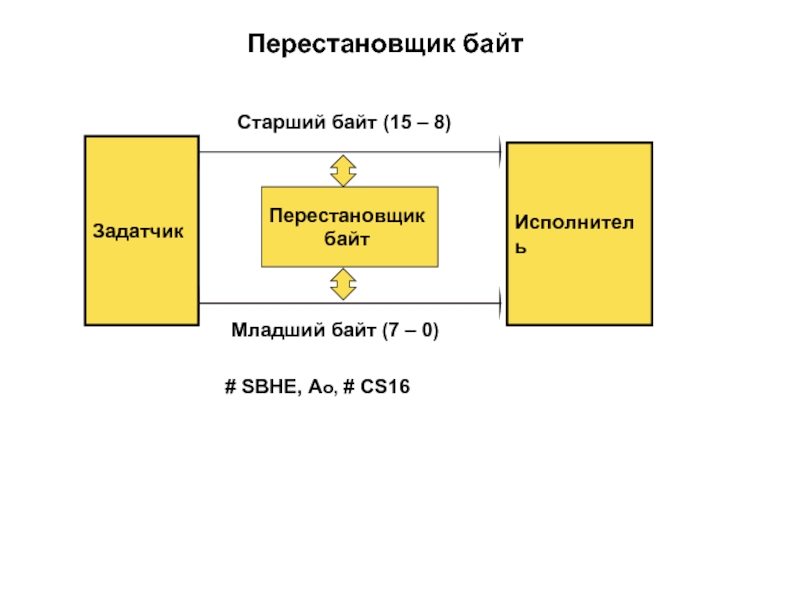

Слайд 80

Задатчик

Исполнитель

Перестановщик

байт

Старший байт (15 – 8)

Младший байт (7 – 0)

# SBHE, Ao, # CS16

Слайд 83Шина PCI

(Peripheral Component Interconnect)

Базовая версия PCI:

Тактовая

Пиковая пропускная способность 133 МБ в секунду;

Параллельная шина данных шириною 32-бита;

Адресное пространство 32-бита (4 ГБ);

Сигнальный уровень 3.3 или 5 вольт.

Слайд 84Позже появляются следующие ключевые модификации шины:

PCI 2.2 — допускается 64-бит ширина

PCI-X, 64-бит версия PCI 2.2 с увеличенной до 133 МГц частотой (пиковая пропускная полоса 1066 МБ/сек.);

PCI-X 266 (PCI-X DDR), DDR версия PCI-X (эффективная частота 266 МГц, реальная 133 МГц с передачей по обоим фронтам тактового сигнала, пиковая пропускная полоса 2.1 ГБ/сек);

PCI-X 533 (PCI-X QDR), QDR версия PCI-X (эффективная частота 533 МГц, пиковая пропускная полоса 4.3 ГБ/сек.);

Mini PCI — PCI с разъемом в стиле SO-DIMM, применяется преимущественно для миниатюрных сетевых, модемных и прочих карточек в ноутбуках;

Compact PCI — стандарт на форм фактор (модули вставляются с торца в шкаф с общей шиной на задней плоскости) и разъем, предназначенные в первую очередь для промышленных компьютеров и других критических применений; развитие – PXI.

Слайд 85многопроцессорная;

двухшинная архитектура;

32, 64 – разрядная адресация данных;

синхронная шина;

производительность 133 Мбайт/сек –

пакетная передача данных, транзакции;

арбитрация;

таймер-задержка;

два метода адресации;

три адресных пространства: ОЗУ, регистры ввода/вывода, регистры автоконфигурации;

поддержка автоконфигурации;

контроль четности.

Архитектура шины

Слайд 86

Пр

Пр

ОЗУ

Контр. ОЗУ

Авто конф.

Арб.

Исп.

Зад.

Мост

П У

PCI, ISA

IDSEL

IDSEL

GRN

REQ

Главный мост

PCI – A/D, Управл.

Слайд 87Базовые сигналы шины PCI

AD[31-0] – адрес – данные;

C/BE[3-0] – код команды,

#FRAME – начало и конец транзакции;

#DEVSEL – исполнитель найден;

#IRDY – готовность задатчика, строб данных;

#TRDY – готовность исполнителя, строб данных;

#STOP – прерывание транзакции от исполнителя;

#LOCK – выполнение нескольких транзакций;

#REQ – запрос на захват шины;

#GNT – разрешение на захват шины;

IDSEL – выбор устройства при автоконфигурации;

PAR – контроль по четности A/D, C/BE;

#PERR – ошибка паритета;

#SERR – системная ошибка;

#RST – сброс;

CLK – синхроимпульс.

Слайд 89

Тц

цикл

tзад

фаза

ФА

ФД1

ФД2

ФДn

X.Xод

Х.Ход

Транзакция

Циклы ожидания

Цикл передачи данных

Фаза данных

Последняя фаза данных

СИ(CLK)

Сигналы на шине

Слайд 93

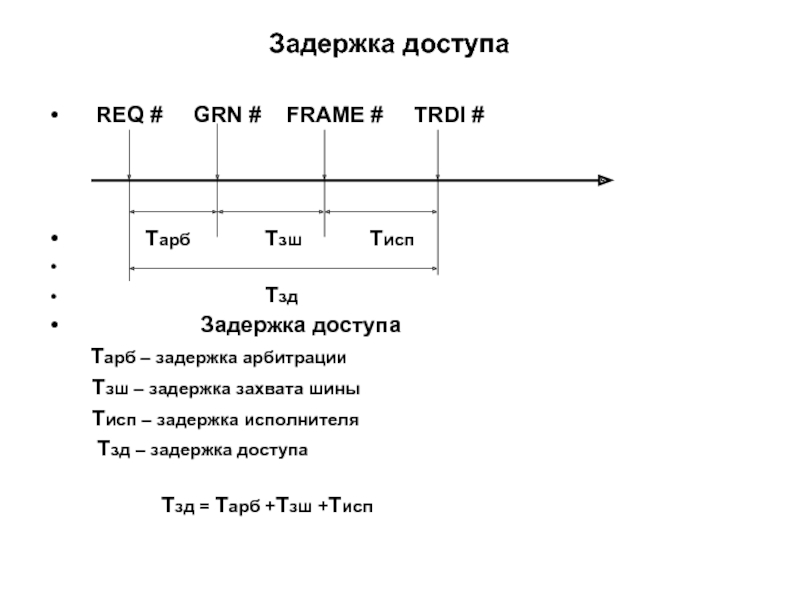

REQ # GRN # FRAME # TRDI #

Тарб Тзш Тисп

Тзд

Задержка доступа

Тарб – задержка арбитрации

Тзш – задержка захвата шины

Тисп – задержка исполнителя

Тзд – задержка доступа

Тзд = Тарб +Тзш +Тисп

Слайд 94

31 16 15 0

0 идентификатор устройства

Идентиф. пройзводителя

1 состояние

команда

2 Код класса

Идент. версии

3 самотест.

Тип заголов.

Таймер задер.

Размер КЭШ

15

16

63

Слайд 96 шина(порт) AGP

AGP построен на базе шины PCI.

32 разряда адреса/данных,частота 66мггц

Высокая производительность за счет:

1.Конвейеризации обращения к памяти.

2.Умножении частоты передачи данных

по отношению к 66мггц(2х,4х,8х).

3.Демультипликация шины адреса/дан-

ных.

Слайд 98 Производительность шины

AGP1х-266мбайт/сек

AGP2х-533мбайт/сек

AGP4x-1066мбайт/сек

Слайд 99PCI Express, на стадии проектирования была также известна как 3GIO (Ввод-вывод

Дата рождения — 22 июля 2002 года — опубликована базовая спецификация протокола и сигнального уровня, а также базовая спецификация на форм-фактор и энергопотребление карт и разъемы

Три версии шины к 2011 г.: PCIe1= 2,5 Гбит/с, PCIe2= 5 Гбит/с, PCIe3=8Гбит/с .

К 2015г.- PCIe4=16Гбит/с.

Слайд 100

PCIExpress- последовательная шина, использующая дуплексный принцип передачи данных по 2 проводам,

емым линией. Данные передаются в виде пакетов определенного формата.

Соединение между двумя устройствами PCI Express состоит из одной (x1) или нескольких (x2, x4, x8, x12, x16 и x32) двунаправленных последовательных линий. Передача данных происходит одновременно по каждой линии путем распределения байт по этим линиям. Совокупность линий образуют последовательную шину с пакетной передачей данных.Каждое устройство должно поддерживать по крайней мере соединение с одной линией (x1).

Слайд 102Каждый байт (8 бит) данных, по определенной схеме кодирует - ся

В PCI Express 3.0 используется более экономное кодирование 128b/130b с избыточностью 1,5%.

Слайд 103

PCI Express относится к шинам класса «точка-точка», то есть одна шина

Программная модель PCI Express во многом унаследована от PCI, то существующие системы и контроллеры могут быть доработаны для использования шины PCI Express заменой только физического уровня, без доработки программного обеспечения.

Слайд 104Вся контрольная информация передается по тем же линиям что и данные,

Стандарт предусматривает и альтернативные носители сигнала, такие как оптические волноводы;

Возможность динамического подключения и конфигурации устройств;

Возможность распознавания и использования альтернативных (улучшенных) протоколов обмена.

Автоконфигурация

Три адресных пространства: ОЗУ,Ввод-вывод, автоконфигурация,Сообщения.

Эффективная скорость передачи данных на шине определяется произведением частоты на количество линий с учетом дуплексности и избыточности 8b/10b – 20%,128/130 – 1,5% потерь

Слайд 106Многоуровневая модель шины PCIe

PCI Express использует традиционную многоуровневую модель, аналогичную

На этом уровне по-прежнему сохраняется стопроцентная совместимость с уже существующей моделью PCI Plug`n`Play (PnP) — все старые операционные системы как работали с PCI, так и будут работать с PCI Express.

Слайд 108

Спуск еще на уровень по схеме — и мы попадаем в

Прежде всего, добавлено два новых уровня (Transaction Layer и Link Layer), которых иначе как TCP и IP не назовешь — выполняемые функции абсолютно те же, что и у «сетевых» аналогов. Transaction Layer получает запросы на чтение и запись от программного уровня и заведует первоначальной упаковкой данных, передачей их конкретному получателю и гарантиями корректной доставки сообщения

Link Layer заведует более приземленными делами - здесь указывается уникальный номер пакета (его маршрутизация осуществляется по заголовку, относящемуся к транспортному уровню), по которому контроллеры шины принимают решение о направлении пакета в конкретную физическую линию передачи данных, здесь же располагается код обнаружения и исправления ошибок в принятом пакете (CRC), номер пакета, позволяющий отличить один пакет от другого, и разная вспомогательная информация

Слайд 109

Frame — начальный и конечный фрейм пакета - его добавляет физический

Packet # — номер пакета, добавляется на сетевом уровне чтобы пакеты можно было отличить друг от друга;

Header — заголовок пакета, описывает тип пакета, получателя, приоритет и другие свойства, это информация транспортного уровня;

Data — собственно данные пакеты;

CRC — контрольная сумма пакета.

Слайд 110Fmt — указание типа заголовка (12 или 16 байт) и признак

Type — тип пакета (один из четырех основных типов - Memory, I/O, Config, Message и бит, определяющий запрос это или ответ на запрос);

RequestorID — получатель пакета (шина, устройство, функция устройства);

Reserved — зарезервированное поле;

Traffic Class — используется для маршрутизации;

Address/Routing — адрес в памяти, куда предназначается пакет (32- или 64-разрядный) или иная информация о маршрутизации пакета;

Length — объем передаваемых в пакете данных;

Attr — вспомогательные атрибуты пакета (Snoop, Ordering);

Tag — идентификатор транзакции (Transaction Tag);

Reserved — зарезервированное поле;

Byte Enables — вспомогательная информация.

Слайд 112Самый простой вариант перехода на PCI-Express для

стандартных по архитектуре настольных систем

Слайд 113 Однако в будущем логично ожидать появление некоего разветвителя

Слайд 117Шина HyperTransport

Технология HyperTransport (ранее известная как Lightning Data Transport) – это

Слайд 120

На данный момент консорциумом HyperTransport разработана уже третья версия спецификации, согласно

Полноразмерная (32-битная) полноскоростная (2,6 ГГц) шина способна обеспечить пропускную способность до 20800 МБ/с (2*(32/8)*2600) в каждую сторону, являясь на сегодняшний день самой быстрой шиной среди себе подобных.

Слайд 125

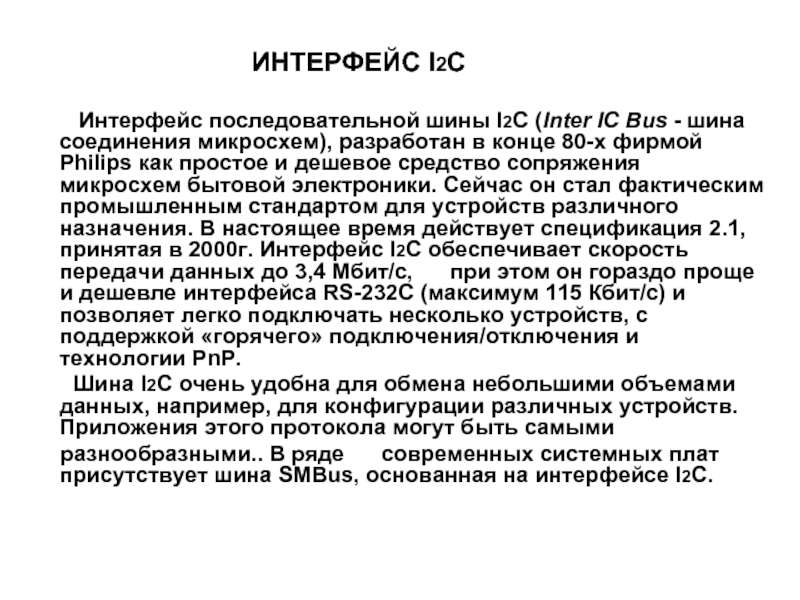

Интерфейс последовательной шины I2C (Inter IС Bus - шина соединения микросхем), разработан в конце 80-х фирмой Philips как простое и дешевое средство сопряжения микросхем бытовой электроники. Сейчас он стал фактическим промышленным стандартом для устройств различного назначения. В настоящее время действует спецификация 2.1, принятая в 2000г. Интерфейс I2C обеспечивает скорость передачи данных до 3,4 Мбит/с, при этом он гораздо проще и дешевле интерфейса RS-232C (максимум 115 Кбит/с) и позволяет легко подключать несколько устройств, с поддержкой «горячего» подключения/отключения и технологии РnР.

Шина I2C очень удобна для обмена небольшими объемами данных, например, для конфигурации различных устройств. Приложения этого протокола могут быть самыми

разнообразными.. В ряде современных системных плат присутствует шина SMBus, основанная на интерфейсе I2C.

Слайд 126

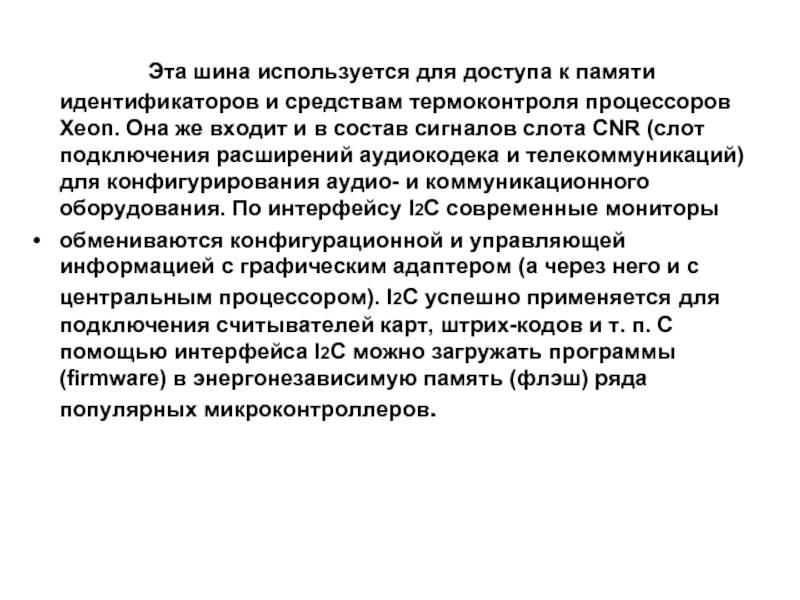

Эта шина используется для доступа

обмениваются конфигурационной и управляющей информацией с графическим адаптером (а через него и с центральным процессором). I2C успешно применяется для подключения считывателей карт, штрих-кодов и т. п. С помощью интерфейса I2C можно загружать программы (firmware) в энергонезависимую память (флэш) ряда популярных микроконтроллеров.

Слайд 127

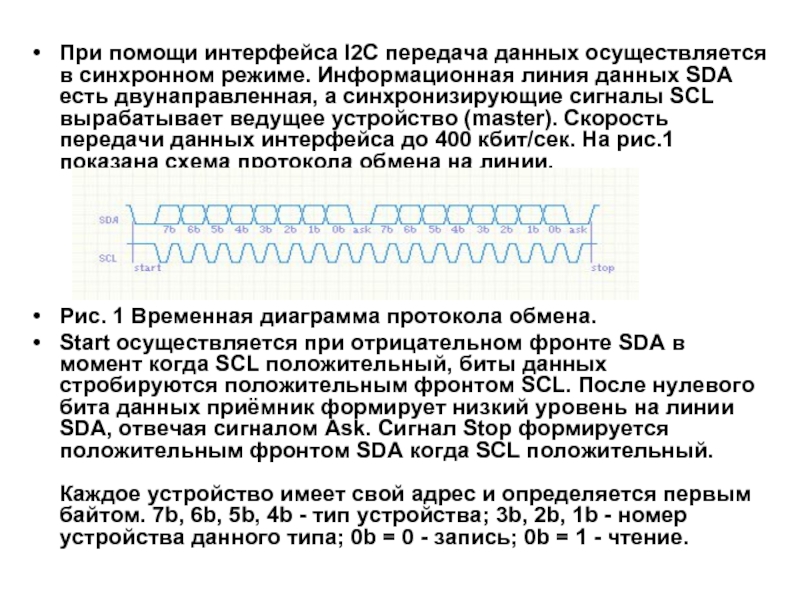

При помощи интерфейса I2C передача данных осуществляется в синхронном режиме. Информационная

Рис. 1 Временная диаграмма протокола обмена.

Start осуществляется при отрицательном фронте SDA в момент когда SCL положительный, биты данных стробируются положительным фронтом SCL. После нулевого бита данных приёмник формирует низкий уровень на линии SDA, отвечая сигналом Ask. Сигнал Stop формируется положительным фронтом SDA когда SCL положительный. Каждое устройство имеет свой адрес и определяется первым байтом. 7b, 6b, 5b, 4b - тип устройства; 3b, 2b, 1b - номер устройства данного типа; 0b = 0 - запись; 0b = 1 - чтение.

Слайд 140Архитектура шины

1.Общая шина, параллельный, полудуплексный.

2.Двух шинная архитектура, шина А/Д

3.Шлейфовое подключение ПУ.

4.Интерфейс асинхронный, синхронная и асинхронная передача данных.

5.Арбитрация распределенная, без специальных линий, используются линии А/Д.

6.Два типа устройств на шине:инициализирующее устройство(ИУ)

(Master Device), обычно - главный контроллер, управляет процессом передачи данных; целевое устройство(ЦУ), контроллер – управляет до 8 ПУ, или многофункциональным.

7.К шине может подключается одно ИУ и 7 или 15 ЦУ.

7.Адресация ПУ двух уровневая: унитарный идентификатор(8,16)

разрядов для ИУ и ЦУ, 3 разряда в дескрипторе команды – логический адрес ПУ, подключенному к ИУ.

9.Шина SCSI является мультиплексной по отношению к ПУ.

Слайд 141 Структура SCSI, шина А/Д –

Хост контроллер

лу1

лу2

лу1

ЦУ 1

ЦУ 2

ЦУ 15

ПУ1

ПУ2

ПУ3

Терминатор

…

лу1

лу3

лу2

ПУ4

ПУ5

ПУ6

Идентификатор ИУ – 1000000000000000

Идентификатор ЦУ - 0000010000000000

Высший уровень приоритета –1000000000000000

Низший уровень приоритета - 0000000000000001

Слайд 144Протокол передачи данных

Передача данных ведется в асинхронном или синхронном

режимах.

данные

данные

REQ

ACK

Слайд 145Фазы шины

Процесс передачи данных реализуется в виде последовательнос-

ти определенной этапов работы

1.Bus Free – шина свободна

2.Arbitration – выбор устройства с наивысшим приоритетом

3.Selektion – адресация ЦУ

4.Reselektion – возобновление прерванной команды

5.Command – передача комманды

6.Data In – ввод данных

7.Data Out- вывод данных

8.Status – передача состояния ЦУ

9.Message In – ввод сообщения

10.Message Out – вывод сообщения

Каждая фаза идентифицируется определенным набором

сигналов шины, выдаваемых ИУ и ЦУ.

Слайд 148Фаза сообщений (message In/Out)

Код сообщения

- 1 байт

7

0

Код сообщения

Аргумент

- 2

01h

Код сообщения

Длина

- 3 байта

Расширенное сообщение

Команды

Общие

Специальные

Обязательные

Дополнительные

Фирменные

Слайд 149Дескриптор команд

Op code

7

0

LUN

Length

Control

5

4

0

1

2

3

4

5

В команде 6 байт, 10 байт, 12 байт

LBA

6

10, 12 – 32 бит

6 – 1 байт

10 – 2 байта

12 – 4 байта

10, 12 имеют 1 байт резерва

Слайд 150Процесс ввода - вывода

Прцесс ввода – вывода содержит две части:

-- установка

-- непосредственно передача данных

Процесс может прерываться и снова возобновляться. С этой целью шина сохраняет для каждого процесса три указателя:

команду, состояние и данные. ИУ имеет текущий набор указателей и наборы указателей прерванных процессов.

Шина SCSI стандартизует наборы команд для управления различными типами ПУ, таких типов имеется 14. Например:

Устройства прямого доступа.

Устройства последовательного доступа.

Принтеры.

Привод CD-ROM.

Сканеры.

Коммуникационные устройства.

Слайд 152Архитектура шины USB

1. Последовательная передача данных.

2. Полудуплексный режим передачи.

3. Принцип действия

4. Максимальное количество подключаемых ПУ – 127.

5. Скорость передачи: USB1 - 1,5 Мбит/сек, низкая сорость(LS)

12 Мбит/сек,полная скорость(FS)

USB2 - 480 Мбит/сек,высокая скорость(HS)

USB3 – 5 Гбит/сек

6. Наличие автоконфигурации.

7. Горячее подключение.

8. Возможно питание от шины.

9. Топология шины – многоуровневая звезда.

Слайд 153Структура шины

В ней используются сетевые принципы построения шины. В основе

структуры лежат

ют из себя сетевые концентраторы, являющиеся центрами многоуров –

невой звезды, к которым кабелем подключатся функции(ПУ).

Могут быть комбинированные устройства, содержащие как хаб так и

функцию(ПУ).

Компьютер имеет хост – контроллер, содержащий корневой хаб,

имеющий одну или несколько точек подключения.

Хаб имеет один восходящий и несколько низходящих портов.

Функции хаба.

Распознает подключение или отключение устройства к порту.

Управляет подачей питания на подключенное устройство.

Может разрешить или запретить использование порта.

Обеспечивает. изоляцию сегментов с низкой скоростью от

Высокоскоростных.

Структура имеет топологию – многоуровневой звезды.

Слайд 157Физический интерфейс USB

Кабель имеет 4 провода: два для передачи сигналов(Д+ и

подачи питания (5в). Дифференциальный способ передачи сигналов.

Передатчик должен иметь 3-е высокоимпедансное состояние, для

реализации полудуплексного режима передачи данных.

Кроме дифференциального сигнала приемник и передатчик могут ра-

ботать и с линейными сигналами. Это дает возможность иметь более

двух состояний линий. Следующие состояния линий:

- линейный ноль (SEO,Singl-Endet Zero): – Д + и Д – низкий уровень,

состояние передаваемых бит : Data J State( J ), Data K State( K ),

- Пауза на шине: Idle State,

- сигнал «пробуждения» : Resume State,

- начало пакета: Start of Packet – переход из Idle State в состояние К,

конец пакета: End of Packed,

устройство отключено от порта: Disconnekt,

устройство подключено к порту: Connekt,

- сброс устройства: Reset.

Слайд 159Кодирование информации

Используется NRZI – кодирование.

0 0 0 0 0 0

NRZI

Об. код

NRZI – код: переключение сигнала происходит только при переходе из 1 в 0

и из 0 в 0.

Если подряд идет более 6 единиц, то после шестой вставляется 0.

Слайд 161Типы передачи данных

1. Управляющие – конфигурирование и управление устройствами.

квитированием. Control transfer.

2. Сплошные – передача больших блоков без жестких требований по

времени доставки. Поле данных пакета не более 64байт. Асинхрон-

ная с квитированием. Bulk data transfer.

3. С прерываниями – короткие передачи типа символа. Асинхронная с квитированием. Interrupt.

4. Изохронные – непрерывная передача в реальном времени с заданной задержкой доставки, например аудио, видео.

Слайд 163Модель передачи данных

Данные передаются между хост– контроллером и функцией(ПУ) в виде

потоков

Возможны передачи только между хост – контроллером и ПУ.

Функция представляется в виде логического устройства, состоящего из

набора конечных точек (End Point, ЕР) – регистров. Каждое логическое

устройство имеет свой адрес, каждая конечная точка идентифицирует-

ся своим номером. В низкоскоростных устройствах 3, а в высокоскоро-

тных до16 ЕР. Каждое устройство должно иметь ЕР с номером 0, через

которую осуществляется конфигурирование и управление устройством.

Для решения задачи в устройстве имеется набор из несколько ЕР, на-

зываемых интерфейсом задачи. Если выполняется несколько задач,

устройство имеет несколько интерфейсов. Набор одновременно под-

держиваемых интерфейсов составляет конфигурацию устройства.

Каждая конечная точка(ЕР) имеет набор характеристик.

Слайд 164Характеристики конечной точки

1.Требуемая частота доступа и задержка обслуживания.

2. Тpебуемая частота прoпускания

3. Номер точки.

4. Требования к обработке ошибок.

5. Максимальный размер пакетов.

6. Тип обмена.

7. Направление обмена.

При конфигурации между драйвером устройства и конечно точкой ус –

танавливаются коммуникационные каналы(communication pipe). Пере-

дача информации между ними производится в виде транзакций.

Имеется два типа каналов:

Потоковый – однонаправленный, реализует сплошной, с прерывания –

ми и изохронный тип передачи, без определенной структуры.

Сообщений – двунаправленный, реализует управляющий тип переда –

чи, имеет формат определяемый спецификацией USB.

Слайд 165Структура модели

Драйвер

USB

EP

EP

EP

EP

EP0

Драйверы устройств

интерфейсы

Устройство USB

Каналы

Каналы

Хост- контроллер

Основной канал

сообщений

Слайд 166Протокол шины USB

Протокол шины USB обеспечивает обмен данными между хостом и

тройством. Используется мультиплексирование данных с временным

уплотнением. Единицей передаваемой информации является транзак-

ция, состоящая из двух - трех пакетов. Хост-контроллер циклически

с периодом 1мс(USB1) или 125 мкс(USB2) для обмена с устройствами

формирует кадры, содержащиe несколько транзакций. Кадры переда –

ются согласно плану распределения ресурсов. Каждый кадр начинает-

ся с пакета-маркера начала кадра SOF (Start Of Frame), а заканчивает-

cя интервалом времени EOF(End Of Frame). Кадры нумеруются поcле -

довательно. В маркере SOF передаются 11 младших бит номера кадра

Кадр i - 1

Кадр i

Кадр i +1

EOP SOF

Слайд 167Транзакции и пакеты

Транзакция содержит определенную последовательность пкетов.

Пакет начинается с синхропоследовательности, один

В коде NRZI: 10101011. Две 1 означает начало информационной части

пакетаSOP(Start Of Packet). Пакет заканчивается сигналом конца паке-

таEOP (End Of Packet) – переводом обеих линий данных в низкое сос -

тояние SEO (Singl-Ended Zero).

В зависимости от назначения пакет имеет 3 формата.

Маркер, пакет данных и пакет квитирования. Каждый пакет начинается

c их идентификатора PID. Код PID задает тип пакета, т.е. его назначе –

ние и функцию. Пакет квитирования имеет только поле PID.

Слайд 176Типы пакетов квитирования

ACK – подтверждение безошибочного приема пакета.

NAK – индикация занятости

STALL – конечная точка требует вмешательство хоста. Серьезная

ошибка.

NYET – безошибочный прием, но отсутствует место для следующего

пакента.

Типы пакетов маркеров

OUT, IN, SETAP, SOF.

Устойчивость к ошибкам

Все принимаемые пакеты проверяются на ошибки.

Дублирование PID.

CRC код.

Вставка бит.

Счетчик тайм-аута

Слайд 182

Беспроводные (wireless) интерфейсы позволяют освободить устройства от связывающих их интерфейсных кабелей, что особенно привлекательно для малогабаритной периферии, по размеру и весу соизмеримой с кабелями. В беспроводных интерфейсах используются электромагнитные волны инфракрасного (IrDA) и радиочастотного (Bluetooth)

диапазонов. Кроме этих интерфейсов периферийных устройств существуют и беспроводные способы подключения к локальным сетям.

Слайд 183Интерфейсы устройств хранения

(внешних запоминающих устройств – ВЗУ)

ВЗУ обеспечивают энергонезависимое

информации на каком либо физическом носителе. Наибольшее рас –

пространение получили три вида носителей.

1.Магнитные: диски и ленты.

2.Оптические: CD и DVD диски.

3.Электрические, твердотельные: флэш – память, флэш – карты

(CompactFlash, SmartMedia Card, MultiMedia card, и др.)

ВЗУ делятся на устройства с прямым доступом – диски, флэш – память

и с последовательным доступом – магнитные ленты.

ВЗУ бывают внутренние, размещаемые в корпусе компьютера и внеш –

ние, переносные, подключаемые к внешним портам компьютера.

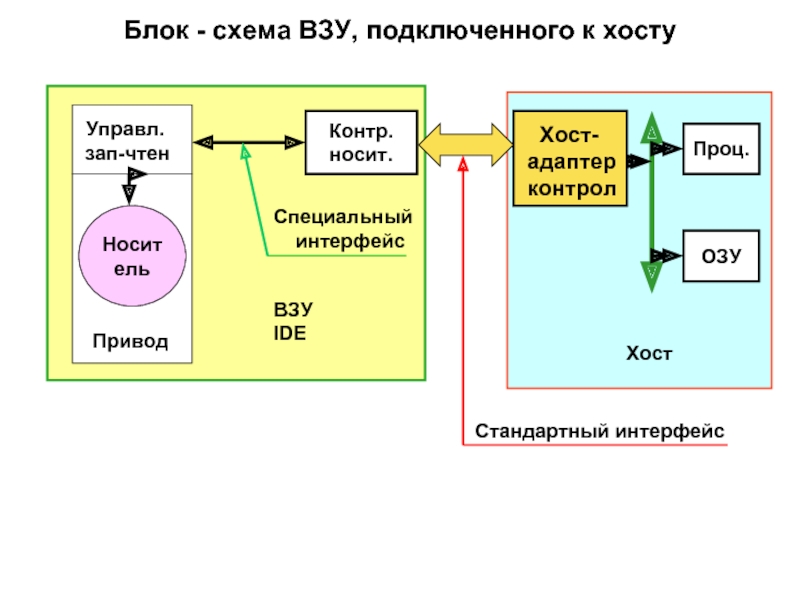

Слайд 184

Контроллер носителя как правило встроен в устройство хранения и

соединяется с

специального интерфейса. Сами ВЗУ соединяются с контроллером

хоста с помощью стандартных интерфейсов.

Слайд 185Блок - схема ВЗУ, подключенного к хосту

Проц.

ОЗУ

Контр.

носит.

Управл.

зап-чтен

Носитель

Привод

Специальный

интерфейс

Хост

ВЗУ

IDE

Стандартный

Хост-

адаптер

контрол

Слайд 186Стандартные интерфейсы ВЗУ

К этим интерфейсам относятся.

Интерфейсы IDE для

(ATA – AT Attachment for Disk Drives. ATAPI – ATA Package Interfeis,

SATA – Serial ATA), универсальные интерфейсы SCSI, USB, Fire Wire

Интерфейсы IDE, SCSI для внутренних ВЗУ, SCSI, USB, Fire Wire для

внешних.

Операции обмена хоста с ВЗУ всегда блочные. Блок – неделимая еди -

ница хранения, имеющая свой адрес. Размер блока может быть

фиксированным или произвольным, наиболее распространен блок с

фиксированным размером в 512 байт.

Адресация блока производится различными способами. Наиболее

проста и удобна – линейная адресация – каждый блок адресуется

oдномерным адресом LBA(Logik Blok Adress) Для дисков может исполь-

зоваться трехмерная адресация: цилиндр, головка, сектор.

Трехмерная адресация имеет предел емкости накопителя в 137Гбайт.

Линейная – 137,4 при 28 разрядах адреса, 2,2Тбайта при 32-х разрядах

и 144Пбайт при 48 разрядах.

Слайд 187Интерфейс ATA / ATAPI

ATA/ATAPI – 16 разрядный

которого устройство хранение IDE подключается к компьютеру.

Устройство хранения посредством плоского 80 проводного кабеля со –

единяется с контроллером (хост-адаптером) компьютера, подключен –

ным к его внутренней шине расширения (ввода-вывода) – PCI, обычно

используется контроллер PCI IDE Bus Master. Контроллер имеет свой

контроллер DMA. Он может обслуживать несколько каналов(шин АТА),

к каждому каналу можно подключить до 2 –х устройств IDE.

Интерфейс АТА появился в 1980 году для подключения накопителя на

жестких магнитных дисках к компьютеру IBM PC AT c шиной ISA.

Поэтому набор сигналов шины АТА подобен сигналам шины ISA.

Интерфейс ATA/ATAPI использует два типа режимов обмена.

1.PIO(Programmed Input/Output) – программный ввод-вывод, управляет

процессор.

2.DMA – прямой доступ к памяти, процессом ввода-вывода управляет

контроллер DMA.

Слайд 188Сигналы шины АТА/ATAPI - 4

RESET# (Device Reset) – сброс устройства.

DA[2:0] (Device

DD[15:0] (Device Data) – 16 битная шина данных.

DIOR# (Device I/O Read) – строб чтения.

DIOW# (Device I/O Write) – строб записи.

IORDY (I/O channel Ready) – готовность устройства завершить обмен.

IOCS16# - разрешение 16 битных операций.

DMARQ (DMA Request) – запрос обмена по каналу DMA.

DMACK# (DMA Acknowledge) – подтверждение DMA.

INTRQ (Interrupt Request) – запрос прерывания.

CS0,# CS1# (Chip Select0,1) – выбор регистров командного и управля -

ющего блоков.

PDIAG# (Passed Diagnostics) – прохождение диагностики.

CBLID# (Cable assembly type identifier) – идентификация типа кабеля.

DASP# (Devise Active, Slave Present) – активность или ведомое устр.

SPSYNC/CSEL (Spindle Synchronization/Cable Select) – синхронизация

шпинделя или выборка кабелем.

Слайд 189Режимы передачи данных

Интерфейс ATA/ATAPI использует два типа режимов обмена.

1.PIO(Programmed Input/Output)

процессор.

2.DMA – прямой доступ к памяти, процессом ввода-вывода управляет

контроллер DMA.

Одиночный режим(Singleword DMA),один цикл обмена на один сигнал

DMARQ.

Множественный режим(Multiword DMA), на один сигнал DMARQ

несколько циклов обмена.

Режим Ultra DMA, передача за один такт двух слов по переднему и

заднему фронтам, использование 80-проводного кабеля.

Интерфейc ATAPI – развитее АТА для других устройств, кроме жест –

ких магнитных дисков. Этот интерфейс позволяет передавать пакет,

содержащий командный блок, подобный шине SCSI. Это дает возмож -

ность расширить применение шины АТА на другие устройства введя

всего лишь одну новую команду.

Слайд 190Скорость передачи данных при различных режимах

После 1980 года появилось 18 разновидностей

личающихся скоростью передачи. Вот некоторые из них.

Интерфейс АТА: PIO mode 0,1,2,3; Singleword DMA Mode 0,1,2;

Multiword DMA Mode 0. ATA-2: Multiword DMA Mode 1. Fast ATA.

ATA/ATAPI 4,5,6,7: UltraDMA Mode 0,1,2,3,4,5,6. Вот некоторые из них.

PIO mode 0 - 3,3 Мбайт/с

PIO mode 4 – 16,6 Мбайт/с

Singleword DMA Mode 0 – 2,08 Мбайт/с

Singleword DMA Mode 2 – 8,33 Мбайт/с

UltraDMA Mode 0 – 16,6 Мбайт/с

UltraDMA Mode 5 – 100 Мбайт/с

UltraDMA Mode 6 – 133 Мбайт/с

Правильный выбор режима работы обеспечивает надежность и произ-

водительность обмена.

Слайд 191Интерфейс Serial ATA (SATA)

SATA – последовательный интерфейс, позволивший

скорость обмена и существенно упростить средства соединения хоста

с устройством. Достоинства интерфейса.

1.Повышение скорости обмена, базовая скорость 150 Мбайт/с, возмож-

но ее увеличение.

2.Расширенный адрес 48 бит.

3.Возможность подключения каждого устройства к собственному порту

контроллера хоста.

4.Возможность работы контроллера сразу с несколькими устройствами

5.Упрощаются и удешевляются кабели и разъемы.

SATA сохраняет работу в режимах PIO и DMA, преемственность

команд и совместимость программного обеспечения ATA/ATAPI.

SATA имеет другой более интеллектуальный контроллер хоста в соот-

ветствии со спецификацией нового программного интерфейса AHCI.

Стандарт SATA рассматривает 4 – х уровневую модель взаимодей –

ствия хоста и устройства SATA.

Слайд 192Четырехурвневая модель интерфейса SATA

Имеется 4 уровня: прикладной, транспортный, канальный и физический

1.Прикладной

состоянии и хранимыми данными.

2.Транспортный конструирует пакеты, называемые информационными

структурами – FIS(Frame Information Structure), которыми обменива –

ются контроллер и устройство. Он передает их канальному уровню.

FIS от канального разбирает на составные части и передает приклад –

ному.

3.Канальный из FIS конструирует кадры, добавляя к ним примитивы,

определяющие начало и конец кадра, а также служащие для управле-

ния потоком передаваемых данных и контрольный CRC код. Выпол –

ет кодирование 8В/10В и передает кадры в виде битовых потоков

физическому уровню. Битовые потоки от физического уровня преобра-

зует в FIS и передает транспортному уровню. Со своим партнером(ка-

нальным уровнем противоположной стороны интерфейса) обменива –

ется подтверждением успешного приема кадра.

Слайд 193

4.Физический уровень. Передача информации производится по двум

экранированным парам проводов

сигналов с использованием NRZ-кодирования. Данные по кабелю пе –

редаются со скоростью 1,5 Гбит/с или 150 Мбайт/с(с учетом 8В/10В

кодирования).Далее предполагается повысить эту скорость. Исполь –

зуются битовая и символьная синхронизации.

Дальнейшее развитие SATA является стандарт SATA II. Его отличия.

1.Работа с мультиплексором портов, позволяющем подключать к одно-

му порту несколько устройств, и селектором портов дающем возмож-

ность работы одного устройства с несколькими хостами.

2.Возможность подключения внешних по отношению к компьютеру ус –

тройств

3.Эффективное обслуживание очередей.

4.Контроллер SATA II приближается по свом возможностям к SCSI.

Появился интерфейс SATA 3 со скоростью 6 Гбит/сек.

На базе SATA появился миниатюрный интерфейс mini – SATA(mSATA)

Слайд 194Внешние системы хранения данных

SEMBR (Serial ATA enclosure management bridge) – мост

SEP(Storage Enclosure Processor) – обслуживающий процессор с фун –

кциями: поддержание климата, контроль питания, защита от не санкци-

онированного доступа и др. - последовательный интерфейс.

Хост

Хост

Селектор порта

Мультиплексор портов

SEMB

SEP

Система

хранения

данных

Устройства хранения

SATA

Слайд 195Интерфейсы флэш - памяти

Для подключения USB – флэш – памяти используется

интерфейс USB 2.0.

Для подключения флэш – карт используются разные интерфейсы в за –

висимости от типа карты. Например, для карты CompactFlash в зависи-

мости от режима работы используют интерфецсы, сопрягаемые или

с интерфейсом PC Card или с IDE (ATA).

Слайд 197 Чипсет(Chipset)

Чипсет - набор

фейсом между составными частями компьюте-

ра: ЦПр,ОЗУ,ПЗУ,порты ввода-вывода.

Обычно это две микросхемы: южный мост и

северный мост.

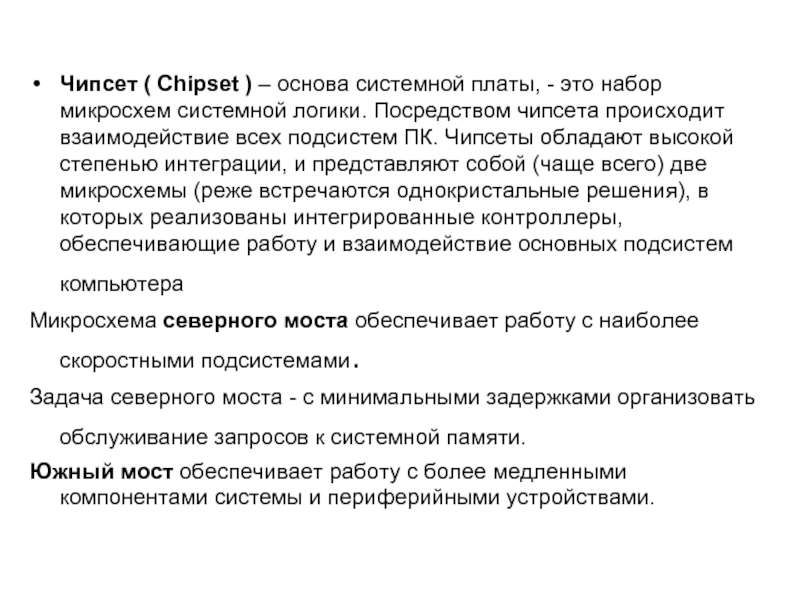

Слайд 198

Чипсет ( Chipset ) – основа системной платы, - это набор

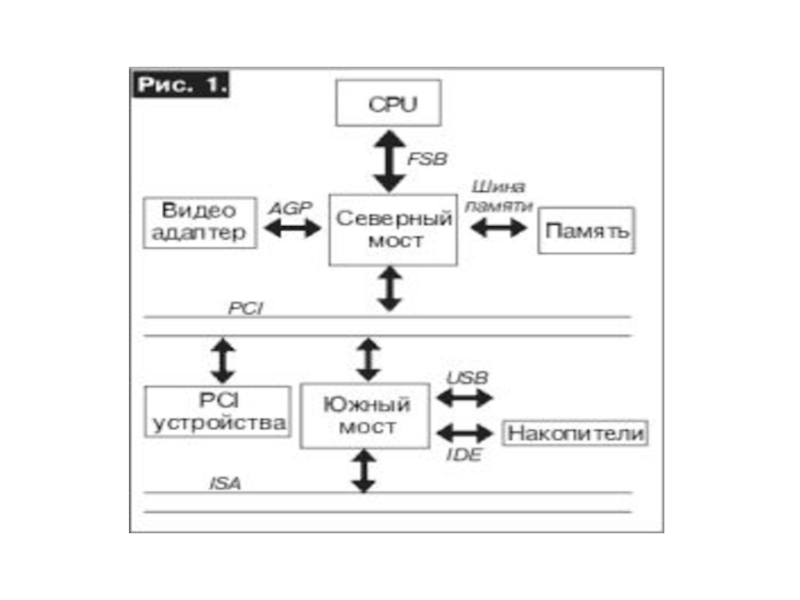

Микросхема северного моста обеспечивает работу с наиболее скоростными подсистемами.

Задача северного моста - с минимальными задержками организовать обслуживание запросов к системной памяти.

Южный мост обеспечивает работу с более медленными компонентами системы и периферийными устройствами.

Слайд 204 Свойства чипсет Intel 440BX:

- возможность подключения

цесcоров Pentium ll;

- поддержка памяти EDORAM и SDRAM;

- системная шина 64 бита,частота 66и

100 МГц;

- синхронный интерфейс PCI (33 МГц);

- порт AGP1x/2x,частота 66/100 МГц;

- управление энергопотреблением.

Слайд 206 Характеристики чипсет i810:

- поддержка однопрцессорной конфигу-

- системная шина 66 и 100МГц,64 разр.;

- интерфейс памяти SDRAM на 100МГц;

- 2Д/3Д графическое ядро;

- поддержка шины PCI 2.2;

- управление энергопотреблением;

- контроллер Ultra ATA/66;

- интерфейс LPC(Lou Pin Count);

- отсутствие шины ISA;

Слайд 208Характеристики чипсет-северный мост

- поддержка процессоров с частотой шины 533/800МГц;

- двухканальный контроллер памяти

DDR333/400 и DDR2-400/533МГц;

- шина для видеоускорителей

PCI Expessx16;

- встроенная графика для i915;

Слайд 209 Характеристики чипсет южный мост

- 4порта PCI Express x1;

- Matrix Storage-поддержка устройств

Serial ATA с RAID и AHCI,4 порта;

- High Defenition Audio-новый стандарт

для встроенного звука;

- Wireless Connect-организация беспроводной сети

- 8 портов USB;

- 6 устройств PCI Bus Master;

- 1 канал Parallel ATA;

- MAC контроллер Fast Ethernet (10/100/1000);

Слайд 211Северный мост -чипсет х38 Express

- поддержка “новых” процессоров Cele-

мной широй 800/1066 и 1333МГц;

- двухканальный контроллер памяти

DDR2-533/1066/1333;

- 2 графических интерфейса PCI

Express2.0x16;

- шина DMI -2Гб/с для южного моста ICH9.

Слайд 212 Чипсет Intel ICH9-южный мост

- 6 портов PCI Express;

-

- 4 порта Serial ATA II,режим AHCI;

- организация RAID-массива с функцией

Matrix RAID;

- 12 устройств USB 2.0;

- MAC-контроллер Gigabit Ethernet;

- поддержка Intel Turbo Memori;

- High Defenition Audi

- обвязка низкоскоростной, старой периферии.

Слайд 214

Северный мост 975X:

поддержка процессоров Intel Pentium 4, Pentium 4 Extreme

двухканальный контроллер памяти DDR2-533/667 с поддержкой до 4 модулей DIMM суммарным объемом до 8 ГБ (возможно применение модулей с и без ECC);

графический интерфейс PCIEx16 или 2 графических интерфейса PCIEx8

первые четырехъядерные процессоры должны официально заработать только в платах на базе i975X.

Слайд 215

процессоры на базе Nehalem, имеющие 4 физических ядра с технологией SMT

Bloomfield использует для связи с чипсет новую шину QPI, разработанную Intel для связи процессоров (сокетов) между собой — функционально это приблизительный аналог шины HyperTransport, широко применяемой в решениях AMD.

Естественно, что для поддержки всех новых процессоров потребуются новые чипсеты (так как прежние соединялись с процессором по шине FSB).

Слайд 217

поддержка новых процессоров (представленных на момент анонса статьи семействами Core i7

2 графических интерфейса PCI Express 2.0 x16, с возможностью разбить каждый на два графических интерфейса с половинной скоростью или даже на четыре с четвертной скоростью;

дополнительный интерфейс PCI Express 2.0 x4, с возможностью разбить его на два интерфейса с половинной скоростью;

шина DMI (с пропускной способностью ~2 ГБ/с) до южного моста ICH10/R.

Слайд 218Южный мост ICH10/R

до 6 портов PCIEx1 (PCI-E 1.1);

до 4

6 портов Serial ATA II на 6 устройств SATA300 (SATA-II, второе поколение стандарта), с поддержкой режима AHCI и функций вроде NCQ (у ICH10 работоспособность этого режима гарантирована только под Windows Vista), с возможностью индивидуального отключения, с поддержкой eSATA и разветвителей портов;

возможность организации RAID-массива (только для ICH10R) уровней 0, 1, 0+1 (10) и 5 с функцией Matrix RAID (один набор дисков может использоваться сразу в нескольких режимах RAID — например, на двух дисках можно организовать RAID 0 и RAID 1, под каждый массив будет выделена своя часть диска);

12 устройств USB 2.0 (на двух хост-контроллерах EHCI) с возможностью индивидуального отключения;

MAC-контроллер Gigabit Ethernet и специальный интерфейс (LCI/GLCI) для подключения PHY-контроллера (i82567 для реализации Gigabit Ethernet, i82562 для реализации Fast Ethernet);

поддержка Intel Turbo Memory(только для ICH10R);

High Definition Audio (7.1);

обвязка для низкоскоростной и устаревшей периферии, прочее

Слайд 219Чипсет Intel P55 для новой платформы Socket 1156

Для поддержки процессоров

Не должен вызывать удивления тот факт, что архитектура чипсета значительно изменилась со времен хотя бы серии Intel 4x. Сначала в процессор (ядро Bloomfield) переехал контроллер памяти, а теперь туда же переместился и контроллер графического интерфейса. Вполне естественно, что P55 при этом отказался от северного моста, который бы иначе оставался просто лишним звеном в цепочке, и теперь чипсет фактически представляет собой прежний (немного улучшенный) южный мост. По-видимому, Intel показалось несолидным сведение чипсета к южному мосту, так что вместо напрашивающейся традиционной аббревиатуры ICH (I/O Controller Hub) мост P55 носит название PCH — Platform Controller Hub.

Слайд 221характеристики чипсета P55 Express

поддержка новых процессоров (представленных на момент анонса

до 8 портов PCIEx1 (PCI-E 2.0, но со скоростью передачи данных PCI-E 1.1);

до 4 слотов PCI;

6 портов Serial ATA II на 6 устройств SATA300 (SATA-II, второе поколение стандарта), с поддержкой режима AHCI и функций вроде NCQ, с возможностью индивидуального отключения, с поддержкой eSATA и разветвителей портов;

возможность организации RAID-массива уровней 0, 1, 0+1 (10) и 5 с функцией Matrix RAID (один набор дисков может использоваться сразу в нескольких режимах RAID — например, на двух дисках можно организовать RAID 0 и RAID 1, под каждый массив будет выделена своя часть диска);

14 устройств USB 2.0 (на двух хост-контроллерах EHCI) с возможностью индивидуального отключения;

MAC-контроллер Gigabit Ethernet (подключение PHY-контроллера i82577/82578 осуществляется через любой свободный порт PCIEx1 чипсета);

High Definition Audio (7.1);

обвязка для низкоскоростной и устаревшей периферии, проч

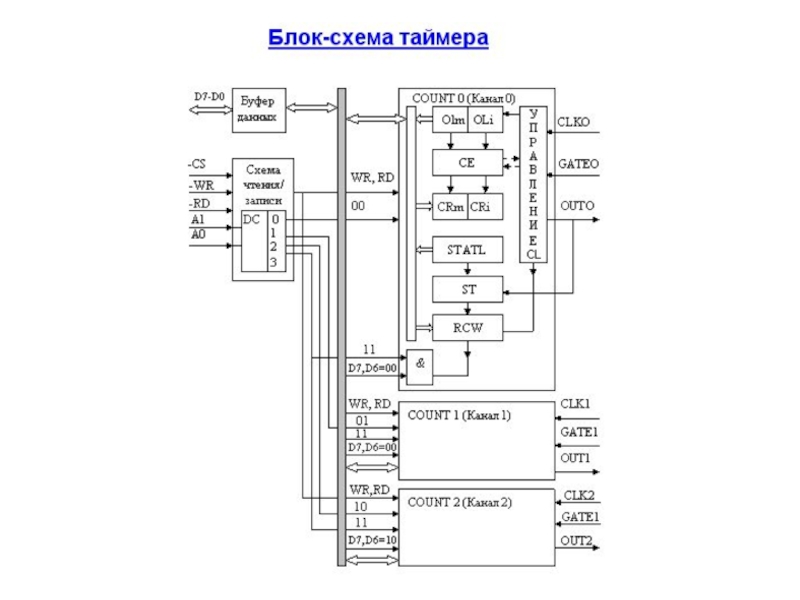

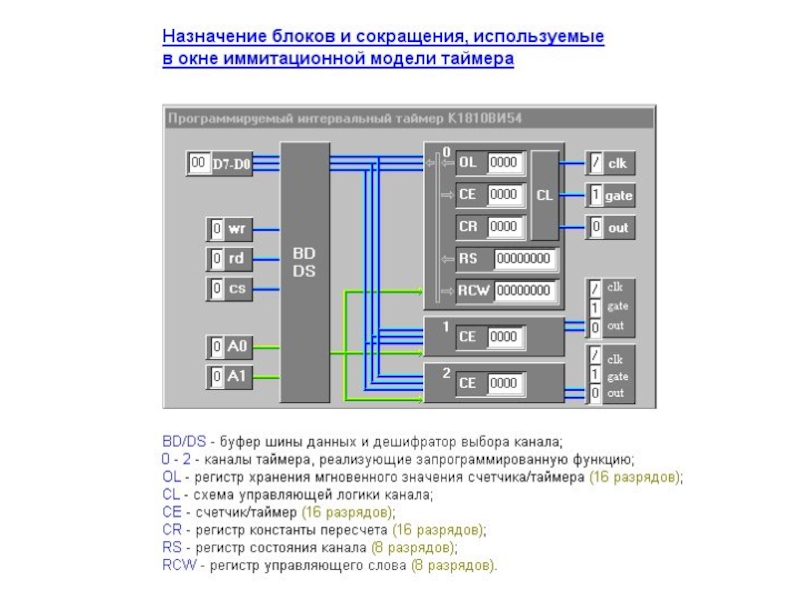

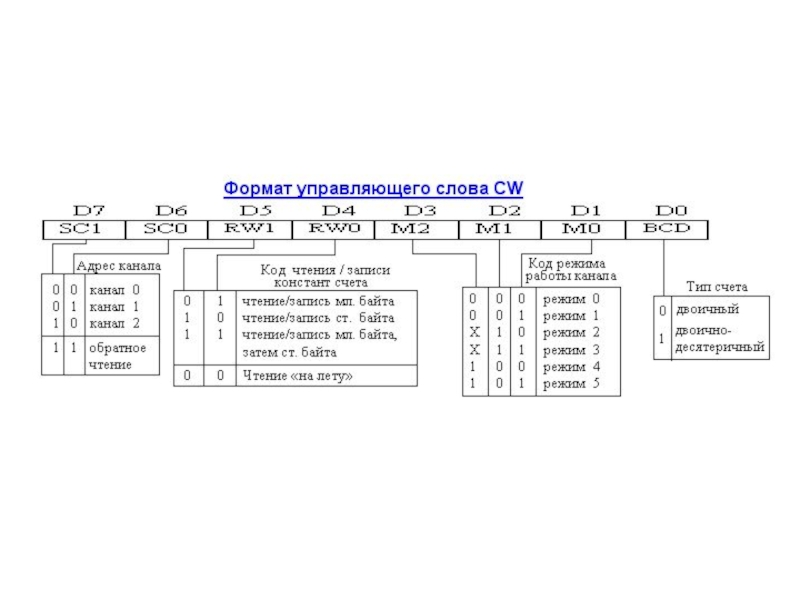

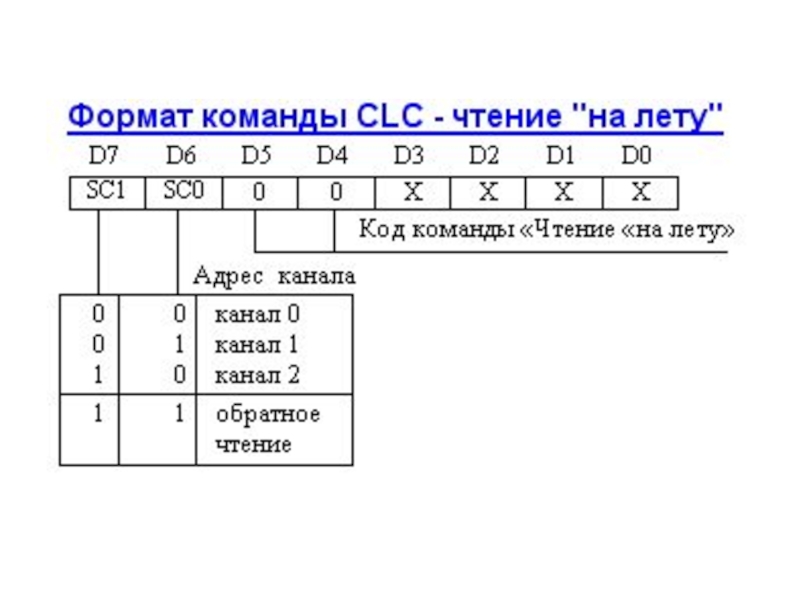

Слайд 222 Таймер

Программно

предназначенное для задания вре-

менных интервалов различного ви-

да в системах ввода-вывода и интер-

фейсах.

![Сигналы шины ISA Сигналы адреса и данных SA(System Adres)[19-0] - адрес с «защелкиванием»](/img/tmb/2/138342/d6c8cf6de1c0686d36e582bbcd4368b9-800x.jpg)

![Базовые сигналы шины PCIAD[31-0] – адрес – данные;C/BE[3-0] – код команды, указатель байт;#FRAME – начало](/img/tmb/2/138342/68420b01edac676695190ef45f4a801a-800x.jpg)

![Сигналы шины АТА/ATAPI - 4RESET# (Device Reset) – сброс устройства.DA[2:0] (Device Address) – адрес регистров](/img/tmb/2/138342/6c91739f8c71402fcda0f505767f8e92-800x.jpg)