- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Advanced Vector Extensions (AVX) и их использование презентация

Содержание

- 1. Advanced Vector Extensions (AVX) и их использование

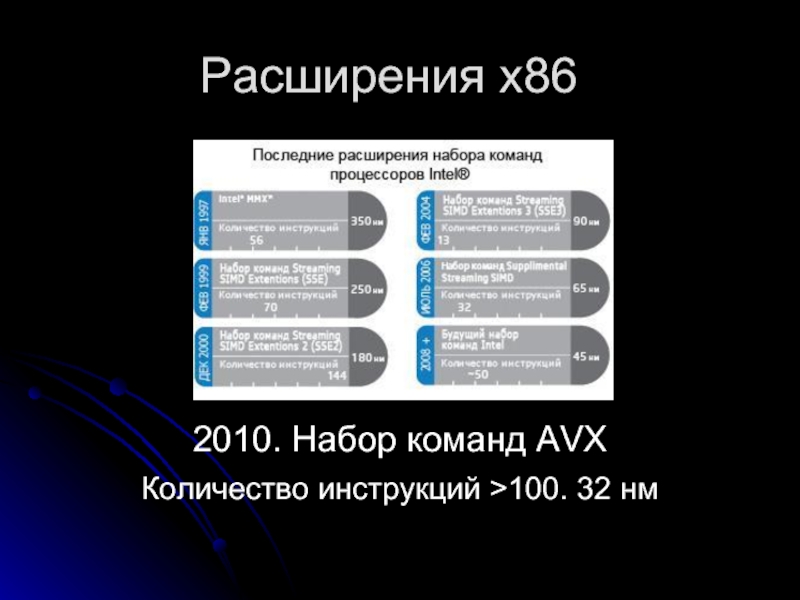

- 2. Расширения x86 2010. Набор команд AVX Количество инструкций >100. 32 нм

- 3. Multi-Media Extensions (MMX) Впервые в процессорах Pentium

- 4. Streaming SIMD Extensions (SSE) Впервые в процессорах

- 5. Streaming SIMD Extensions 2 (SSE2) Впервые в

- 6. Streaming SIMD Extensions 3 (SSE3) Впервые в

- 7. Supplemental Streaming SIMD Extension 3 (SSSE3) Впервые

- 8. Streaming SIMD Extensions 4 (SSE4) Впервые в

- 9. Advanced Vector Extensions (AVX) Регистры: YMM0 —

- 10. Расшифровка инструкций ADDxx PD - Packed Double

- 11. Расшифровка инструкций CVTxx2yy (Convert xx to yy

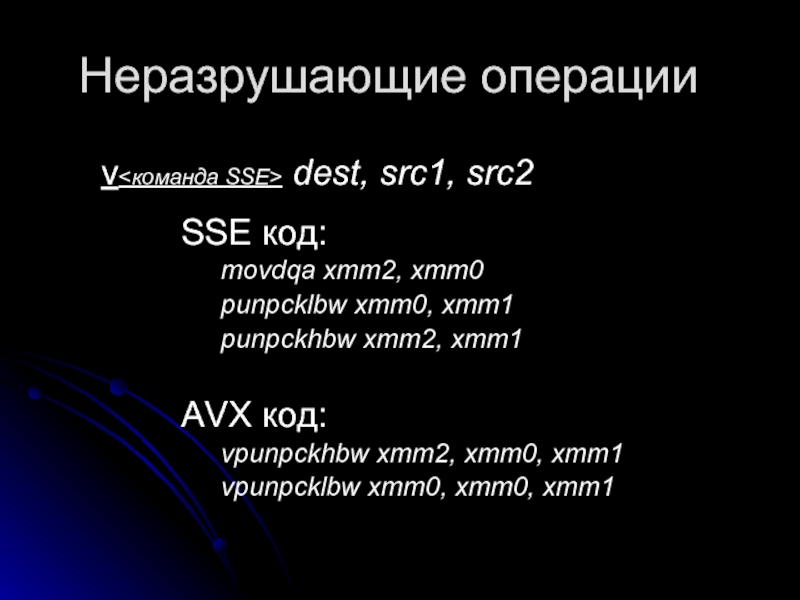

- 12. Неразрушающие операции SSE код: movdqa xmm2, xmm0

- 13. Преимущества трехоперандных инструкций: Позволяют избавиться от лишних

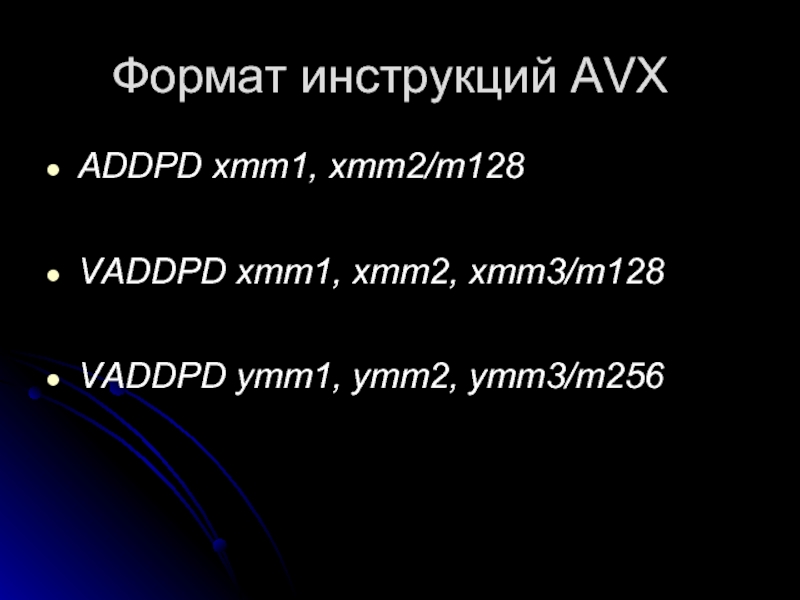

- 14. Формат инструкций AVX ADDPD xmm1, xmm2/m128 VADDPD xmm1, xmm2, xmm3/m128 VADDPD ymm1, ymm2, ymm3/m256

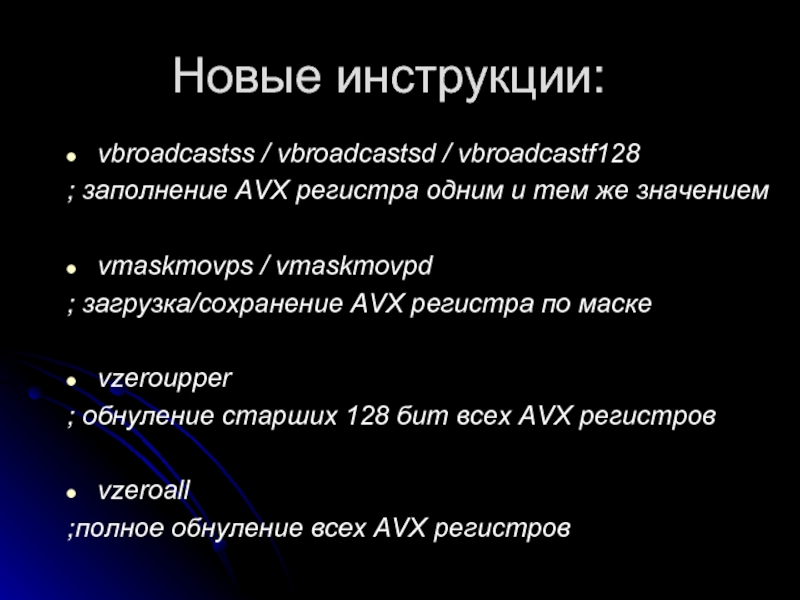

- 15. Новые инструкции: vbroadcastss / vbroadcastsd / vbroadcastf128

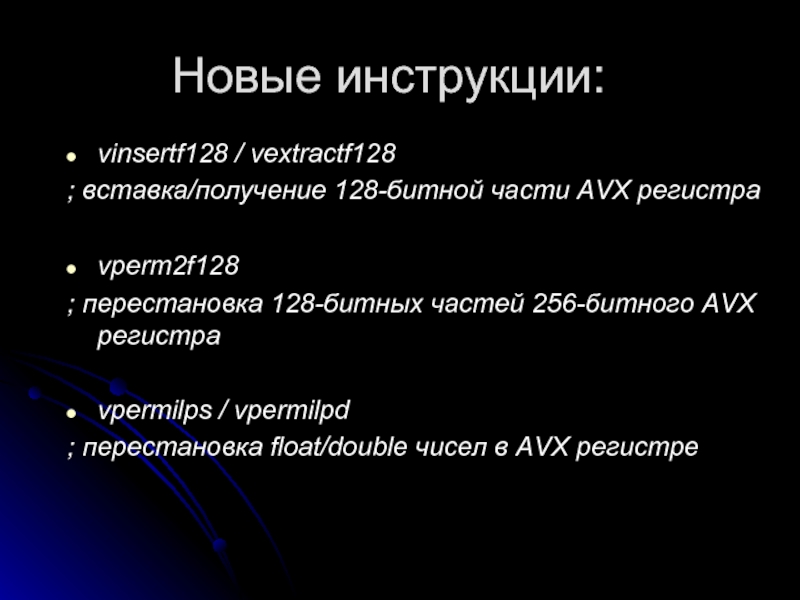

- 16. Новые инструкции: vinsertf128 / vextractf128 ; вставка/получение

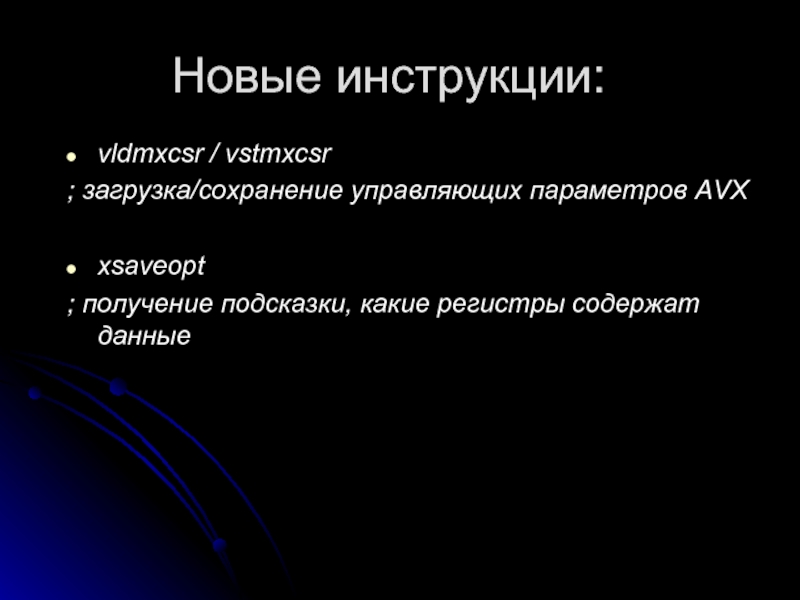

- 17. Новые инструкции: vldmxcsr / vstmxcsr ; загрузка/сохранение

- 18. Поддержка в операционных системах Windows 7 Windows

- 19. Использование AVX в ассемблерном коде GAS -

- 20. Определение поддержки AVX системой Убедимся, что ОС

- 21. Определение поддержки AVX системой Инструкции XSAVE/XRSTOR конфигурируются

- 22. Использование AVX-инструкций Нежелательно смешивать SSE- и AVX-инструкции.

- 23. Использование AVX-инструкций Пусть в функцию передали double

- 24. Использование AVX в коде на C/C++ Поддержка

- 25. Использование AVX в коде на C/C++ Чтобы

- 26. Использование AVX в коде на C/C++ Пусть

- 27. Нормализация 3D-векторов Рассмотрим код: void Normalize(float

- 28. Нормализация 3D-векторов Рассмотрим код: void Normalize(float

- 29. Нормализация 3D-векторов AVX позволяет делать параллельные вычисления

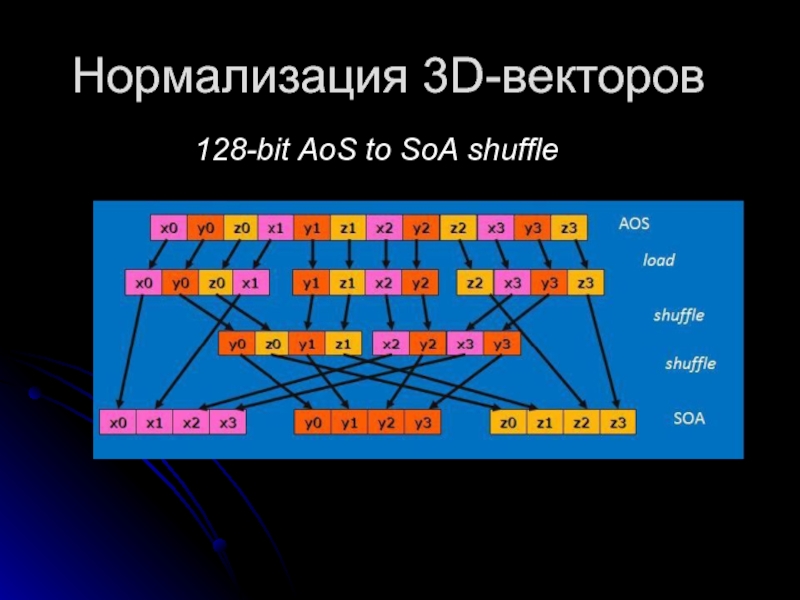

- 30. Нормализация 3D-векторов 128-bit AoS to SoA shuffle

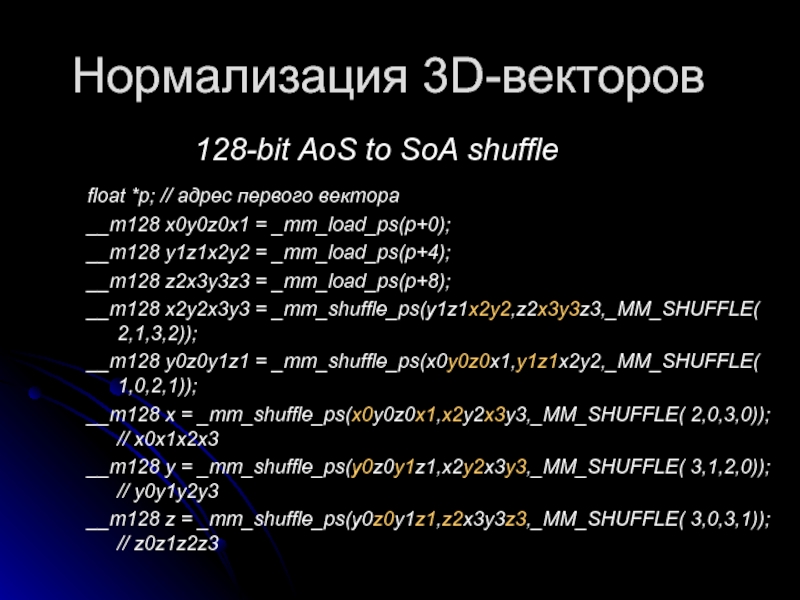

- 31. Нормализация 3D-векторов 128-bit AoS to SoA shuffle

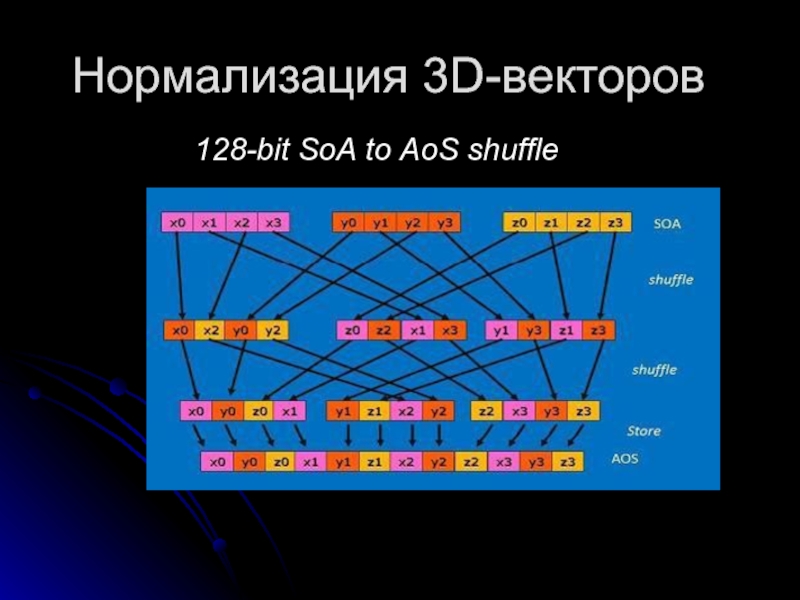

- 32. Нормализация 3D-векторов 128-bit SoA to AoS shuffle

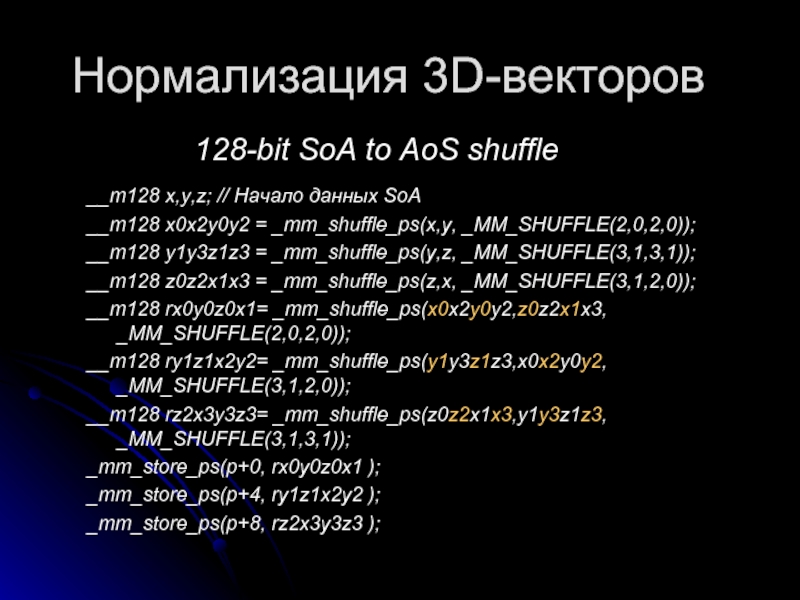

- 33. Нормализация 3D-векторов 128-bit SoA to AoS shuffle

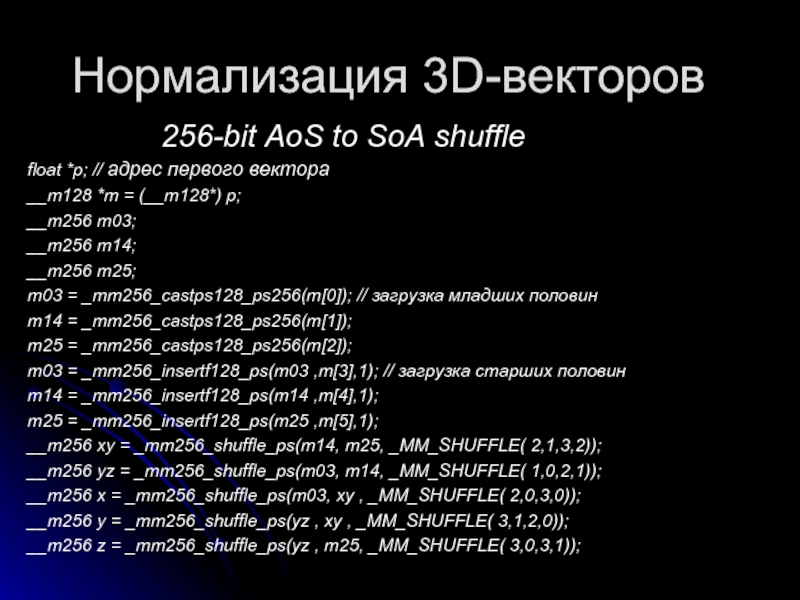

- 34. Нормализация 3D-векторов 256-bit AoS to SoA shuffle

- 35. Нормализация 3D-векторов 256-bit AoS to SoA shuffle

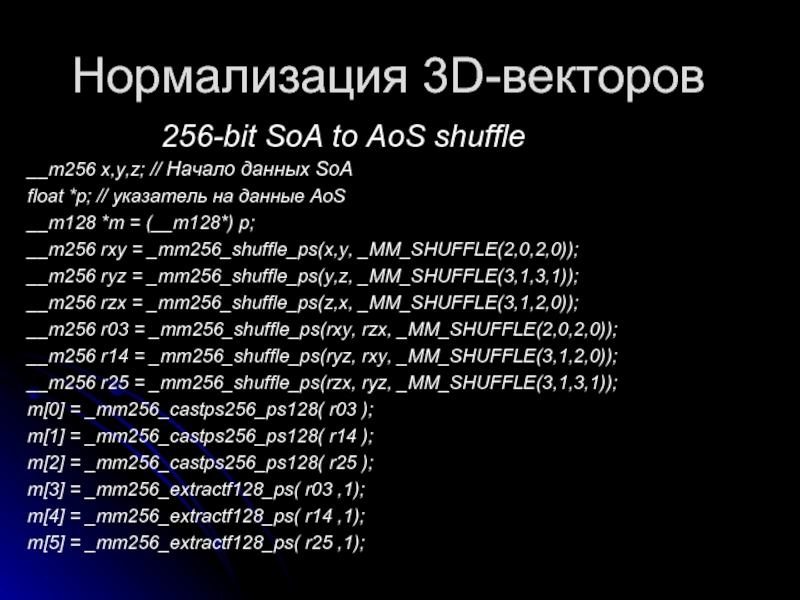

- 36. Нормализация 3D-векторов 256-bit SoA to AoS shuffle

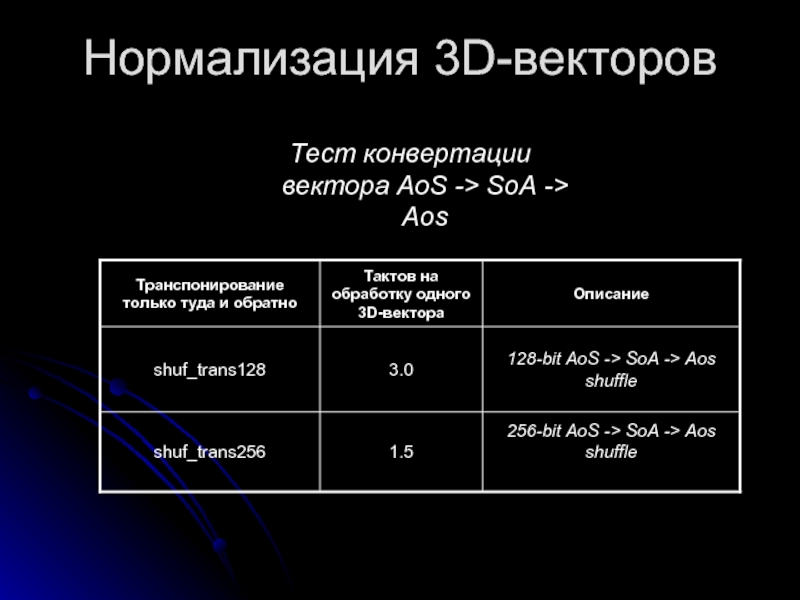

- 37. Нормализация 3D-векторов Тест конвертации вектора AoS -> SoA -> Aos

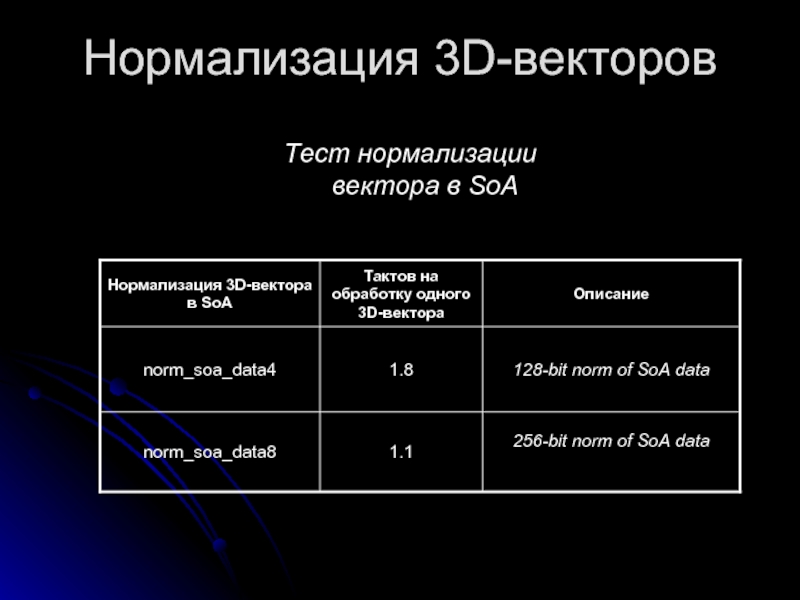

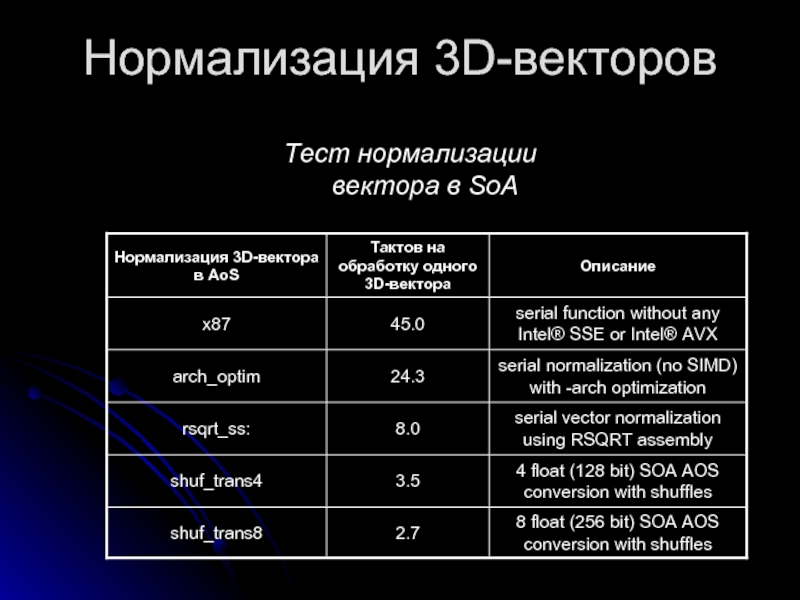

- 38. Нормализация 3D-векторов Тест нормализации вектора в SoA

- 39. Нормализация 3D-векторов Тест нормализации вектора в SoA

- 40. Шифрование AES Стандарт шифрования AES является официальным

- 41. Шифрование AES AES-128, AES-192, AES-256 обрабатывают блоки

- 42. Шифрование AES AddRoundKey (128-bit, 128-bit) является 128-битным

- 43. Шифрование AES S-Box (Блок подстановки) это 8-битное

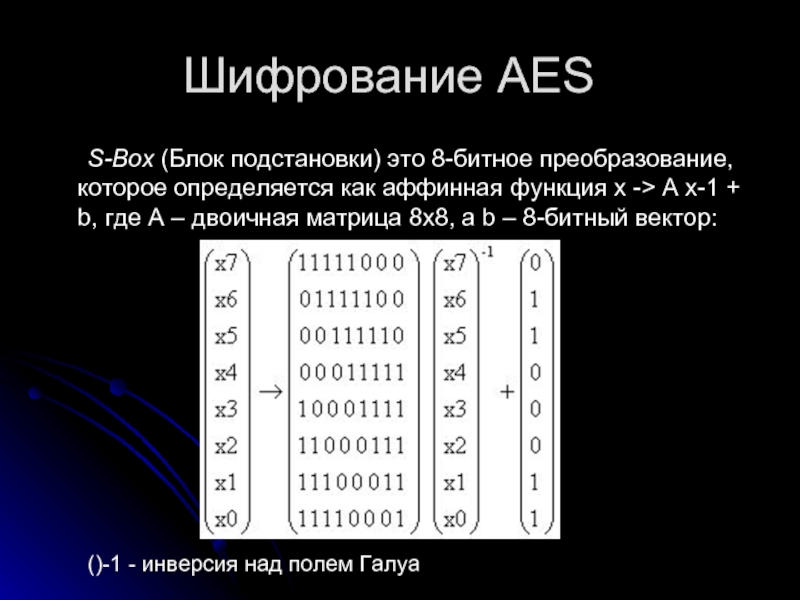

- 44. Шифрование AES InvS-Box является обратным преобразованием по

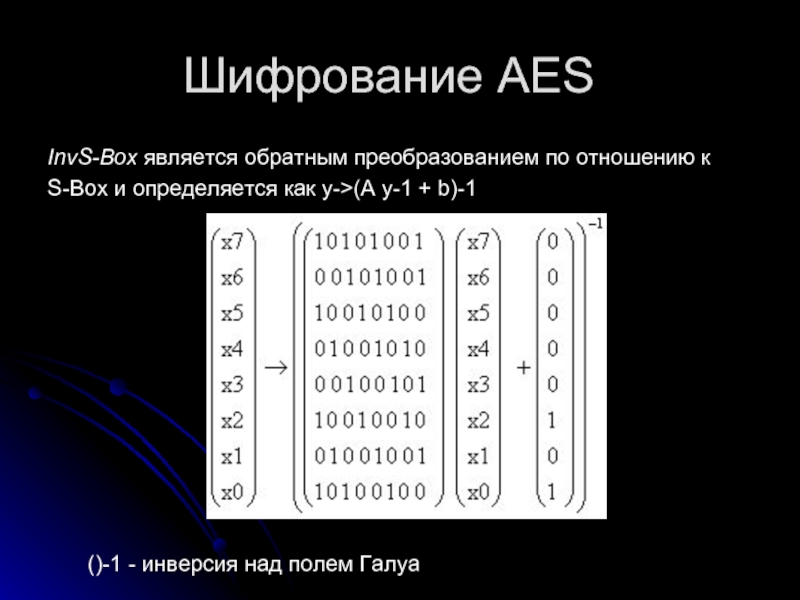

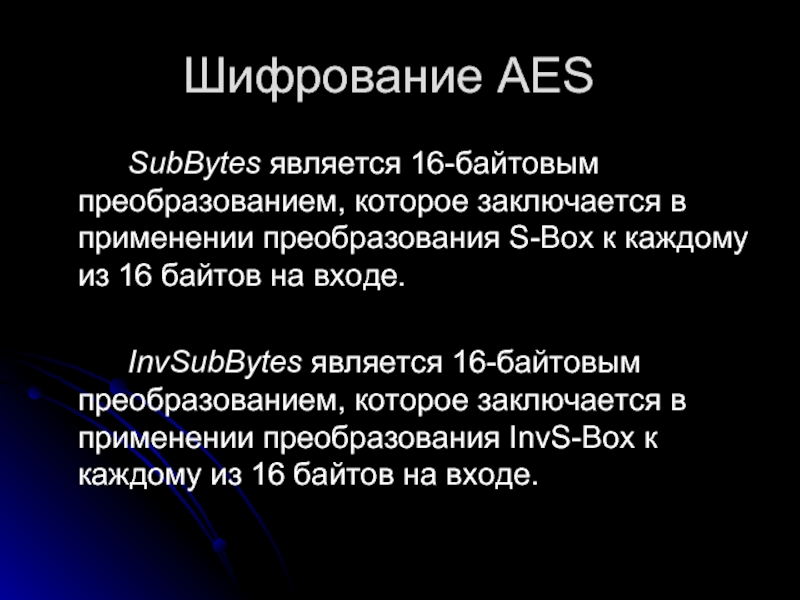

- 45. Шифрование AES SubBytes является 16-байтовым преобразованием, которое

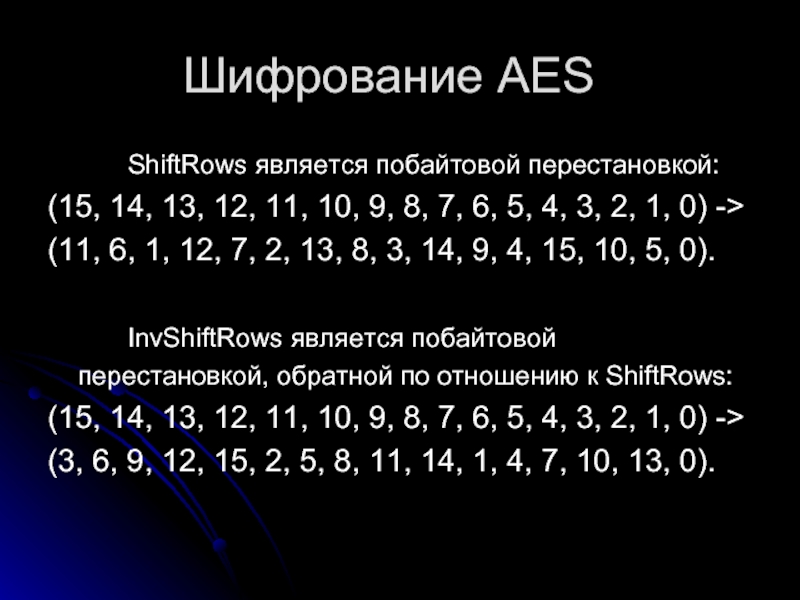

- 46. Шифрование AES ShiftRows является побайтовой перестановкой:

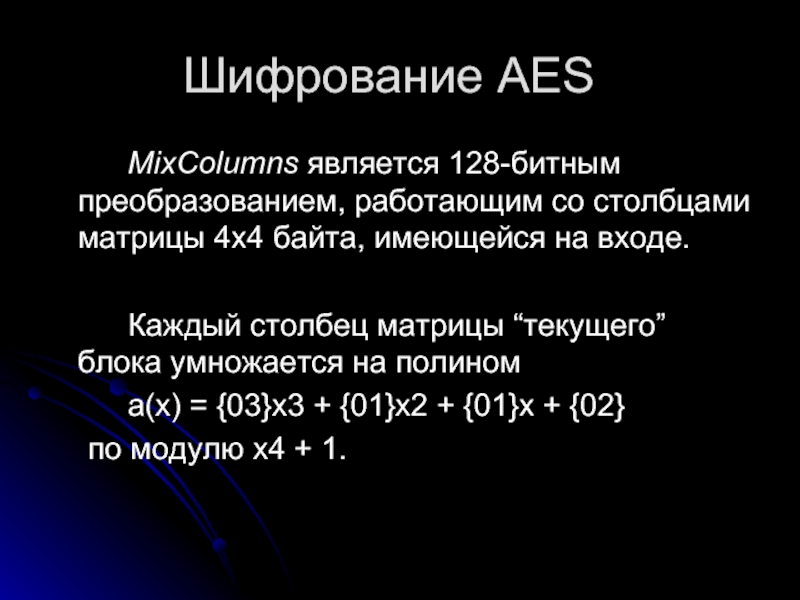

- 47. Шифрование AES MixColumns является 128-битным преобразованием, работающим

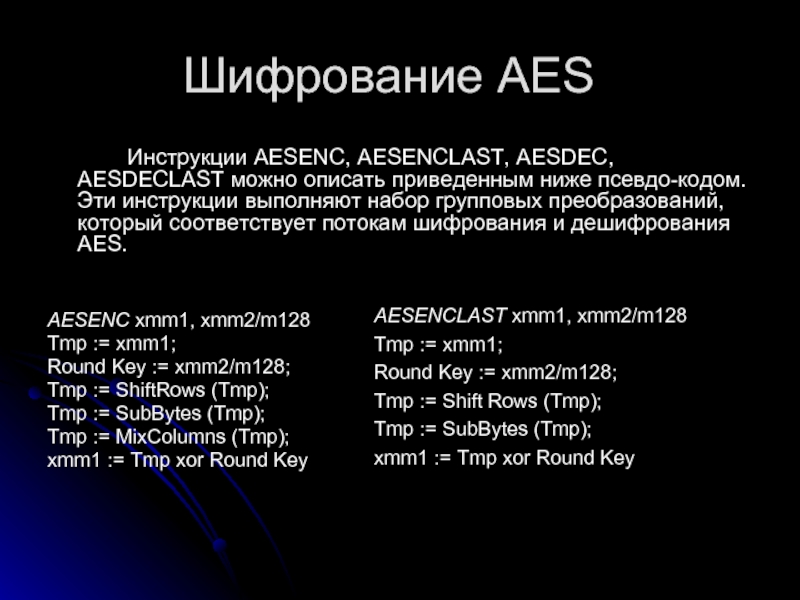

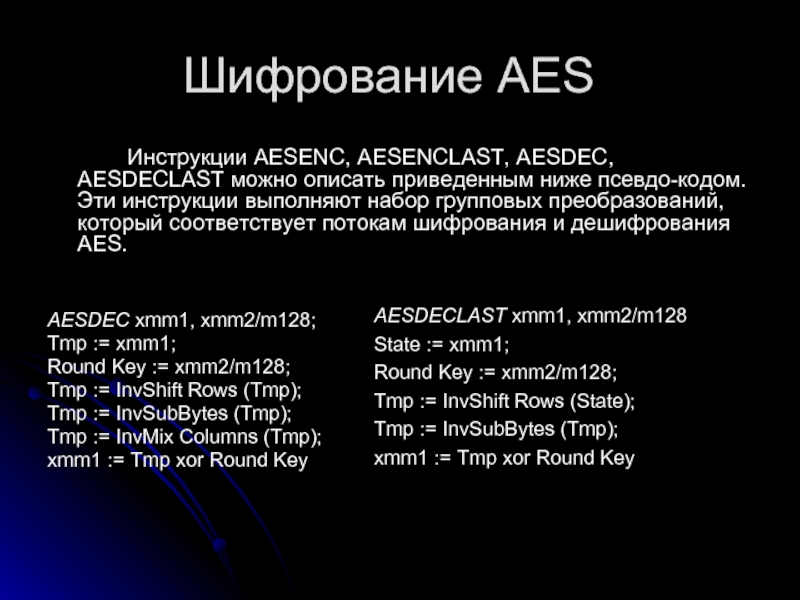

- 48. Шифрование AES Инструкции AESENC, AESENCLAST, AESDEC, AESDECLAST

- 49. Шифрование AES Инструкции AESENC, AESENCLAST, AESDEC, AESDECLAST

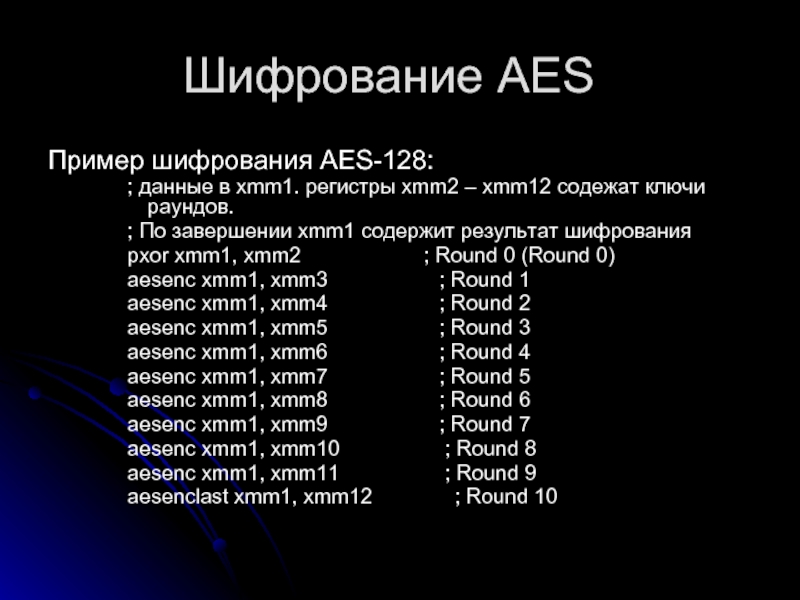

- 50. Шифрование AES Пример шифрования AES-128: ; данные

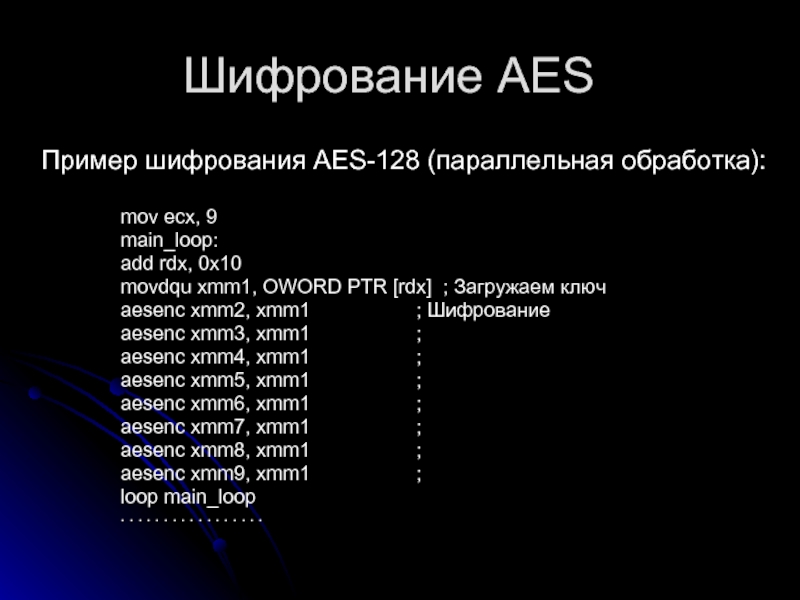

- 51. Шифрование AES Пример шифрования AES-128 (параллельная обработка):

- 52. Шифрование AES Пример шифрования AES-128 (параллельная обработка):

- 53. Заключение Наборы векторных данных большей разрядности могут

- 54. Ссылки http://software.intel.com/en-us/avx/ http://ru.wikipedia.org/wiki/AVX/

Слайд 3Multi-Media Extensions (MMX)

Впервые в процессорах Pentium MMX.

Регистры: MM0 - MM7 (64

Целочисленные вычисления.

Слайд 4Streaming SIMD Extensions (SSE)

Впервые в процессорах Pentium 3.

Регистры: XMM0 - XMM7

Поддерживает вычисления с плавающей точкой.

Слайд 5Streaming SIMD Extensions 2 (SSE2)

Впервые в процессорах Pentium 4.

Регистры: XMM0 -

Включает в себя ряд команд управления кэшем для минимизации загрязнения кэша при обработке неопределенных потоков информации.

Слайд 6Streaming SIMD Extensions 3 (SSE3)

Впервые в процессорах Prescott.

Регистры: XMM0 - XMM7

Возможность горизонтальной работы с регистрами. Преобразования значений с плавающей точкой в целые.

Слайд 7Supplemental Streaming SIMD Extension 3 (SSSE3)

Впервые в процессорах Intel Core Microarchitecture.

Регистры:

Работа с упакованными целыми.

Слайд 8Streaming SIMD Extensions 4 (SSE4)

Впервые в процессорах Penryn.

Регистры: XMM0 – XMM15

Ускорение видео, обработка строк 8/16 битных символов.

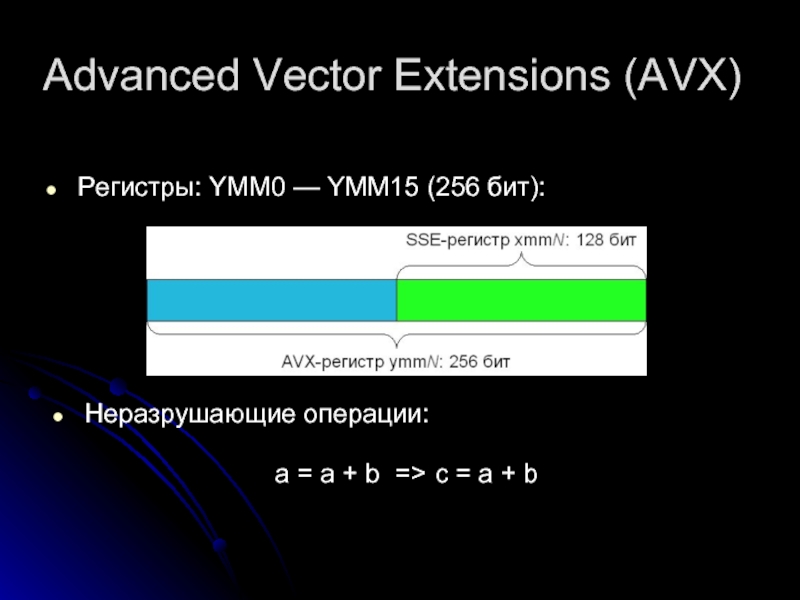

Слайд 9Advanced Vector Extensions (AVX)

Регистры: YMM0 — YMM15 (256 бит):

Неразрушающие операции:

a =

Слайд 10Расшифровка инструкций

ADDxx

PD - Packed Double Precision Floating-Point Values

PS - Packed Single

SD - Scalar Double Precision Floating-Point Values

SS - Scalar Single Precision Floating-Point Values

Слайд 11Расшифровка инструкций

CVTxx2yy (Convert xx to yy Values)

DQ - Packed Doubleword Integers

SI

Слайд 12Неразрушающие операции

SSE код:

movdqa xmm2, xmm0

punpcklbw xmm0, xmm1

punpckhbw xmm2, xmm1

AVX код:

vpunpckhbw xmm2,

vpunpcklbw xmm0, xmm0, xmm1

v<команда SSE> dest, src1, src2

Слайд 13Преимущества трехоперандных инструкций:

Позволяют избавиться от лишних операций копирования регистров в коде.

Упрощают

Слайд 14Формат инструкций AVX

ADDPD xmm1, xmm2/m128

VADDPD xmm1, xmm2, xmm3/m128

VADDPD ymm1, ymm2, ymm3/m256

Слайд 15Новые инструкции:

vbroadcastss / vbroadcastsd / vbroadcastf128

; заполнение AVX регистра одним и

vmaskmovps / vmaskmovpd

; загрузка/сохранение AVX регистра по маске

vzeroupper

; обнуление старших 128 бит всех AVX регистров

vzeroall

;полное обнуление всех AVX регистров

Слайд 16Новые инструкции:

vinsertf128 / vextractf128

; вставка/получение 128-битной части AVX регистра

vperm2f128

; перестановка 128-битных

vpermilps / vpermilpd

; перестановка float/double чисел в AVX регистре

Слайд 17Новые инструкции:

vldmxcsr / vstmxcsr

; загрузка/сохранение управляющих параметров AVX

xsaveopt

; получение подсказки, какие

Слайд 19Использование AVX в ассемблерном коде

GAS - начиная с версии binutils 2.19.50.0.1

MASM

NASM - начиная с версии 2.03

YASM - начиная с версии 0.70

AVX поддерживается всеми популярными ассемблерами для x86:

Слайд 20Определение поддержки AVX системой

Убедимся, что ОС сохраняет/восстанавливает контекст AVX с помощью

mov eax, 1

cpuid

and ecx, 018000000h ; Проверяем, что установлены биты 27 (ОС использует XSAVE/XRSTOR)

cmp ecx, 018000000h ; и 28 (поддержка AVX процессором)

Слайд 21Определение поддержки AVX системой

Инструкции XSAVE/XRSTOR конфигурируются с помощью extended control register

xor ecx, ecx

xgetbv ; значение XRC0 в edx:eax

and eax, 110b

cmp eax, 110b ; ОС сохраняет AVX регистры при переключении контекста

Слайд 22Использование AVX-инструкций

Нежелательно смешивать SSE- и AVX-инструкции.

vzeroupper и vzeroall работают быстро.

Команды загрузки/сохранения

На Windows x64 подпрограмма не должна изменять регистры xmm6-xmm15.

Ядро Sandy Bridge будет способно запускать на выполнение две 256-битные AVX-команды с плавающей точкой каждый такт. (одно умножение и одно сложение)

Слайд 23Использование AVX-инструкций

Пусть в функцию передали double a[4], double b[4]. Посчитаем a*b:

mov

mov edx, [esp + 8 + 8] ; edx = b

vmovupd ymm0, [eax] ; ymm0 = *a

vmovupd ymm1, [edx] ; ymm1 = *b

vmulpd ymm0, ymm0, ymm1

; ymm0 = ( a3 * b3, a2 * b2, a1 * b1, a0 * b0 )

Слайд 24Использование AVX в коде на C/C++

Поддержка AVX реализована в следующих популярных

Microsoft C/C++ Compiler - начиная с версии 16 (входит в Visual Studio 2010)

Intel C++ Compiler - начиная с версии 11.1

GCC - начиная с версии 4.4

Для использования 256-битных инструкций AVX в дистрибутив включен заголовочный файл immintrin.h.

Слайд 25Использование AVX в коде на C/C++

Чтобы проверить, что процессор поддерживает AVX:

int

int cpuInfo[4];

__cpuid( cpuInfo, 0 );

if( cpuInfo[0] != 0 ) {

__cpuid( cpuInfo, 1 );

return cpuInfo[3] & 0x10000000; // Возвращаем ноль, если 28-ой бит в ecx сброшен

} else {

return 0; // Процессор не поддерживает получение информации о поддерживаемых наборах инструкций

}

}

Слайд 26Использование AVX в коде на C/C++

Пусть в функцию передали double a[4],

// mmA = a

const __m256d mmA = _mm256_loadu_pd( a );

// mmB = b

const __m256d mmB = _mm256_loadu_pd( b );

// mmAB = ( a3 * b3, a2 * b2, a1 * b1, a0 * b0 )

const __m256d mmAB = _mm256_mul_pd( mmA, mmB );

Слайд 27Нормализация 3D-векторов

Рассмотрим код:

void Normalize(float Vec[][3],int N) {

for (int i=0; i

float *v=Vec[i];

float normal = 1.0f/sqrtf(v[0]*v[0]+v[1]*v[1]+v[2]*v[2]);

v[0] *= normal;

v[1] *= normal;

v[2] *= normal;

}

}

Слайд 28Нормализация 3D-векторов

Рассмотрим код:

void Normalize(float Vec [ ] [3],int N) {

for

float *v=Vec[i];

float normal = 1.0f/sqrtf(v[0]*v[0]+v[1]*v[1]+v[2]*v[2]);

v[0] *= normal;

v[1] *= normal;

v[2] *= normal;

}

}

Array of Structures (AoS).

Умножение может быть распараллелено, если рассматривать как Structure of Arrays (SoA).

Слайд 29Нормализация 3D-векторов

AVX позволяет делать параллельные вычисления с 8-ми float. Например, нормализовывать

Нам удобно работать с массивами, состоящими из координат 3D-векторов.

Некоторые приложения требуют хранения 3D-векторов как массив структур.

Слайд 31Нормализация 3D-векторов

128-bit AoS to SoA shuffle

float *p; // адрес первого вектора

__m128 x0y0z0x1 = _mm_load_ps(p+0);

__m128 y1z1x2y2 = _mm_load_ps(p+4);

__m128 z2x3y3z3 = _mm_load_ps(p+8);

__m128 x2y2x3y3 = _mm_shuffle_ps(y1z1x2y2,z2x3y3z3,_MM_SHUFFLE( 2,1,3,2));

__m128 y0z0y1z1 = _mm_shuffle_ps(x0y0z0x1,y1z1x2y2,_MM_SHUFFLE( 1,0,2,1));

__m128 x = _mm_shuffle_ps(x0y0z0x1,x2y2x3y3,_MM_SHUFFLE( 2,0,3,0)); // x0x1x2x3

__m128 y = _mm_shuffle_ps(y0z0y1z1,x2y2x3y3,_MM_SHUFFLE( 3,1,2,0)); // y0y1y2y3

__m128 z = _mm_shuffle_ps(y0z0y1z1,z2x3y3z3,_MM_SHUFFLE( 3,0,3,1)); // z0z1z2z3

Слайд 33Нормализация 3D-векторов

128-bit SoA to AoS shuffle

__m128 x,y,z; // Начало данных SoA

__m128 x0x2y0y2 = _mm_shuffle_ps(x,y, _MM_SHUFFLE(2,0,2,0));

__m128 y1y3z1z3 = _mm_shuffle_ps(y,z, _MM_SHUFFLE(3,1,3,1));

__m128 z0z2x1x3 = _mm_shuffle_ps(z,x, _MM_SHUFFLE(3,1,2,0));

__m128 rx0y0z0x1= _mm_shuffle_ps(x0x2y0y2,z0z2x1x3, _MM_SHUFFLE(2,0,2,0));

__m128 ry1z1x2y2= _mm_shuffle_ps(y1y3z1z3,x0x2y0y2, _MM_SHUFFLE(3,1,2,0));

__m128 rz2x3y3z3= _mm_shuffle_ps(z0z2x1x3,y1y3z1z3, _MM_SHUFFLE(3,1,3,1));

_mm_store_ps(p+0, rx0y0z0x1 );

_mm_store_ps(p+4, ry1z1x2y2 );

_mm_store_ps(p+8, rz2x3y3z3 );

Слайд 35Нормализация 3D-векторов

256-bit AoS to SoA shuffle

float *p; // адрес первого вектора

__m128

__m256 m03;

__m256 m14;

__m256 m25;

m03 = _mm256_castps128_ps256(m[0]); // загрузка младших половин

m14 = _mm256_castps128_ps256(m[1]);

m25 = _mm256_castps128_ps256(m[2]);

m03 = _mm256_insertf128_ps(m03 ,m[3],1); // загрузка старших половин

m14 = _mm256_insertf128_ps(m14 ,m[4],1);

m25 = _mm256_insertf128_ps(m25 ,m[5],1);

__m256 xy = _mm256_shuffle_ps(m14, m25, _MM_SHUFFLE( 2,1,3,2));

__m256 yz = _mm256_shuffle_ps(m03, m14, _MM_SHUFFLE( 1,0,2,1));

__m256 x = _mm256_shuffle_ps(m03, xy , _MM_SHUFFLE( 2,0,3,0));

__m256 y = _mm256_shuffle_ps(yz , xy , _MM_SHUFFLE( 3,1,2,0));

__m256 z = _mm256_shuffle_ps(yz , m25, _MM_SHUFFLE( 3,0,3,1));

Слайд 36Нормализация 3D-векторов

256-bit SoA to AoS shuffle

__m256 x,y,z; // Начало данных SoA

float *p; // указатель на данные AoS

__m128 *m = (__m128*) p;

__m256 rxy = _mm256_shuffle_ps(x,y, _MM_SHUFFLE(2,0,2,0));

__m256 ryz = _mm256_shuffle_ps(y,z, _MM_SHUFFLE(3,1,3,1));

__m256 rzx = _mm256_shuffle_ps(z,x, _MM_SHUFFLE(3,1,2,0));

__m256 r03 = _mm256_shuffle_ps(rxy, rzx, _MM_SHUFFLE(2,0,2,0));

__m256 r14 = _mm256_shuffle_ps(ryz, rxy, _MM_SHUFFLE(3,1,2,0));

__m256 r25 = _mm256_shuffle_ps(rzx, ryz, _MM_SHUFFLE(3,1,3,1));

m[0] = _mm256_castps256_ps128( r03 );

m[1] = _mm256_castps256_ps128( r14 );

m[2] = _mm256_castps256_ps128( r25 );

m[3] = _mm256_extractf128_ps( r03 ,1);

m[4] = _mm256_extractf128_ps( r14 ,1);

m[5] = _mm256_extractf128_ps( r25 ,1);

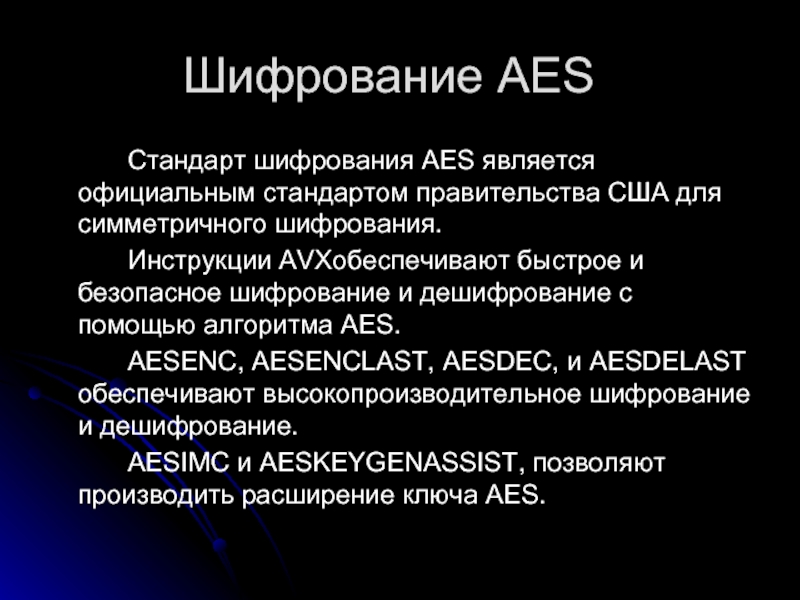

Слайд 40Шифрование AES

Стандарт шифрования AES является официальным стандартом правительства США для симметричного

Инструкции AVXобеспечивают быстрое и безопасное шифрование и дешифрование с помощью алгоритма AES.

AESENC, AESENCLAST, AESDEC, и AESDELAST обеспечивают высокопроизводительное шифрование и дешифрование.

AESIMC и AESKEYGENASSIST, позволяют производить расширение ключа AES.

Слайд 41Шифрование AES

AES-128, AES-192, AES-256 обрабатывают блоки данных за соответственно 10, 12

Блок данных последовательно проходит через следующие стадии: над ним выполняется операция XOR первыми 128 битами ключа, на выходе получается “текущий” блок.

Затем текущий блок проходит через 10/12/14 раундов шифрования, после которых он превращается в шифрованный (или дешифрованный) блок.

Слайд 42Шифрование AES

AddRoundKey (128-bit, 128-bit) является 128-битным преобразованием, которое заключается в побитовой

Слайд 43Шифрование AES

S-Box (Блок подстановки) это 8-битное преобразование, которое определяется как аффинная

()-1 - инверсия над полем Галуа

Слайд 44Шифрование AES

InvS-Box является обратным преобразованием по отношению к

S-Box и определяется

()-1 - инверсия над полем Галуа

Слайд 45Шифрование AES

SubBytes является 16-байтовым преобразованием, которое заключается в применении преобразования S-Box

InvSubBytes является 16-байтовым преобразованием, которое заключается в применении преобразования InvS-Box к каждому из 16 байтов на входе.

Слайд 46Шифрование AES

ShiftRows является побайтовой перестановкой:

(15, 14, 13, 12, 11, 10,

(11, 6, 1, 12, 7, 2, 13, 8, 3, 14, 9, 4, 15, 10, 5, 0).

InvShiftRows является побайтовой перестановкой, обратной по отношению к ShiftRows:

(15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) ->

(3, 6, 9, 12, 15, 2, 5, 8, 11, 14, 1, 4, 7, 10, 13, 0).

Слайд 47Шифрование AES

MixColumns является 128-битным преобразованием, работающим со столбцами матрицы 4х4 байта,

Каждый столбец матрицы “текущего” блока умножается на полином

a(x) = {03}x3 + {01}x2 + {01}x + {02}

по модулю x4 + 1.

Слайд 48Шифрование AES

Инструкции AESENC, AESENCLAST, AESDEC, AESDECLAST можно описать приведенным ниже псевдо-кодом.

AESENC xmm1, xmm2/m128

Tmp := xmm1;

Round Key := xmm2/m128;

Tmp := ShiftRows (Tmp);

Tmp := SubBytes (Tmp);

Tmp := MixColumns (Tmp);

xmm1 := Tmp xor Round Key

AESENCLAST xmm1, xmm2/m128

Tmp := xmm1;

Round Key := xmm2/m128;

Tmp := Shift Rows (Tmp);

Tmp := SubBytes (Tmp);

xmm1 := Tmp xor Round Key

Слайд 49Шифрование AES

Инструкции AESENC, AESENCLAST, AESDEC, AESDECLAST можно описать приведенным ниже псевдо-кодом.

AESDEC xmm1, xmm2/m128;

Tmp := xmm1;

Round Key := xmm2/m128;

Tmp := InvShift Rows (Tmp);

Tmp := InvSubBytes (Tmp);

Tmp := InvMix Columns (Tmp);

xmm1 := Tmp xor Round Key

AESDECLAST xmm1, xmm2/m128

State := xmm1;

Round Key := xmm2/m128;

Tmp := InvShift Rows (State);

Tmp := InvSubBytes (Tmp);

xmm1 := Tmp xor Round Key

Слайд 50Шифрование AES

Пример шифрования AES-128:

; данные в xmm1. регистры xmm2 – xmm12

; По завершении xmm1 содержит результат шифрования

pxor xmm1, xmm2 ; Round 0 (Round 0)

aesenc xmm1, xmm3 ; Round 1

aesenc xmm1, xmm4 ; Round 2

aesenc xmm1, xmm5 ; Round 3

aesenc xmm1, xmm6 ; Round 4

aesenc xmm1, xmm7 ; Round 5

aesenc xmm1, xmm8 ; Round 6

aesenc xmm1, xmm9 ; Round 7

aesenc xmm1, xmm10 ; Round 8

aesenc xmm1, xmm11 ; Round 9

aesenclast xmm1, xmm12 ; Round 10

Слайд 51Шифрование AES

Пример шифрования AES-128 (параллельная обработка):

mov ecx, 9

main_loop:

add rdx,

movdqu xmm1, OWORD PTR [rdx] ; Загружаем ключ

aesenc xmm2, xmm1 ; Шифрование

aesenc xmm3, xmm1 ;

aesenc xmm4, xmm1 ;

aesenc xmm5, xmm1 ;

aesenc xmm6, xmm1 ;

aesenc xmm7, xmm1 ;

aesenc xmm8, xmm1 ;

aesenc xmm9, xmm1 ;

loop main_loop

. . . . . . . . . . . . . . . . .

Слайд 52Шифрование AES

Пример шифрования AES-128 (параллельная обработка):

movdqu xmm1, OWORD PTR [rdx] ;

aesenclast xmm2, xmm1 ; Последний раунд

aesenclast xmm3, xmm1 ;

aesenclast xmm4, xmm1 ;

aesenclast xmm5, xmm1 ;

aesenclast xmm6, xmm1 ;

aesenclast xmm7, xmm1 ;

aesenclast xmm8, xmm1 ;

aesenclast xmm9, xmm1 ;

Слайд 53Заключение

Наборы векторных данных большей разрядности могут обрабатываться со скоростью до двух

Новый набор команд Intel AVX может использоваться любыми приложениями, в которых значительная доля вычислений приходится на операции SIMD.

Наибольший прирост производительности новая технология даст для тех из них, которые преимущественно выполняют вычисления с плавающей запятой и могут быть распараллелены (программы обработки звука и аудио-кодеки, программы для редактирования изображений и видео, приложения для моделирования и финансового анализа, промышленные и инженерные приложения).

![Использование AVX-инструкцийПусть в функцию передали double a[4], double b[4]. Посчитаем a*b:mov eax, [esp + 8](/img/tmb/1/99841/b4102d4e33e1621f967d32793790f884-800x.jpg)

![Использование AVX в коде на C/C++Чтобы проверить, что процессор поддерживает AVX:int isAvxSupportedByCpu() { int cpuInfo[4];](/img/tmb/1/99841/4b2f11fb43ddf95d12a558d74abb61c9-800x.jpg)

![Использование AVX в коде на C/C++Пусть в функцию передали double a[4], double b[4]. Посчитаем a*b://](/img/tmb/1/99841/b01dda27a1d794d48c912ce7466849a9-800x.jpg)

![Нормализация 3D-векторовРассмотрим код:void Normalize(float Vec[][3],int N) { for (int i=0; i < N; ++i) {](/img/tmb/1/99841/e67a672459a99353f6e02d59844b9a44-800x.jpg)

![Нормализация 3D-векторовРассмотрим код:void Normalize(float Vec [ ] [3],int N) { for (int i=0; i <](/img/tmb/1/99841/331d9af100055788a0b4ae0344ef7477-800x.jpg)

![Шифрование AESПример шифрования AES-128 (параллельная обработка):movdqu xmm1, OWORD PTR [rdx] ; Загружаем ключ aesenclast xmm2,](/img/tmb/1/99841/669705e4470485267eb24e97670b13c1-800x.jpg)