Zhao

- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

A FPGA Accelerated AI for Connect-5 презентация

Содержание

- 1. A FPGA Accelerated AI for Connect-5

- 2. Goal Build an AI for connect-5 (Gomoku)

- 3. Literature Review Began by looking at papers

- 4. Board Evaluation Board Evaluation Function sweeps a

- 5. Board Evaluation (Cont.) If the board is

- 6. Search Tree Minimax Search Tree + Alpha-Beta Pruning

- 7. Search Tree (Cont.) To avoid dynamic memory

- 8. Hardware Acceleration Instead of checking the squares

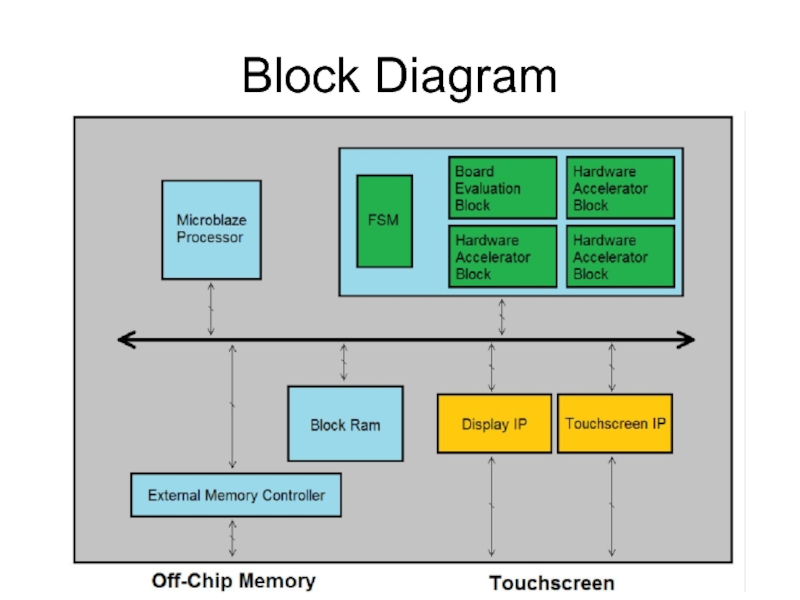

- 9. Block Diagram

- 10. Plan of Action Phase 1: Write the

Слайд 1A FPGA Accelerated AI for Connect-5

ECE532 Digital Systems Design

David Biancolin

Mohamed Kayed

Ritchie

Слайд 2Goal

Build an AI for connect-5 (Gomoku) in FPGA hardware and leverage

Vivado’s High Level Synthesis functions

The AI should run faster than its software counterpart running on a top of the line general purpose PC

The AI should be competitive with software AIs on Gomocup

The AI should run faster than its software counterpart running on a top of the line general purpose PC

The AI should be competitive with software AIs on Gomocup

Слайд 3Literature Review

Began by looking at papers from ICFPT design competition

2013: Blokus

2012:

Connect-6 Variant

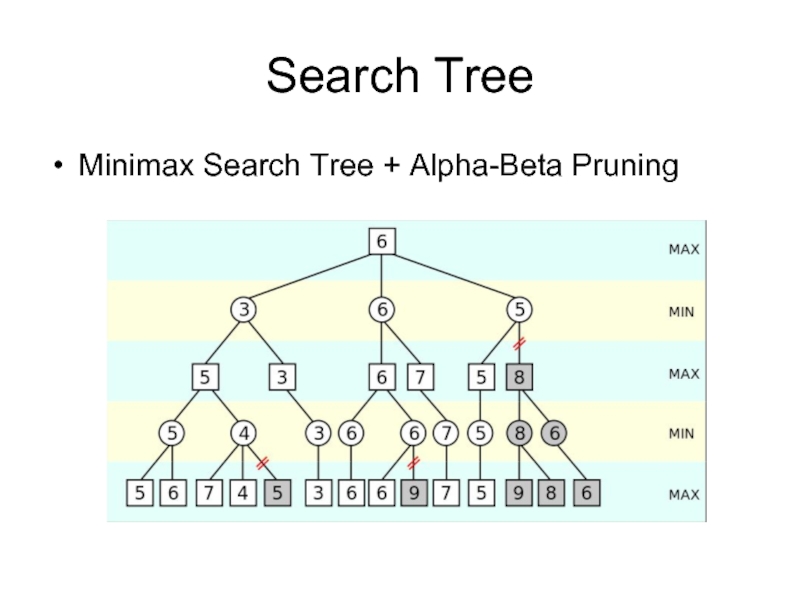

Most papers use a board evaluation function and brute force every possible

Sometimes search forward n-ply using a minimax tree, but cannot examine every move

Most papers use a board evaluation function and brute force every possible

Sometimes search forward n-ply using a minimax tree, but cannot examine every move

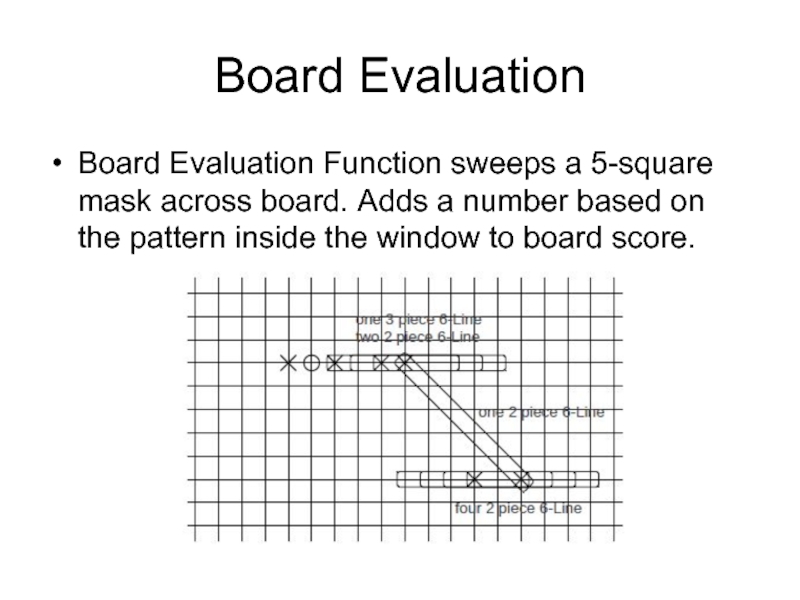

Слайд 4Board Evaluation

Board Evaluation Function sweeps a 5-square mask across board. Adds

a number based on the pattern inside the window to board score.

Слайд 5Board Evaluation (Cont.)

If the board is represented with a bit-board, the

BEF is just bit-manipulation, and can be done in hardware in parallel

Other mask functions can be used to determine relevant squares (squares which extend or block a pattern) and trim away irrelevant positions

Other mask functions can be used to determine relevant squares (squares which extend or block a pattern) and trim away irrelevant positions

Слайд 7Search Tree (Cont.)

To avoid dynamic memory allocation, we will specify how

many moves per level and the maximum height of the tree

The traversal algorithm will also be sequential and not recursive

Possible to parallelize the traversal in hardware

The traversal algorithm will also be sequential and not recursive

Possible to parallelize the traversal in hardware

Слайд 8Hardware Acceleration

Instead of checking the squares in a mask sequentially, a

hardware module can do all the checks in one cycle

CPU writes data to predefined locations, the block reads the data, performs the calculations, and write back result

FSM used to track program state and alert CPU when hardware modules are done

CPU writes data to predefined locations, the block reads the data, performs the calculations, and write back result

FSM used to track program state and alert CPU when hardware modules are done

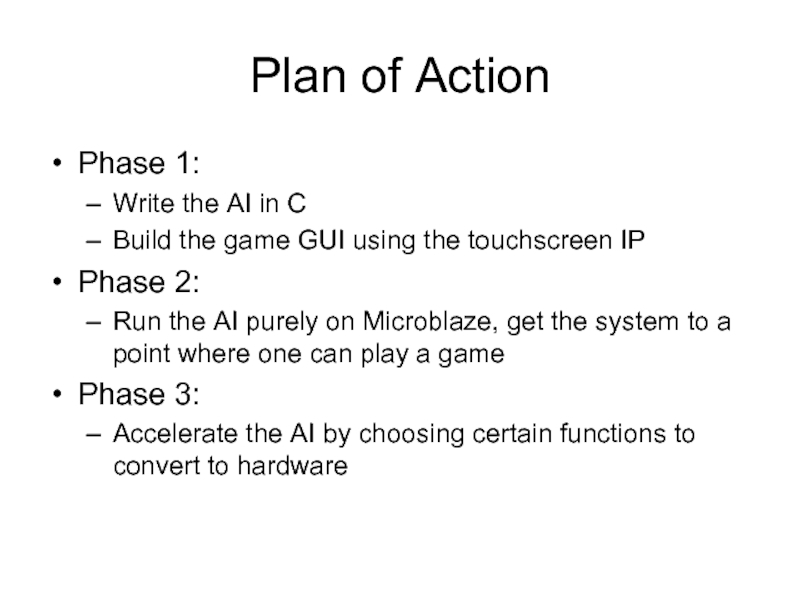

Слайд 10Plan of Action

Phase 1:

Write the AI in C

Build the game GUI

using the touchscreen IP

Phase 2:

Run the AI purely on Microblaze, get the system to a point where one can play a game

Phase 3:

Accelerate the AI by choosing certain functions to convert to hardware

Phase 2:

Run the AI purely on Microblaze, get the system to a point where one can play a game

Phase 3:

Accelerate the AI by choosing certain functions to convert to hardware