- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Исследование аппаратной предвыборки данных в кэш второго уровня микропроцессора Студент: Гребенкин А.П., 816 гр. Научный руководитель: Черепанов С.А. презентация

Содержание

- 1. Исследование аппаратной предвыборки данных в кэш второго уровня микропроцессора Студент: Гребенкин А.П., 816 гр. Научный руководитель: Черепанов С.А.

- 2. Основные классы алгоритмов аппаратной предвыборки Использующие принцип

- 3. Цель исследования

- 4. Выделение постоянного шага (Stride) Класс инструкций ”с

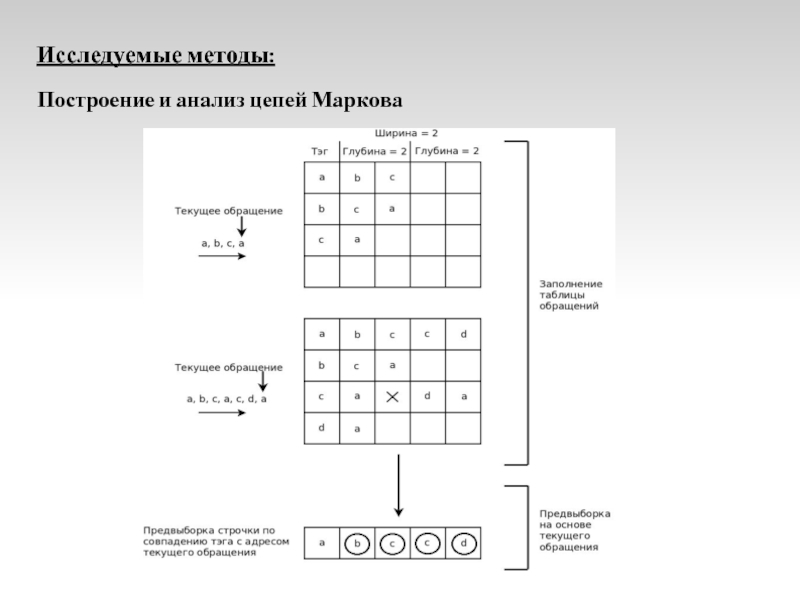

- 5. Исследуемые методы:

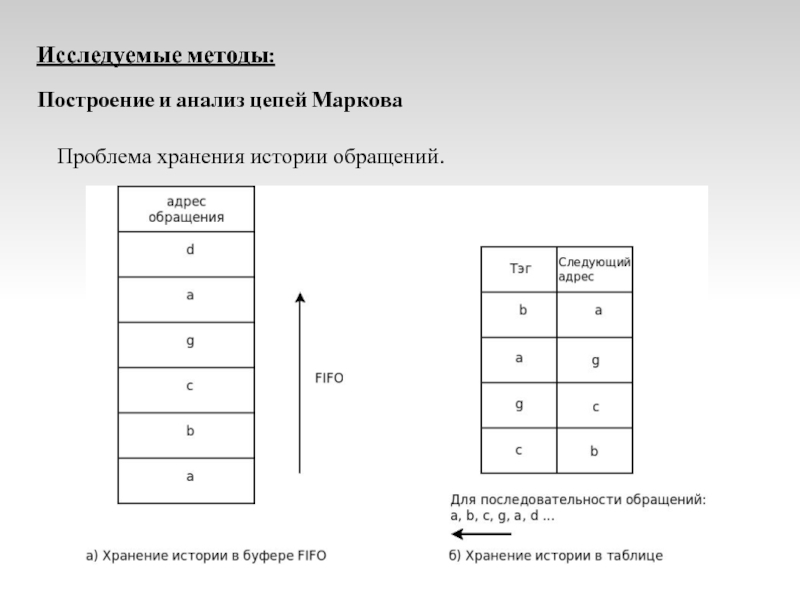

- 6. Проблема хранения истории обращений. Исследуемые методы:

- 7. Исследуемые методы:

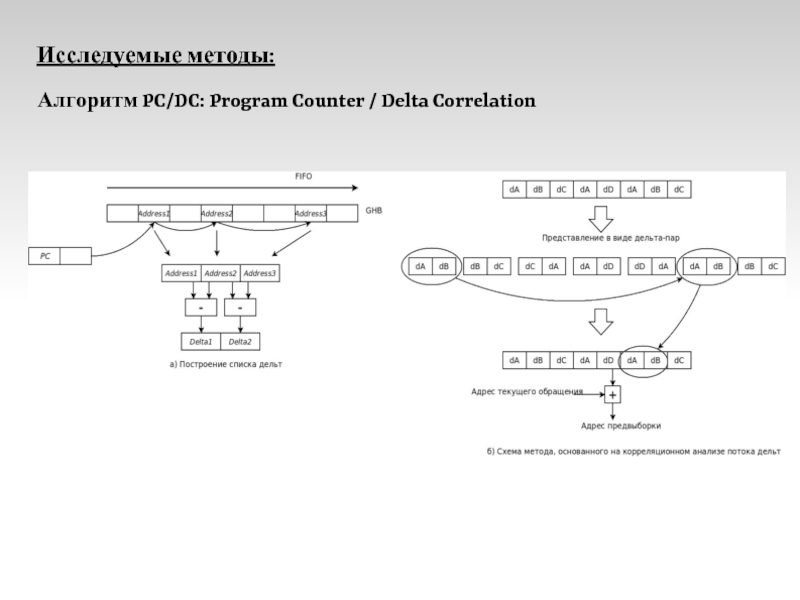

- 8. Исследуемые методы:

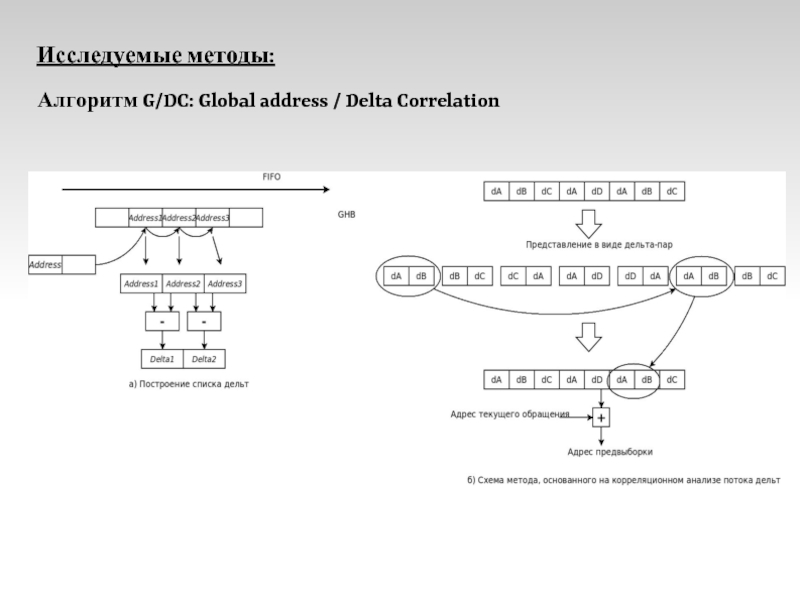

- 9. Исследуемые методы:

- 10. Методология

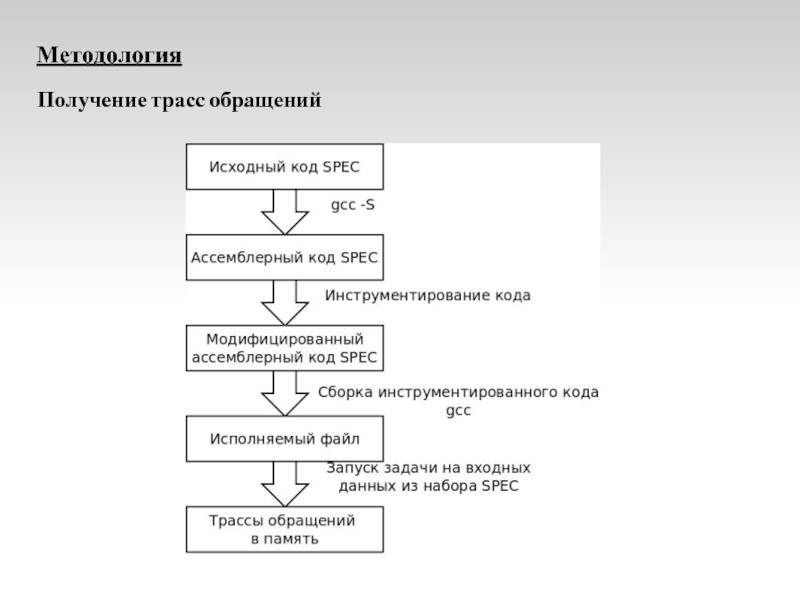

- 11. Методология

- 12. Методология

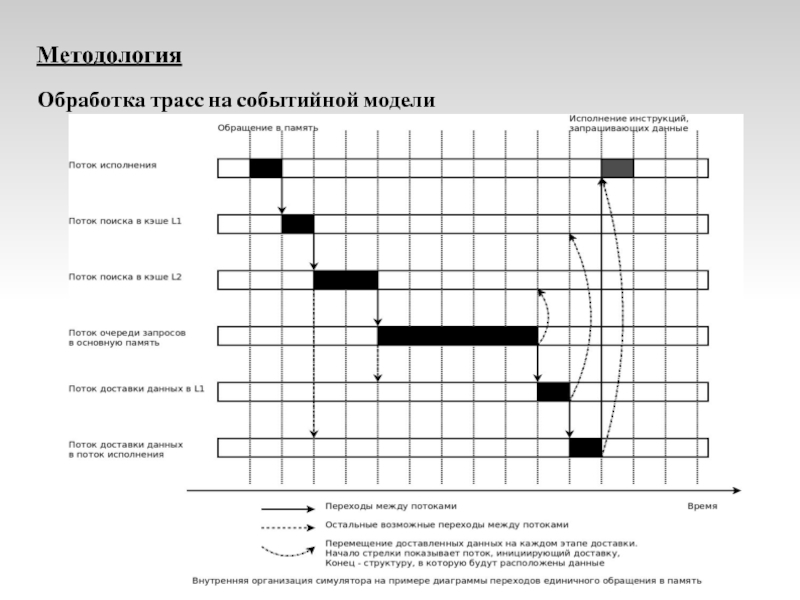

- 13. Методология

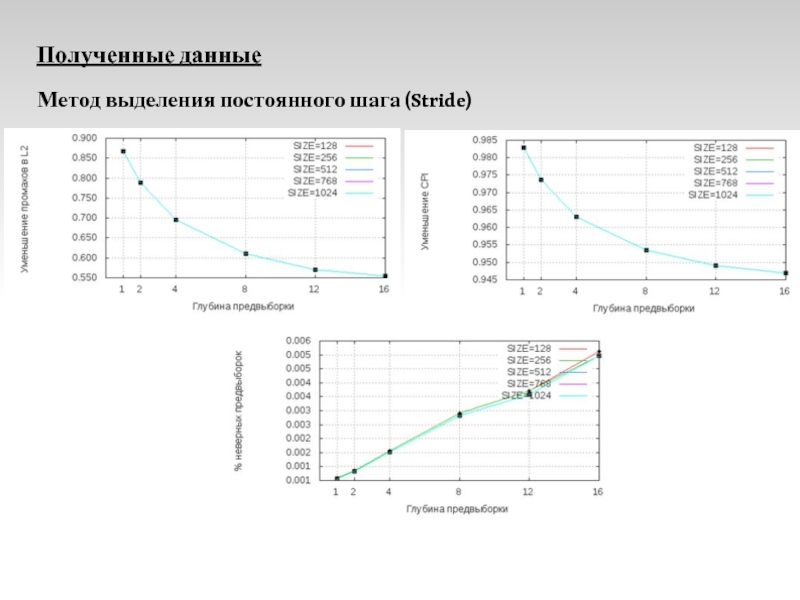

- 14. Полученные данные

- 15. Полученные данные

- 16. Полученные данные

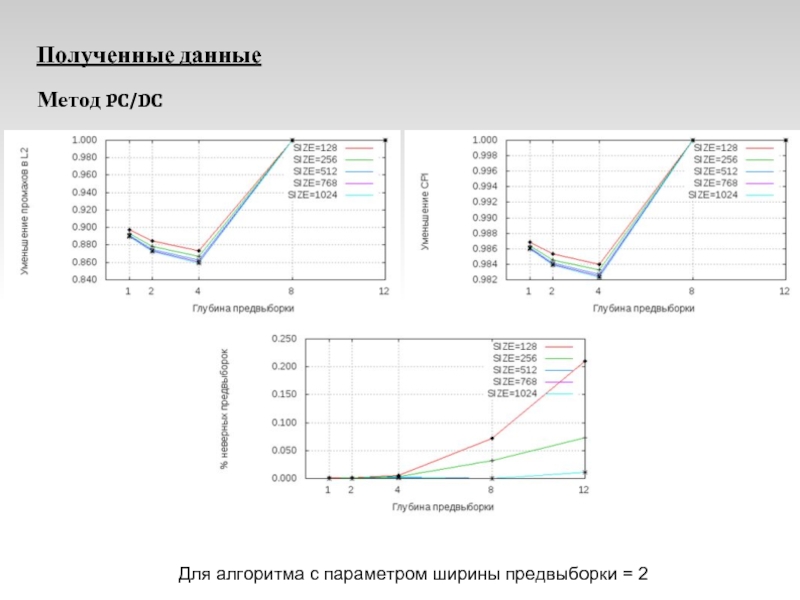

- 17. Полученные данные

- 18. Полученные данные

- 19. Полученные данные

- 20. Полученные данные

- 21. Выводы

- 22. Разработана методология исследования: создана система автоматизации получения

- 23. Направления дальнейшей работы

- 24. Спасибо за внимание

- 25. Приложение

Слайд 1Выпускная квалификационная работа

Исследование аппаратной предвыборки данных в кэш второго уровня микропроцессора

Студент:

Научный руководитель: Черепанов С.А.

Слайд 2Основные классы алгоритмов аппаратной предвыборки

Использующие принцип локальности данных

Применение: исходный код

Использующие корреляционный анализ адресов последовательных обращений

Применение: крупные линейные участки кода; циклы, не зависящие явно от итератора.

Использующие корреляционный анализ адресов обращений для отдельно взятых инструкций

Применение: циклы, зависящие явно от итератора.

Слайд 3Цель исследования

Разработка методологии и оценка эффективности основных методов аппаратной предвыборки данных в кэш второго уровня

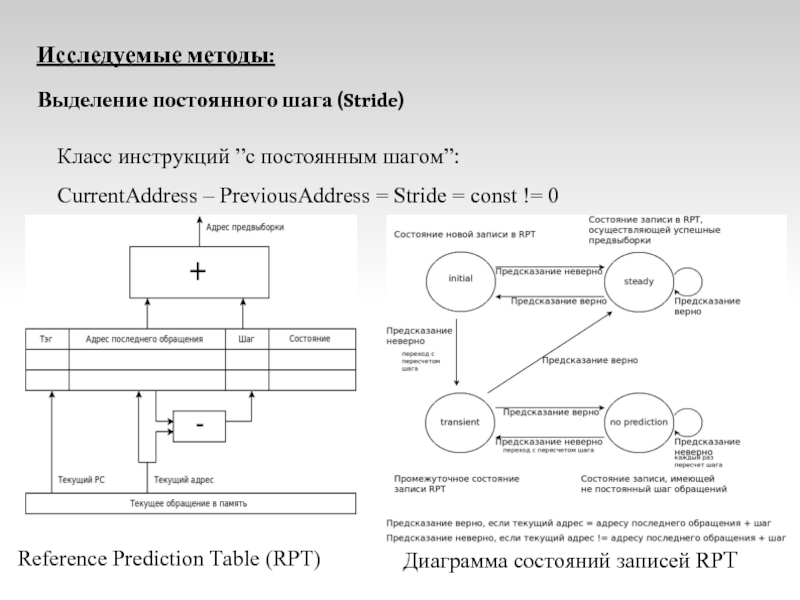

Слайд 4Выделение постоянного шага (Stride)

Класс инструкций ”с постоянным шагом”:

CurrentAddress – PreviousAddress =

Reference Prediction Table (RPT)

Диаграмма состояний записей RPT

Исследуемые методы:

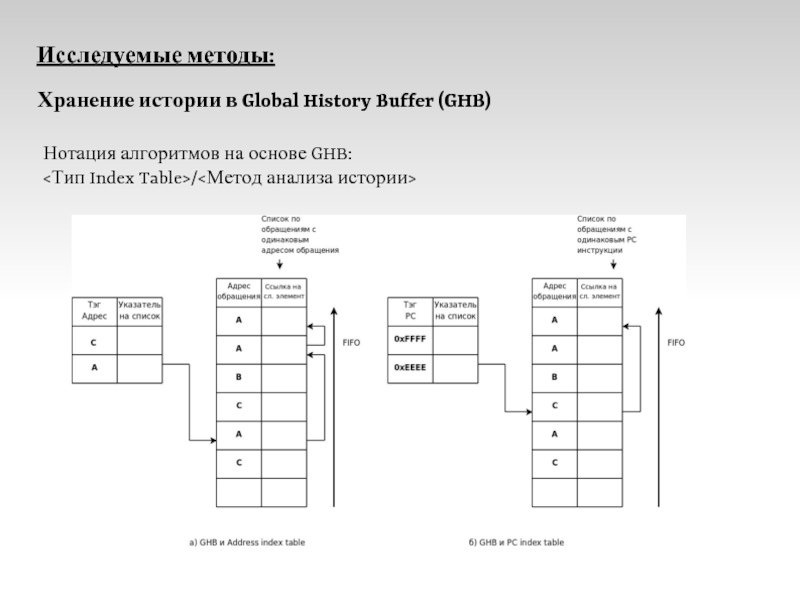

Слайд 7 Исследуемые методы:

Хранение истории в Global History Buffer (GHB)

Нотация алгоритмов на основе GHB:

<Тип Index Table>/<Метод анализа истории>

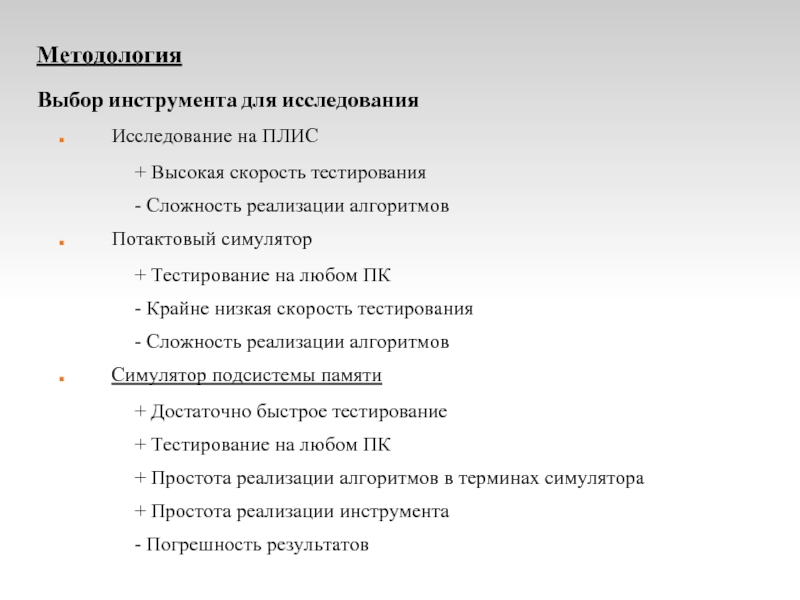

Слайд 10 Методология

Выбор инструмента для исследования

Исследование на ПЛИС

+ Высокая скорость тестирования

- Сложность реализации алгоритмов

Потактовый симулятор

+ Тестирование на любом ПК

- Крайне низкая скорость тестирования

- Сложность реализации алгоритмов

Симулятор подсистемы памяти

+ Достаточно быстрое тестирование

+ Тестирование на любом ПК

+ Простота реализации алгоритмов в терминах симулятора

+ Простота реализации инструмента

- Погрешность результатов

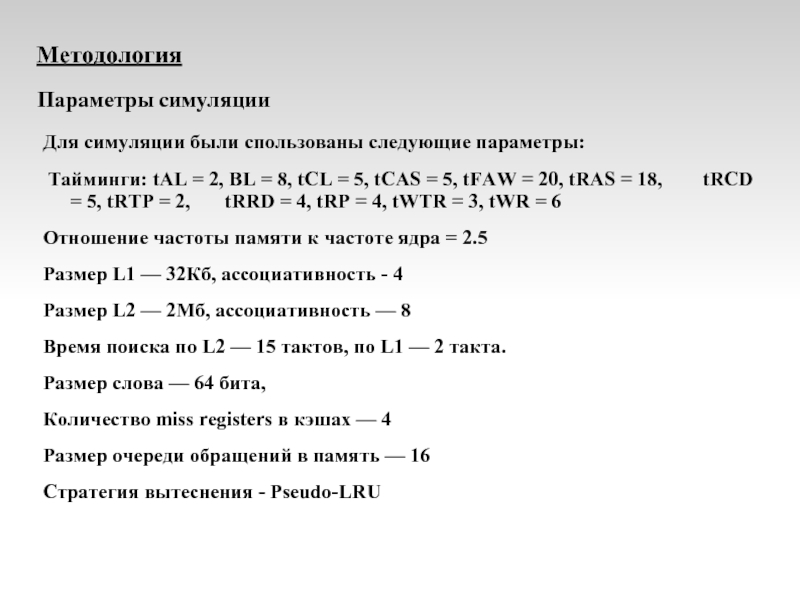

Слайд 13 Методология

Параметры симуляции

Для симуляции были спользованы следующие параметры:

Тайминги: tAL = 2, BL = 8, tCL = 5, tCAS = 5, tFAW = 20, tRAS = 18, tRCD = 5, tRTP = 2, tRRD = 4, tRP = 4, tWTR = 3, tWR = 6

Отношение частоты памяти к частоте ядра = 2.5

Размер L1 — 32Кб, ассоциативность - 4

Размер L2 — 2Мб, ассоциативность — 8

Время поиска по L2 — 15 тактов, по L1 — 2 такта.

Размер слова — 64 бита,

Количество miss registers в кэшах — 4

Размер очереди обращений в память — 16

Стратегия вытеснения - Pseudo-LRU

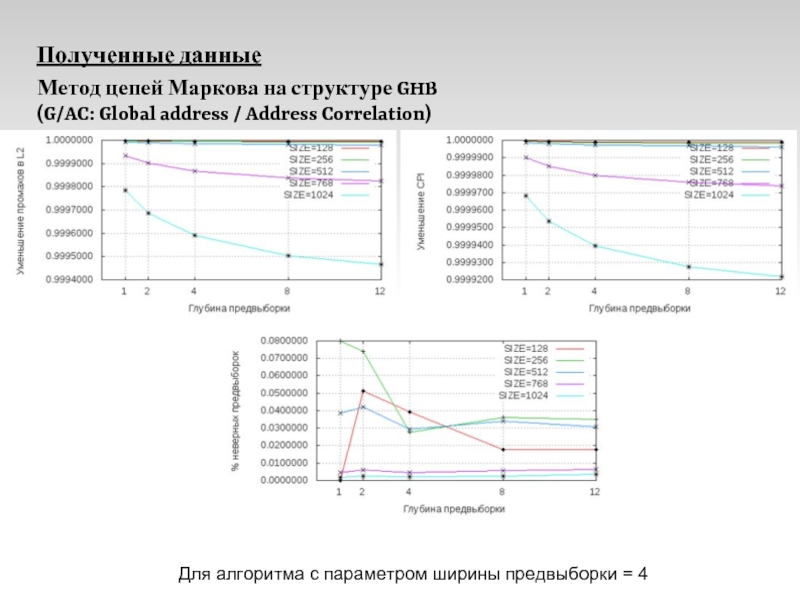

Слайд 15 Полученные данные

Метод цепей Маркова на структуре GHB

(G/AC: Global address / Address Correlation)

Для алгоритма с параметром ширины предвыборки = 4

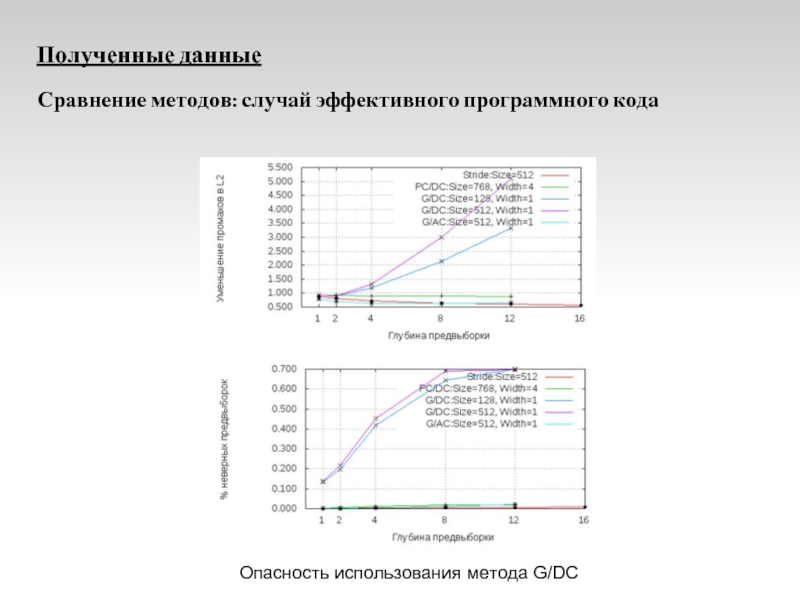

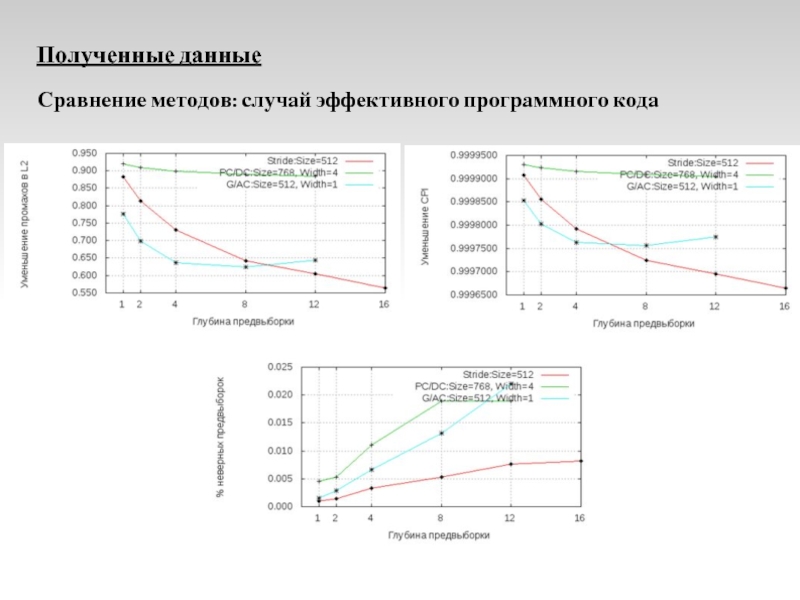

Слайд 19 Полученные данные

Сравнение методов: случай эффективного программного кода

Опасность использования метода G/DC

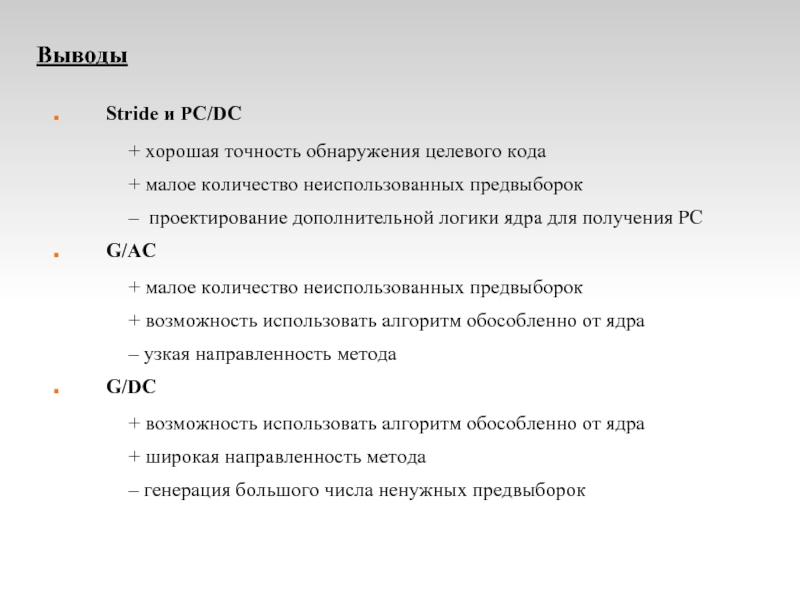

Слайд 21 Выводы

Stride и PC/DC

+ хорошая точность обнаружения целевого кода

+ малое количество неиспользованных предвыборок

– проектирование дополнительной логики ядра для получения PC

G/AC

+ малое количество неиспользованных предвыборок

+ возможность использовать алгоритм обособленно от ядра

– узкая направленность метода

G/DC

+ возможность использовать алгоритм обособленно от ядра

+ широкая направленность метода

– генерация большого числа ненужных предвыборок

Слайд 22Разработана методология исследования: создана система автоматизации получения исходных данных для симуляции

Исследованы 4 класса алгоритмов на симуляционной модели

Результаты

Слайд 23 Направления дальнейшей работы

Осуществление корреляции симулятора с различными реализациями процессоров путем использования в симуляторе соответствующих параметров и аппаратных решений

Разработка эффективных методов предвыборки, оценивая их по разработанной методологии.