VIRTEX

- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Л е к ц и я 8ПЛИС семейства VIRTEX презентация

Содержание

- 1. Л е к ц и я 8ПЛИС семейства VIRTEX

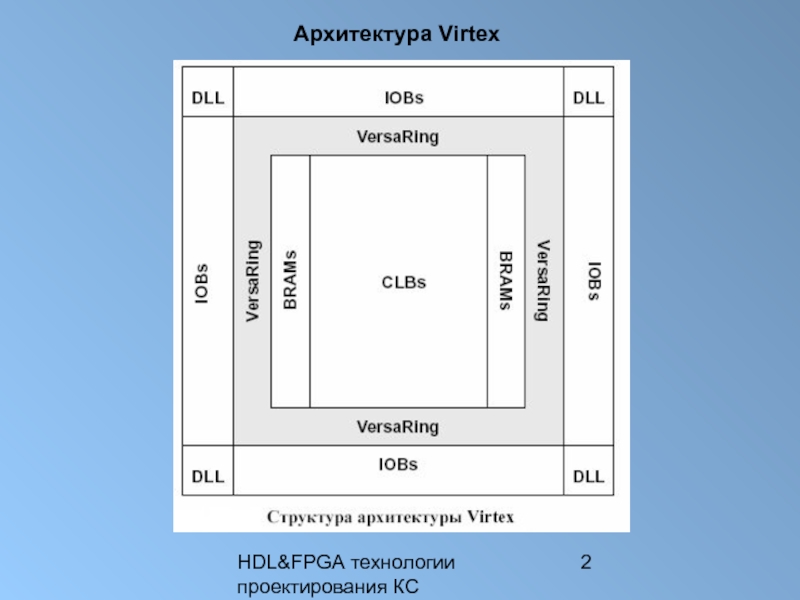

- 2. HDL&FPGA технологии проектирования КС Архитектура Virtex

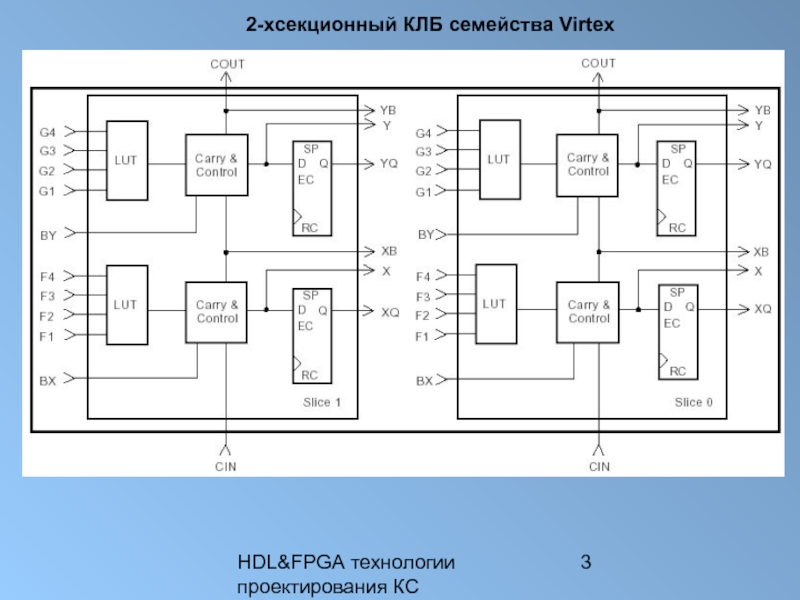

- 3. HDL&FPGA технологии проектирования КС 2-хсекционный КЛБ семейства Virtex

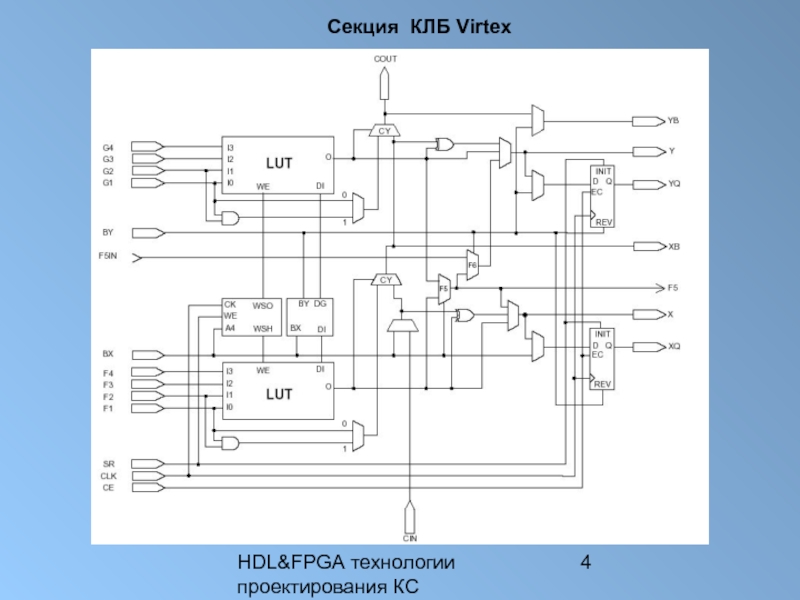

- 4. HDL&FPGA технологии проектирования КС Секция КЛБ Virtex

- 5. HDL&FPGA технологии проектирования КС

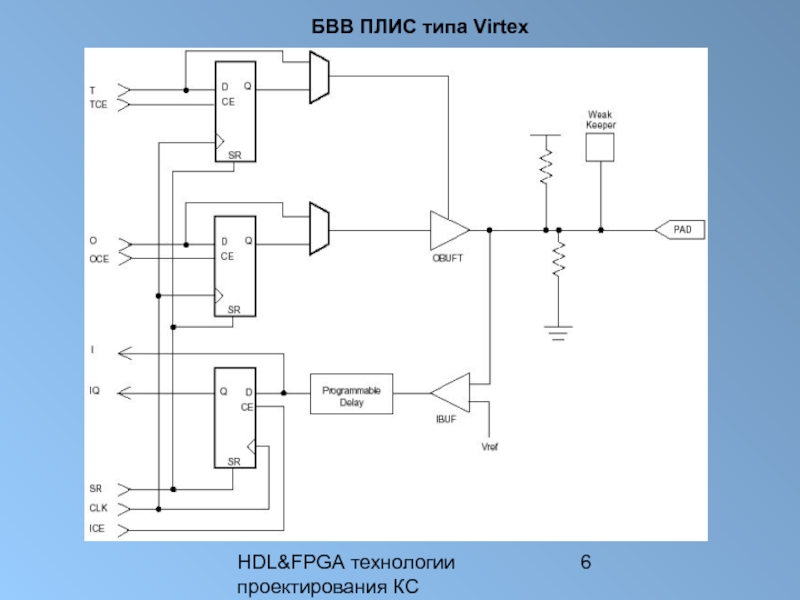

- 6. HDL&FPGA технологии проектирования КС БВВ ПЛИС типа Virtex

- 7. HDL&FPGA технологии проектирования КС Поддерживаемые стандарты ввода/вывода

- 8. HDL&FPGA технологии проектирования КС

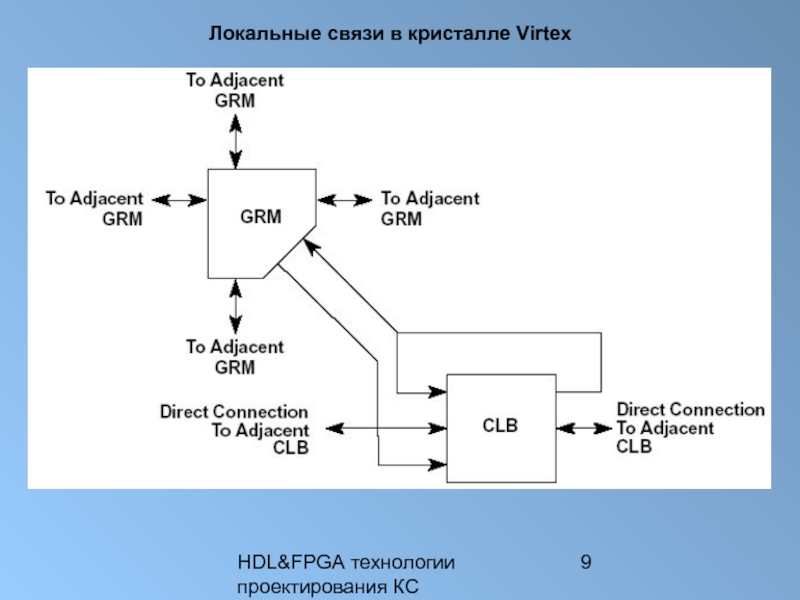

- 9. HDL&FPGA технологии проектирования КС Локальные связи в кристалле Virtex

- 10. HDL&FPGA технологии проектирования КС Основными программируемыми

- 11. HDL&FPGA технологии проектирования КС Подключение трёхстабильных буферов к горизонтальным линиям

- 12. HDL&FPGA технологии проектирования КС Глобальные цепи синхронизации

- 13. HDL&FPGA технологии проектирования КС Основные характеристики семейства

- 14. HDL&FPGA технологии проектирования КС Поддержка

- 15. HDL&FPGA технологии проектирования КС Гибкая архитектура

- 16. HDL&FPGA технологии проектирования КС Конфигурация кристалла

- 17. HDL&FPGA технологии проектирования КС

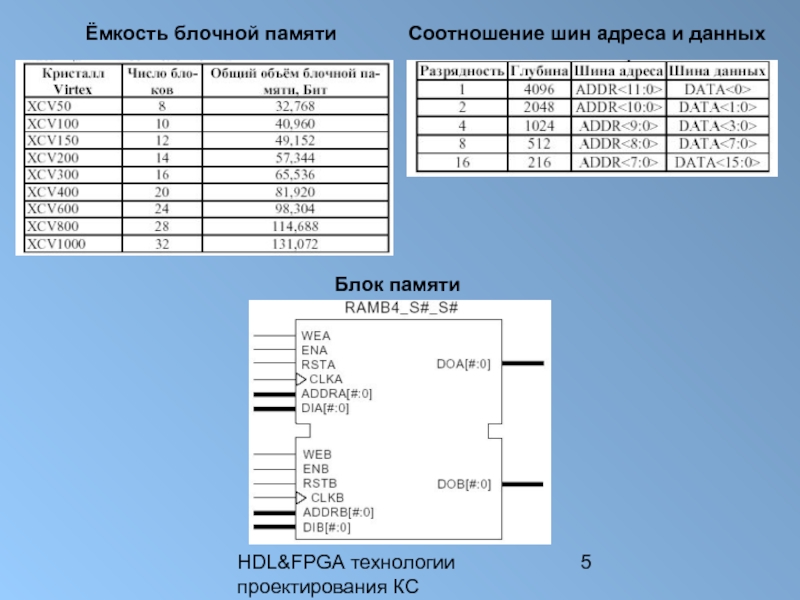

Слайд 5HDL&FPGA технологии проектирования КС

Ёмкость

блочной памяти Соотношение шин адреса и данных

Блок памяти

Слайд 7HDL&FPGA технологии проектирования КС

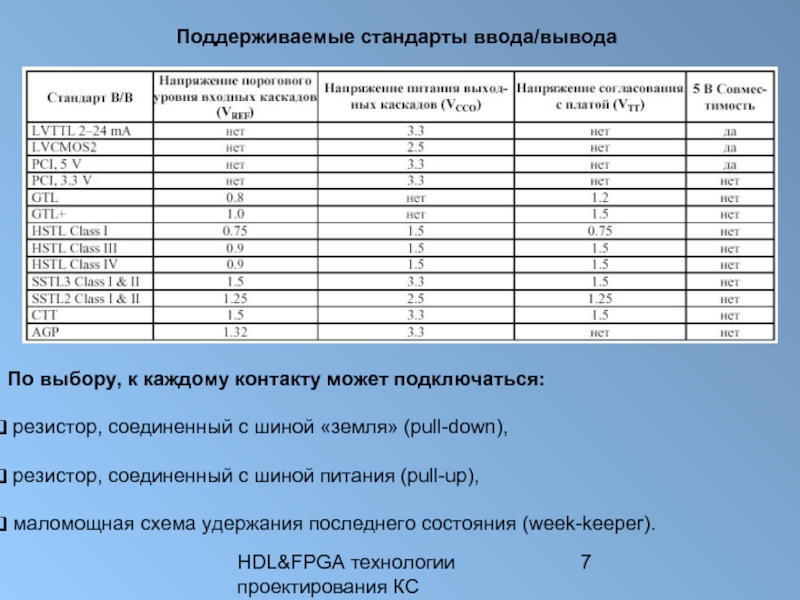

Поддерживаемые стандарты ввода/вывода

По выбору, к каждому контакту может

подключаться:

резистор, соединенный с шиной «земля» (pull-down),

резистор, соединенный с шиной питания (pull-up),

маломощная схема удержания последнего состояния (week-keeper).

резистор, соединенный с шиной «земля» (pull-down),

резистор, соединенный с шиной питания (pull-up),

маломощная схема удержания последнего состояния (week-keeper).

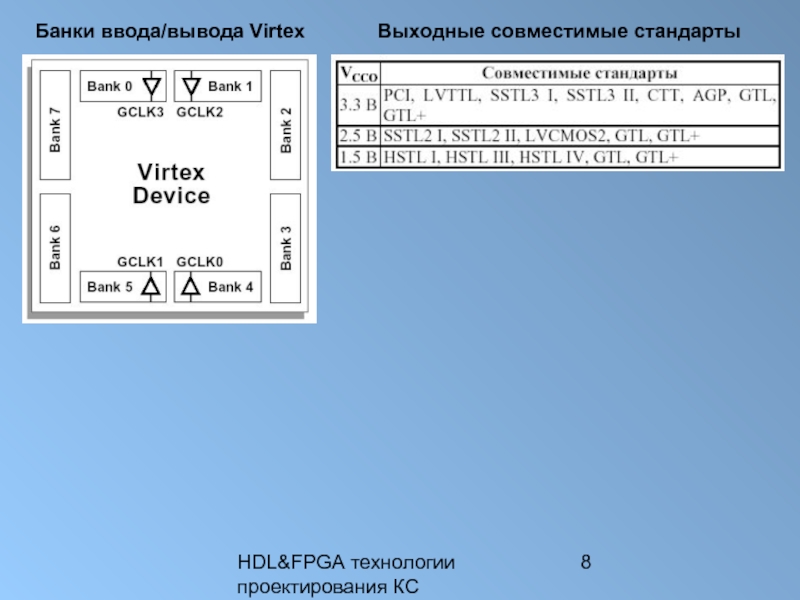

Слайд 8HDL&FPGA технологии проектирования КС

Банки ввода/вывода Virtex

Выходные совместимые стандарты

Слайд 10HDL&FPGA технологии проектирования КС

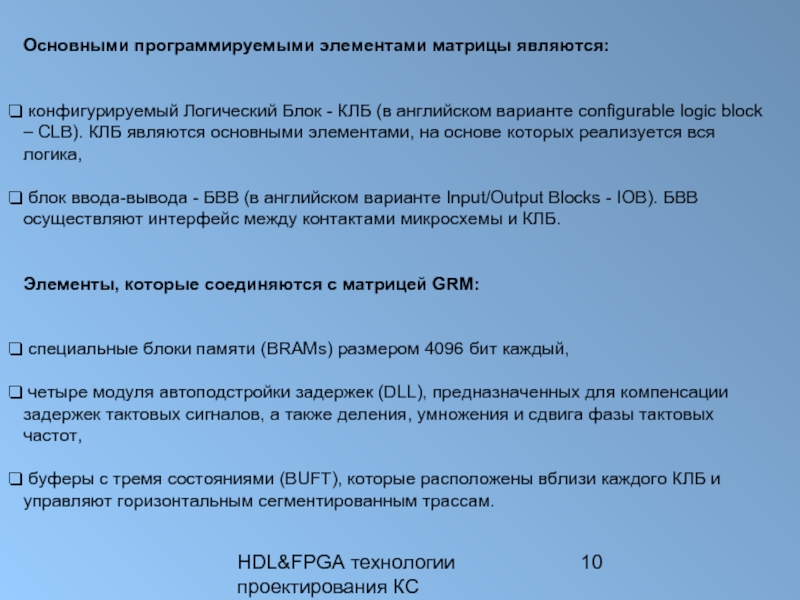

Основными программируемыми элементами матрицы являются:

конфигурируемый Логический Блок

- КЛБ (в английском варианте configurable logic block – CLB). КЛБ являются основными элементами, на основе которых реализуется вся логика,

блок ввода-вывода - БВВ (в английском варианте Input/Output Blocks - IOB). БВВ осуществляют интерфейс между контактами микросхемы и КЛБ.

Элементы, которые соединяются с матрицей GRM:

специальные блоки памяти (BRAMs) размером 4096 бит каждый,

четыре модуля автоподстройки задержек (DLL), предназначенных для компенсации задержек тактовых сигналов, а также деления, умножения и сдвига фазы тактовых частот,

буферы с тремя состояниями (BUFT), которые расположены вблизи каждого КЛБ и управляют горизонтальным сегментированным трассам.

блок ввода-вывода - БВВ (в английском варианте Input/Output Blocks - IOB). БВВ осуществляют интерфейс между контактами микросхемы и КЛБ.

Элементы, которые соединяются с матрицей GRM:

специальные блоки памяти (BRAMs) размером 4096 бит каждый,

четыре модуля автоподстройки задержек (DLL), предназначенных для компенсации задержек тактовых сигналов, а также деления, умножения и сдвига фазы тактовых частот,

буферы с тремя состояниями (BUFT), которые расположены вблизи каждого КЛБ и управляют горизонтальным сегментированным трассам.

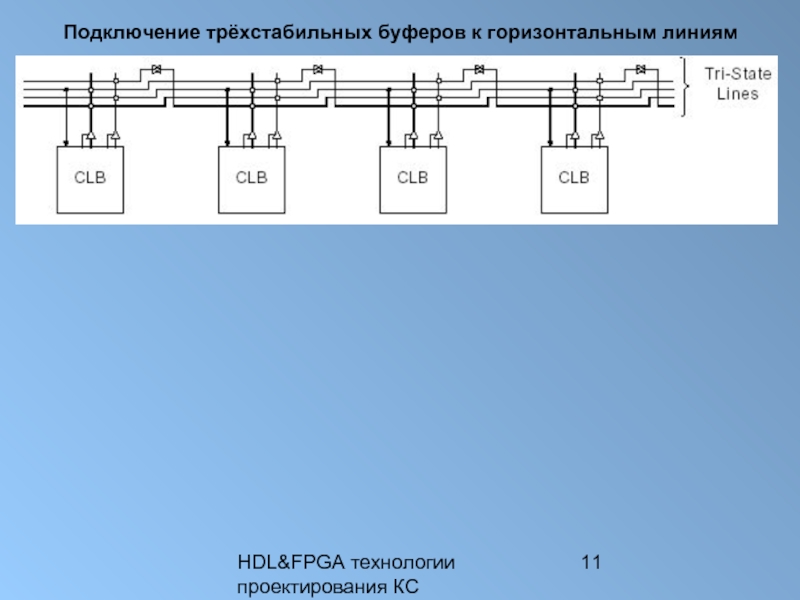

Слайд 11HDL&FPGA технологии проектирования КС

Подключение трёхстабильных буферов к горизонтальным линиям

Слайд 13HDL&FPGA технологии проектирования КС

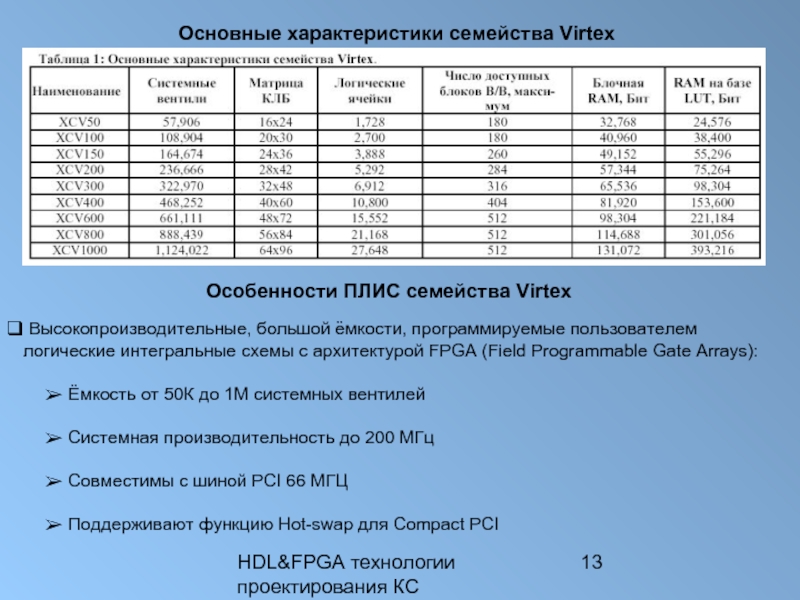

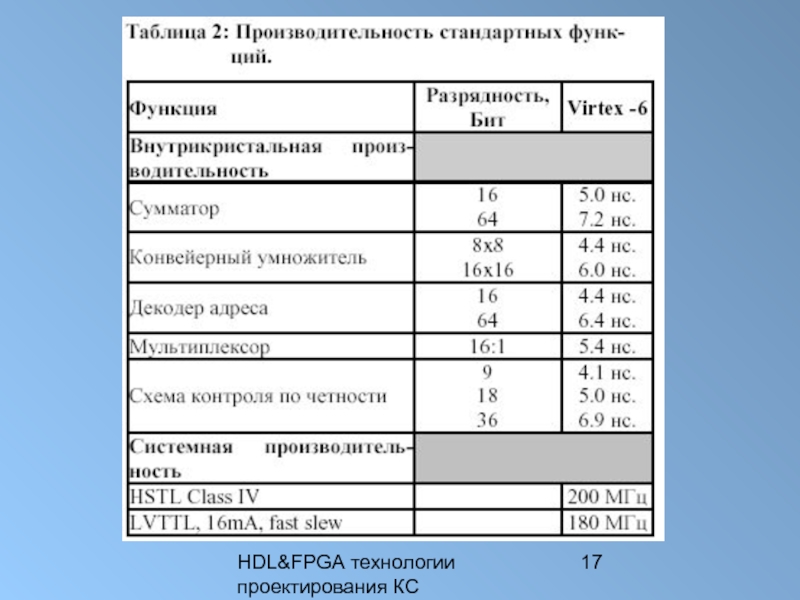

Основные характеристики семейства Virtex

Особенности ПЛИС семейства Virtex

Высокопроизводительные,

большой ёмкости, программируемые пользователем логические интегральные схемы с архитектурой FPGA (Field Programmable Gate Arrays):

Ёмкость от 50К до 1М системных вентилей

Системная производительность до 200 МГц

Совместимы с шиной PCI 66 МГЦ

Поддерживают функцию Hot-swap для Compact PCI

Ёмкость от 50К до 1М системных вентилей

Системная производительность до 200 МГц

Совместимы с шиной PCI 66 МГЦ

Поддерживают функцию Hot-swap для Compact PCI

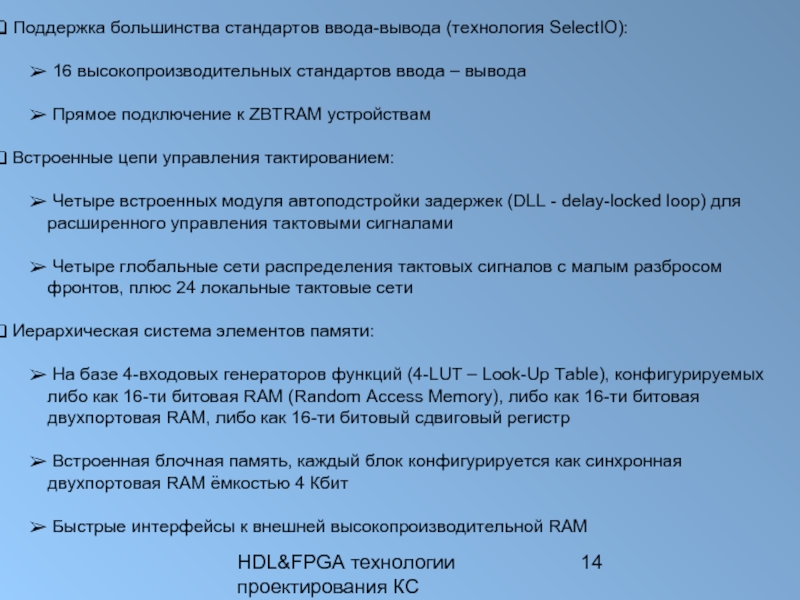

Слайд 14HDL&FPGA технологии проектирования КС

Поддержка большинства стандартов ввода-вывода (технология SelectIO):

16

высокопроизводительных стандартов ввода – вывода

Прямое подключение к ZBTRAM устройствам

Встроенные цепи управления тактированием:

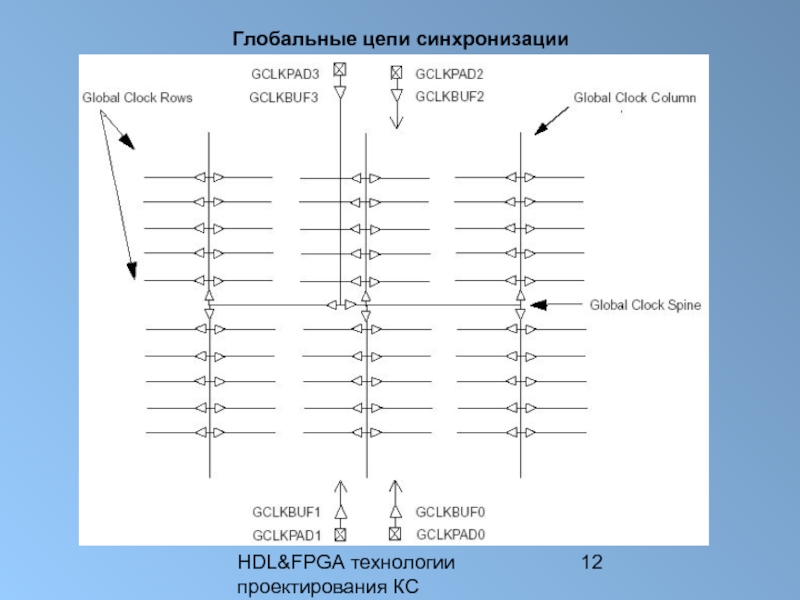

Четыре встроенных модуля автоподстройки задержек (DLL - delay-locked loop) для расширенного управления тактовыми сигналами

Четыре глобальные сети распределения тактовых сигналов с малым разбросом фронтов, плюс 24 локальные тактовые сети

Иерархическая система элементов памяти:

На базе 4-входовых генераторов функций (4-LUT – Look-Up Table), конфигурируемых либо как 16-ти битовая RAM (Random Access Memory), либо как 16-ти битовая двухпортовая RAM, либо как 16-ти битовый сдвиговый регистр

Встроенная блочная память, каждый блок конфигурируется как синхронная двухпортовая RAM ёмкостью 4 Кбит

Быстрые интерфейсы к внешней высокопроизводительной RAM

Прямое подключение к ZBTRAM устройствам

Встроенные цепи управления тактированием:

Четыре встроенных модуля автоподстройки задержек (DLL - delay-locked loop) для расширенного управления тактовыми сигналами

Четыре глобальные сети распределения тактовых сигналов с малым разбросом фронтов, плюс 24 локальные тактовые сети

Иерархическая система элементов памяти:

На базе 4-входовых генераторов функций (4-LUT – Look-Up Table), конфигурируемых либо как 16-ти битовая RAM (Random Access Memory), либо как 16-ти битовая двухпортовая RAM, либо как 16-ти битовый сдвиговый регистр

Встроенная блочная память, каждый блок конфигурируется как синхронная двухпортовая RAM ёмкостью 4 Кбит

Быстрые интерфейсы к внешней высокопроизводительной RAM

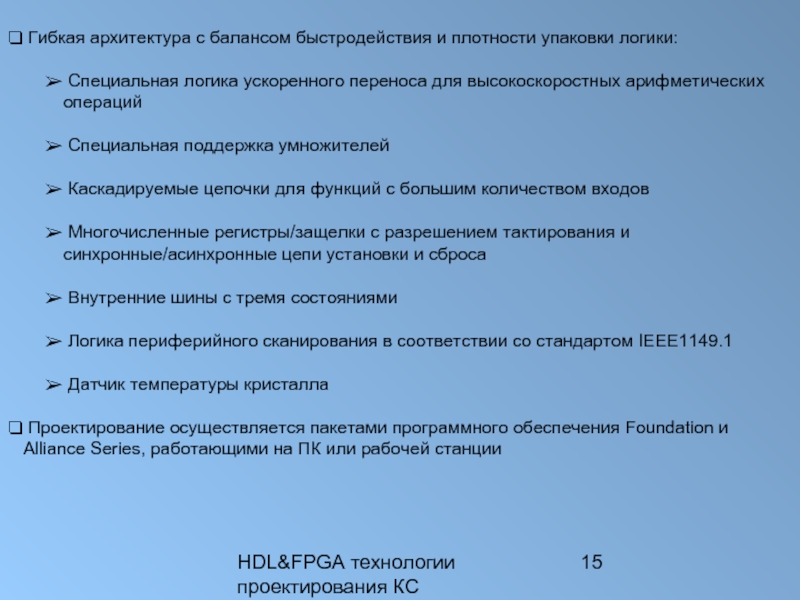

Слайд 15HDL&FPGA технологии проектирования КС

Гибкая архитектура с балансом быстродействия и плотности

упаковки логики:

Специальная логика ускоренного переноса для высокоскоростных арифметических операций

Специальная поддержка умножителей

Каскадируемые цепочки для функций с большим количеством входов

Многочисленные регистры/защелки с разрешением тактирования и синхронные/асинхронные цепи установки и сброса

Внутренние шины с тремя состояниями

Логика периферийного сканирования в соответствии со стандартом IEEE1149.1

Датчик температуры кристалла

Проектирование осуществляется пакетами программного обеспечения Foundation и Alliance Series, работающими на ПК или рабочей станции

Специальная логика ускоренного переноса для высокоскоростных арифметических операций

Специальная поддержка умножителей

Каскадируемые цепочки для функций с большим количеством входов

Многочисленные регистры/защелки с разрешением тактирования и синхронные/асинхронные цепи установки и сброса

Внутренние шины с тремя состояниями

Логика периферийного сканирования в соответствии со стандартом IEEE1149.1

Датчик температуры кристалла

Проектирование осуществляется пакетами программного обеспечения Foundation и Alliance Series, работающими на ПК или рабочей станции

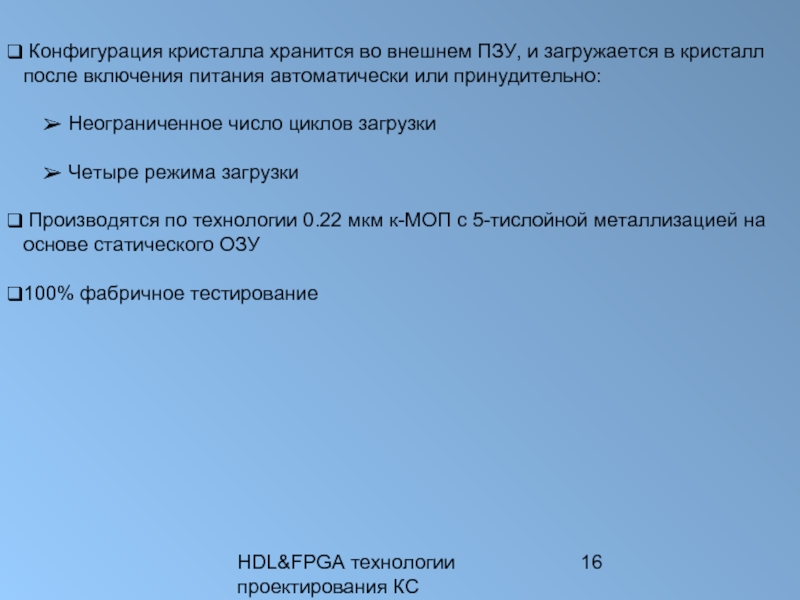

Слайд 16HDL&FPGA технологии проектирования КС

Конфигурация кристалла хранится во внешнем ПЗУ, и

загружается в кристалл после включения питания автоматически или принудительно:

Неограниченное число циклов загрузки

Четыре режима загрузки

Производятся по технологии 0.22 мкм к-МОП с 5-тислойной металлизацией на основе статического ОЗУ

100% фабричное тестирование

Неограниченное число циклов загрузки

Четыре режима загрузки

Производятся по технологии 0.22 мкм к-МОП с 5-тислойной металлизацией на основе статического ОЗУ

100% фабричное тестирование