- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Сумматор презентация

Содержание

- 1. Сумматор

- 2. Основными техническими параметрами сумматоров являются: аппаратная сложность

- 3. Выделяя главные моменты, остановимся лишь на некоторых

- 4. Одноразрядный сумматор Он имеет три входа

- 5. Полные сумматоры тринарные (трёхоперандные) сумматоры по модулю

- 6. Полусумматоры бинарные (двухоперандные) сумматоры по модулю

- 7. Четвертьсумматоры бинарные (двухоперандные) сумматоры по модулю без

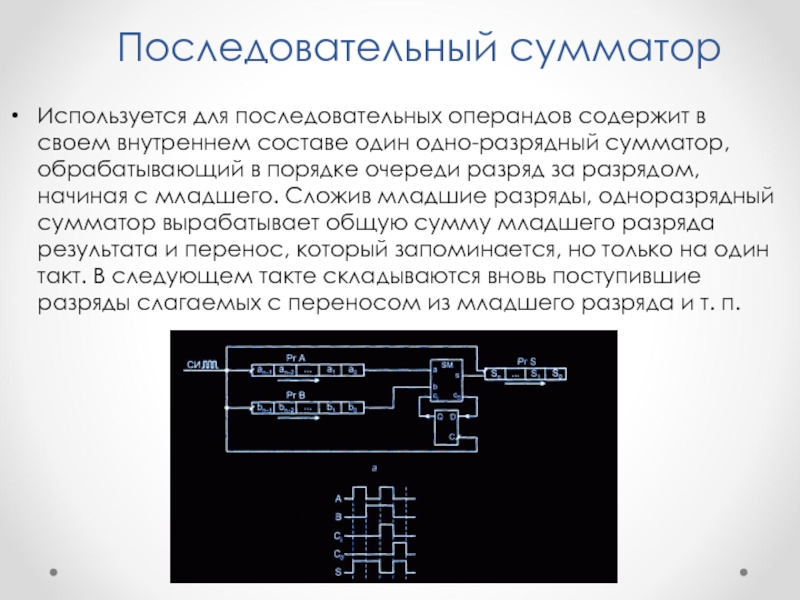

- 8. Последовательный сумматор Используется для последовательных операндов

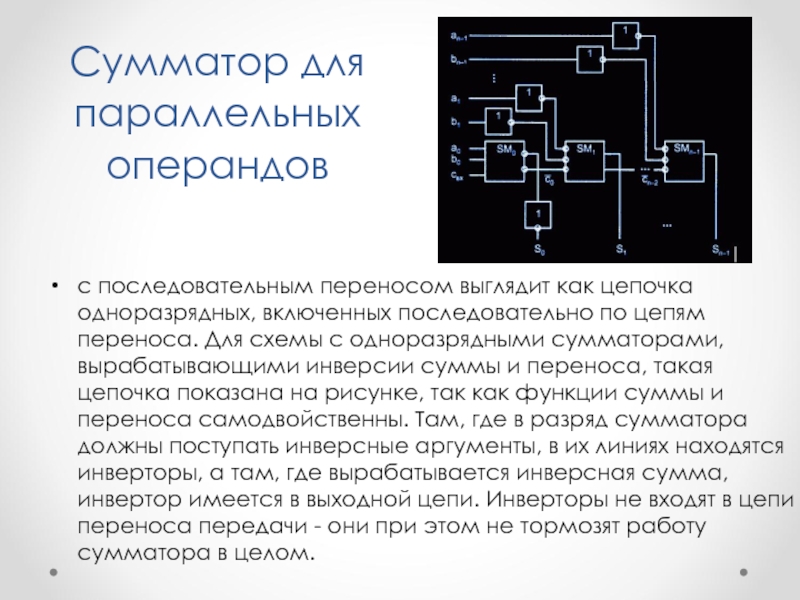

- 9. Сумматор для параллельных операндов с

- 10. Параллельный сумматор с параллельным переносом

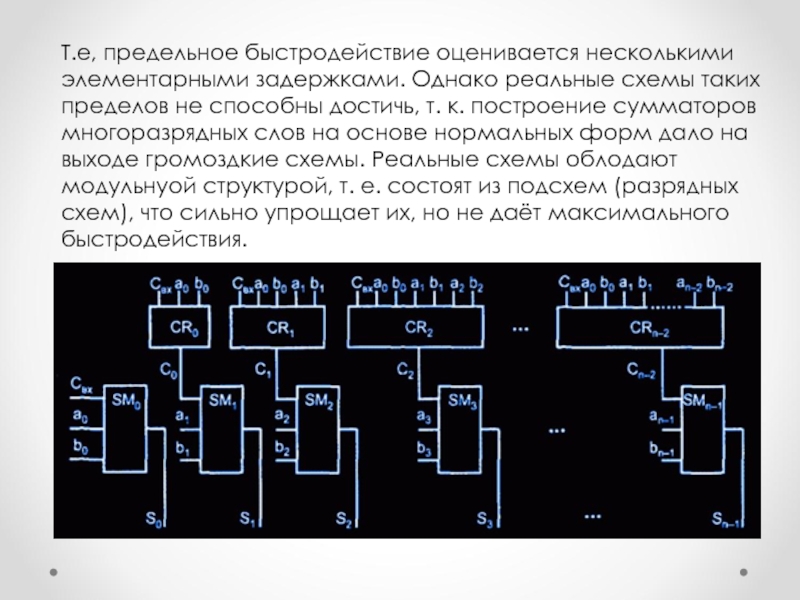

- 11. Т.е, предельное быстродействие оценивается несколькими элементарными задержками.

- 12. Сумматор с передачей сигнала переноса по цепочке

- 13. Сумматор с условным переносом Давно

- 14. Накапливающий снабжённый собственной внутренней памятью. схема,

- 15. По системе счисления сумматоры бывают: Двоичные

Слайд 2Основными техническими параметрами сумматоров являются: аппаратная сложность и быстродействие и поэтому

Сумматоры

- это комбинированные цифровые устройства, осуществляющие арифметическое (в противоположность логическому) сложение и вычитание чисел. Они обладают самостоятельными значениями и являются ядром схем при построение арифметико-логических устройств, реализующих несколько различных операций, являющихся частью всех процессоров.

Слайд 3Выделяя главные моменты, остановимся лишь на некоторых

1) одноразрядный сумматор

2)полные сумматоры

3)полусумматоры

4)четвертьсумматоры

5) сумматор для последовательных операндов

6) для параллельных операндов с последовательным переносом

7) для параллельных операндов с параллельным переносом

8) с последовательным распространением переноса по цепочке замкнутых ключей

9) с условным переносом

10) накапливающий сумматор

Слайд 4Одноразрядный сумматор

Он имеет три входа

(2 слагаемых и перенос

из предыдущего

и 2 выхода (суммы

и переноса

в следующий разряд).

Слайд 5Полные сумматоры

тринарные (трёхоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием

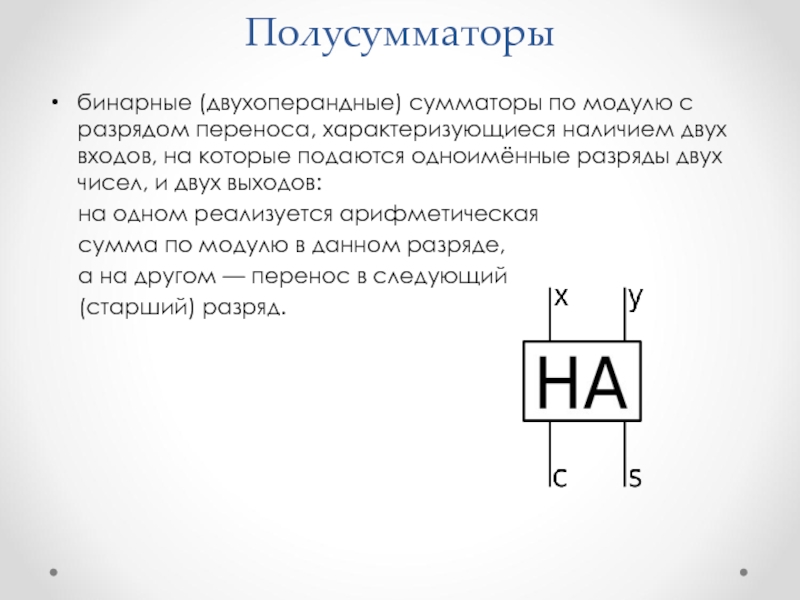

Слайд 6Полусумматоры

бинарные (двухоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием двух

на одном реализуется арифметическая

сумма по модулю в данном разряде,

а на другом — перенос в следующий

(старший) разряд.