- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Організація обчислювальних систем та мереж. Апаратні складові ЕОМ. (Лекція 6) презентация

Содержание

- 1. Організація обчислювальних систем та мереж. Апаратні складові ЕОМ. (Лекція 6)

- 2. Конвейерная обработка данных Конвейерная организация процессора означает,

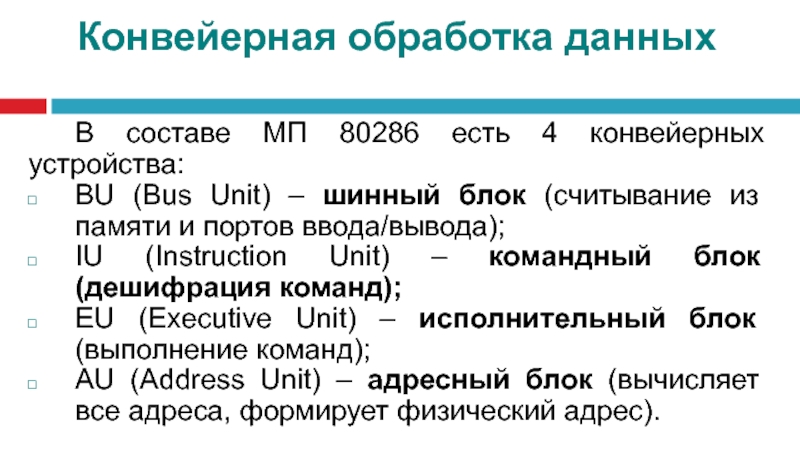

- 3. Конвейерная обработка данных В составе МП 80286

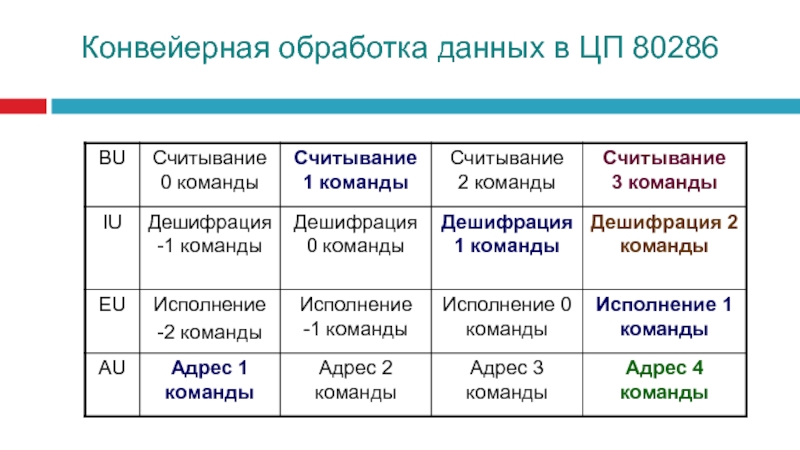

- 4. Конвейерная обработка данных в ЦП 80286

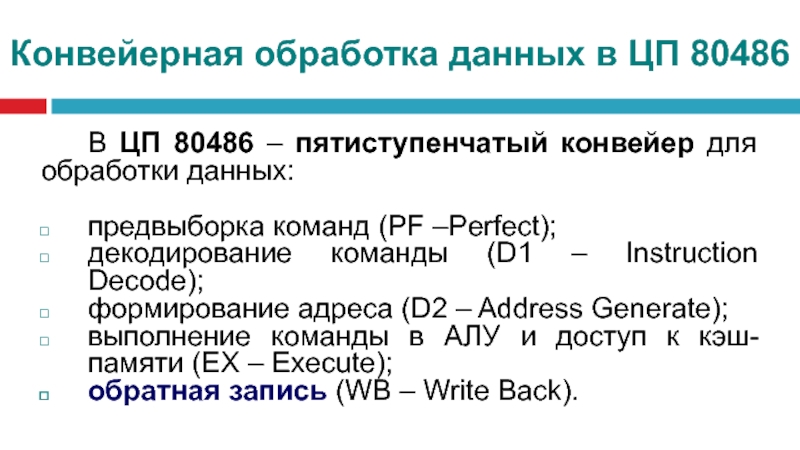

- 5. Конвейерная обработка данных в ЦП 80486 В

- 6. Конвейерная обработка данных Можно выделить два наиболее

- 7. Конвейерная обработка данных Длина конвейера функционального устройства,

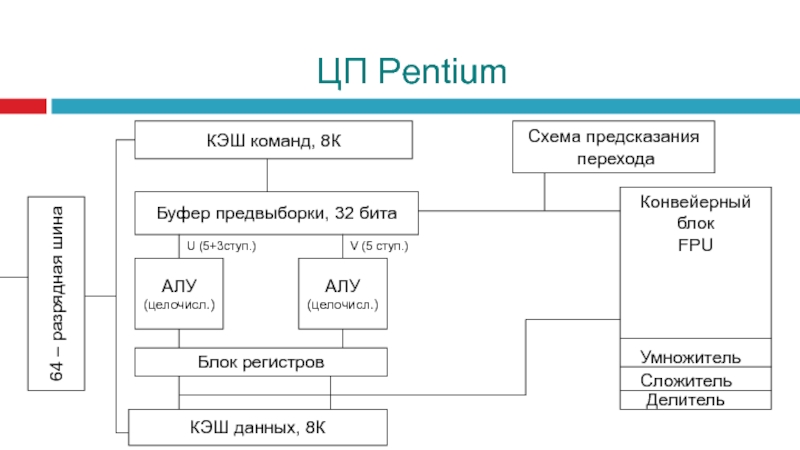

- 8. ЦП Pentium КЭШ команд, 8К Буфер предвыборки,

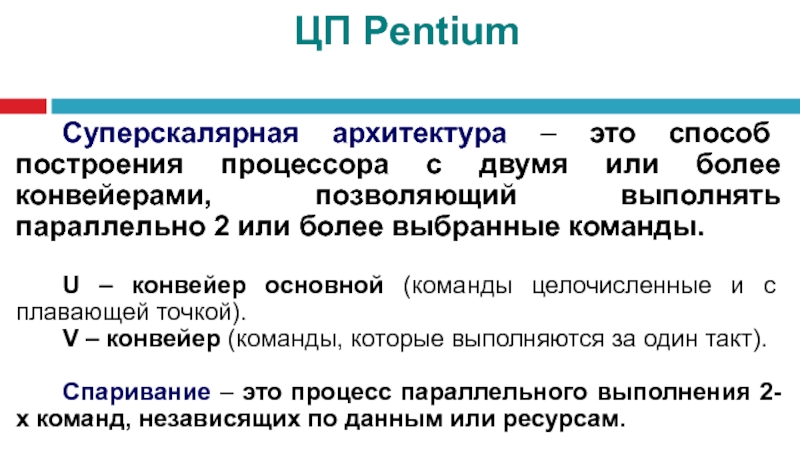

- 9. ЦП Pentium Суперскалярная архитектура – это способ

- 10. Конвейеры ЦП Pentium

- 11. Основные отличия ЦП Pentium Увеличен размер страничной

- 12. Структура микропроцессора Pentium Pro Кэш 2-го уровня,

- 13. ЦП Pentium Pro (P6) Термин динамическое исполнение

- 14. ЦП Pentium MMX Основные черты MMX (MultiMediaeXtention)

- 15. ЦП Pentium II 2 кэша I уровня

- 16. ЦП Pentium III Используется расширение SSE (Streaming

- 17. ЦП Pentium IV В МП Pentium 4

- 19. Линейка процессоров Intel Core 2 Duo

- 20. Процессоры Intel Core i7 Intel выпустила процессоры

- 24. Процессоры компании AMD Развитие современных микроархитектур в

- 25. Однако K8 значительно уступает новому процессору P8

- 26. Многоядерный процессор - центральный процессор,

- 27. Кэш- сверхоперативная память В многоядерных процессорах кэш

- 28. Производительность. В приложениях, оптимизированных под многопоточность, наблюдается

- 29. Наращивание количества ядер. На сегодняшний день основными

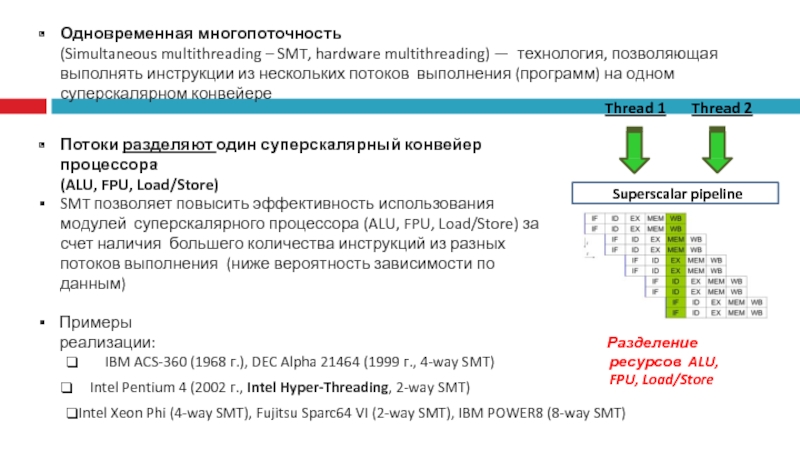

- 30. Одновременная многопоточность (Simultaneous multithreading) Одновременная многопоточность (Simultaneous

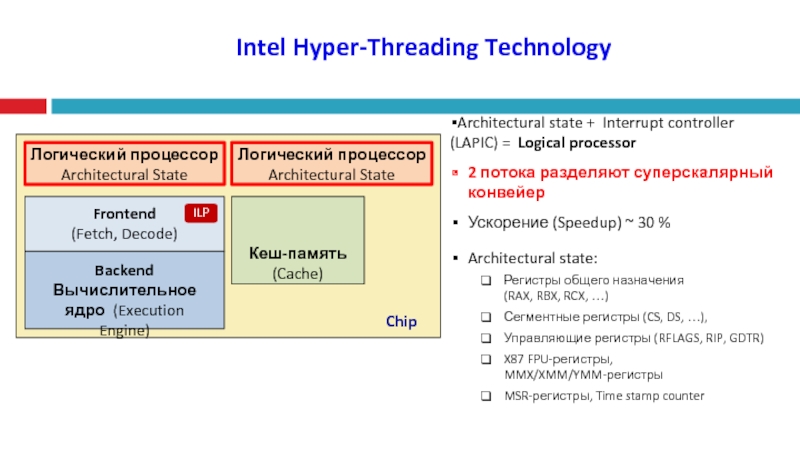

- 31. Intel Hyper-Threading Technology Логический процессор

- 32. Проблемы многоядерности. Многоядерные и Hyper-Threading процессоры не

- 33. Многопроцессорные системы создают много проблем и далеко

- 34. 28 Параллелизм уровня данных (Data Parallelism – DP)

- 35. Векторные процессоры Векторный процессор (Vector processor) –

- 36. Векторные процессоры ▪ Векторный процессор (Vector processor) –

- 37. 33 Параллелизм уровня потоков (Thread Level Parallelism – TLP)

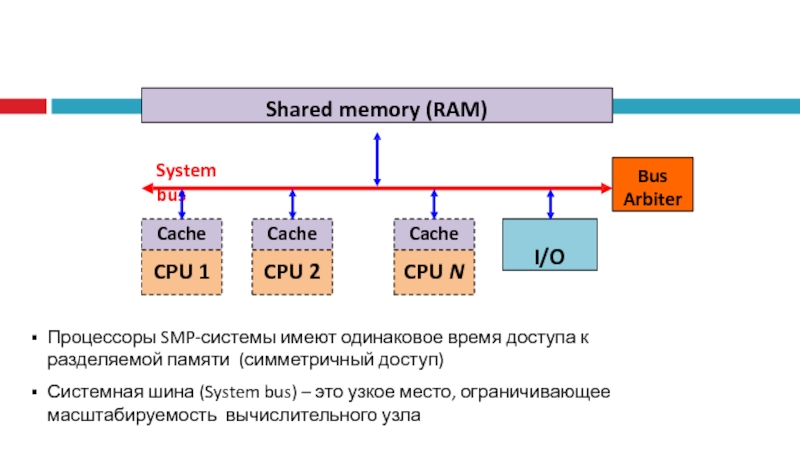

- 38. Многопроцессорные SMP-системы (Symmetric multiprocessing) CPU

- 39. Многопроцессорные SMP-системы (Symmetric multiprocessing)

- 40. Многопроцессорные NUMA-системы (AMD) NUMA (Non-Uniform Memory

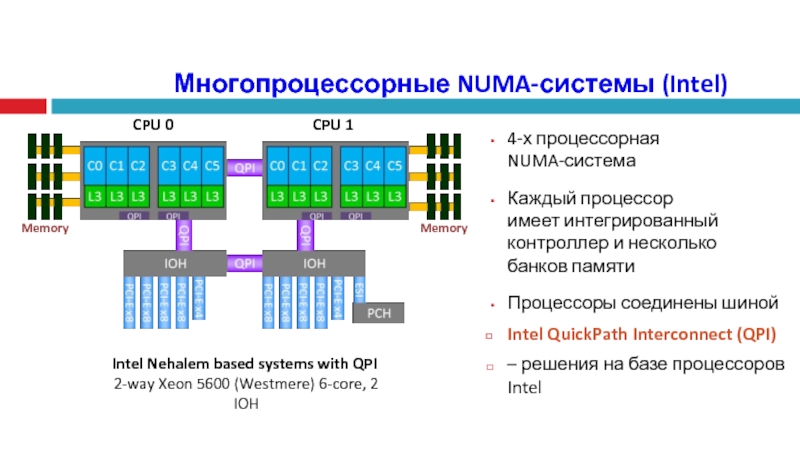

- 41. Многопроцессорные NUMA-системы (Intel) 4-х процессорная NUMA-система Каждый

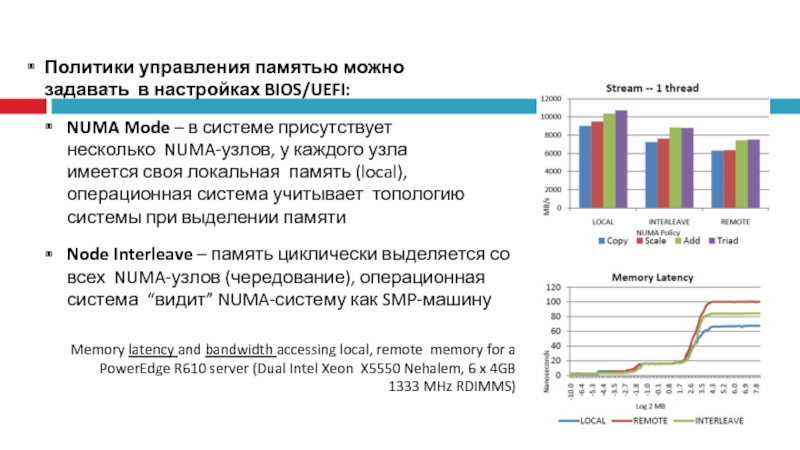

- 42. Политики управления памятью NUMA-системы Политики

- 43. 43 Современные системы на базе многоядерных процессоров

- 44. Современные системы на базе многоядерных процессоров

- 45. Intel Xeon Phi (Intel MIC): 64

- 46. Graphics Processing Unit (GPU) – графический процессор,

- 47. Sony Playstation 3 IBM Cell (2-way SMT

- 48. Система команд Принципы функционирования ЭВМ

- 49. Функциональная и структурная организация ЭВМ Принципы функционирования

- 50. Функциональная и структурная организация ЭВМ Принципы функционирования

- 51. Функциональная и структурная организация ЭВМ При аппаратной

- 52. Функциональная и структурная организация ЭВМ ЭВМ представляет

- 53. Функциональная и структурная организация ЭВМ В основной

- 54. Функциональная и структурная организация ЭВМ Все устройства

- 55. Функциональная и структурная организация ЭВМ В состав

- 56. Функциональная и структурная организация ЭВМ Периферийные устройства

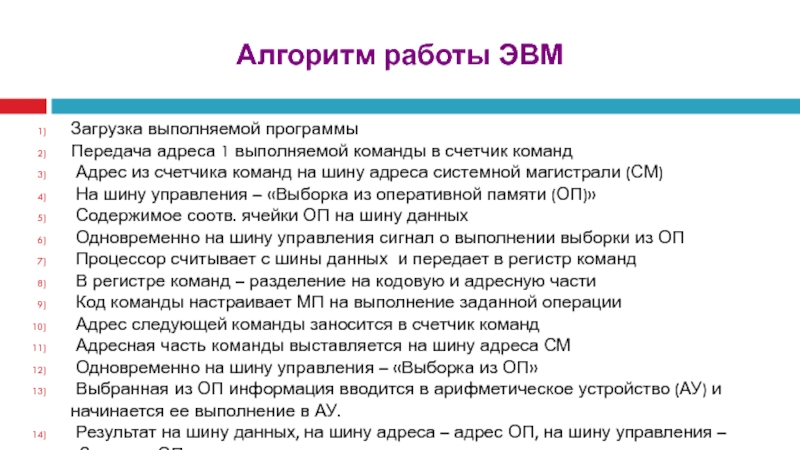

- 57. Алгоритм работы ЭВМ Загрузка выполняемой программы Передача

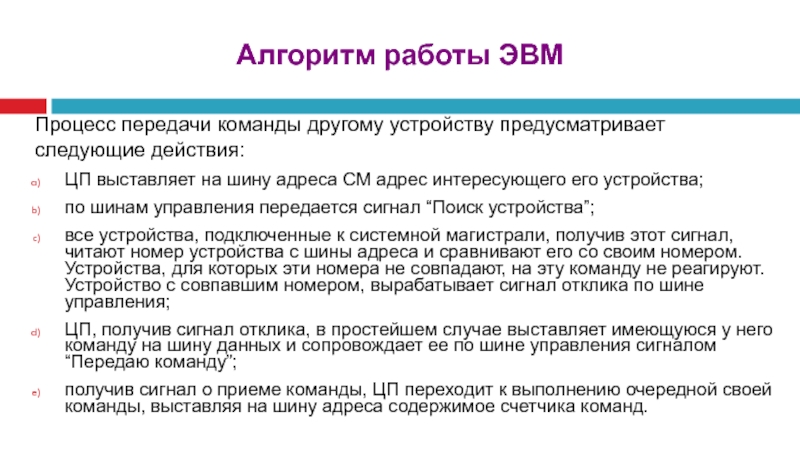

- 58. Алгоритм работы ЭВМ Процесс передачи команды другому

- 59. Память Центральные устройства ЭВМ

- 60. VIII. Организация памяти ЭВМ Памятью ЭВМ называется

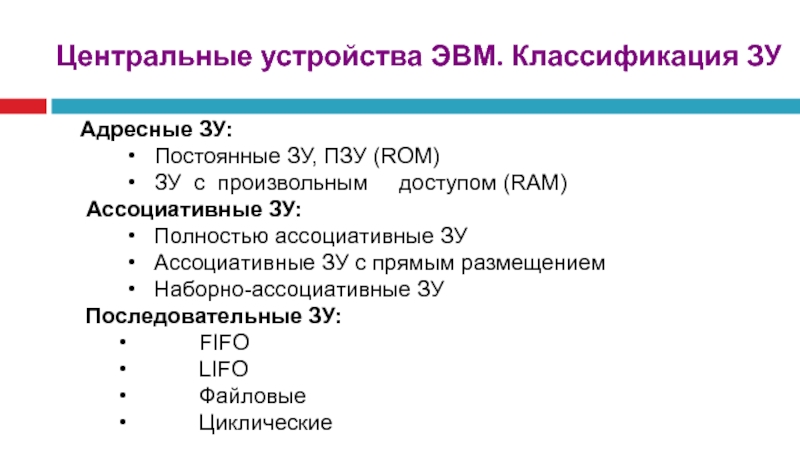

- 61. Адресные ЗУ: Постоянные ЗУ, ПЗУ (ROM) ЗУ

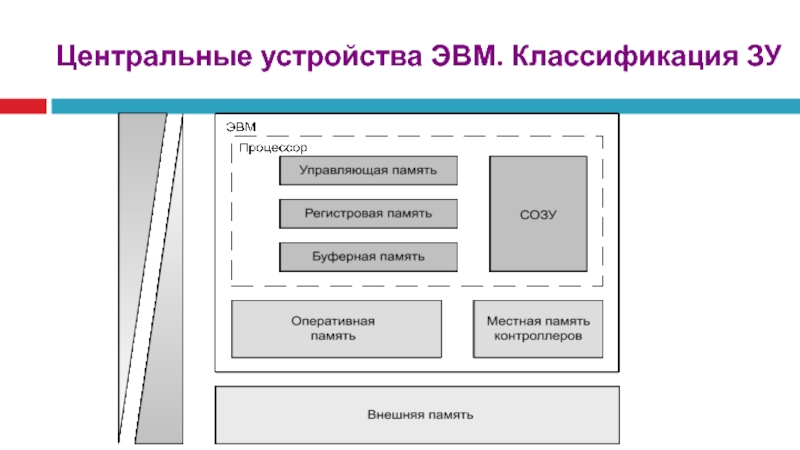

- 62. Центральные устройства ЭВМ. Классификация ЗУ

- 63. Основная память включает два типа устройств: оперативное

- 64. ОЗУ предназначено для хранения переменной информации

- 65. ПЗУ содержит информацию, которая не должна изменяться

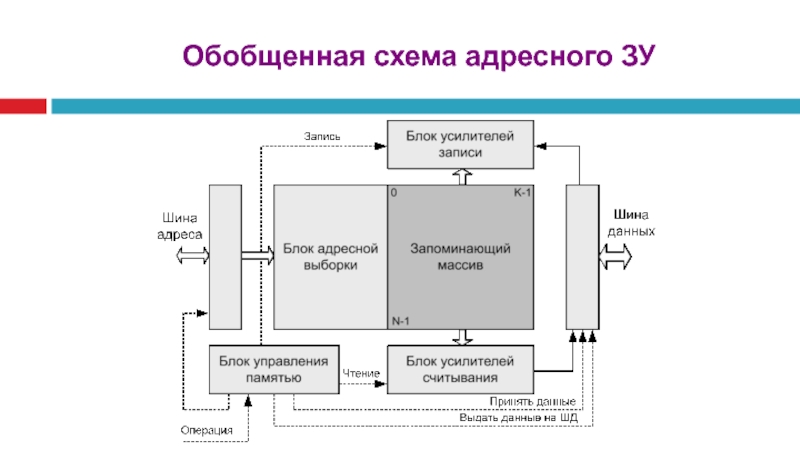

- 66. Обобщенная схема адресного ЗУ

- 67. Обобщенная схема ассоциативного ЗУ

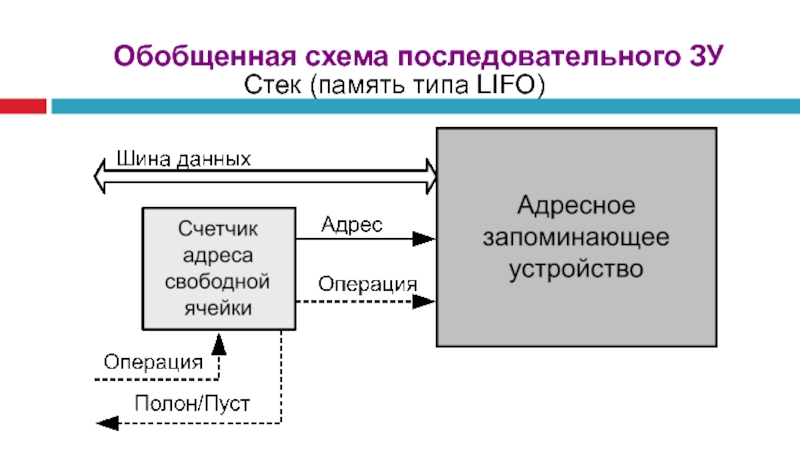

- 68. Обобщенная схема последовательного ЗУ Стек (память типа LIFO)

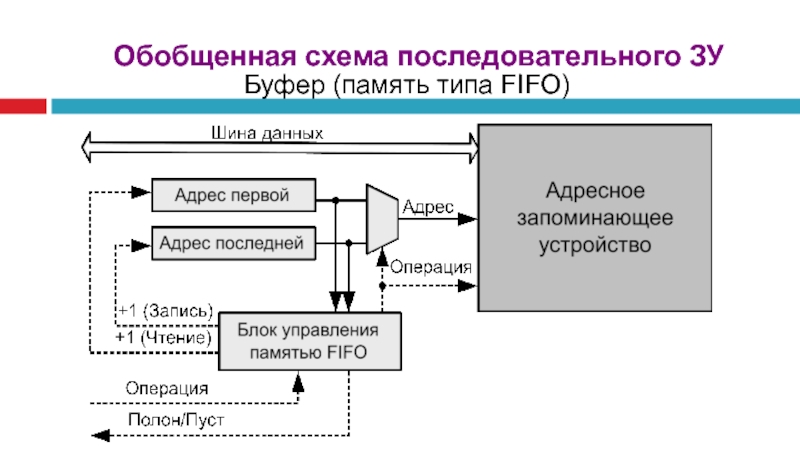

- 69. Обобщенная схема последовательного ЗУ Буфер (память типа FIFO)

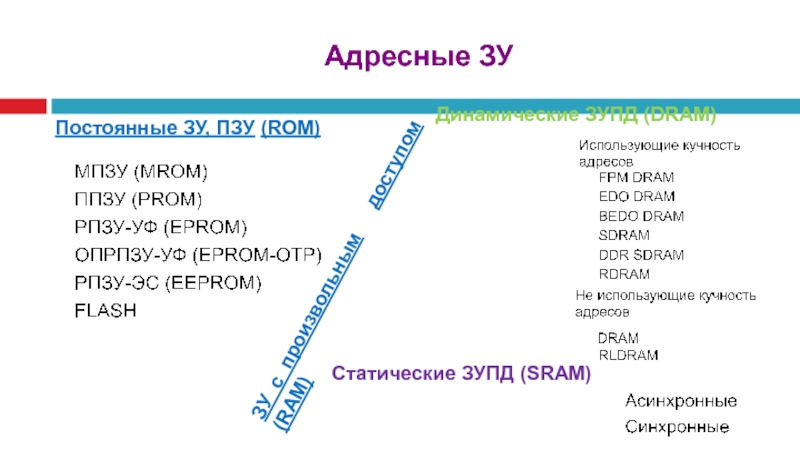

- 70. Адресные ЗУ Постоянные ЗУ, ПЗУ

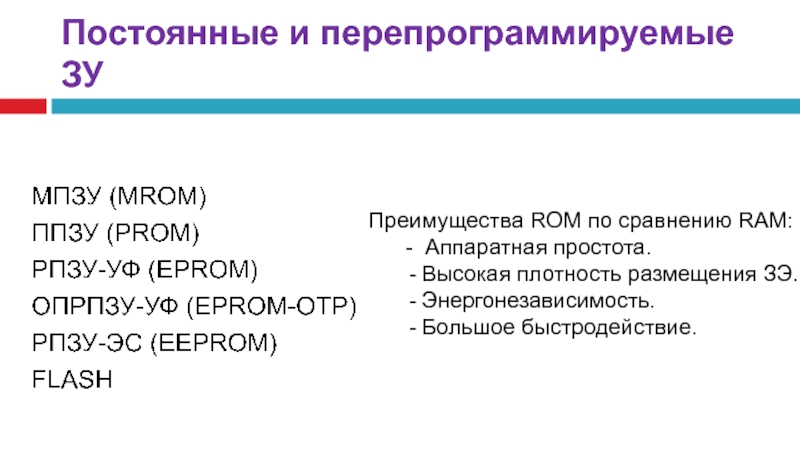

- 71. Постоянные и перепрограммируемые ЗУ Преимущества ROM

- 72. Структура ROM

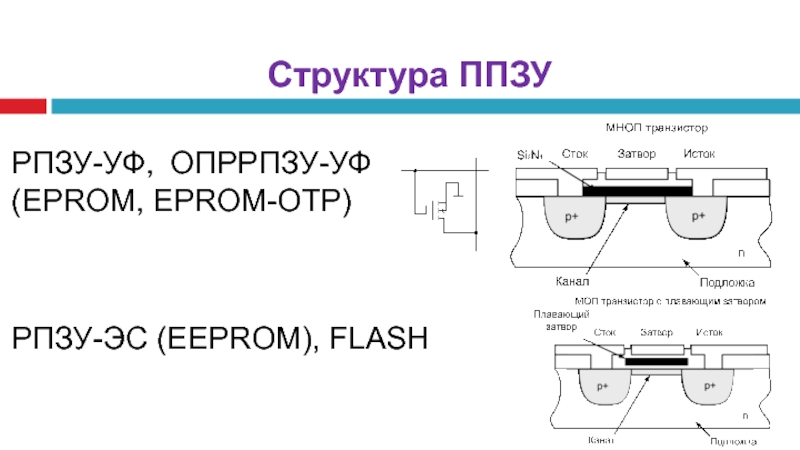

- 73. Структура ППЗУ РПЗУ-УФ, ОПРРПЗУ-УФ (EPROM, EPROM-OTP) РПЗУ-ЭС (EEPROM), FLASH

- 74. Модели оперативной памяти. Сегментированная модель. Программе выделяются

- 75. Особенности использования и реализации моделей памяти

- 76. Сегментация - это механизм адресации, обеспечивающий существование

- 77. - Адрес начала сегмента хранится в соответствующем

- 78. Формирование физического адреса - Диапазон изменения физического

- 79. В сегментном регистре содержаться только старшие 16

- 80. Получившееся 20-битное значение и является настоящим физическим

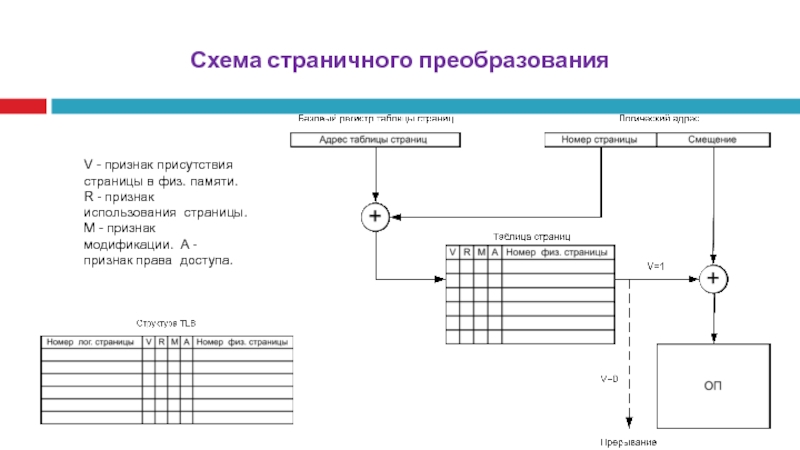

- 81. Схема страничного преобразования V - признак

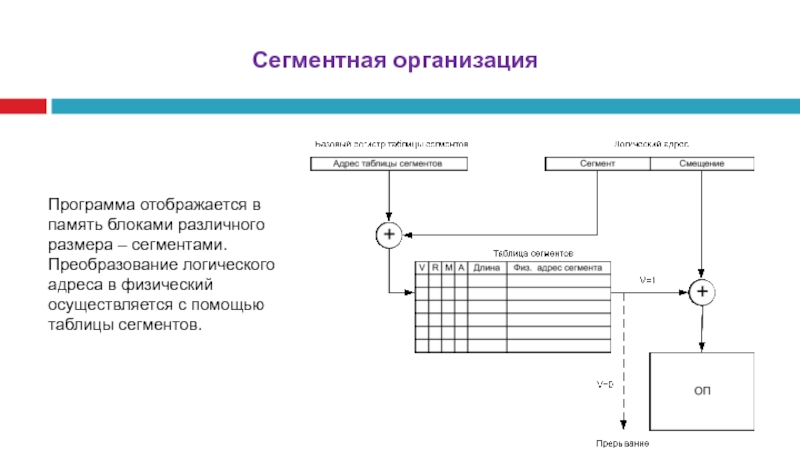

- 82. Сегментная организация Программа отображается в память

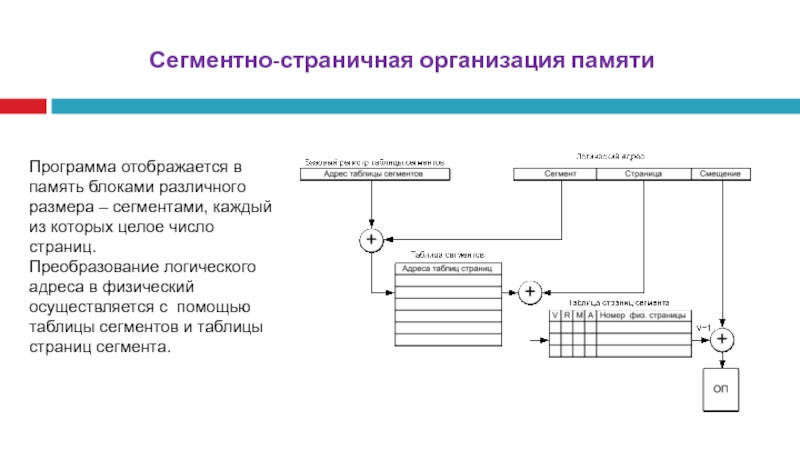

- 83. Сегментно-страничная организация памяти Программа отображается в

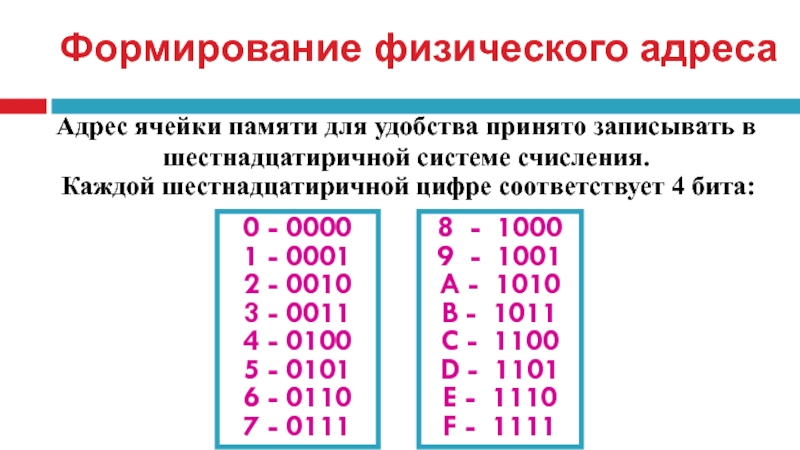

- 84. Адрес ячейки памяти для удобства принято записывать

- 85. Пример формирования физического адреса: - Пусть содержимое

- 86. Размещение информации в основной памяти IBM PC

- 87. Размещение информации в основной памяти IBM PC

- 88. Размещение информации в основной памяти IBM PC

- 89. Размещение информации в основной памяти IBM PC

- 90. Размещение информации в основной памяти IBM PC

- 91. Размещение информации в основной памяти IBM PC

- 92. Конструкциями машинного языка являются константы и команды.

- 93. Основные тенденции развития ЭВМ Повышение степени интеграции

- 94. Организация ЭВМ ИУ6 13 RISC – Reduced

- 95. Сравнение CISC, RISC и VLIW архитектур СК

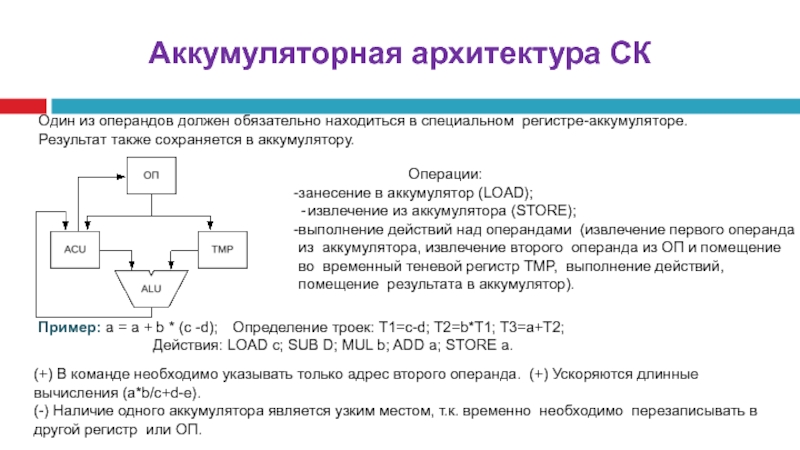

- 97. Один из операндов должен обязательно находиться

- 98. В состав процессора входит большое количество

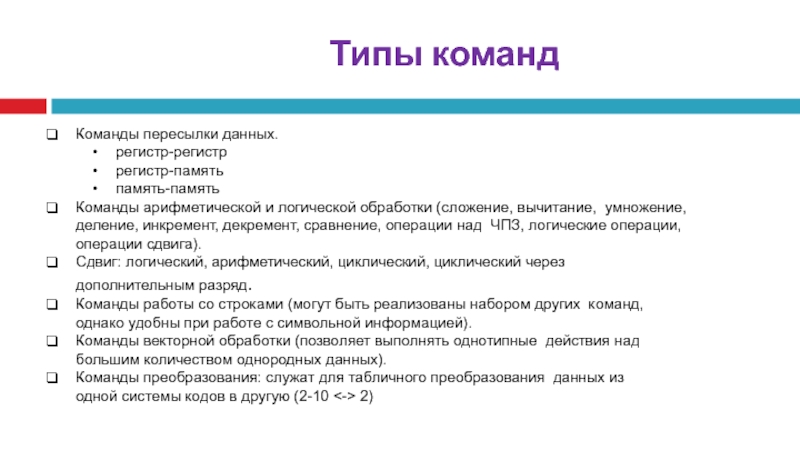

- 99. Типы команд Команды пересылки данных. регистр-регистр регистр-память

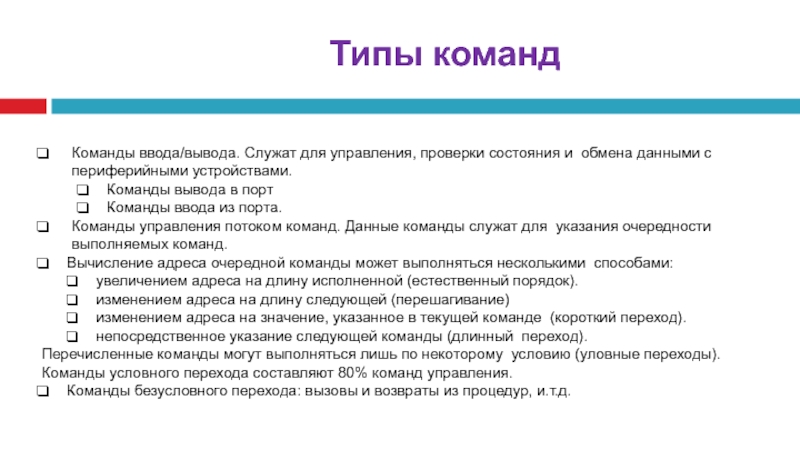

- 100. Команды ввода/вывода. Служат для управления, проверки состояния

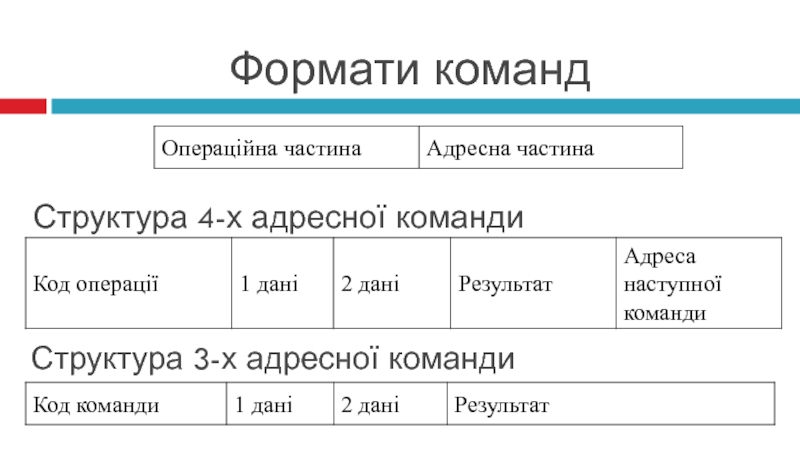

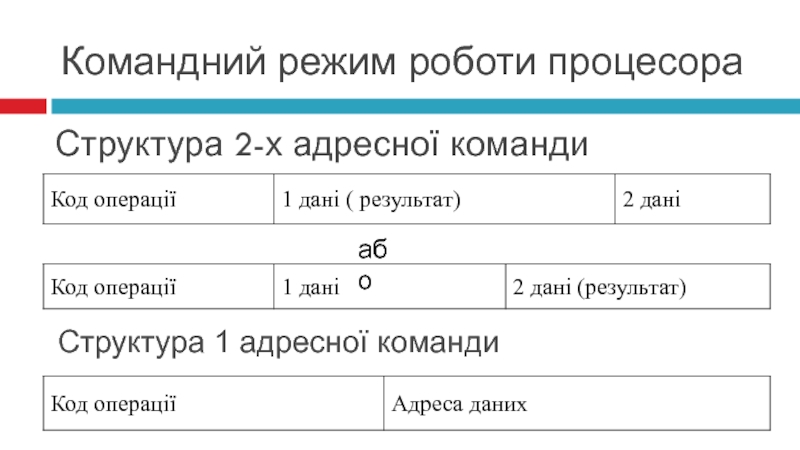

- 101. Формати команд Структура 4-х адресної команди Структура 3-х адресної команди

- 102. Структура 2-х адресної команди або Структура 1 адресної команди Командний режим роботи процесора

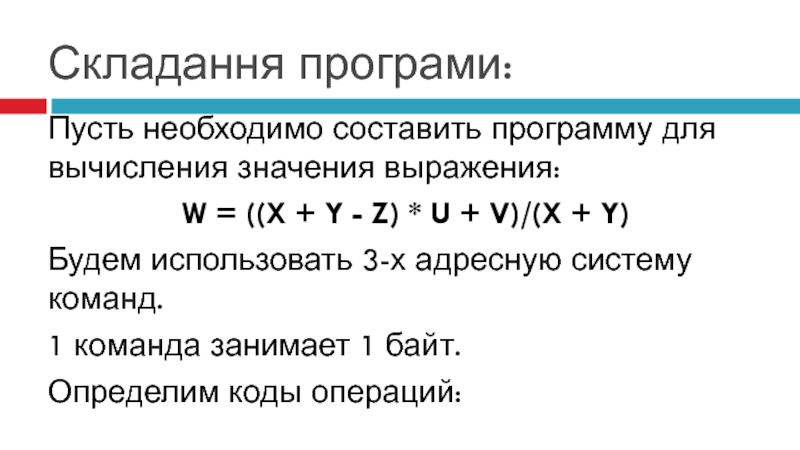

- 103. Складання програми: Пусть необходимо составить программу для

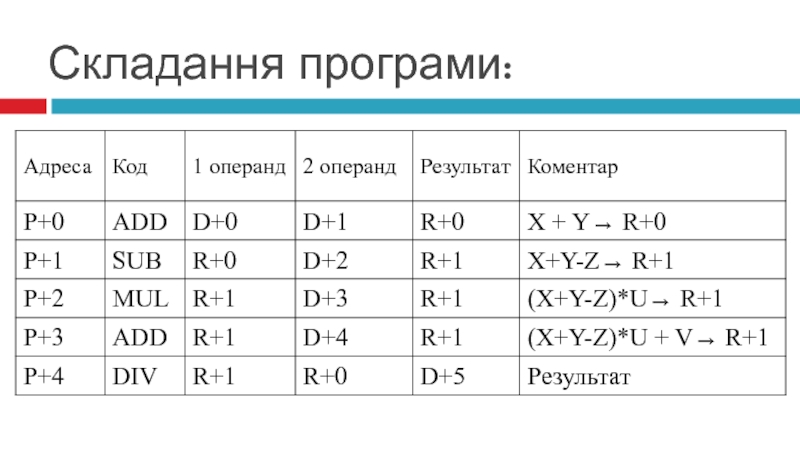

- 104. Складання програми: W = ((X + Y - Z) * U + V)/(X + Y)

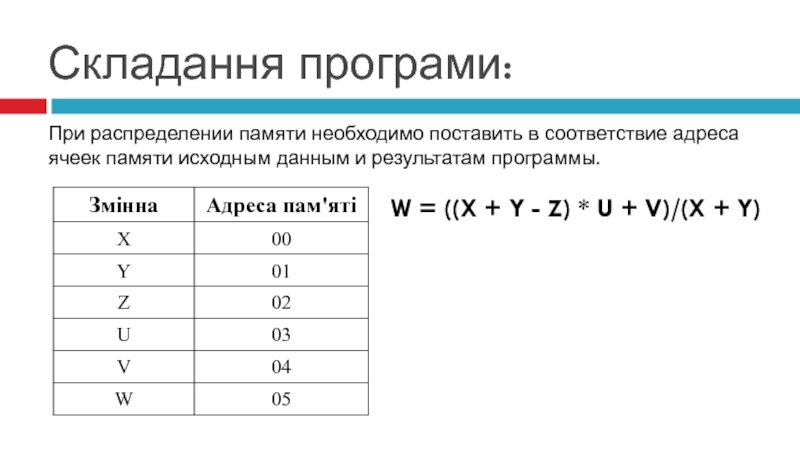

- 105. Складання програми: При распределении памяти необходимо поставить

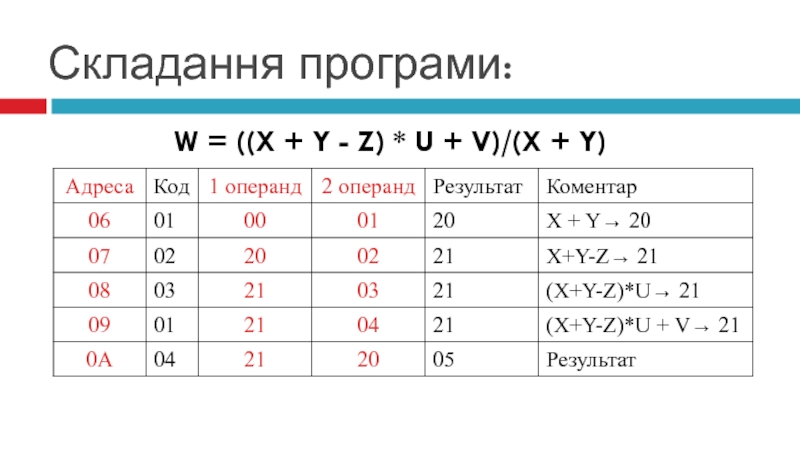

- 106. Складання програми: W = ((X + Y - Z) * U + V)/(X + Y)

- 107. Адреса сегменту даних: D D + 0

- 108. Складання програми:

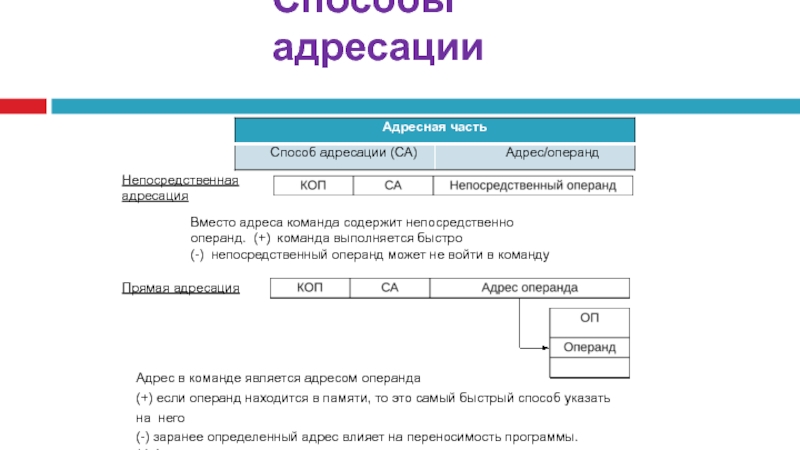

- 109. Способы адресации Непосредственная адресация Вместо адреса команда

- 110. Адрес в команде указывает на ячейку памяти,

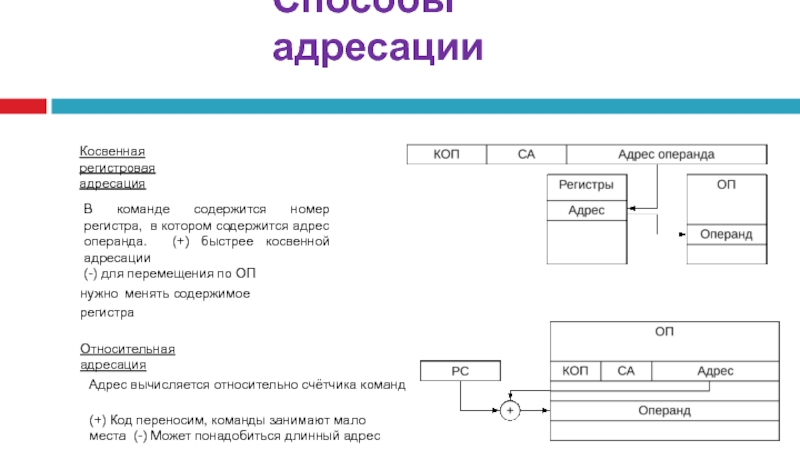

- 111. Косвенная регистровая адресация В команде

- 112. Базовая регистровая адресация Адрес в команде представляет

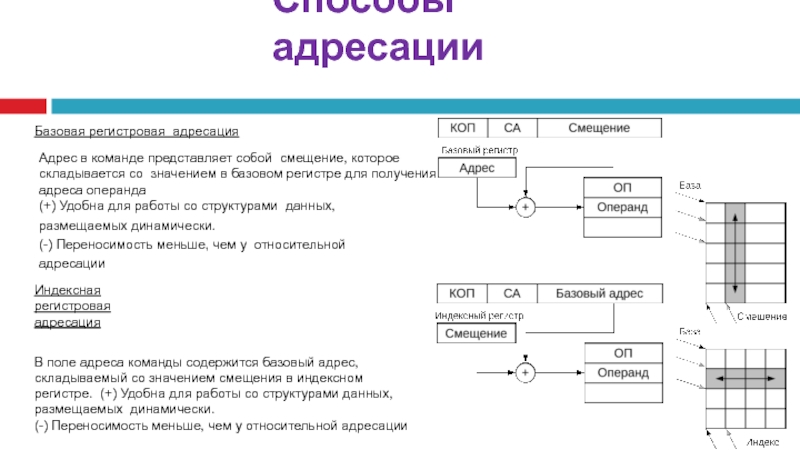

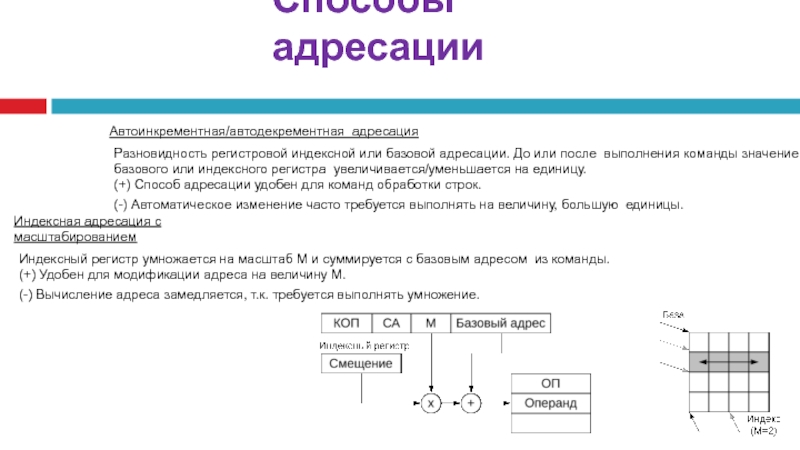

- 113. Автоинкрементная/автодекрементная адресация Разновидность регистровой индексной или базовой

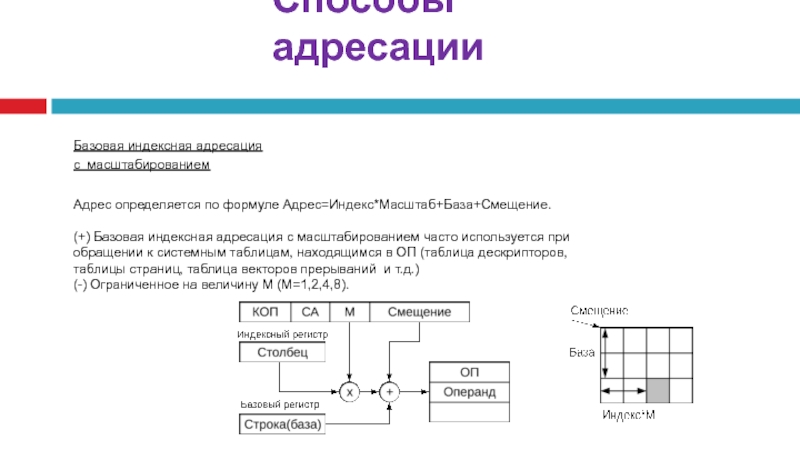

- 114. Базовая индексная адресация с масштабированием Адрес

- 115. Язык программирования, в котором вместо машинных кодов

- 116. Керування зовнішніми пристроями

- 117. Управление внешними устройствами Состав вычислительных машин: Процессор,

- 118. Управление внешними устройствами Принципы построения систем ввода-вывода

- 119. Управление внешними устройствами Технология обращения к автономным

- 120. Управление внешними устройствами Интерфейс ввода-вывода Интерфейс

- 121. Управление внешними устройствами В общем случае для

- 122. Управление внешними устройствами Стандартный интерфейс — это

- 123. Управление внешними устройствами Соединение между собой нескольких

- 124. Управление внешними устройствами Под машинно-ориентированными интерфейсами понимают

- 125. Управление внешними устройствами В зависимости от типа

- 126. Управление внешними устройствами По способу передачи адресов

- 127. Управление внешними устройствами Недостаток последовательного интерфейса –

- 128. Управление внешними устройствами Синхронный интерфейс – сигнал

- 129. Управление внешними устройствами При асинхронном способе о

- 130. Управление внешними устройствами В зависимости от используемых

- 131. Управление внешними устройствами В зависимости от степени

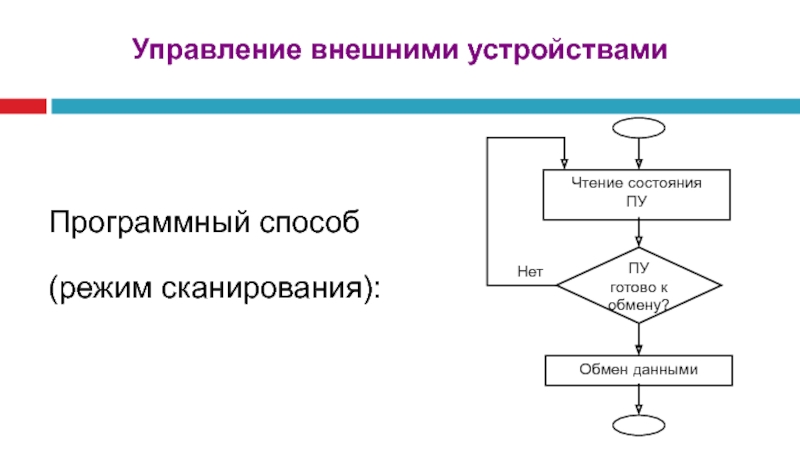

- 132. Управление внешними устройствами Программный способ (режим сканирования):

- 133. Управление внешними устройствами Режим сканирования упрощает

- 134. Управление внешними устройствами В асинхронном режиме центральный

- 135. Управление внешними устройствами Организация прерываний требует: опознания

- 136. Быстродействие процессора Быстродействие процессора, оперативной памяти и

- 137. Частота процессора определяется тем количеством бит, которые

- 138. Увеличение быстродействия процессора Увеличение производительности процессоров за

- 139. Аппаратный и программный разгон А) через BIOS Б) программным способом

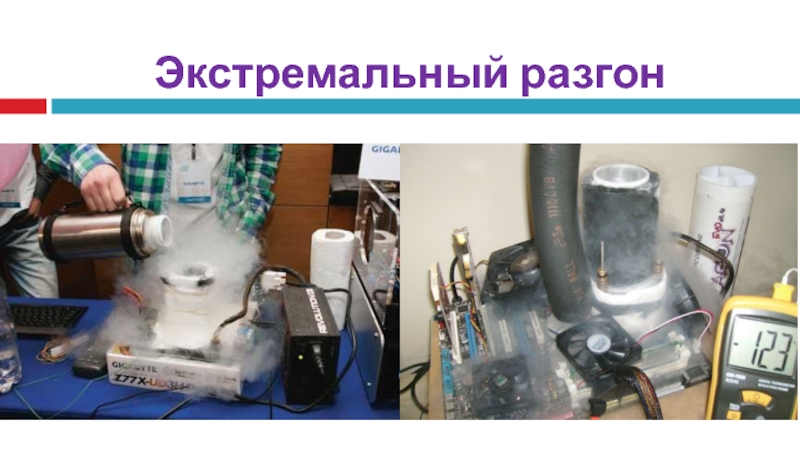

- 140. Экстремальный разгон

- 141. Шина памяти Обмен данными между северным мостом

- 142. Шина PCI Express Шина PCI Express связывает

- 143. Шина SATA Устройства внешней памяти (жесткие диски,

- 144. Шина USB Для подключения принтеров, сканеров, цифровых

Слайд 2Конвейерная обработка данных

Конвейерная организация процессора означает, что многие сложные действия разбиваются

Конвейеризация позволяет нескольким внутренним блокам МП работать одновременно, совмещая дешифрование команды, операции АЛУ, вычисление эффективного адреса и циклы шины нескольких команд.

Слайд 3Конвейерная обработка данных

В составе МП 80286 есть 4 конвейерных устройства:

BU (Bus

IU (Instruction Unit) – командный блок (дешифрация команд);

EU (Executive Unit) – исполнительный блок (выполнение команд);

AU (Address Unit) – адресный блок (вычисляет все адреса, формирует физический адрес).

Слайд 5Конвейерная обработка данных в ЦП 80486

В ЦП 80486 – пятиступенчатый конвейер

предвыборка команд (PF –Perfect);

декодирование команды (D1 – Instruction Decode);

формирование адреса (D2 – Address Generate);

выполнение команды в АЛУ и доступ к кэш-памяти (EX – Execute);

обратная запись (WB – Write Back).

Слайд 6Конвейерная обработка данных

Можно выделить два наиболее важных проявления конвейерной организации процессора

Первое проявление обычно называют «конвейером процессора» либо «конвейером непредсказанного перехода» (что более правильно). Длина этого конвейера влияет на производительность только в случае неправильного предсказания перехода в программе, когда происходит отмена работы, выполненной во всех этапах, начиная с этого перехода (сброс конвейера).

Слайд 7Конвейерная обработка данных

Длина конвейера функционального устройства, в свою очередь, определяет время

Такое старт-стопное время выполнения операции в функциональном устройстве называют латентностью.

Обращение к кэшам всех уровней и к оперативной памяти также производится конвейерным образом. Большинство простых операций целочисленной арифметики и логики имеют латентность, равную единице — то есть они выполняются в функциональных устройствах синхронно, без конвейеризации.

Слайд 8ЦП Pentium

КЭШ команд, 8К

Буфер предвыборки, 32 бита

АЛУ

(целочисл.)

АЛУ

(целочисл.)

Блок регистров

КЭШ данных, 8К

64 –

Схема предсказания

перехода

Конвейерный

блок

FPU

Делитель

Сложитель

Умножитель

U (5+3ступ.)

V (5 ступ.)

Слайд 9ЦП Pentium

Суперскалярная архитектура – это способ построения процессора с двумя или

U – конвейер основной (команды целочисленные и с плавающей точкой).

V – конвейер (команды, которые выполняются за один такт).

Спаривание – это процесс параллельного выполнения 2-х команд, независящих по данным или ресурсам.

Слайд 11Основные отличия ЦП Pentium

Увеличен размер страничной памяти. Механизм страничной организации памяти

64-разрядная ШД.

Конвейеризация машинного цикла.

Суперскалярная архитектура.

Контроль четности адреса и данных.

Раздельные блоки кэш-памяти для данных и кода.

Блок прогнозирования ветвлений.

Средства управления питанием (снижение мощности потребления).

Слайд 12Структура микропроцессора Pentium Pro

Кэш 2-го уровня, 256 Кбайт

(монтируется в один корпус

Интерфейс памяти

Внешняя

64-разрядная

синхронная

шина

Синхронная

64-разрядная

шина

Блок выборки

инструкций

Буфер команд,

8 Кбайт

За 1 такт выбираются 2 строки кэша

(строка – 32 байта)

Дешифратор команд

Дешифратор,

1 микро-

операция

за такт

Дешифратор,

1 микро-

операция

за такт

Дешифратор,

4 микро-

операции

Таблица переименования регистров

Блок интерфейса с памятью

Блок формирования адреса

Арифметическое устройство

с фиксированной точкой

Арифметическое устройство

с фиксированной точкой

Арифметическое устройство

с плавающей точкой

Блок формирования адреса

Пул инструкций

Блок удаления

Блок резервирования

Буфер

запросов

Буфер

данных

Блок

предсказания

переходов

(512 входов)

Блок

микропрог-

раммного

управления

Слайд 13ЦП Pentium Pro (P6)

Термин динамическое исполнение программы определил 3 способа обработки

Глубокое предсказание ветвлений (с вероятностью > 90% можно предсказать 10 - 15 ближайших переходов).

Анализ потока данных (на 20-30 шагов вперед посмотреть программу и определить зависимость команд по данным или ресурсам).

Опережающее (внеочередное) исполнение команд.

Слайд 14ЦП Pentium MMX

Основные черты MMX (MultiMediaeXtention) технологии:

SIMD архитектура (одна команда над

57 новых инструкций;

8 64-разрядных регистра MMX (ММ0-ММ7 – это мантиссы 8 регистров блока арифметики с плавающей точкой);

4 новых типа данных:

упакованный байт 64=8х8

упакованное слово 64=4х16

упакованное двойное слово 64=2х32

учетверенное слово 64=1х64

Слайд 15ЦП Pentium II

2 кэша I уровня (16 Кб).

Кэш II уровня (512

Двойная независимая шина (300-разрядная) -

2 независимых канала передачи данных:

для связи ЦП с кэш II уровня;

для связи ЦП с оперативной памятью.

Слайд 16ЦП Pentium III

Используется расширение SSE (Streaming SIMD Extensions) – потоковые SIMD

70 новых инструкций.

8 новых 128-разрядных регистров данных: XMM0, XMM1,…, XMM7. 32-битный регистр управления/состояния MXCSR используется для маскирования исключений, выбора режимов и определения состояния флагов.

Новый тип данных - упакованные числа с плавающей запятой одинарной точности. В одном 128-разрядном регистре 4 новых типа данных.

Все команды SSE доступны из любых режимов работы ЦП: реального, защищенного и виртуального.

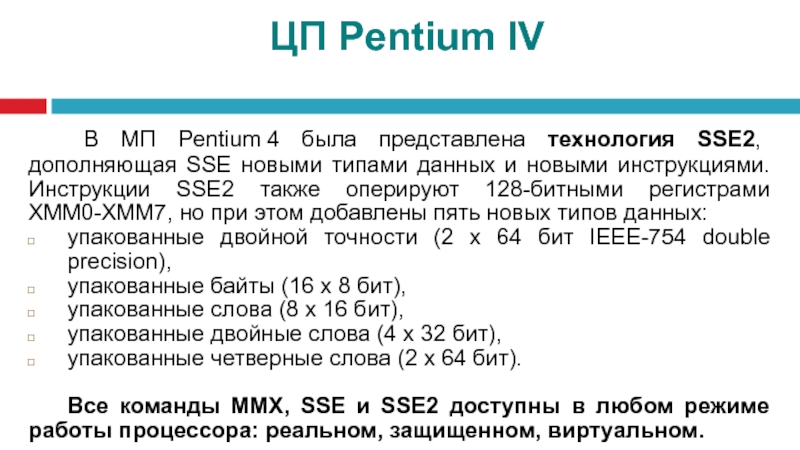

Слайд 17ЦП Pentium IV

В МП Pentium 4 была представлена технология SSE2, дополняющая

упакованные двойной точности (2 х 64 бит IEEE-754 double precision),

упакованные байты (16 x 8 бит),

упакованные слова (8 х 16 бит),

упакованные двойные слова (4 х 32 бит),

упакованные четверные слова (2 х 64 бит).

Все команды MMX, SSE и SSE2 доступны в любом режиме работы процессора: реальном, защищенном, виртуальном.

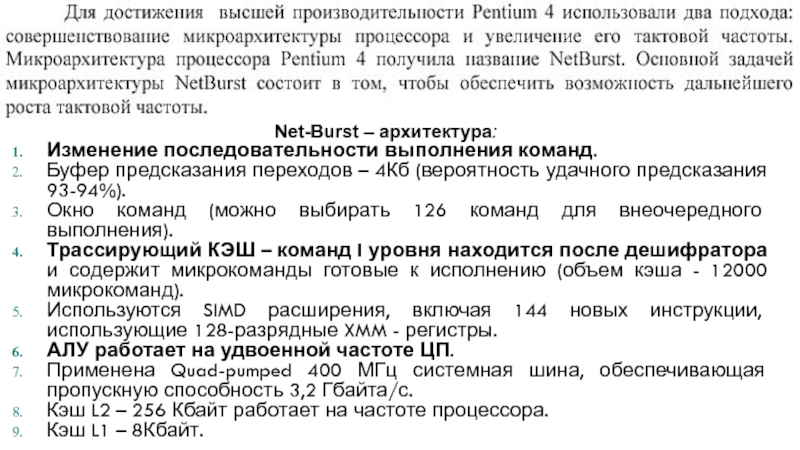

Слайд 18

Net-Burst – архитектура:

Изменение последовательности выполнения

Буфер предсказания переходов – 4Кб (вероятность удачного предсказания 93-94%).

Окно команд (можно выбирать 126 команд для внеочередного выполнения).

Трассирующий КЭШ – команд I уровня находится после дешифратора и содержит микрокоманды готовые к исполнению (объем кэша - 12000 микрокоманд).

Используются SIMD расширения, включая 144 новых инструкции, использующие 128-разрядные XMM - регистры.

АЛУ работает на удвоенной частоте ЦП.

Применена Quad-pumped 400 МГц системная шина, обеспечивающая пропускную способность 3,2 Гбайта/с.

Кэш L2 – 256 Кбайт работает на частоте процессора.

Кэш L1 – 8Кбайт.

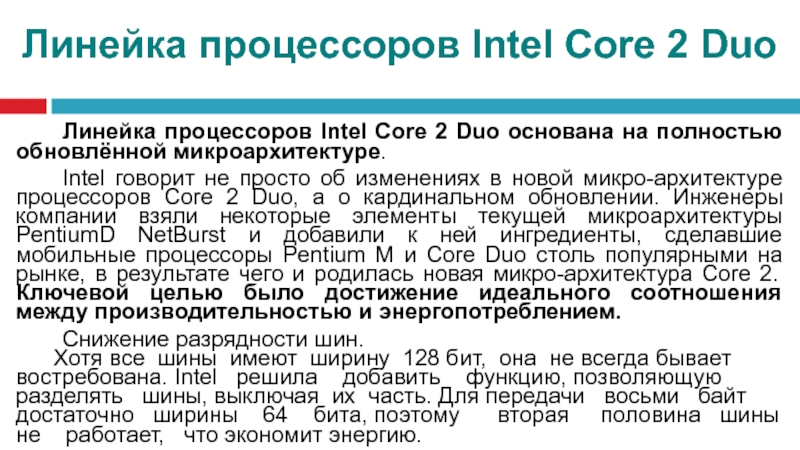

Слайд 19Линейка процессоров Intel Core 2 Duo

Линейка процессоров Intel Core 2

Intel говорит не просто об изменениях в новой микро-архитектуре процессоров Core 2 Duo, а о кардинальном обновлении. Инженеры компании взяли некоторые элементы текущей микроархитектуры PentiumD NetBurst и добавили к ней ингредиенты, сделавшие мобильные процессоры Pentium M и Core Duo столь популярными на рынке, в результате чего и родилась новая микро-архитектура Core 2. Ключевой целью было достижение идеального соотношения между производительностью и энергопотреблением.

Снижение разрядности шин. Хотя все шины имеют ширину 128 бит, она не всегда бывает востребована. Intel решила добавить функцию, позволяющую разделять шины, выключая их часть. Для передачи восьми байт достаточно ширины 64 бита, поэтому вторая половина шины не работает, что экономит энергию.

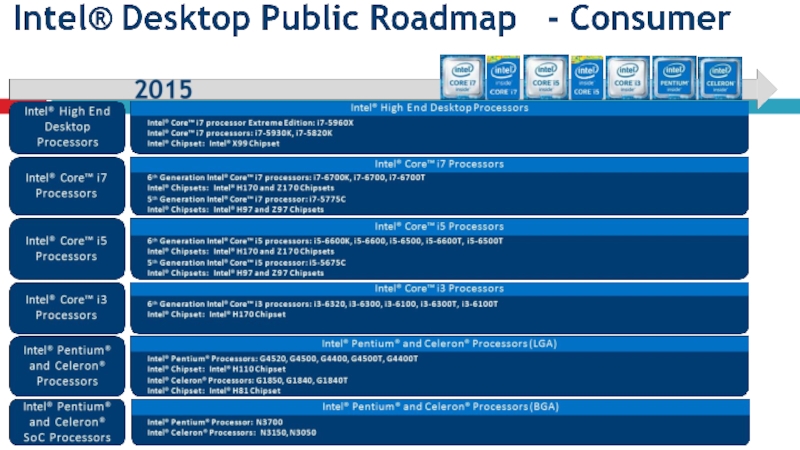

Слайд 20Процессоры Intel Core i7

Intel выпустила процессоры для десктопов Core i7 архитектуры

"Экстремальная" модель отличается повышенной скоростью обмена данными между процессорными ядрами (6.4 GT/sec против 4.8 GT/sec в других двух моделях). В остальном архитектура одинакова: производимые по 45-нм техпроцессу Core i7 оснащены 8 MB кэш-памяти третьего уровня, поддерживают оперативную память DDR3-1066, а энергопотребление при пиковой загрузке составляет 130 Вт.

Слайд 24Процессоры компании AMD

Развитие современных микроархитектур в компании AMD началось с создания

Следующий процессор компании Athlon 64 / Opteron (K8), увидевший свет в 2003 г., мало отличается от своего предшественника K7 по микроархитектуре. При его создании основной упор был сделан на две ключевые технологии: 64-битный режим целочисленной и адресной арифметики AMD64 (x86-64), и интегрированный контроллер оперативной памяти, встроенный в процессорный чип.

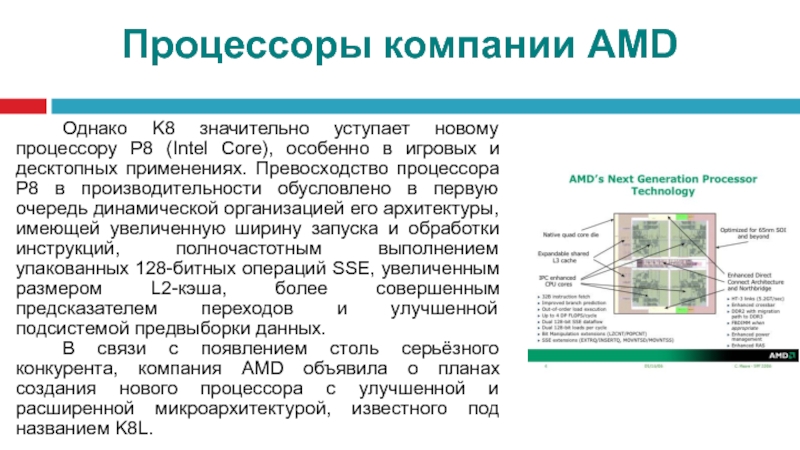

Слайд 25Однако K8 значительно уступает новому процессору P8 (Intel Core), особенно в

В связи с появлением столь серьёзного конкурента, компания AMD объявила о планах создания нового процессора с улучшенной и расширенной микроархитектурой, известного под названием K8L.

Процессоры компании AMD

Слайд 26Многоядерный процессор -

центральный процессор, содержащий два и более вычислительных

Ядром процессора - это система исполнительных устройств (набор арифметико-логических устройств), предназначенных для обработки данных.

Слайд 27Кэш- сверхоперативная память

В многоядерных процессорах кэш первого уровня у каждого ядра

разделяемый — кэш расположен на одном с обеими ядрами кристалле и доступен каждому из них в полном объёме (процессоры семейств Intel Core).

индивидуальный — отдельные кэш равного объёма, интегрированные в каждое из ядер. Обмен данными из кэш L2 между ядрами осуществляется через контроллер памяти — интегрированный (Athlon 64 X2) или внешний (Pentium D).

Слайд 28Производительность.

В приложениях, оптимизированных под многопоточность, наблюдается прирост производительности на двухъядерном процессоре.

Старые приложения (не оптимизированные под многопоточность), либо приложения, которым многопоточность не нужна или невозможна не будут получать практически никакой выгоды от дополнительных ядер, и могут даже выполняться медленнее, чем на процессоре с меньшим количеством ядер, но большей тактовой частотой.

Слайд 29Наращивание количества ядер.

На сегодняшний день основными производителями процессоров — Intel и

Слайд 30Одновременная многопоточность (Simultaneous multithreading)

Одновременная многопоточность

(Simultaneous multithreading – SMT, hardware multithreading) —

Потоки разделяют один суперскалярный конвейер процессора

(ALU, FPU, Load/Store)

SMT позволяет повысить эффективность использования модулей суперскалярного процессора (ALU, FPU, Load/Store) за счет наличия большего количества инструкций из разных потоков выполнения (ниже вероятность зависимости по данным)

Superscalar pipeline

Thread 1

Thread 2

Разделение ресурсов ALU, FPU, Load/Store

Примеры реализации:

❑ IBM ACS-360 (1968 г.), DEC Alpha 21464 (1999 г., 4-way SMT)

Intel Pentium 4 (2002 г., Intel Hyper-Threading, 2-way SMT)

❑Intel Xeon Phi (4-way SMT), Fujitsu Sparc64 VI (2-way SMT), IBM POWER8 (8-way SMT)

Слайд 31Intel Hyper-Threading Technology

Логический процессор

Architectural State

Backend Вычислительное ядро (Execution Engine)

Кеш-память

(Cache)

Frontend

(Fetch, Decode)

ILP

Chip

Логический процессор

Architectural

Architectural state + Interrupt controller (LAPIC) = Logical processor

2 потока разделяют суперскалярный

конвейер

Ускорение (Speedup) ~ 30 %

Architectural state:

Регистры общего назначения

(RAX, RBX, RCX, …)

Сегментные регистры (CS, DS, …),

Управляющие регистры (RFLAGS, RIP, GDTR)

X87 FPU-регистры,

MMX/XMM/YMM-регистры

MSR-регистры, Time stamp counter

Слайд 32Проблемы многоядерности.

Многоядерные и Hyper-Threading процессоры не только увеличивают производительность, но и

Основной "удар" различий одно- и многопроцессорных машин операционная система и BIOS берут на себя.

Прикладное приложение или драйвер устройства, спроектированный для однопроцессорной системы, не требует никакой адаптации для переноса на многопроцессорную систему, если, конечно, он спроектирован правильно. Многие типы ошибок (и, в особенности, ошибки синхронизации) могут годами не проявляться в однопроцессорных конфигурациях, но заваливают многопроцессорную машину каждые десять минут, а то и чаще.

Слайд 33Многопроцессорные системы создают много проблем и далеко не все из них

Проблемы многоядерности.

Слайд 35Векторные процессоры

Векторный процессор (Vector processor) – процессор поддерживающий

на уровне системы команд

Векторные вычислительные системы

CDC STAR-100 (1972 г., векторы до 65535 элементов)

Cray Research Inc.: Cray-1 (векторные регистры), Cray-2, Cray X-MP, Cray Y-MP

X1

X2

…

XN

Source 1

Y1

Y2

…

YN

Source 2

Destination

+

+

+

Сложение двух векторов

Слайд 36Векторные процессоры

▪ Векторный процессор (Vector processor) – процессор поддерживающий

на уровне системы команд

▪ Векторные вычислительные системы

o CDC STAR-100 (1972 г., векторы до 65535 элементов)

o Cray Research Inc.: Cray-1 (векторные регистры), Cray-2, Cray X-MP, Cray Y-MP

X1

X2

…

XN

Source 1

Y1

Y2

…

YN

Source 2

Destination

+

+

+

Сложение двух векторов

Максимальное ускорение (Speedup)

линейно зависит от числа элементов в векторном регистре

(использование векторных инструкций может привести к сокращению количества команд в программе, а это может обеспечить более эффективное использование кеш-памяти)

Слайд 38Многопроцессорные SMP-системы (Symmetric multiprocessing)

CPU 1

Cache

CPU 2

Cache

CPU N

Cache

I/O

Bus

Arbiter

System bus

Shared memory (RAM)

Процессоры SMP-системы

Системная шина (System bus) – это узкое место, ограничивающее масштабируемость вычислительного узла

Слайд 40Многопроцессорные NUMA-системы (AMD)

NUMA (Non-Uniform Memory Architecture) – это архитектура вычислительной системы

с

Процессоры сгруппированы в NUMA-узлы со своей локальной памятью

Доступ к локальной памяти NUMA-узла занимает меньше времени по сравнению с временем доступом к памяти удаленных процессоров

4-х процессорная NUMA-система

Каждый процессор имеет интегрированный контроллер и несколько банков памяти

Процессоры соединены шиной

Hyper-Transport

(системы на базе процессоров AMD)

Доступ к удаленной памяти занимает больше времени

(для Hyper-Transport ~ на 30%, 2006 г.)

Local access (fast)

Remote access (slow)

Слайд 41Многопроцессорные NUMA-системы (Intel)

4-х процессорная NUMA-система

Каждый процессор имеет интегрированный контроллер и несколько

Процессоры соединены шиной

Intel QuickPath Interconnect (QPI)

– решения на базе процессоров Intel

Intel Nehalem based systems with QPI

2-way Xeon 5600 (Westmere) 6-core, 2 IOH

Memory

Memory

CPU 0

CPU 1

Слайд 42Политики управления памятью NUMA-системы

Политики управления памятью можно задавать в настройках BIOS/UEFI:

NUMA

Node Interleave – память циклически выделяется со всех NUMA-узлов (чередование), операционная система “видит” NUMA-систему как SMP-машину

Memory latency and bandwidth accessing local, remote memory for a PowerEdge R610 server (Dual Intel Xeon X5550 Nehalem, 6 x 4GB 1333 MHz RDIMMS)

Слайд 45

Intel Xeon Phi (Intel MIC): 64 cores Intel P54C (Pentium)

Pipeline: in-order,

Кольцевая шина (1024 бит, ring bus) для связи ядер и контроллера памяти GDDR5

Устанавливается в PCI Express слот

SMP-система 256 логических процессоров

Современные системы на базе многоядерных процессоров

Слайд 46Graphics Processing Unit (GPU) – графический процессор, специализированный многопроцессорный ускоритель с

Большая часть площади чипа занята элементарными ALU/FPU/Load/Store модулями

Устройство управления (Control unit) относительно простое по сравнению с CPU

NVIDIA GeForce GTX 780

(Kepler, 2304 cores, GDDR5 3 GB)

AMD Radeon HD 8970

(2048 cores, GDDR5 3 GB)

Современные системы на базе многоядерных процессоров

Слайд 47Sony Playstation 3 IBM Cell

(2-way SMT PowerPC core + 6 SPE)

Microsoft

(3 cores with 2-way SMT)

Tilera TILEPro64

(64 cores, VLIW, mesh)

Cisco Routers

MIPS

Multi-core processors

Современные системы на базе многоядерных процессоров

Слайд 49Функциональная и структурная организация ЭВМ

Принципы функционирования ЭВМ, т.е. коды, система команд,

Слайд 50Функциональная и структурная организация ЭВМ

Принципы функционирования ЭВМ могут быть реализованы:

аппаратными,

программно-аппаратными

программными средствами.

Слайд 51Функциональная и структурная организация ЭВМ

При аппаратной и программно-аппаратной реализации могут быть

При программной реализации могут быть применены различные виды программ.

Слайд 52Функциональная и структурная организация ЭВМ

ЭВМ представляет собой совокупность устройств, выполненных на

Комплект интегральных схем, из которых состоит ЭВМ, называется микропроцессорным комплектом.

Слайд 53Функциональная и структурная организация ЭВМ

В основной состав микропроцессорных комплектов входят:

системный

микропроцессор,

сопроцессоры,

контроллер прерываний,

контроллер прямого доступа к памяти,

контроллеры устройств ввода-вывода.

Слайд 54Функциональная и структурная организация ЭВМ

Все устройства ЭВМ делятся на

центральные и

Центральные устройства — полностью электронные.

Периферийные устройства могут быть либо электронными, либо электромеханическими с электронным управлением.

Слайд 55Функциональная и структурная организация ЭВМ

В состав центральных устройств ЭВМ входят:

центральный

основная память

ряд дополнительных узлов, выполняющих служебные функции:

контроллер прерываний,

таймер и контроллер прямого доступа к памяти (ПДП).

Слайд 56Функциональная и структурная организация ЭВМ

Периферийные устройства делятся на два вида:

внешние

НМД

НГМД

НМЛ

устройства ввода-вывода (УВВ):

клавиатура

дисплей

принтер

мышь

адаптер каналов связи (КС) и др.

Слайд 57Алгоритм работы ЭВМ

Загрузка выполняемой программы

Передача адреса 1 выполняемой команды в счетчик

Адрес из счетчика команд на шину адреса системной магистрали (СМ)

На шину управления – «Выборка из оперативной памяти (ОП)»

Содержимое соотв. ячейки ОП на шину данных

Одновременно на шину управления сигнал о выполнении выборки из ОП

Процессор считывает с шины данных и передает в регистр команд

В регистре команд – разделение на кодовую и адресную части

Код команды настраивает МП на выполнение заданной операции

Адрес следующей команды заносится в счетчик команд

Адресная часть команды выставляется на шину адреса СМ

Одновременно на шину управления – «Выборка из ОП»

Выбранная из ОП информация вводится в арифметическое устройство (АУ) и начинается ее выполнение в АУ.

Результат на шину данных, на шину адреса – адрес ОП, на шину управления – «Запись в ОП»

Слайд 58Алгоритм работы ЭВМ

Процесс передачи команды другому устройству предусматривает следующие действия:

ЦП выставляет

по шинам управления передается сигнал “Поиск устройства”;

все устройства, подключенные к системной магистрали, получив этот сигнал, читают номер устройства с шины адреса и сравнивают его со своим номером. Устройства, для которых эти номера не совпадают, на эту команду не реагируют. Устройство с совпавшим номером, вырабатывает сигнал отклика по шине управления;

ЦП, получив сигнал отклика, в простейшем случае выставляет имеющуюся у него команду на шину данных и сопровождает ее по шине управления сигналом “Передаю команду”;

получив сигнал о приеме команды, ЦП переходит к выполнению очередной своей команды, выставляя на шину адреса содержимое счетчика команд.

Слайд 60VIII. Организация памяти ЭВМ

Памятью ЭВМ называется совокупность устройств, служащих для запоминания,

Характеристики памяти ЭВМ:

-Назначение.

-Информационная емкость.

-Информационная емкость читаемого слова.

-Способ доступа.

-Быстродействие.

-Физический способ хранения информации.

Центральные устройства ЭВМ. Память

Слайд 61Адресные ЗУ:

Постоянные ЗУ, ПЗУ (ROM)

ЗУ c произвольным доступом (RAM)

Ассоциативные ЗУ:

Полностью ассоциативные ЗУ

Ассоциативные ЗУ с прямым размещением

Наборно-ассоциативные ЗУ

Последовательные ЗУ:

FIFO

LIFO

Файловые

Циклические

Центральные устройства ЭВМ. Классификация ЗУ

Слайд 63Основная память включает два типа устройств:

оперативное запоминающее устройство

(ОЗУ или RAM -

постоянное запоминающее устройство (ПЗУ или ROM - Read Only Memory)

Центральные устройства ЭВМ. Память

Слайд 64

ОЗУ предназначено для хранения переменной информации и допускает изменение своего содержимого

Центральные устройства ЭВМ. Память

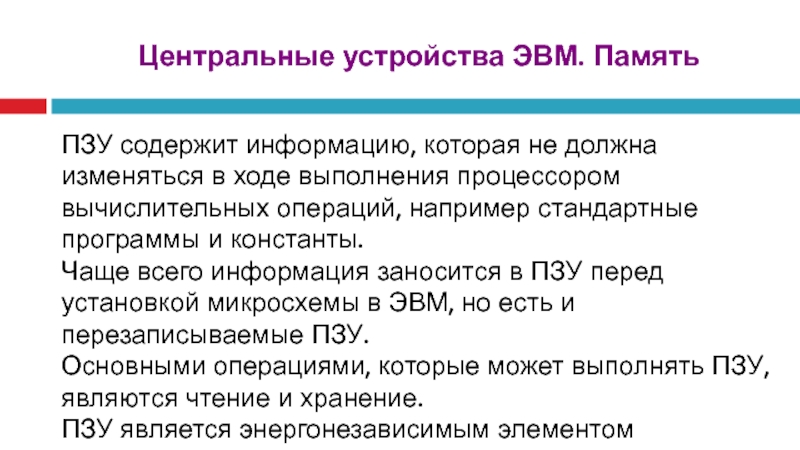

Слайд 65ПЗУ содержит информацию, которая не должна изменяться в ходе выполнения процессором

Чаще всего информация заносится в ПЗУ перед установкой микросхемы в ЭВМ, но есть и перезаписываемые ПЗУ.

Основными операциями, которые может выполнять ПЗУ, являются чтение и хранение.

ПЗУ является энергонезависимым элементом

Центральные устройства ЭВМ. Память

Слайд 70Адресные ЗУ

Постоянные ЗУ, ПЗУ (ROM)

Динамические ЗУПД (DRAM)

Статические ЗУПД (SRAM)

ЗУ c произвольным доступом

Слайд 71Постоянные и перепрограммируемые ЗУ

Преимущества ROM по сравнению RAM:

- Аппаратная простота.

Высокая плотность

Энергонезависимость.

Большое быстродействие.

Слайд 74Модели оперативной памяти.

Сегментированная модель. Программе выделяются непрерывные области памяти (сегменты) -

Страничная модель. ОЗУ рассматривается как совокупность блоков фиксированного размера (4 Кбайт). Основное применение этой модели связано с организацией виртуальной памяти, что позволяет ОС использовать для работы программ пространство памяти большее, чем объем физической памяти.

Слайд 75 Особенности использования и реализации моделей памяти зависят от режима работы

Режим реальных адресов.

Защищенный режим.

Режим виртуального 8086.

Режим системного управления.

Модели оперативной памяти.

Слайд 76Сегментация - это механизм адресации, обеспечивающий существование нескольких независимых адресных пространств

В основе механизма сегментации лежит понятие сегмента, который представляет собой независимый, поддерживаемый на аппаратном уровне блок памяти.

Сегментация памяти

Слайд 77- Адрес начала сегмента хранится в соответствующем сегментном регистре.

- Внутри сегмента

Сегментация памяти.

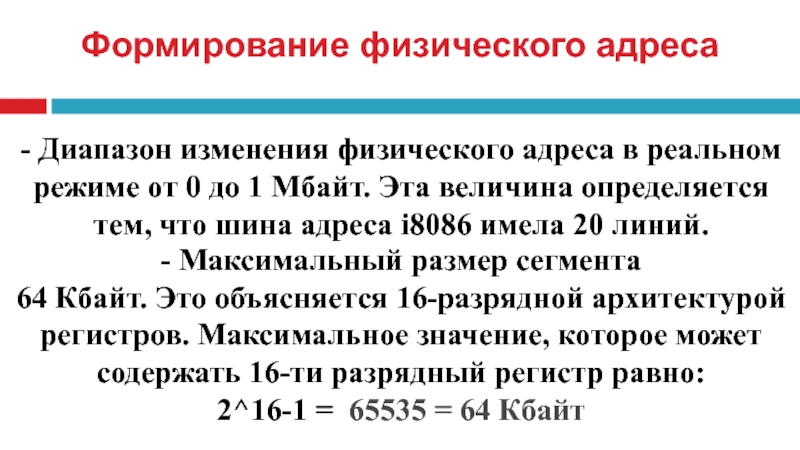

Слайд 78Формирование физического адреса

- Диапазон изменения физического адреса в реальном режиме от

- Максимальный размер сегмента

64 Кбайт. Это объясняется 16-разрядной архитектурой регистров. Максимальное значение, которое может содержать 16-ти разрядный регистр равно:

2^16-1 = 65535 = 64 Кбайт

Слайд 79В сегментном регистре содержаться только старшие 16 бит физического адреса начала

Недостающие младшие 4 бита 20-битного адреса получаются сдвигом в сегментном регистре влево на 4 разряда.

Эта операция сдвига выполняется аппаратно и для программного обеспечения абсолютно прозрачна.

Формирование физического адреса.

Слайд 80Получившееся 20-битное значение и является настоящим физическим адресом, соответствующим началу сегмента.

К

Формирование физического адреса.

Слайд 81Схема страничного преобразования

V - признак присутствия страницы в физ. памяти. R

M - признак модификации. A - признак права доступа.

Слайд 82Сегментная организация

Программа отображается в память блоками различного размера – сегментами. Преобразование

Слайд 83Сегментно-страничная организация памяти

Программа отображается в память блоками различного размера – сегментами,

Преобразование логического адреса в физический осуществляется с помощью таблицы сегментов и таблицы страниц сегмента.

Слайд 84Адрес ячейки памяти для удобства принято записывать в шестнадцатиричной системе счисления.

Каждой

0 - 0000

1 - 0001

2 - 0010

3 - 0011

4 - 0100

5 - 0101

6 - 0110

7 - 0111

8 - 1000

9 - 1001

A - 1010

B - 1011

C - 1100

D - 1101

E - 1110

F - 1111

Формирование физического адреса

Слайд 85Пример формирования физического адреса:

- Пусть содержимое сегментного регистра равно: 1А62h

После сдвига

Смещение пусть равно: 01B5h

К физическому адресу начала сегмента прибавляется смещение:

1А620h

+ 01B5h

------------

1A7D5h

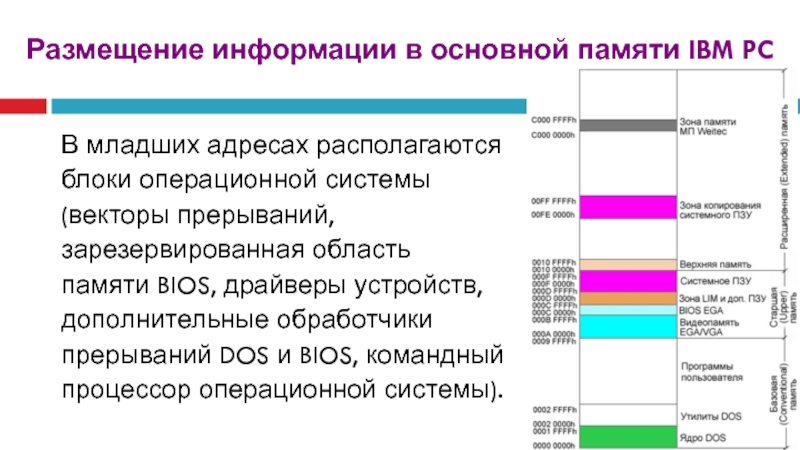

Слайд 86Размещение информации в основной памяти IBM PC

В младших адресах располагаются блоки

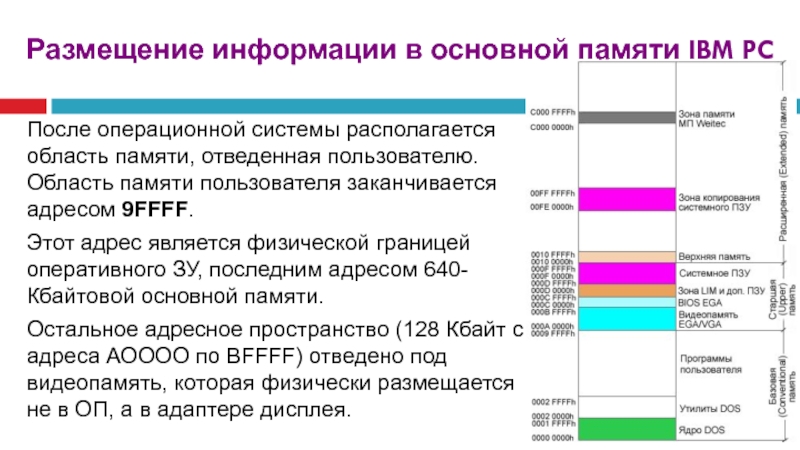

Слайд 87Размещение информации в основной памяти IBM PC

После операционной системы располагается область

Этот адрес является физической границей оперативного ЗУ, последним адресом 640-Кбайтовой основной памяти.

Остальное адресное пространство (128 Кбайт с адреса АОООО по BFFFF) отведено под видеопамять, которая физически размещается не в ОП, а в адаптере дисплея.

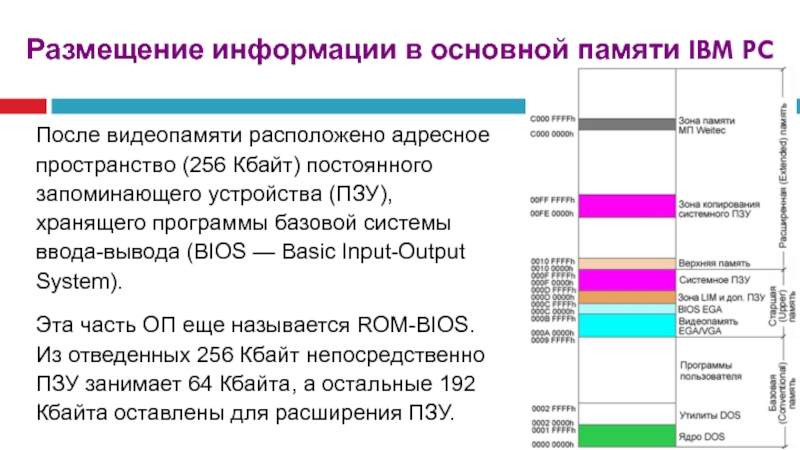

Слайд 88Размещение информации в основной памяти IBM PC

После видеопамяти расположено адресное пространство

Эта часть ОП еще называется ROM-BIOS. Из отведенных 256 Кбайт непосредственно ПЗУ занимает 64 Кбайта, а остальные 192 Кбайта оставлены для расширения ПЗУ.

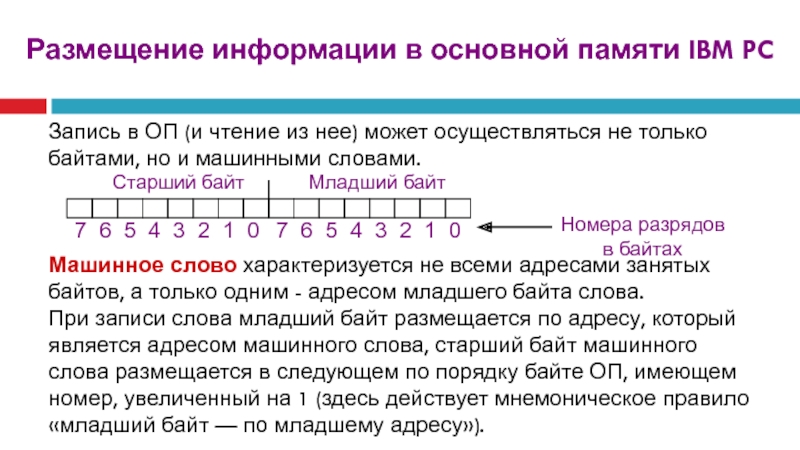

Слайд 89Размещение информации в основной памяти IBM PC

Запись в ОП (и чтение

Машинное слово характеризуется не всеми адресами занятых байтов, а только одним - адресом младшего байта слова.

При записи слова младший байт размещается по адресу, который является адресом машинного слова, старший байт машинного слова размещается в следующем по порядку байте ОП, имеющем номер, увеличенный на 1 (здесь действует мнемоническое правило «младший байт — по младшему адресу»).

Номера разрядов

в байтах

Слайд 90Размещение информации в основной памяти IBM PC

При чтении из ОП двух

Старший байт

Младший байт

Номера разрядов

в байтах

Слайд 91Размещение информации в основной памяти IBM PC

При записи отдельных байтов каждый

При записи же в ОП единиц информации; имеющих в своем составе больше одного байта, адресом информационной единицы является адрес самого младшего байта, запись в ОП ведется побайтно, начиная с самого младшего байта, каждый последующий байт располагается в ячейке, адрес которой на 1 больше предыдущего.

Иными словами, запись машинного или двойного слова производится справа налево, тогда как при чтении считанные байты обычно располагаются слева направо — происходят «вращение» байтов, перестановка их местами, что необходимо учитывать при работе с ОП на физическом уровне.

Слайд 92Конструкциями машинного языка являются константы и команды. Команды содержат код команды

Программирование процессора

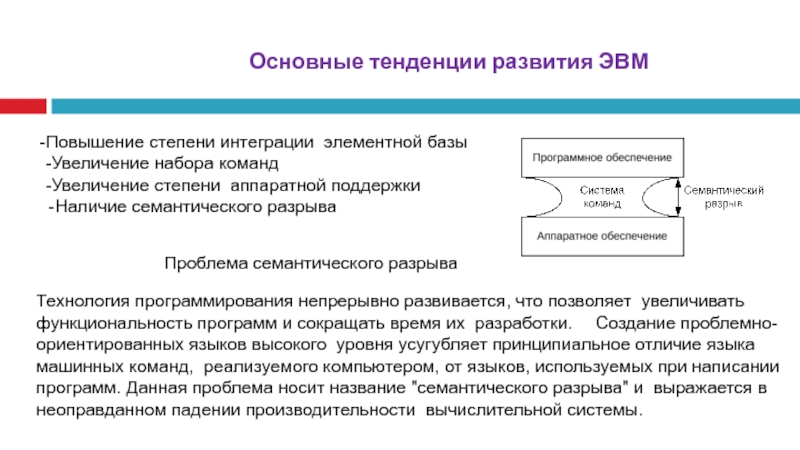

Слайд 93Основные тенденции развития ЭВМ

Повышение степени интеграции элементной базы

-Увеличение набора команд

-Увеличение степени

Наличие семантического разрыва

Проблема семантического разрыва

Технология программирования непрерывно развивается, что позволяет увеличивать функциональность программ и сокращать время их разработки. Создание проблемно-ориентированных языков высокого уровня усугубляет принципиальное отличие языка машинных команд, реализуемого компьютером, от языков, используемых при написании программ. Данная проблема носит название "семантического разрыва" и выражается в неоправданном падении производительности вычислительной системы.

Слайд 94Организация ЭВМ ИУ6 13

RISC – Reduced Instruction Set Computer;

CISC – Complex

VLIW – Very Long Instruction Word;

ROSC - Removed Operand Set Computer

Архитектура системы команд

В команде указывается, какую операцию выполнять (КОП), над какими операндами выполнять операцию, а также куда поместить операнд.

Слайд 96

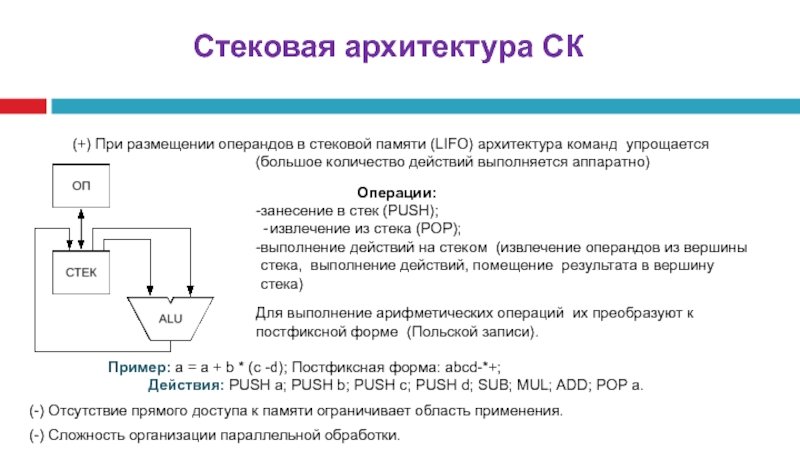

(+) При размещении операндов в стековой памяти (LIFO) архитектура команд упрощается (большое количество действий выполняется аппаратно)

Операции:

занесение в стек (PUSH);

извлечение из стека (POP);

выполнение действий на стеком (извлечение операндов из вершины стека, выполнение действий, помещение результата в вершину стека)

Для выполнение арифметических операций их преобразуют к постфиксной форме (Польской записи).

Пример: a = a + b * (c -d); Постфиксная форма: abcd-*+;

Действия: PUSH a; PUSH b; PUSH c; PUSH d; SUB; MUL; ADD; POP a.

(-) Отсутствие прямого доступа к памяти ограничивает область применения.

(-) Сложность организации параллельной обработки.

Стековая архитектура СК

Слайд 97

Один из операндов должен обязательно находиться в специальном регистре-аккумуляторе. Результат также

Операции:

занесение в аккумулятор (LOAD);

извлечение из аккумулятора (STORE);

выполнение действий над операндами (извлечение первого операнда из аккумулятора, извлечение второго операнда из ОП и помещение во временный теневой регистр TMP, выполнение действий, помещение результата в аккумулятор).

Пример: a = a + b * (c -d); Определение троек: T1=c-d; T2=b*T1; T3=a+T2;

Действия: LOAD c; SUB D; MUL b; ADD a; STORE a.

(+) В команде необходимо указывать только адрес второго операнда. (+) Ускоряются длинные вычисления (a*b/c+d-e).

(-) Наличие одного аккумулятора является узким местом, т.к. временно необходимо перезаписывать в другой регистр или ОП.

Аккумуляторная архитектура СК

Слайд 98

В состав процессора входит большое количество однотипных регистров. В команде необходимо

Для данной архитектуры возможны варианты размещения операндов: оба операнда в памяти; один операнд в памяти и один в РОН; оба операнда в РОН.

Для уменьшения размерности команд и для упрощения декодирования накладывают ограничения на размещение операндов.

Регистровая архитектура СК

Слайд 99Типы команд

Команды пересылки данных.

регистр-регистр

регистр-память

память-память

Команды арифметической и логической обработки (сложение, вычитание, умножение,

Сдвиг: логический, арифметический, циклический, циклический через дополнительным разряд.

Команды работы со строками (могут быть реализованы набором других команд, однако удобны при работе с символьной информацией).

Команды векторной обработки (позволяет выполнять однотипные действия над большим количеством однородных данных).

Команды преобразования: служат для табличного преобразования данных из одной системы кодов в другую (2-10 <-> 2)

Слайд 100Команды ввода/вывода. Служат для управления, проверки состояния и обмена данными с

Команды вывода в порт

Команды ввода из порта.

Команды управления потоком команд. Данные команды служат для указания очередности выполняемых команд.

Вычисление адреса очередной команды может выполняться несколькими способами:

увеличением адреса на длину исполненной (естественный порядок).

изменением адреса на длину следующей (перешагивание)

изменением адреса на значение, указанное в текущей команде (короткий переход).

непосредственное указание следующей команды (длинный переход).

Перечисленные команды могут выполняться лишь по некоторому условию (уловные переходы).

Команды условного перехода составляют 80% команд управления.

Команды безусловного перехода: вызовы и возвраты из процедур, и.т.д.

Типы команд

Слайд 102Структура 2-х адресної команди

або

Структура 1 адресної команди

Командний режим роботи процесора

Слайд 103Складання програми:

Пусть необходимо составить программу для вычисления значения выражения:

W = ((X

Будем использовать 3-х адресную систему команд.

1 команда занимает 1 байт.

Определим коды операций:

Слайд 105Складання програми:

При распределении памяти необходимо поставить в соответствие адреса ячеек памяти

W = ((X + Y - Z) * U + V)/(X + Y)

Слайд 107Адреса сегменту даних: D

D + 0 : X

D + 1 :

D + 2 : Z

D + 3 : U

D + 4 : V

D + 5 : W

Адреса сегменту програми: P

Адреса сегменту результату: R

Складання програми:

Слайд 109Способы адресации

Непосредственная адресация

Вместо адреса команда содержит непосредственно операнд. (+) команда выполняется

(-) непосредственный операнд может не войти в команду

Прямая адресация

Адрес в команде является адресом операнда

(+) если операнд находится в памяти, то это самый быстрый способ указать на него

(-) заранее определенный адрес влияет на переносимость программы.

(-) Адрес занимает много места

Слайд 110Адрес в команде указывает на ячейку памяти, в которой находится адрес

(+) удобна для обработки структурных типов данных. (-) приходится осуществлять много обращений к ОП.

Неявная адресация

Операнд подразумевается (следует из КОП). (+) Команда занимает мало места

(-) только такие командах нельзя использовать для построение всей системы команд.

Регистровая адресация

Адрес в команде указывает не на ячейку ОП, а на регистр. (+) Быстрее прямой адресации

(-) Количество регистров ограничено

Косвенная адресация

Способы адресации

Слайд 111

Косвенная регистровая адресация

В команде содержится номер регистра, в котором содержится адрес

(-) для перемещения по ОП нужно менять содержимое регистра

Относительная адресация

Адрес вычисляется относительно счётчика команд

(+) Код переносим, команды занимают мало места (-) Может понадобиться длинный адрес

Способы адресации

Слайд 112Базовая регистровая адресация

Адрес в команде представляет собой смещение, которое складывается со

(+) Удобна для работы со структурами данных, размещаемых динамически.

(-) Переносимость меньше, чем у относительной адресации

Индексная регистровая адресация

В поле адреса команды содержится базовый адрес, складываемый со значением смещения в индексном регистре. (+) Удобна для работы со структурами данных, размещаемых динамически.

(-) Переносимость меньше, чем у относительной адресации

Способы адресации

Слайд 113Автоинкрементная/автодекрементная адресация

Разновидность регистровой индексной или базовой адресации. До или после выполнения

(+) Способ адресации удобен для команд обработки строк.

(-) Автоматическое изменение часто требуется выполнять на величину, большую единицы.

Индексная адресация с масштабированием

Индексный регистр умножается на масштаб M и суммируется с базовым адресом из команды.

(+) Удобен для модификации адреса на величину M.

(-) Вычисление адреса замедляется, т.к. требуется выполнять умножение.

Способы адресации

Слайд 114Базовая индексная адресация с масштабированием

Адрес определяется по формуле Адрес=Индекс*Масштаб+База+Смещение.

(+) Базовая индексная

(-) Ограниченное на величину M (M=1,2,4,8).

Способы адресации

Слайд 115Язык программирования, в котором вместо машинных кодов используются их символические обозначения,

Ассемблер - язык, для которого одна команда преобразуется в одну команду машинного языка. Исключением являются макросы, в этом случае одной макрокоманде может соответствовать более одной машинной команды.

Командний режим роботи процесора

Слайд 117Управление внешними устройствами

Состав вычислительных машин:

Процессор,

Основная память,

Периферийные устройства (ПУ):

внешние запоминающие устройства

устройства ввода-вывода (УВВ).

Передача информации с периферийного устройства в ЭВМ называется операцией ввода, а передача из ЭВМ в ПУ — операцией вывода.

Слайд 118Управление внешними устройствами

Принципы построения систем ввода-вывода ЭВМ:

возможность реализации машин с переменным

одновременная работа процессора над программой и выполнение периферийными устройствами процедур ввода-вывода;

стандартизация и унификация операций ввода-вывода;

автоматические распознавание и реакция ядра ЭВМ на многообразие ситуаций, возникающих в ПУ (готовность устройства, отсутствие носителя, различные нарушения нормальной работы и др.).

Слайд 119Управление внешними устройствами

Технология обращения к автономным внешним устройствам — интерфейс.

Унифицированная технология

Стандартизация интерфейсов ввода-вывода — возможности гибкого и оперативного изменения конфигураций вычислительных машин (количество и состав внешних устройств, расширять комплект ЭВМ за счет подключения новых устройств).

Концепция виртуальных устройств — совмещение различных типов ЭВМ, операционных систем.

Слайд 120Управление внешними устройствами

Интерфейс ввода-вывода

Интерфейс ввода-вывода характеризуется 4 функциями:

буферизация;

дешифрация адреса

дешифрация адреса команды;

синхронизация и управление.

Слайд 121Управление внешними устройствами

В общем случае для организации и проведения обмена данными

специальные управляющие сигналы и их последовательности;

устройства сопряжения;

линии связи;

программы, реализующие обмен.

Весь этот комплекс линий и шин, сигналов, электронных схем, алгоритмов и программ, предназначенный для осуществления обмена информацией, называется интерфейсом.

Слайд 122Управление внешними устройствами

Стандартный интерфейс — это совокупность унифицированных технических программных и

Слайд 123Управление внешними устройствами

Соединение между собой нескольких устройств осуществляется через шины интерфейса.

В

машинно-ориентированный

системный

приборный

Слайд 124Управление внешними устройствами

Под машинно-ориентированными интерфейсами понимают интерфейсы, которые решают задачу подключения

Системный интерфейс - сопряжение устройств (модулей), имеющих системное назначение и исполнение, т.е. основное назначение которых создание системы. Системный интерфейс не решает конкретную задачу ввода/вывода, а, прежде всего, стандартизует устройства для решения этой задачи.

Приборный интерфейс предназначен для соединения различных приборов, в т.ч. работающих автономно от ЭВМ.

Слайд 125Управление внешними устройствами

В зависимости от типа соединяемых устройств различаются:

внутренний интерфейс ЭВМ

интерфейс ввода-вывода — для сопряжения различных устройств с системным блоком (клавиатурой, принтером, сканером, мышью, дисплеем и др.);

интерфейсы межмашинного обмена (для обмена между разными машинами) — для сопряжения различных ЭВМ (например, при образовании вычислительных сетей);

интерфейсы «человек — машина» — для обмена информацией между человеком и ЭВМ.

Слайд 126Управление внешними устройствами

По способу передачи адресов и данных различают:

Интерфейс с совмещенным

Интерфейс с разделенными шинам адреса и данных

Интерфейс может быть внутриплатный, межплатный и межблочный.

По способу передачи информации различают:

последовательный и параллельный интерфейс

синхронный и асинхронный интерфейс

Слайд 127Управление внешними устройствами

Недостаток последовательного интерфейса – низкое быстродействие (устранение недостатка –

Недостаток параллельного интерфейса связан, с так называемым, "перекосом" информации из-за различного времени передачи по параллельным физическим линиям. (Наиболее простой способ устранения последнего недостатка - это стробирование передаваемых сигналов).

Слайд 128Управление внешними устройствами

Синхронный интерфейс – сигнал на физических линиях поддерживается в

Точка отсчета заданного времени осуществляется за счет подачи сигнала строба или синхронизации.

Синхронизация должна работать исходя из быстродействия самого медленного устройства, подключенного к интерфейсу.

Слайд 129Управление внешними устройствами

При асинхронном способе о каждой передаче должно быть сообщено

Прием последующей информации производится только после получения подтверждения о приеме предыдущей информации, получением так называемого сигнала-квитанции (Передача с квитированием).

Для асинхронного интерфейса время передачи информации равно сумме времени передачи управления сигнала по линиям запроса и ответа плюс время передачи самой информации.

Слайд 130Управление внешними устройствами

В зависимости от используемых при обмене программно-технических средств интерфейсы

Слайд 131Управление внешними устройствами

В зависимости от степени участия центрального процессора в обмене

режим сканирования (синхронный обмен) или программно-управляемая передача (программный способ) ;

асинхронный обмен или использование прерываний;

прямой доступ к памяти.

Слайд 133Управление внешними устройствами

Режим сканирования упрощает подготовку к обмену, но имеет ряд

процессор постоянно задействован и не может выполнять другую работу;

при большом быстродействии периферийного устройства процессор не успевает организовать обмен данными.

Слайд 134Управление внешними устройствами

В асинхронном режиме центральный процессор выполняет основную роль по

Обмен инициируется УВВ.

Процессор должен иметь спец. вход, периодически опрашиваемый.

Наличие сигнала на этом входе заставляет процессор отложить исполнение текущей программы и перейти в режим обслуживания прерываний (приоритет и запрет прерываний).

Слайд 135Управление внешними устройствами

Организация прерываний требует:

опознания (идентификации) устройства, запросившего прерывание.

сохранения состояния процессора,

переход на выполнение спец. программы в зависимости от поступившего прерывания с последующим возвратом.

восстановление состояния процессора до прерывания, т.е. восстановление содержимого активных регистров, в т.ч. управления, счетчика команд и т.д.

Прерывания могут быть реализованы как аппаратно, так и программно.

Слайд 136Быстродействие процессора

Быстродействие процессора, оперативной памяти и периферийных устройств существенно различается.

Быстродействие

Соответственно, скорость передачи данных (пропускная способность) соединяющих эти устройства шин также должна различаться.

пропускная способность шины =разрядность шины × частота шины.

Слайд 137Частота процессора определяется тем количеством бит, которые процессор может обработать одновременно

В

Например, в современных процессорах используется коэффициент умножения частоты 8.

Это означает, что процессор за один такт шины способен генерировать 8 своих внутренних тактов и, следовательно, частота процессора составляет при частоте шины в 400 МГц:

400 МГц • 8 = 3200 МГц = 3,2 ГГц.

Быстродействие процессора

Слайд 138Увеличение быстродействия процессора

Увеличение производительности процессоров за счет увеличения частоты имеет свой

Выделение процессором теплоты Q пропорционально потребляемой мощности Р, которая, в свою очередь, пропорциональна квадрату частоты v :

Q ~ Р ~ v2

Слайд 141Шина памяти

Обмен данными между северным мостом и оперативной памятью производится по

400 МГц • 4 = 1600 МГц,

Т. е. оперативная память получает данные с такой же частотой, что и процессор. Так как разрядность шины памяти равна разрядности процессора и составляет 64 бита, то пропускная способность шины памяти также равна:

64 бита • 1600 МГц = 102 400 Мбит/с = 12,5 Гбайт/с = 12 800 Мбайт/с

Слайд 142Шина PCI Express

Шина PCI Express связывает видеопамять с процессором и оперативной

Пропускная способность этой шины может достигать 32 Гбайт/с.

К видеоплате с помощью аналогового разъема VGA или цифрового разъема DVI подключается монитор или проектор.

Слайд 143Шина SATA

Устройства внешней памяти (жесткие диски, CD- и DVD-дисководы) подключаются к

Слайд 144Шина USB

Для подключения принтеров, сканеров, цифровых камер и других периферийных устройств

Эта шина обладает пропускной способностью до 60 Мбайт/с и обеспечивает подключение к компьютеру одновременно до 127 периферийных устройств