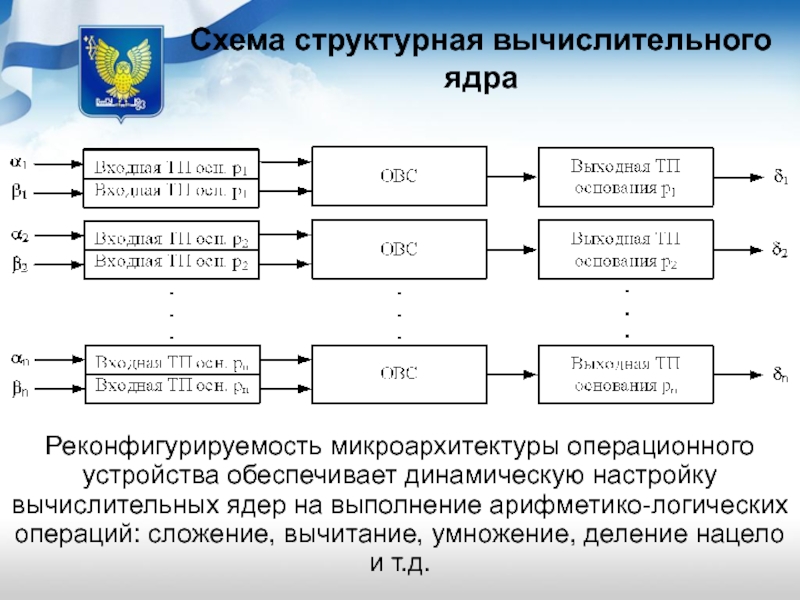

- Реконфигурируемость микроархитектуры операционной части процессора за счет динамической настройки вычислительных ядер на выполнение требуемого набора арифметико-логических операций: сложение, вычитание, умножение, деление и так далее;

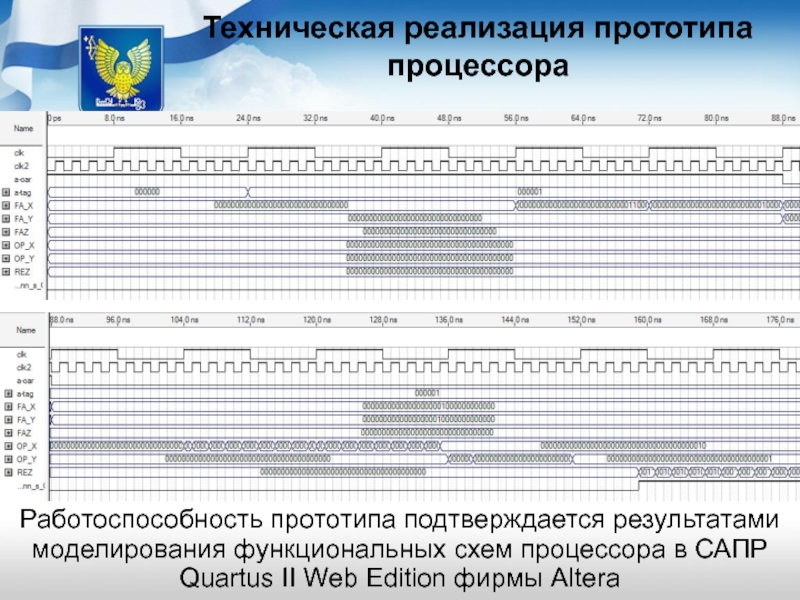

- все арифметические операции реализуются с использованием конвейерной техники вычислений;

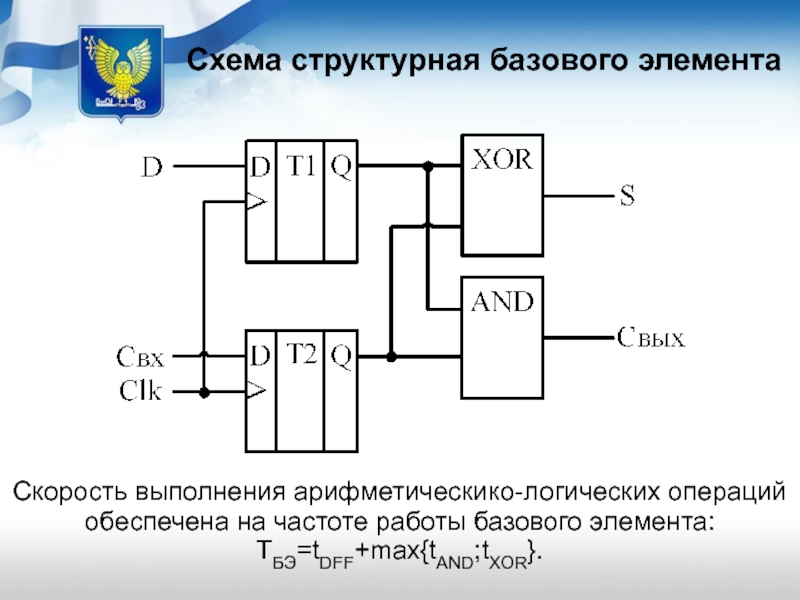

- скорость выполнения всех операций обеспечена на частоте базового элемента;

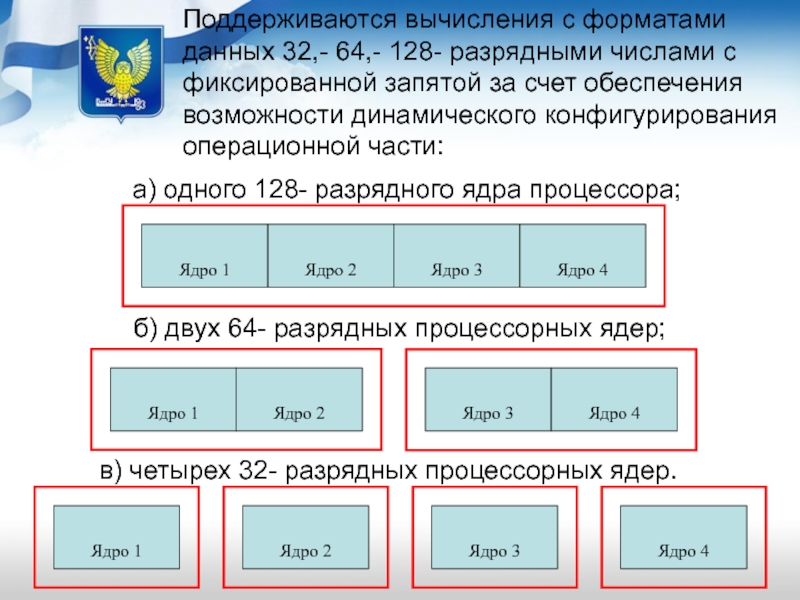

- обеспечена поддержка вычислений в форматах данных 32,- 64,- 128- разрядными числами с фиксированной запятой за счет обеспечения возможности динамического конфигурирования операционной части – разбиения среды на независимые процессорные ядра, причем, «влет»: а) одного 128- разрядного ядра процессора; б) двух 64- разрядных процессорных ядер; в) четырех 32- разрядных процессорных ядер;

- за счет реконфигурации микроархитектуры однородной вычислительной среды процессорных ядер обеспечиваются также и выполнение всех арифметических операции в традиционной позиционной системе счисления;

- обеспечиваются аппаратные преобразования кодов чисел из ППС в СОК и наоборот со скоростью работы ядер процессора.