Московский физико-технический институт (ГУ)

ЗАО «МЦСТ»

- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Проектирование системной панели для вычислительного комплекса Эльбрус-3М1 презентация

Содержание

- 1. Проектирование системной панели для вычислительного комплекса Эльбрус-3М1

- 2. Цель работы Создание системной панели для

- 3. Основные проблемы предыдущей конструкции системной панели Перекрестные

- 4. Методы решения проблем Переход к конструктиву EATX

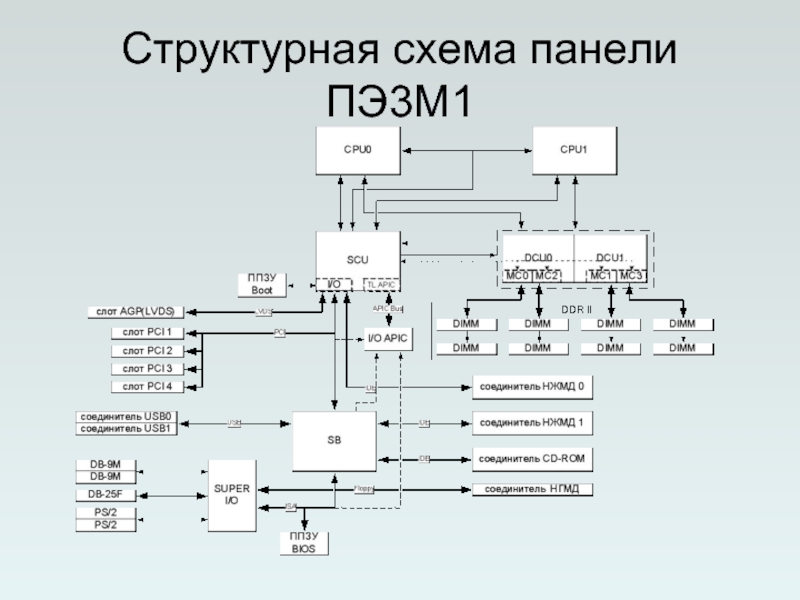

- 5. Структурная схема панели ПЭ3М1

- 6. Структурная схема центральной части панели ПЭ3М1

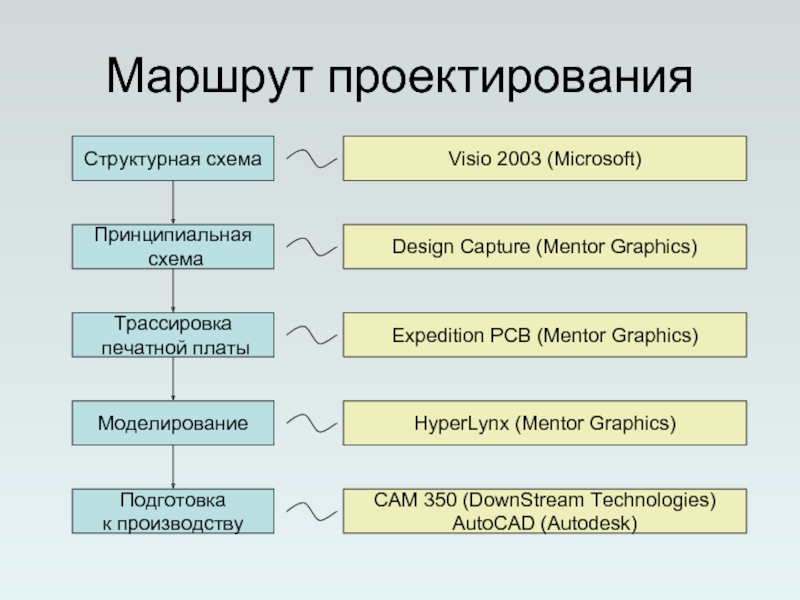

- 7. Маршрут проектирования Структурная схема Принципиальная схема

- 8. Используемые стандарты. IPC standards A Server System

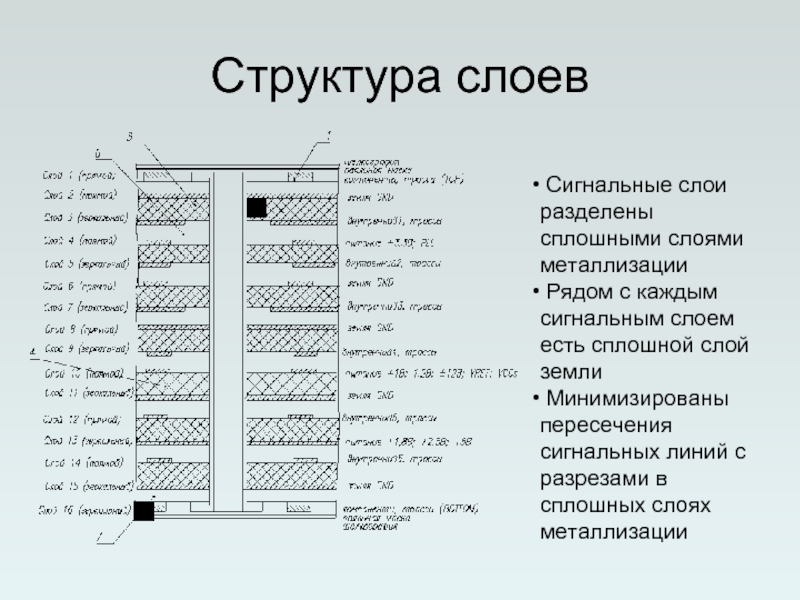

- 9. Структура слоев Сигнальные слои разделены сплошными

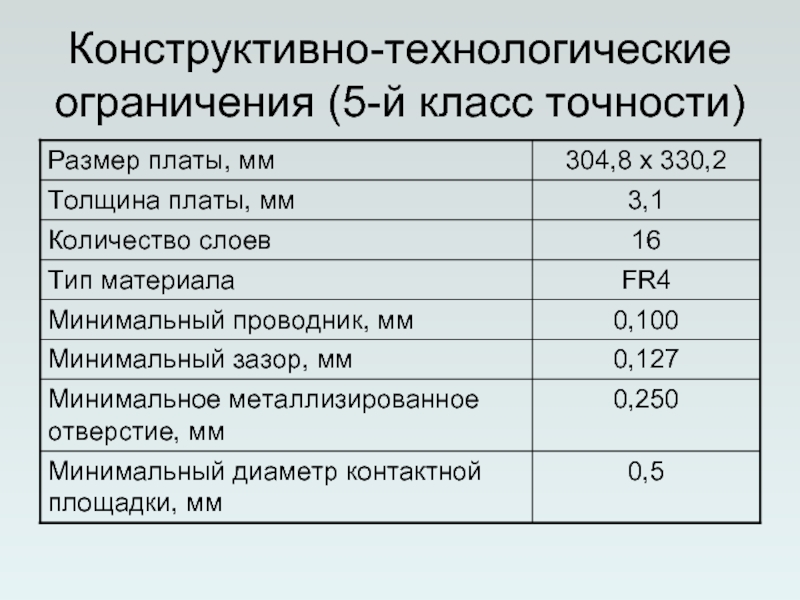

- 10. Конструктивно-технологические ограничения (5-й класс точности)

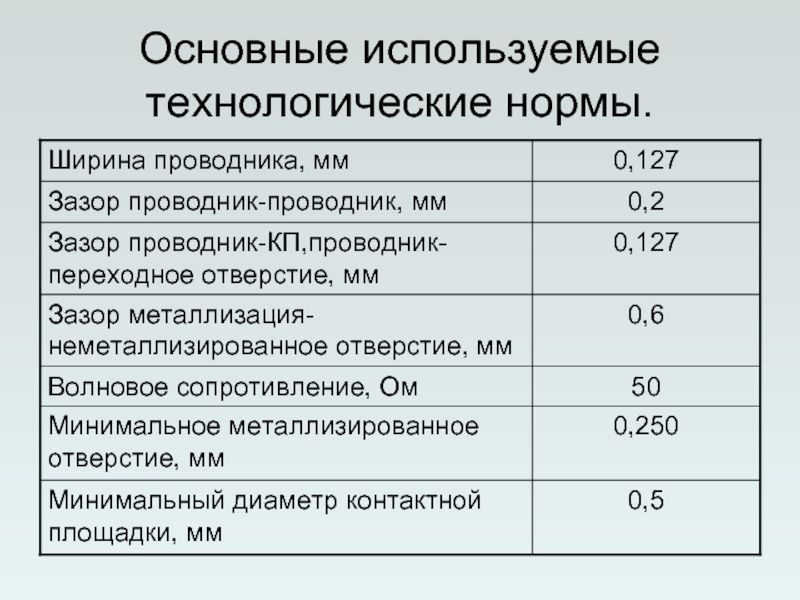

- 11. Основные используемые технологические нормы.

- 12. Внешний вид панели ПЭ3М1

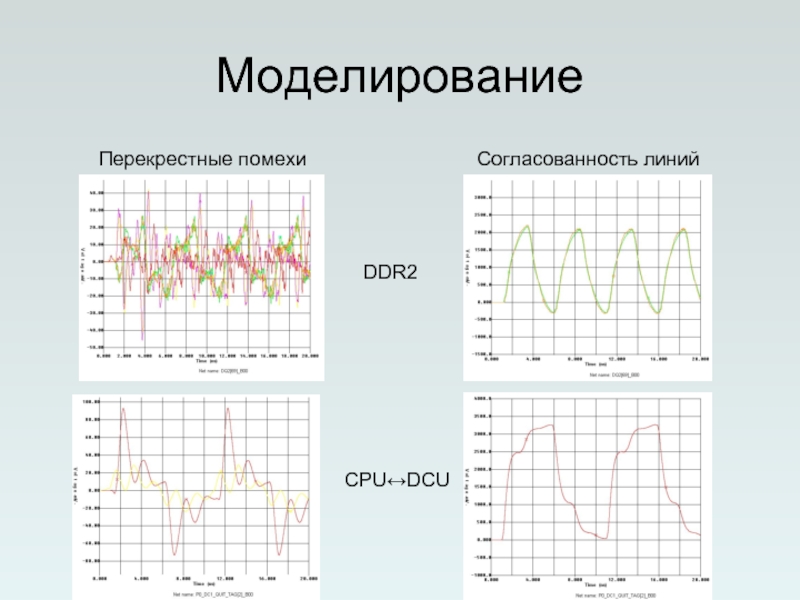

- 13. Моделирование Перекрестные помехи Согласованность линий DDR2 CPU↔DCU

- 14. Внешний вид вычислителя вид сверху, без верхней

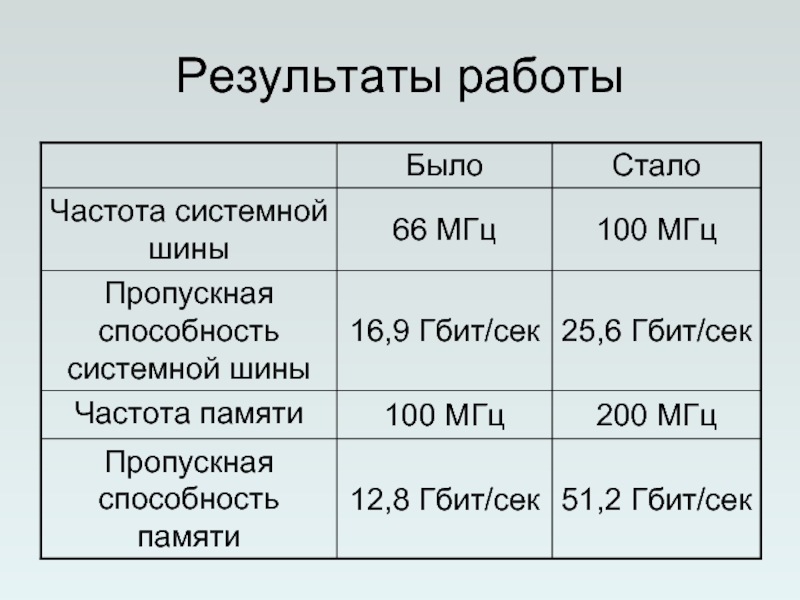

- 15. Результаты работы

Слайд 1Проектирование системной панели для вычислительного комплекса «Эльбрус-3М1»

Воробушков Василий Владимирович

Руководитель: Каре Юлий

Анатольевич

Слайд 2Цель работы

Создание системной панели для вычислительный комплекса «Эльбрус-3М1», являющегося двухпроцессорной

вычислительной системой, на базе микропроцессоров «Эльбрус»

Основываясь на опыте предыдущих разработок устранить обнаруженные ранее недостатки системной панели.

Основываясь на опыте предыдущих разработок устранить обнаруженные ранее недостатки системной панели.

Слайд 3Основные проблемы предыдущей конструкции системной панели

Перекрестные помехи

Большое количество межсоединений

Высокая плотность трассировки

и монтажа

Недостаточное пространство для размещения всех компонентов и сигнальных шин

Сохранение целостности сигнала и большое количество брака

Процессоры установлены в отдельных ячейках

Кодозависимые ошибки

Одновременно переключающиеся сигналы в ПЛИС (SSO)

Большое время доступа при обращении двух процессоров к памяти

Малая скорость работы памяти

Не возможность трассировки памяти согласно спецификации

Разделенные контроллеры памяти

Недостаточное пространство для размещения всех компонентов и сигнальных шин

Сохранение целостности сигнала и большое количество брака

Процессоры установлены в отдельных ячейках

Кодозависимые ошибки

Одновременно переключающиеся сигналы в ПЛИС (SSO)

Большое время доступа при обращении двух процессоров к памяти

Малая скорость работы памяти

Не возможность трассировки памяти согласно спецификации

Разделенные контроллеры памяти

Слайд 4Методы решения проблем

Переход к конструктиву EATX

Размещение всех компонентов на одной плате

Уменьшение

перекрестных помех

Размещение процессоров на самой системной панели

Улучшение целостности сигналов

Переход на ПЛИС Altera Stratix2 EP2S130F1508C3.

Уменьшение эффекта одновременно переключающихся сигналов в ПЛИС (SSO)

Переход от системы с четырьмя контроллерами к системе с тремя контроллерами

Уменьшение количества межсоединений

Компоновка контроллеров памяти в одной микросхеме

Переход к памяти с интерфейсом DDR2 с частой 200МГц

Уменьшение времени доступа при обращение двух процессоров

Использование 4 каналов памяти с двумя слотами памяти на каждом канале

возможность установить до 8 модулей памяти DDR2 суммарным объемом до 8Гбайт

Размещение процессоров на самой системной панели

Улучшение целостности сигналов

Переход на ПЛИС Altera Stratix2 EP2S130F1508C3.

Уменьшение эффекта одновременно переключающихся сигналов в ПЛИС (SSO)

Переход от системы с четырьмя контроллерами к системе с тремя контроллерами

Уменьшение количества межсоединений

Компоновка контроллеров памяти в одной микросхеме

Переход к памяти с интерфейсом DDR2 с частой 200МГц

Уменьшение времени доступа при обращение двух процессоров

Использование 4 каналов памяти с двумя слотами памяти на каждом канале

возможность установить до 8 модулей памяти DDR2 суммарным объемом до 8Гбайт

Слайд 6Структурная схема центральной части панели ПЭ3М1

Неразделенные контроллеры памяти

Уменьшено количество межсоединений

Используются более скоростные контроллеры памяти стандарта DDR2

Слайд 7Маршрут проектирования

Структурная схема

Принципиальная

схема

Трассировка

печатной платы

Моделирование

Подготовка

к производству

Visio 2003 (Microsoft)

Design Capture

(Mentor Graphics)

Expedition PCB (Mentor Graphics)

HyperLynx (Mentor Graphics)

CAM 350 (DownStream Technologies)

AutoCAD (Autodesk)

Слайд 8Используемые стандарты.

IPC standards

A Server System Infrastructure (SSI) Specification version 3-61

DDR2 SDRAM

SPECIFICATION revision JESD79-2A

PCI Local Bus Specification revision 2.2

PCI Local Bus Specification revision 2.2

Слайд 9Структура слоев

Сигнальные слои разделены сплошными слоями металлизации

Рядом с каждым

сигнальным слоем есть сплошной слой земли

Минимизированы пересечения сигнальных линий с разрезами в сплошных слоях металлизации

Минимизированы пересечения сигнальных линий с разрезами в сплошных слоях металлизации