- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Построение тестовых программ для проверки подсистем управления памяти микропроцессоров презентация

Содержание

- 1. Построение тестовых программ для проверки подсистем управления памяти микропроцессоров

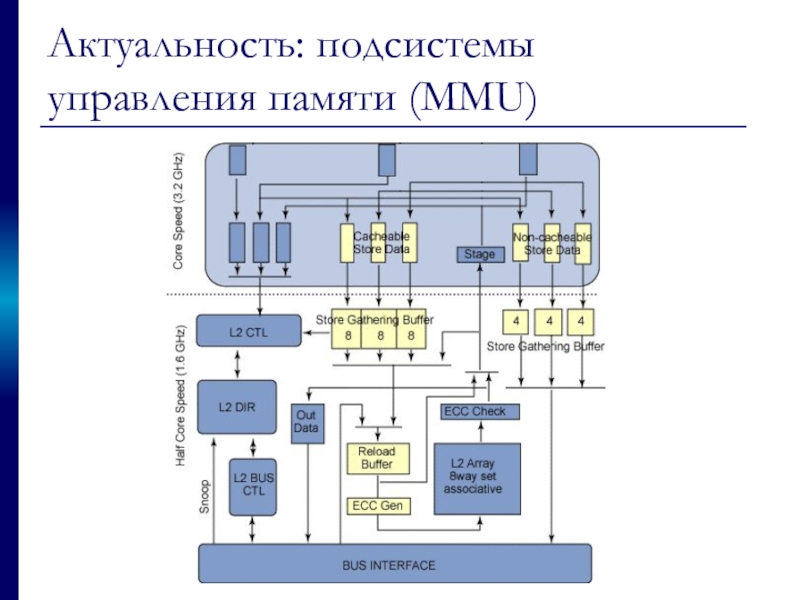

- 2. Актуальность: подсистемы управления памяти (MMU)

- 3. Системное тестирование Задача эмулятор микропроцессора (эталон) (

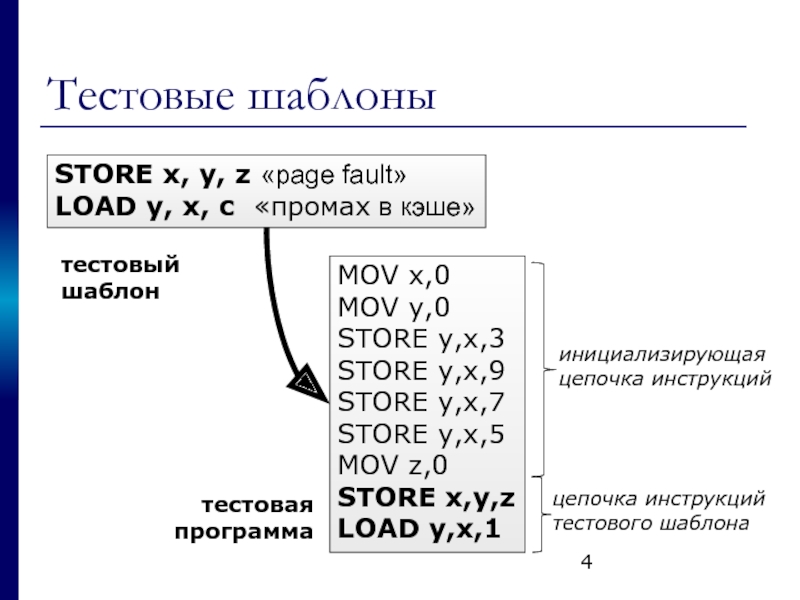

- 4. Тестовые шаблоны STORE x, y, z «page

- 5. Сложность построения тестовых программ по тестовым шаблонам

- 6. Предлагаемый подход к построению тестовых программ

- 7. Эксперименты увеличение допустимого размера шаблонов (было 2-3,

- 8. Основные результаты Предложен подход к построению тестовых

- 10. Основные результаты Создан язык для описания вариантов

- 11. Где предлагаемые методы работают многоуровневая кэш-память

- 12. Направления развития псевдослучайное вытеснение псевдослучайный выбор

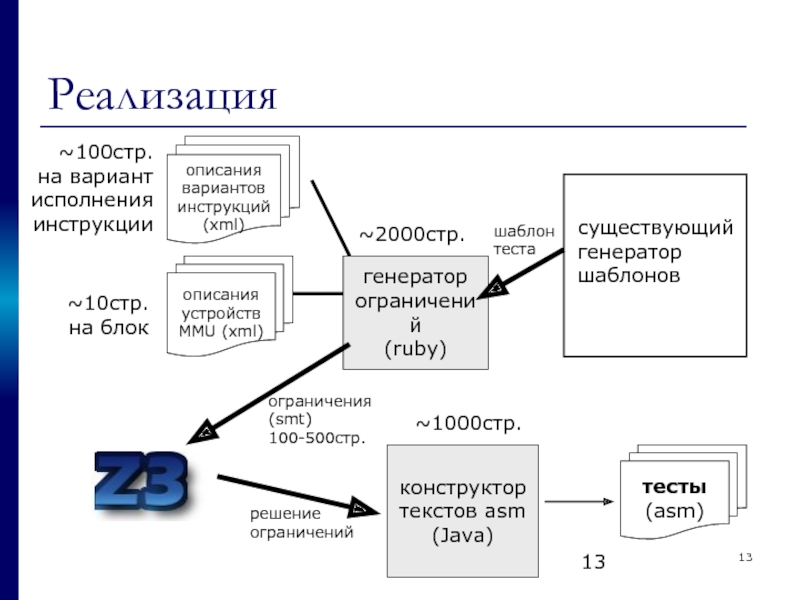

- 13. Реализация существующий генератор шаблонов описания вариантов

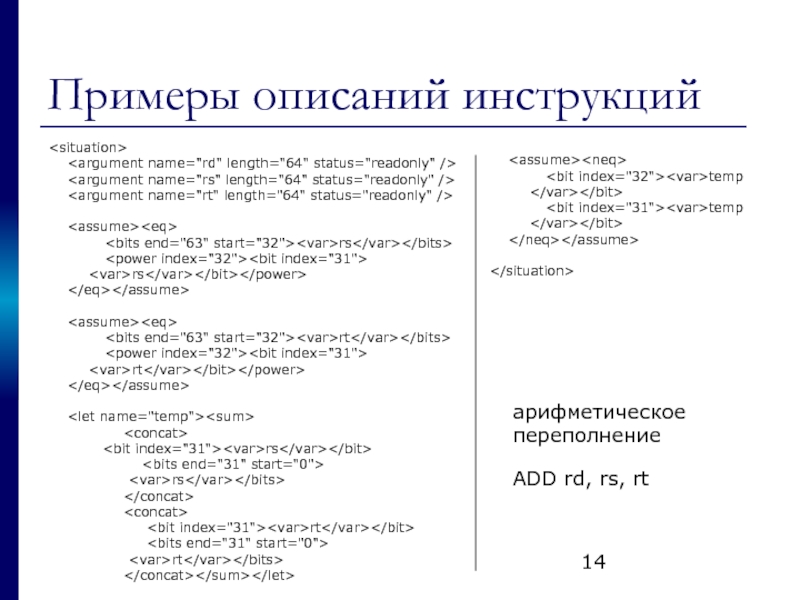

- 14. Примеры описаний инструкций

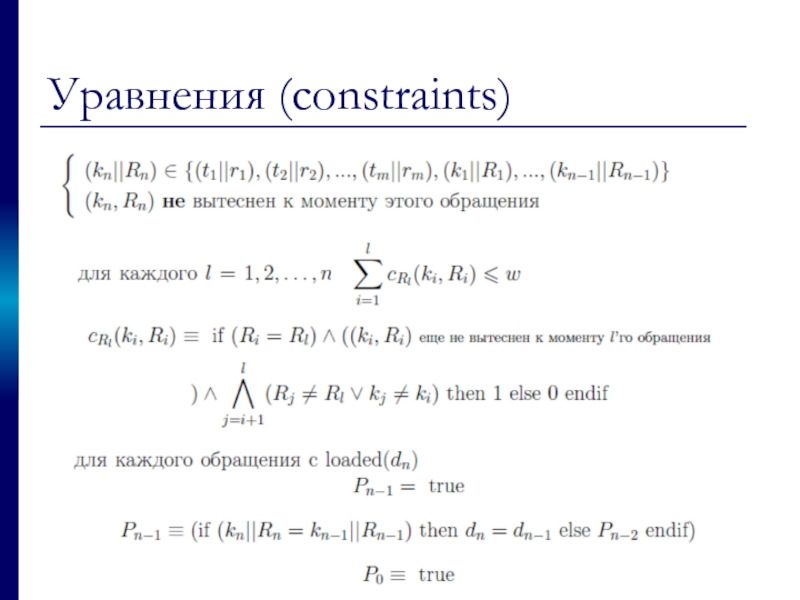

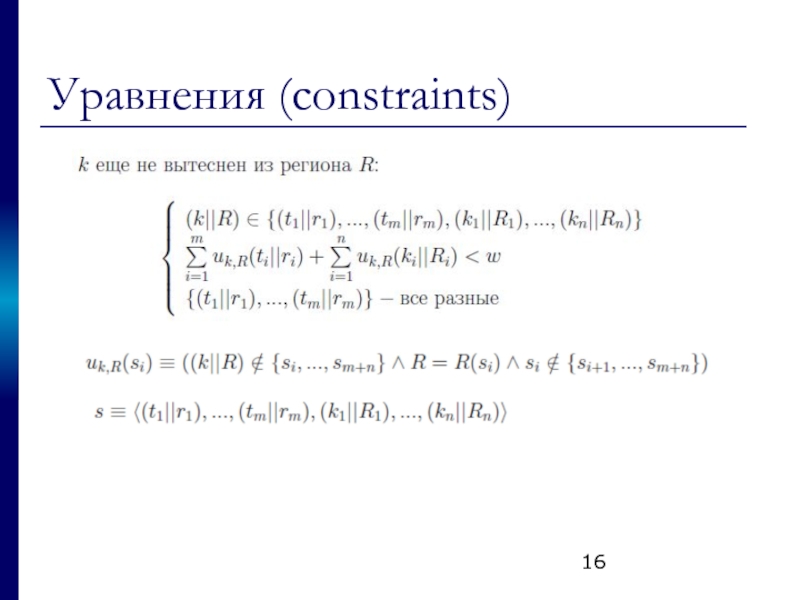

- 15. Уравнения (constraints)

- 16. Уравнения (constraints)

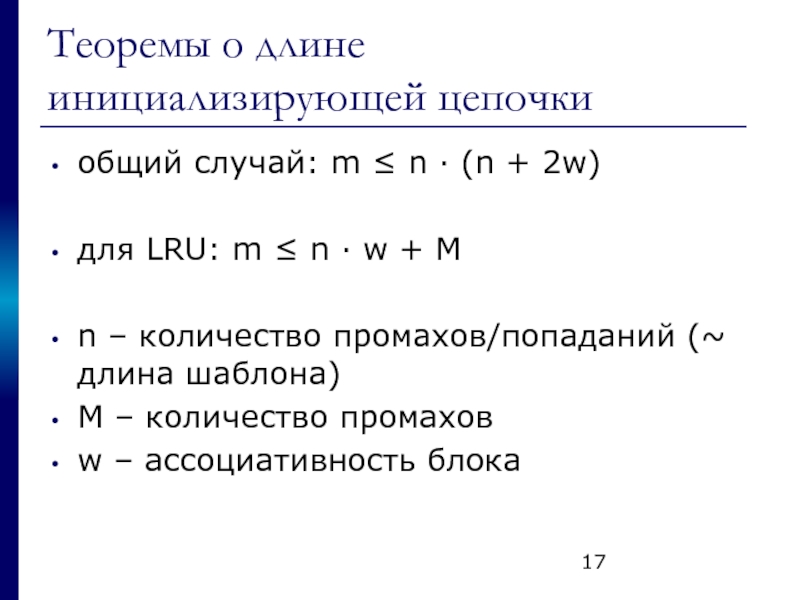

- 17. Теоремы о длине инициализирующей цепочки общий случай:

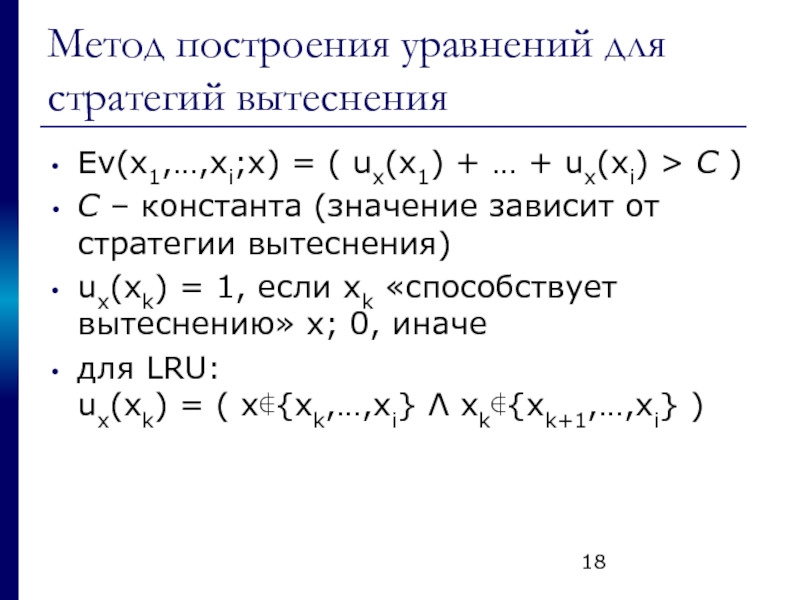

- 18. Метод построения уравнений для стратегий вытеснения Ev(x1,…,xi;x)

- 19. Основные определения Адрес – вектор целых неотрицательных

- 20. Основные определения Данные по адресу x присутствуют

- 21. Основные определения Стратегия вытеснения – это пара

- 22. Направления исследований стратегий вытеснения эффективность стратегий вытесн.

- 23. Метод полезных обращений подобрать функцию a: A*

- 24. Метод полезных обращений подобрать функцию a: A*

- 25. Ситуации в MMU ситуации для отдельных инструкций:

- 26. Ошибки в MMU ошибки обработки управляющих битов

Слайд 1Построение тестовых программ для проверки подсистем управления памяти микропроцессоров

Евгений Корныхин

Слайд 3Системное тестирование

Задача

эмулятор

микропроцессора

(эталон)

( на Си )

cравнение трасс

Возникла ошибка

Успешный прогон

программная

модель

(на Verilog)

lui s1,0x27

ori s1,s1,0xc8

lui

ori s3,s3,0xf7 ...

проводится «сравнением

с эталоном»

тестовые

программы

Задача – построение

тестовых

программ

Слайд 4Тестовые шаблоны

STORE x, y, z «page fault»

LOAD y, x, c «промах

тестовый

шаблон

MOV x,0

MOV y,0

STORE y,x,3

STORE y,x,9

STORE y,x,7

STORE y,x,5

MOV z,0

STORE x,y,z

LOAD y,x,1

тестовая

программа

инициализирующая

цепочка инструкций

цепочка инструкций

тестового шаблона

Слайд 5Сложность построения тестовых программ по тестовым шаблонам

переборная задача

[Кук, 1971]

нетривиальное сведение к

Слайд 6Предлагаемый подход к построению тестовых программ

генератор

системы

ограничений

конструктор

текста

программы

решатель

ограничений

тестовый

шаблон

тестовая

программа

описания

вариантов

исполнения

инструкций

описания

устройств

ограничения для

промахов и

попаданий

ограничения

для всего

шаблона

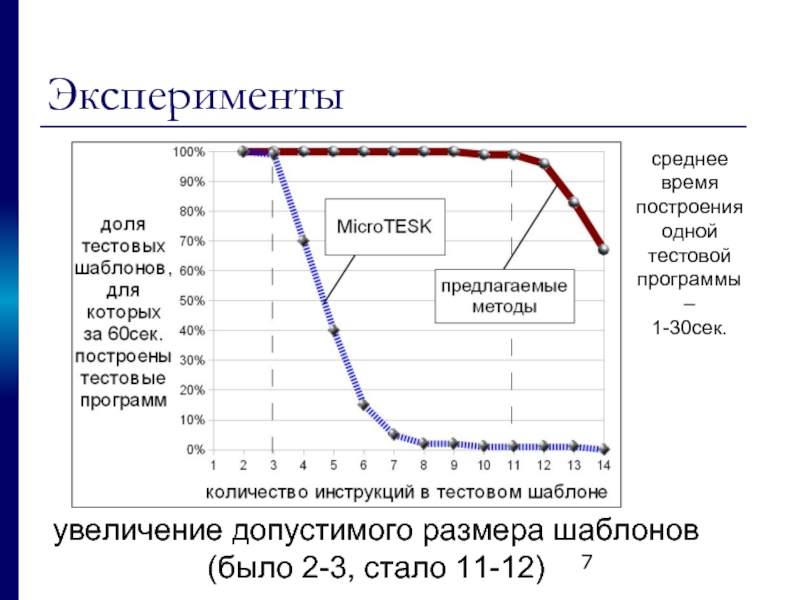

Слайд 7Эксперименты

увеличение допустимого размера шаблонов

(было 2-3, стало 11-12)

среднее

время построения

одной

тестовой

программы –

1-30сек.

Слайд 8Основные результаты

Предложен подход к построению тестовых программ, позволяющий понизить трудоемкость построение

Предложен метод формализации механизма вытеснения при помощи ограничений, эффективно разрешаемых современным инструментарием

Создан прототип генератора тестовых программ, при помощи которого исследована эффективность предложенных решений

Слайд 10Основные результаты

Создан язык для описания вариантов исполнения инструкций ПУП широкого класса

Построена математическая модель последовательной ПУП, в рамках которой сформулирован алгоритм формирования системы ограничений на значения аргументов инструкций тестовой программы. Свойства корректности и полноты этого алгоритма доказаны.

Предложен метод полезных обращений, позволяющий сократить число ограничений на значения аргументов инструкций тестовой программы для случаев вытеснения элемента из кэш-памяти. Получены оценки минимально необходимой длины инициализирующей последовательности инструкций для основных стратегий замещения в кэш-памяти (LRU, Pseudo-LRU, FIFO).

На основе предложенных моделей и методов создан прототип системы построения тестовых программ для проверки ПУП микропроцессоров архитектуры MIPS64 и экспериментально показана его эффективность.

Слайд 11Где предлагаемые методы работают

многоуровневая кэш-память

обращение в память с / без

сквозная запись / отложенная запись

доп.условия на строки кэш-памяти

virtually indexed кэш-память

virtually tagged кэш-память

Слайд 12Направления развития

псевдослучайное вытеснение

псевдослучайный выбор блоков MMU в инструкции

временные ограничения (длительности,

циклические действия (итеративная реализация sqrt)

кэш-память инструкций

многоядерные микропроцессоры

тестирование, нацеленное на эти особенности, надо проводить иначе

Слайд 13Реализация

существующий

генератор

шаблонов

описания

вариантов

инструкций

(xml)

конструктор

текстов asm

(Java)

~100стр.

на вариант

исполнения

инструкции

~2000стр.

~1000стр.

ограничения

(smt)

100-500стр.

генератор

ограничений

(ruby)

описания

устройств

MMU (xml)

~10стр.

на блок

шаблон

теста

решение

ограничений

тесты

(asm)

Слайд 14Примеры описаний инструкций

rs

rt

rs

rt

арифметическое

переполнение

ADD rd, rs, rt

Слайд 17Теоремы о длине инициализирующей цепочки

общий случай: m ≤ n · (n

для LRU: m ≤ n · w + M

n – количество промахов/попаданий (~ длина шаблона)

M – количество промахов

w – ассоциативность блока

Слайд 18Метод построения уравнений для стратегий вытеснения

Ev(x1,…,xi;x) = ( ux(x1) + …

C – константа (значение зависит от стратегии вытеснения)

ux(xk) = 1, если xk «способствует вытеснению» x; 0, иначе

для LRU: ux(xk) = ( x∉{xk,…,xi} Λ xk∉{xk+1,…,xi} )

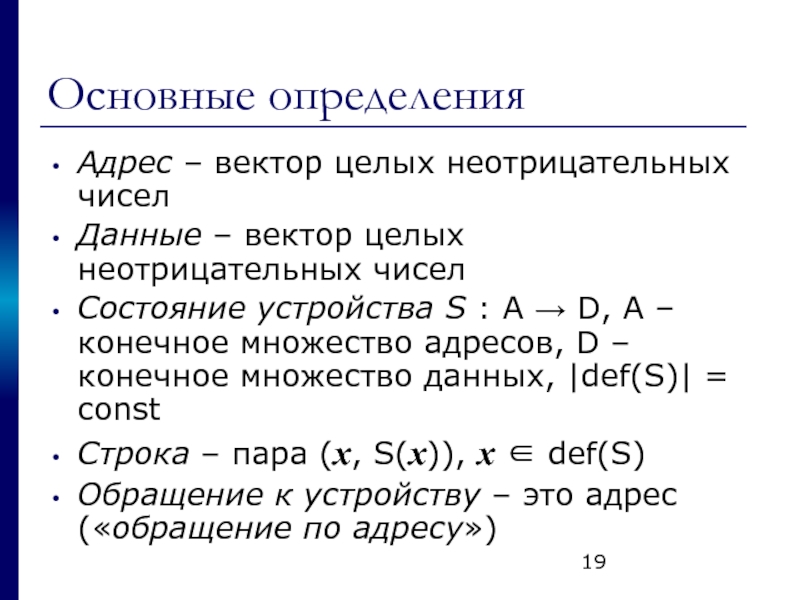

Слайд 19Основные определения

Адрес – вектор целых неотрицательных чисел

Данные – вектор целых неотрицательных

Состояние устройства S : A → D, A – конечное множество адресов, D – конечное множество данных, |def(S)| = const

Строка – пара (x, S(x)), x ∈ def(S)

Обращение к устройству – это адрес («обращение по адресу»)

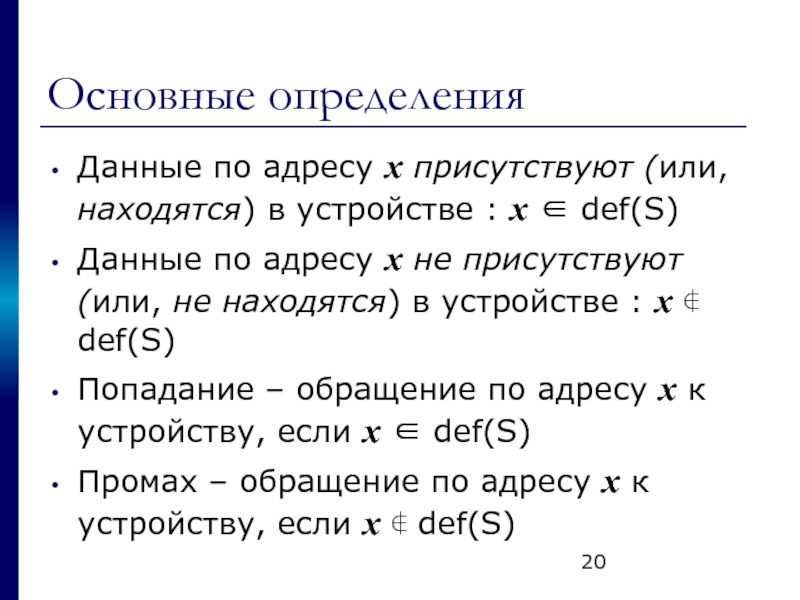

Слайд 20Основные определения

Данные по адресу x присутствуют (или, находятся) в устройстве :

Данные по адресу x не присутствуют (или, не находятся) в устройстве : x ∉ def(S)

Попадание – обращение по адресу x к устройству, если x ∈ def(S)

Промах – обращение по адресу x к устройству, если x ∉ def(S)

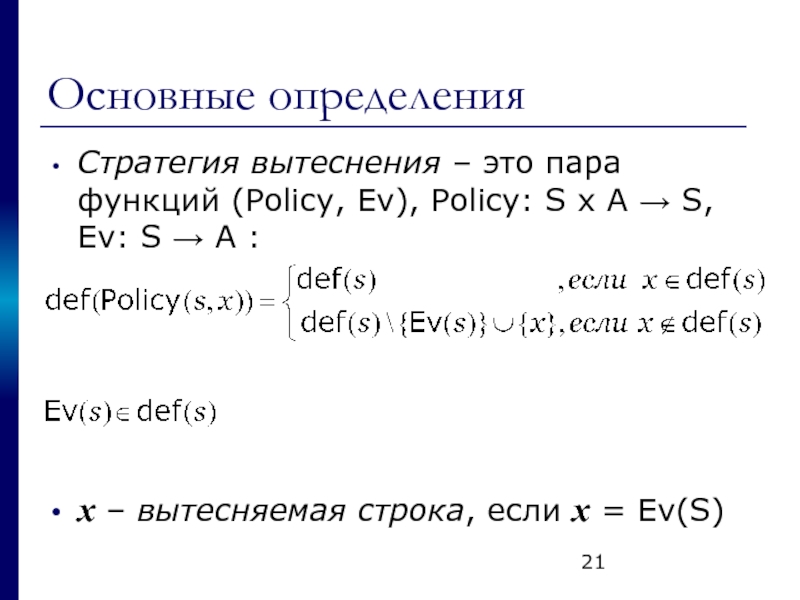

Слайд 21Основные определения

Стратегия вытеснения – это пара функций (Policy, Ev), Policy: S

x – вытесняемая строка, если x = Ev(S)

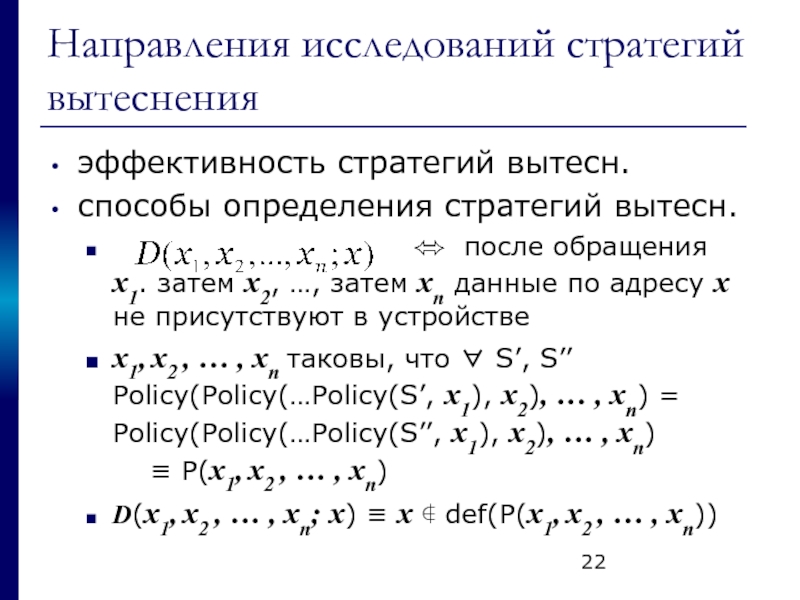

Слайд 22Направления исследований стратегий вытеснения

эффективность стратегий вытесн.

способы определения стратегий вытесн.

x1, x2 , … , xn таковы, что ∀ S’, S’’ Policy(Policy(…Policy(S’, x1), x2), … , xn) = Policy(Policy(…Policy(S’’, x1), x2), … , xn) ≡ P(x1, x2 , … , xn)

D(x1, x2 , … , xn; x) ≡ x ∉ def(P(x1, x2 , … , xn))

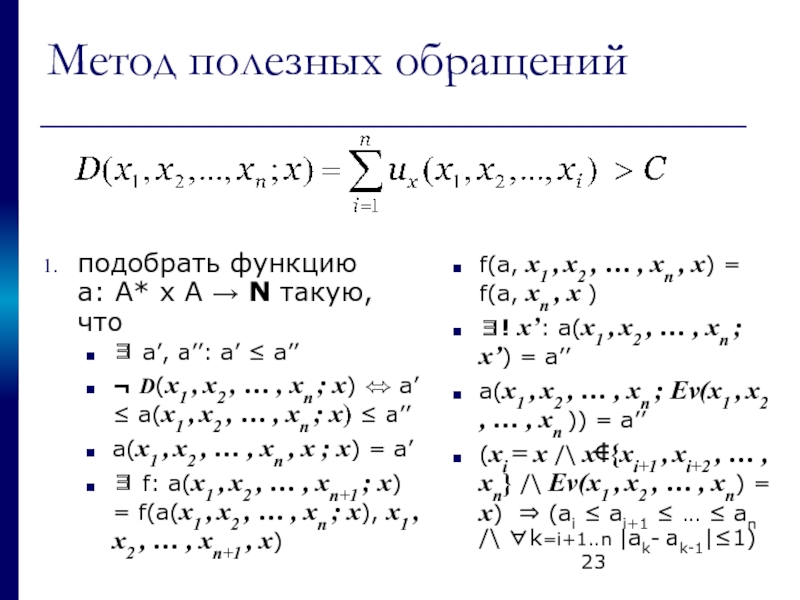

Слайд 23Метод полезных обращений

подобрать функцию

a: A* x A → N такую, что

∃

¬ D(x1 , x2 , … , xn ; x) ⬄ a’ ≤ a(x1 , x2 , … , xn ; x) ≤ a’’

a(x1 , x2 , … , xn , x ; x) = a’

∃ f: a(x1 , x2 , … , xn+1 ; x) = f(a(x1 , x2 , … , xn ; x), x1 , x2 , … , xn+1 , x)

f(a, x1 , x2 , … , xn , x) = f(a, xn , x )

∃! x’: a(x1 , x2 , … , xn ; x’) = a’’

a(x1 , x2 , … , xn ; Ev(x1 , x2 , … , xn )) = a’’

(xi = x /\ x∉{xi+1 , xi+2 , … , xn} /\ Ev(x1 , x2 , … , xn) = x) ⇒ (ai ≤ ai+1 ≤ … ≤ an /\ ∀k=i+1..n |ak- ak-1|≤1)

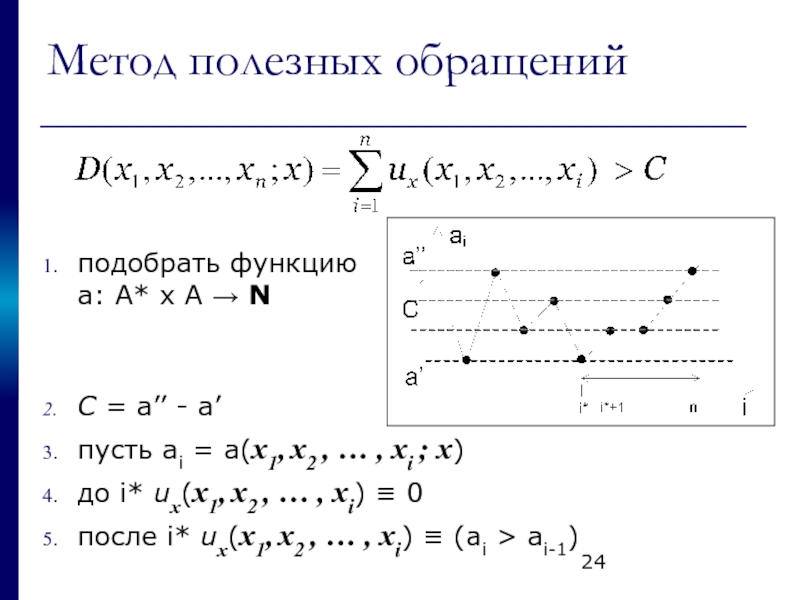

Слайд 24Метод полезных обращений

подобрать функцию

a: A* x A → N

C = a’’

пусть ai = a(x1, x2 , … , xi ; x)

до i* ux(x1, x2 , … , xi) ≡ 0

после i* ux(x1, x2 , … , xi) ≡ (ai > ai-1)

Слайд 25Ситуации в MMU

ситуации для отдельных инструкций:

возникновение исключительных ситуаций

промахи/попадания в кэшах разных

кэшируемые/некэшируемые обращения в память

отображаемые/неотображаемые вирт.адреса

ситуации для цепочек инструкций:

чтение регистра после записи в него

обращения по одинаковым/разным физическим/виртуальным адресам

чтение после записи ячейки памяти

одинаковые/разные страницы вирт.памяти

одинаковые/разные строки кэш-памяти

запись/чтение совместно с исключит.ситуациями

Слайд 26Ошибки в MMU

ошибки обработки управляющих битов

ошибки сопоставления тэгов

конфликты использования ресурсов

ошибки обновления/вытеснения данных

ошибки синхронизации данных

ошибки планирования обработки запросов

ошибки, вызванные исключениями

![Сложность построения тестовых программ по тестовым шаблонампереборная задача[Кук, 1971]нетривиальное сведение к решению систем уравнений и](/img/tmb/3/233855/d754782cb27c70d24d6de2292321008b-800x.jpg)