- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Построение тестовых программ для проверки подсистем управления памяти микропроцессоров презентация

Содержание

- 1. Построение тестовых программ для проверки подсистем управления памяти микропроцессоров

- 2. Место задачи в разработке аппаратного обеспечения ...

- 3. Системное тестирование генерация тестовых программ эмулятор микропроцессора

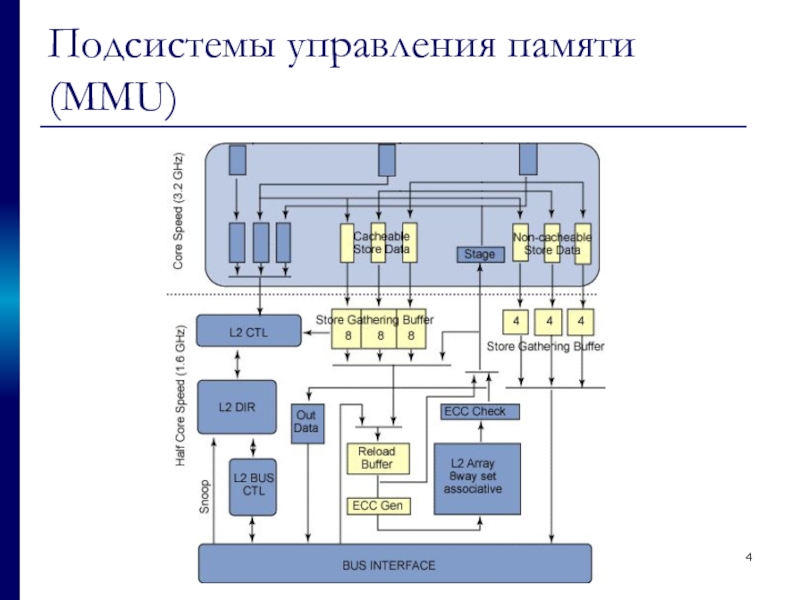

- 4. Подсистемы управления памяти (MMU)

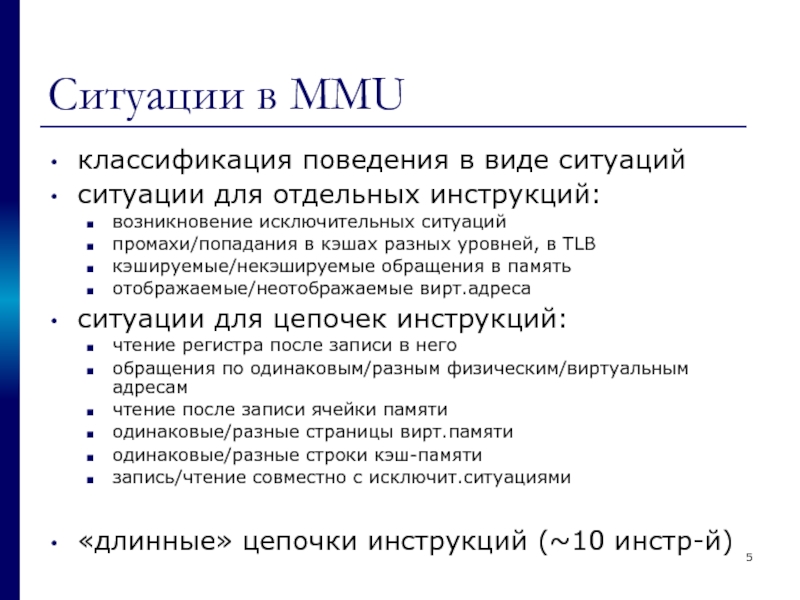

- 5. Ситуации в MMU классификация поведения в виде

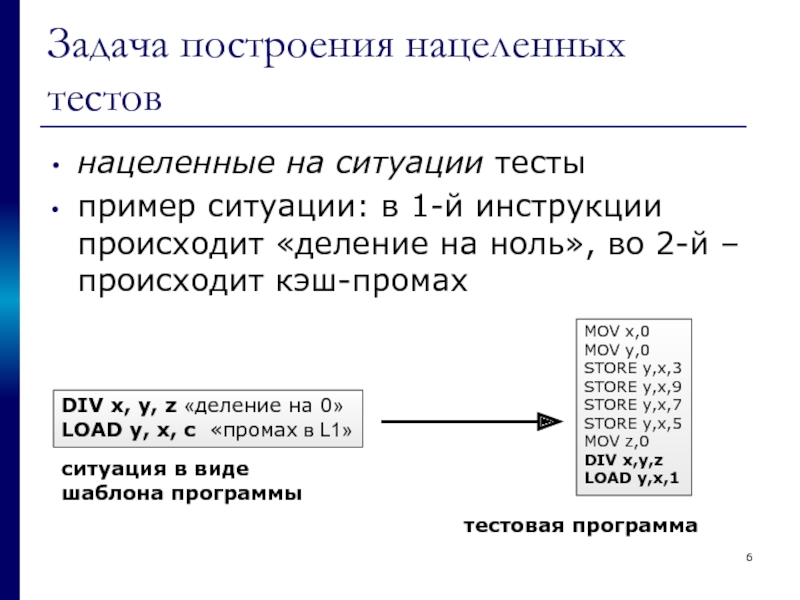

- 6. Задача построения нацеленных тестов нацеленные на ситуации

- 7. Актуальность и задача Актуальность: необходимы методы построения

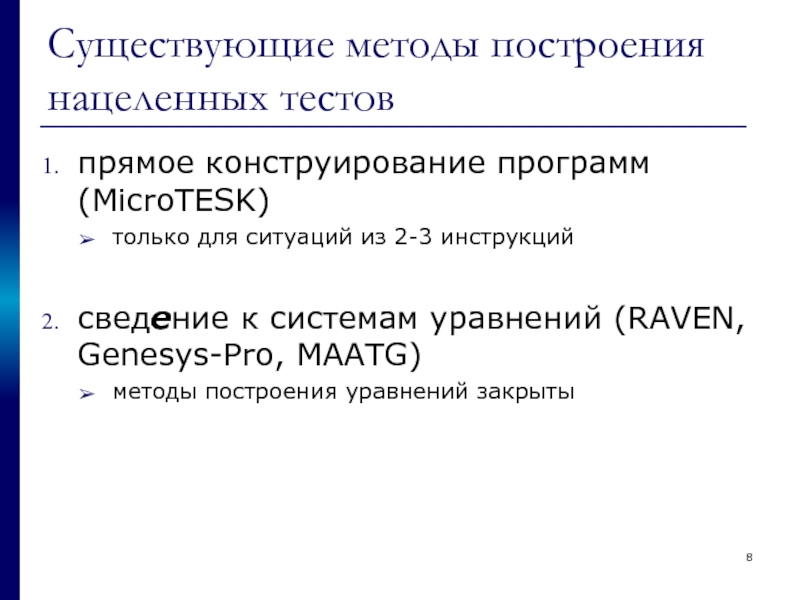

- 8. Существующие методы построения нацеленных тестов прямое конструирование

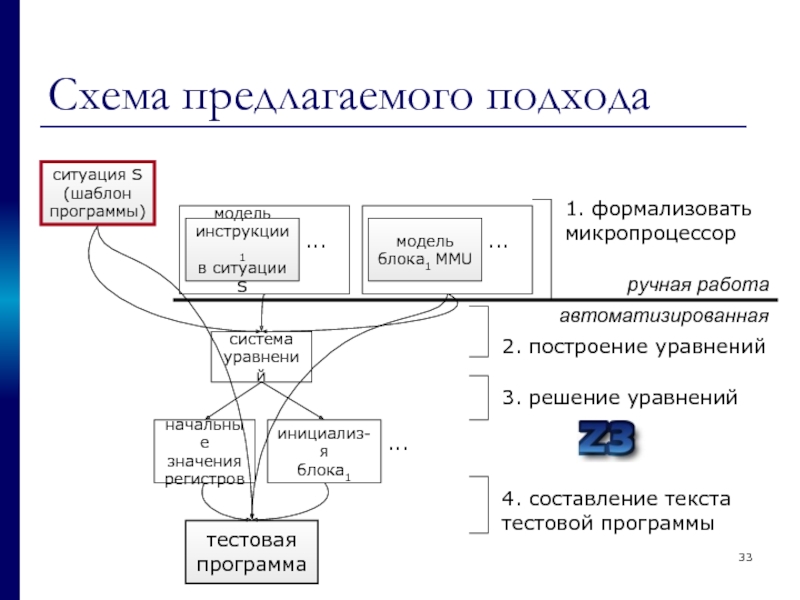

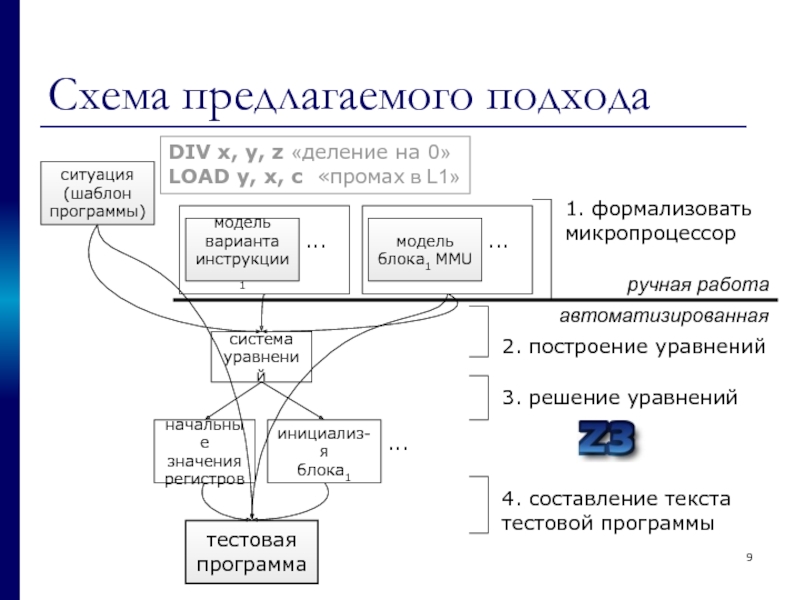

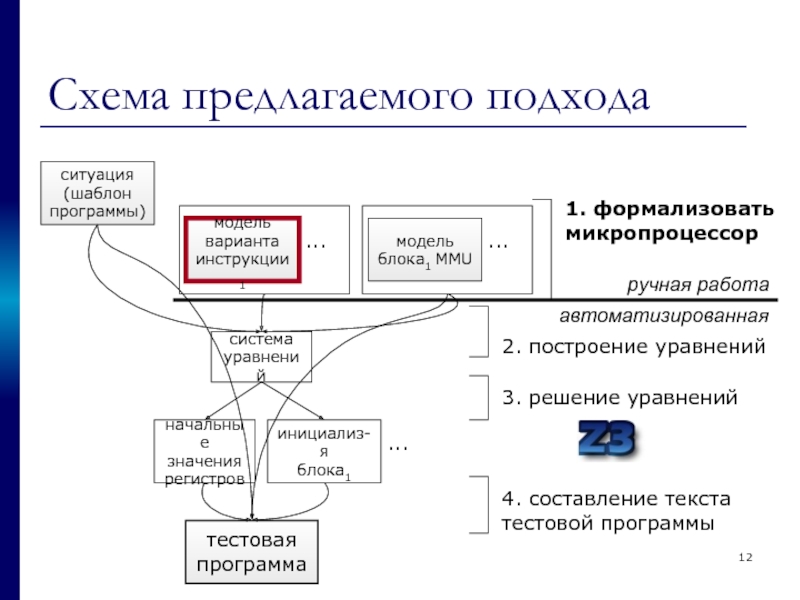

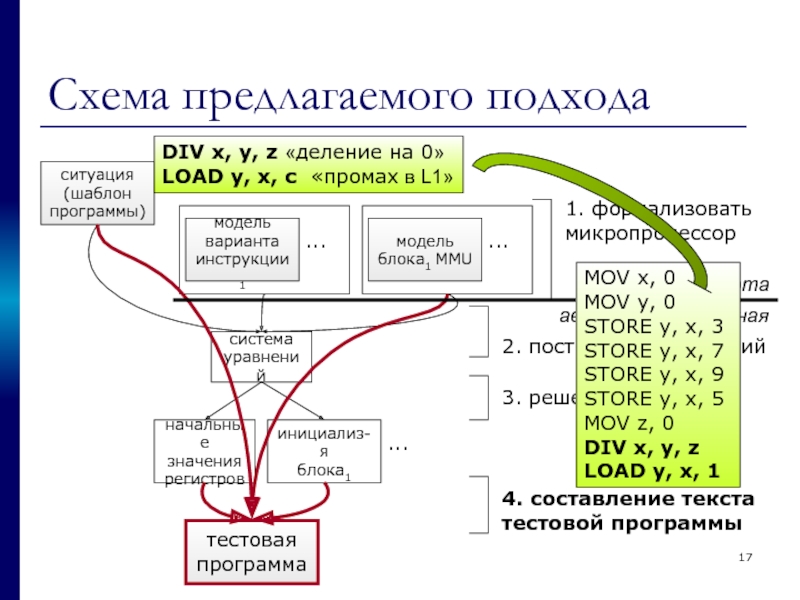

- 9. Схема предлагаемого подхода ситуация (шаблон программы) модель

- 10. Схема предлагаемого подхода ситуация (шаблон программы) модель

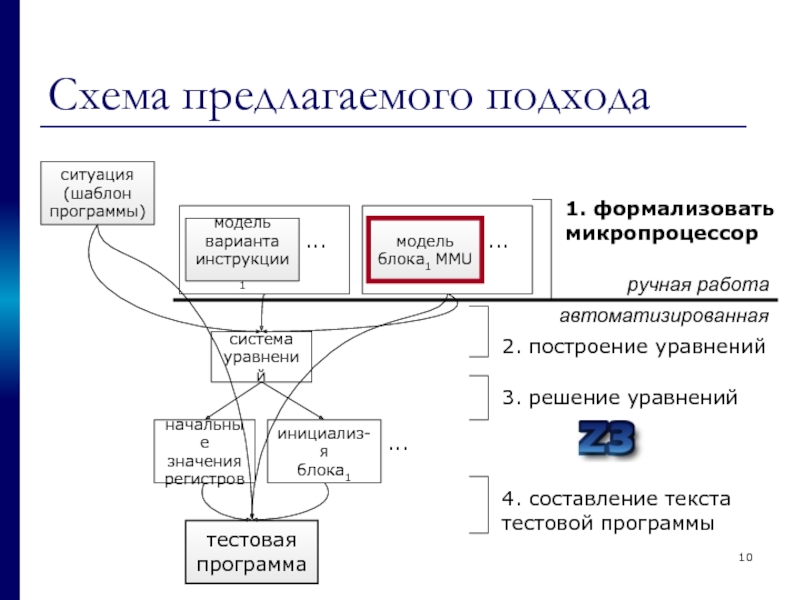

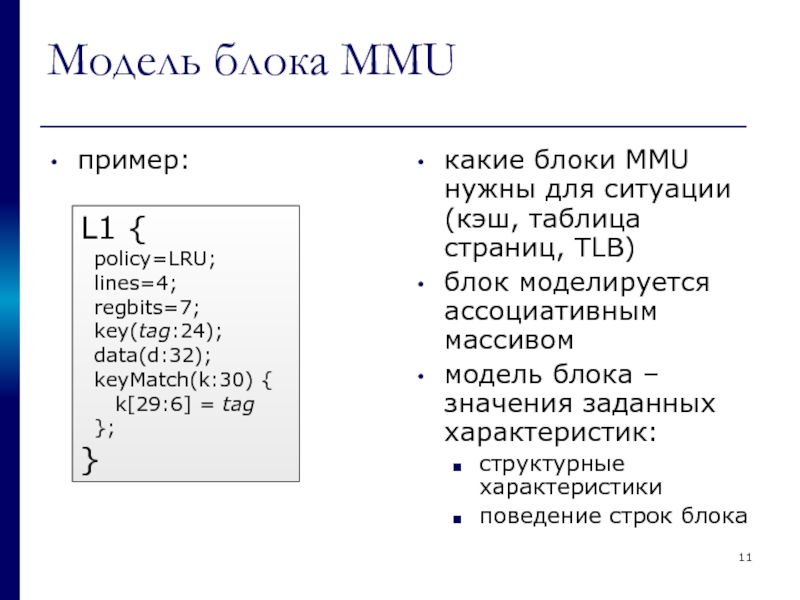

- 11. Модель блока MMU пример: какие блоки MMU

- 12. Схема предлагаемого подхода ситуация (шаблон программы) модель

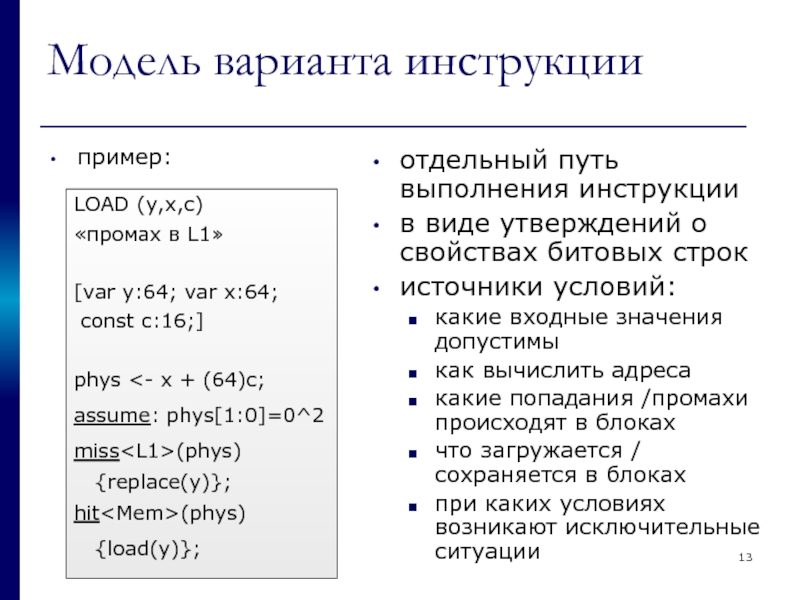

- 13. Модель варианта инструкции пример: отдельный путь выполнения

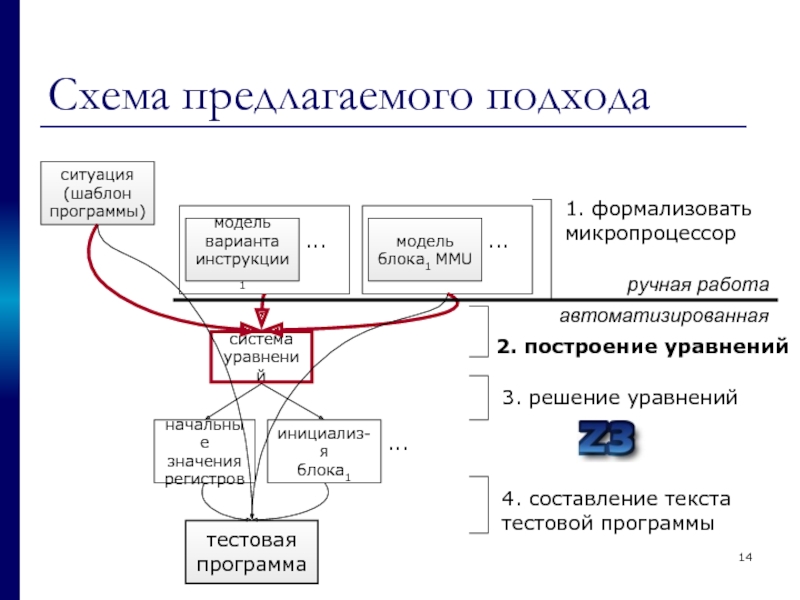

- 14. Схема предлагаемого подхода ситуация (шаблон программы) модель

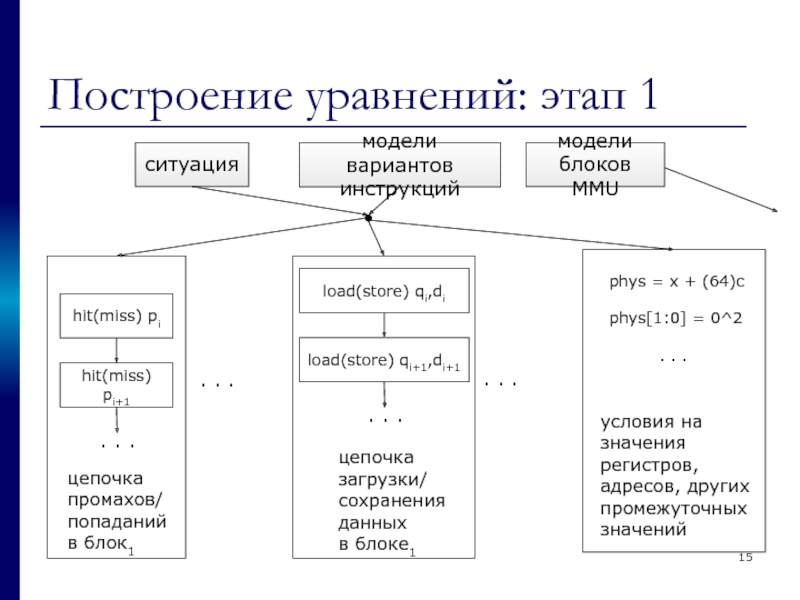

- 15. Построение уравнений: этап 1 ситуация hit(miss) pi

- 16. Построение уравнений: этап 2 hit(miss) pi load(store)

- 17. Схема предлагаемого подхода ситуация (шаблон программы) модель

- 18. Теоремы корректности и полноты методов построения уравнений

- 19. Новизна ситуация (шаблон программы) модель варианта

- 20. Особенности предлагаемых методов блоки инициализируются цепочкой обращений

- 21. Где предлагаемые методы работают многоуровневая кэш-память

- 22. Направления развития псевдослучайное вытеснение псевдослучайный выбор

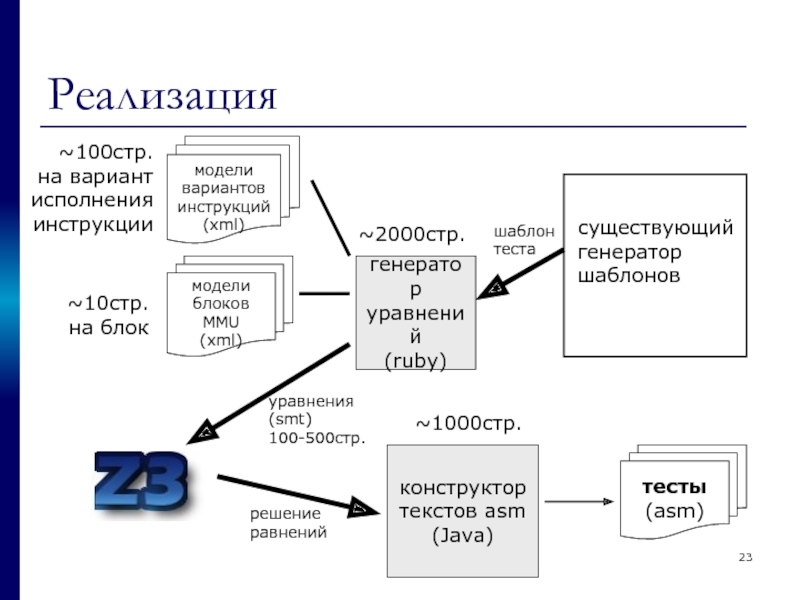

- 23. Реализация существующий генератор шаблонов модели вариантов

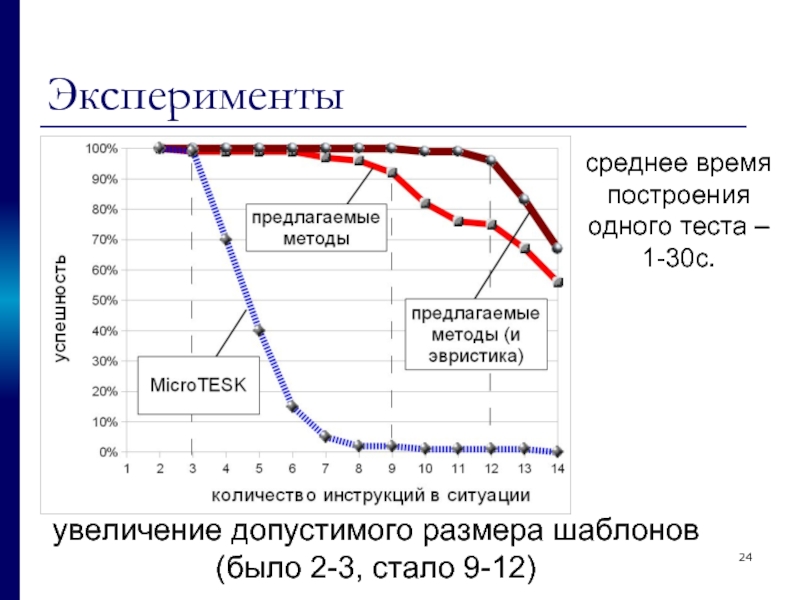

- 24. Эксперименты увеличение допустимого размера шаблонов (было 2-3,

- 25. Практическое использование микропроцессор архитектуры MIPS блоки MMU

- 26. Результаты модель блока MMU, описывающая его характеристики

- 27. Публикации 1. статья в «Программировании» [из

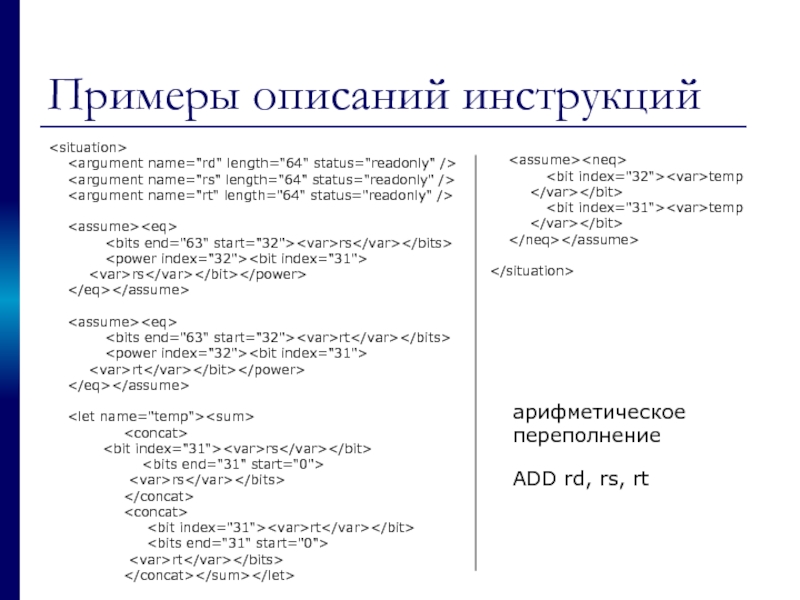

- 28. Примеры описаний инструкций

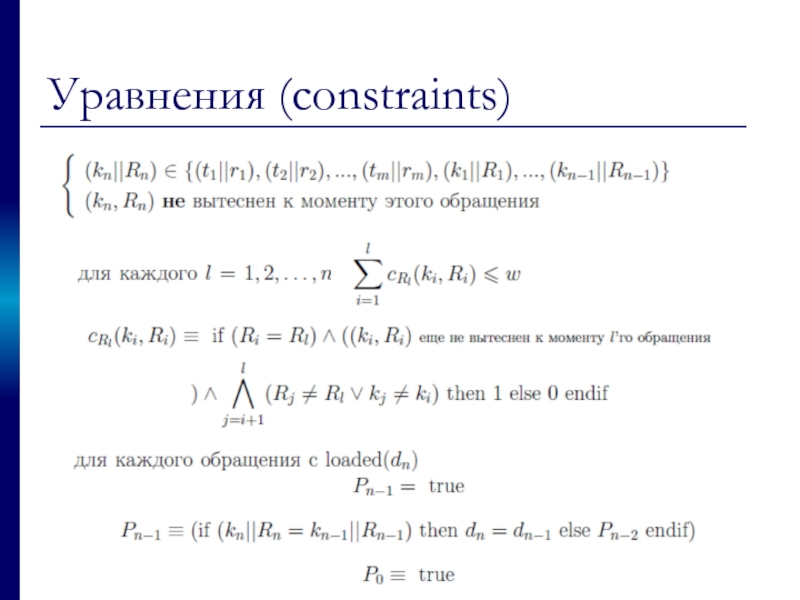

- 29. Уравнения (constraints)

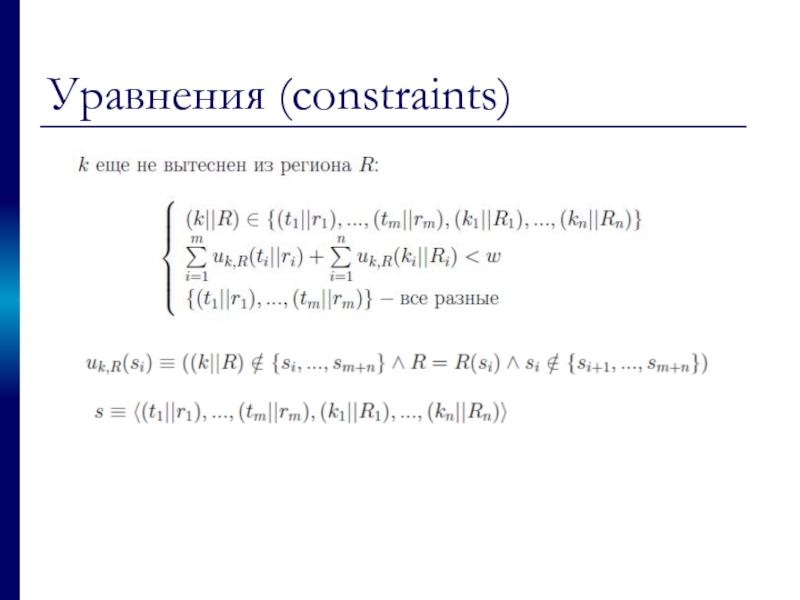

- 30. Уравнения (constraints)

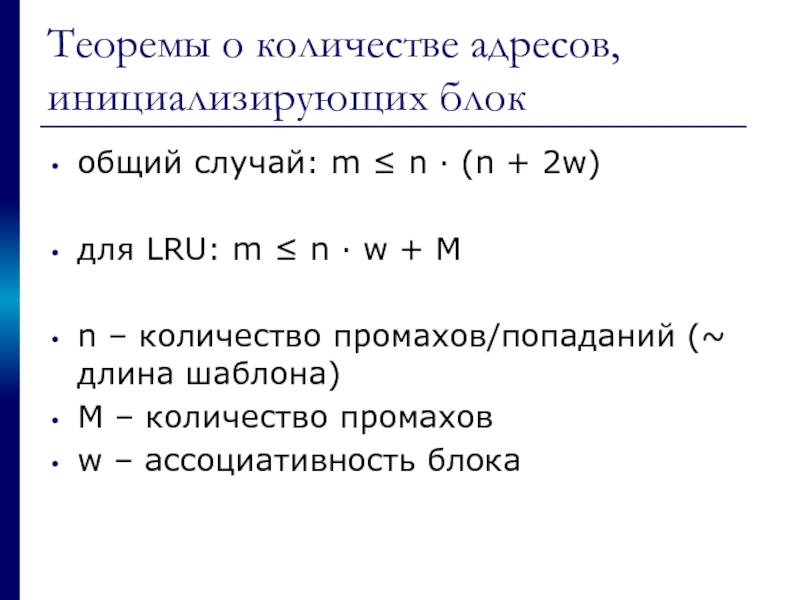

- 31. Теоремы о количестве адресов, инициализирующих блок общий

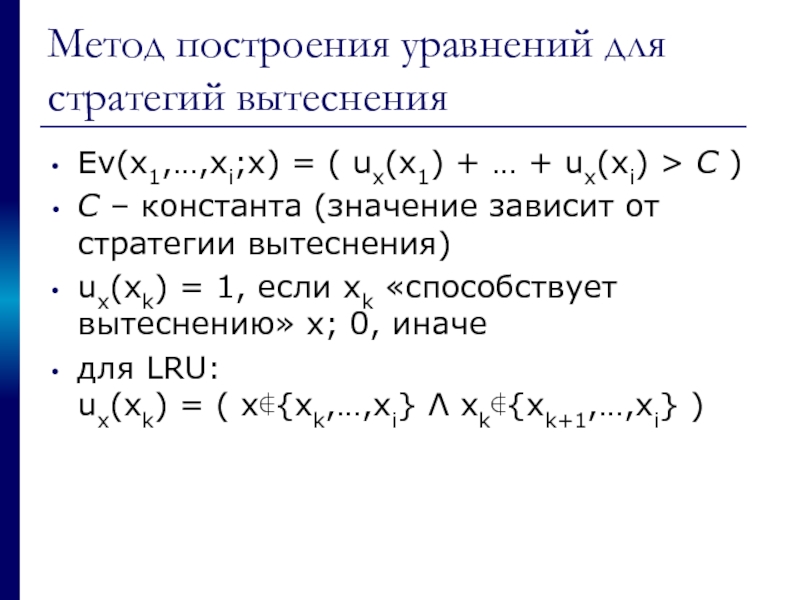

- 32. Метод построения уравнений для стратегий вытеснения Ev(x1,…,xi;x)

- 33. Схема предлагаемого подхода ситуация S (шаблон программы)

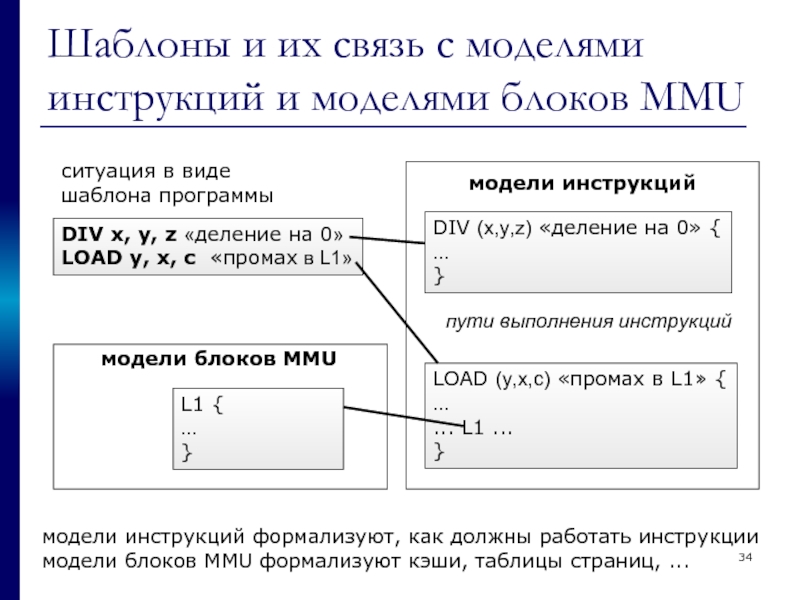

- 34. Шаблоны и их связь с моделями инструкций

Слайд 1Построение тестовых программ для проверки подсистем управления памяти микропроцессоров

Евгений Корныхин

научный руководитель:

д.ф.-м.н.

Слайд 2Место задачи в разработке аппаратного обеспечения

...

output sm_out;

reg [1:0] c, next_state;

always

...

проектные документы

design на Verilog

микропроцессор

тестирование design’а

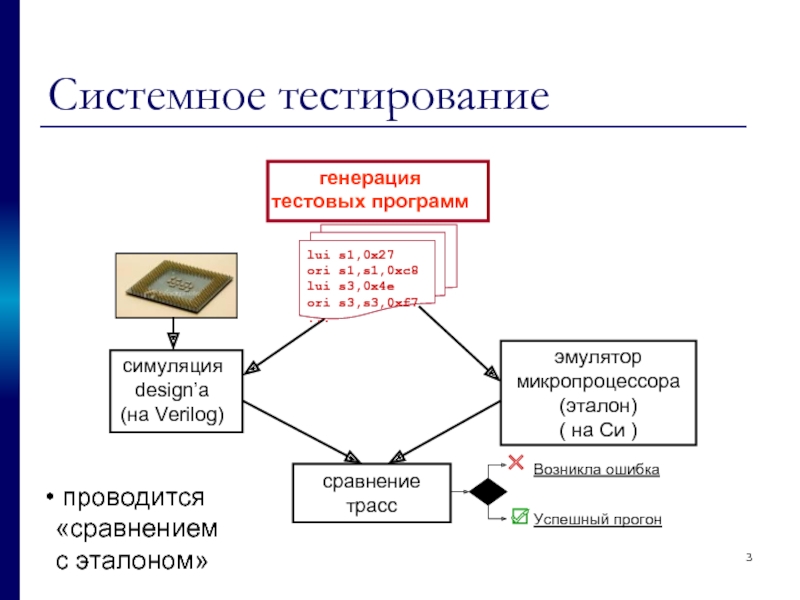

Слайд 3Системное тестирование

генерация

тестовых программ

эмулятор

микропроцессора

(эталон)

( на Си )

cравнение трасс

Возникла ошибка

Успешный прогон

cимуляция

design’а

(на Verilog)

lui

ori s1,s1,0xc8

lui s3,0x4e

ori s3,s3,0xf7 ...

проводится «сравнением

с эталоном»

Слайд 5Ситуации в MMU

классификация поведения в виде ситуаций

ситуации для отдельных инструкций:

возникновение исключительных

промахи/попадания в кэшах разных уровней, в TLB

кэшируемые/некэшируемые обращения в память

отображаемые/неотображаемые вирт.адреса

ситуации для цепочек инструкций:

чтение регистра после записи в него

обращения по одинаковым/разным физическим/виртуальным адресам

чтение после записи ячейки памяти

одинаковые/разные страницы вирт.памяти

одинаковые/разные строки кэш-памяти

запись/чтение совместно с исключит.ситуациями

«длинные» цепочки инструкций (~10 инстр-й)

Слайд 6Задача построения нацеленных тестов

нацеленные на ситуации тесты

пример ситуации: в 1-й инструкции

DIV x, y, z «деление на 0»

LOAD y, x, c «промах в L1»

ситуация в виде

шаблона программы

MOV x,0

MOV y,0

STORE y,x,3

STORE y,x,9

STORE y,x,7

STORE y,x,5

MOV z,0

DIV x,y,z

LOAD y,x,1

тестовая программа

Слайд 7Актуальность и задача

Актуальность:

необходимы методы построения тестов, нацеленных на верификацию MMU в

Задача:

разработать метод построения нацеленных тестов (пригодный в том числе и для ситуаций из «длинных» цепочек инструкций на MMU)

Слайд 8Существующие методы построения нацеленных тестов

прямое конструирование программ (MicroTESK)

только для ситуаций из

сведение к системам уравнений (RAVEN, Genesys-Pro, MAATG)

методы построения уравнений закрыты

Слайд 9Схема предлагаемого подхода

ситуация

(шаблон

программы)

модель

варианта

инструкции1

...

модель

блока1 MMU

...

1. формализовать

микропроцессор

система

уравнений

начальные

значения

регистров

инициализ-я

блока1

...

тестовая

программа

2. построение уравнений

3. решение уравнений

4. составление текста

тестовой

ручная работа

автоматизированная

DIV x, y, z «деление на 0»

LOAD y, x, c «промах в L1»

Слайд 10Схема предлагаемого подхода

ситуация

(шаблон

программы)

модель

варианта

инструкции1

...

модель

блока1 MMU

...

1. формализовать

микропроцессор

система

уравнений

начальные

значения

регистров

инициализ-я

блока1

...

тестовая

программа

2. построение уравнений

3. решение уравнений

4. составление текста

тестовой

ручная работа

автоматизированная

Слайд 11Модель блока MMU

пример:

какие блоки MMU нужны для ситуации (кэш, таблица страниц,

блок моделируется ассоциативным массивом

модель блока – значения заданных характеристик:

структурные характеристики

поведение строк блока

L1 {

policy=LRU;

lines=4;

regbits=7;

key(tag:24);

data(d:32);

keyMatch(k:30) {

k[29:6] = tag

};

}

Слайд 12Схема предлагаемого подхода

ситуация

(шаблон

программы)

модель

варианта

инструкции1

...

модель

блока1 MMU

...

1. формализовать

микропроцессор

система

уравнений

начальные

значения

регистров

инициализ-я

блока1

...

тестовая

программа

2. построение уравнений

3. решение уравнений

4. составление текста

тестовой

ручная работа

автоматизированная

Слайд 13Модель варианта инструкции

пример:

отдельный путь выполнения инструкции

в виде утверждений о свойствах битовых

источники условий:

какие входные значения допустимы

как вычислить адреса

какие попадания /промахи происходят в блоках

что загружается / сохраняется в блоках

при каких условиях возникают исключительные ситуации

LOAD (y,x,c)

«промах в L1»

[var y:64; var x:64;

const c:16;]

phys <- x + (64)c;

assume: phys[1:0]=0^2

miss

hit

{load(y)};

Слайд 14Схема предлагаемого подхода

ситуация

(шаблон

программы)

модель

варианта

инструкции1

...

модель

блока1 MMU

...

1. формализовать

микропроцессор

система

уравнений

начальные

значения

регистров

инициализ-я

блока1

...

тестовая

программа

2. построение уравнений

3. решение уравнений

4. составление текста

тестовой

ручная работа

автоматизированная

Слайд 15Построение уравнений: этап 1

ситуация

hit(miss) pi

hit(miss) pi+1

. . .

цепочка

промахов/

попаданий

в блок1

load(store) qi,di

load(store) qi+1,di+1

.

цепочка

загрузки/

сохранения

данных

в блоке1

. . .

. . .

phys = x + (64)c

phys[1:0] = 0^2

. . .

условия на

значения

регистров,

адресов, других

промежуточных

значений

модели вариантов

инструкций

модели

блоков MMU

Слайд 16Построение уравнений: этап 2

hit(miss) pi

load(store) qi,di

phys[1:0] = 0^2

(свойства битовых строк)

система уравнений

Hit [pi] =

pi ∈{p1,…,pi-1} Λ

¬Ev(p1,…,pi-1; pi)

Miss [pi] =

pi ∈{p1,…,pi-1} Λ

Ev(p1,…,pi-1; pi)

равенство

данных

при равных

адресах

phys[1:0] = 0^2

(без изменений)

это

новые

методы

модели

блоков MMU

Слайд 17Схема предлагаемого подхода

ситуация

(шаблон

программы)

модель

варианта

инструкции1

...

модель

блока1 MMU

...

1. формализовать

микропроцессор

система

уравнений

начальные

значения

регистров

инициализ-я

блока1

...

тестовая

программа

2. построение уравнений

3. решение уравнений

4. составление текста

тестовой

ручная работа

автоматизированная

DIV x, y, z «деление на 0»

LOAD y, x, c «промах в L1»

MOV x, 0

MOV y, 0

STORE y, x, 3

STORE y, x, 7

STORE y, x, 9

STORE y, x, 5

MOV z, 0

DIV x, y, z

LOAD y, x, 1

Слайд 18Теоремы корректности и полноты методов построения уравнений

доказана корректность: если предлагаемые методы

доказана полнота: если для шаблона существует тест, то предлагаемые методы строят систему уравнений, среди решений которой есть этот тест (если она несовместна, то шаблону не соответствует ни один тест)

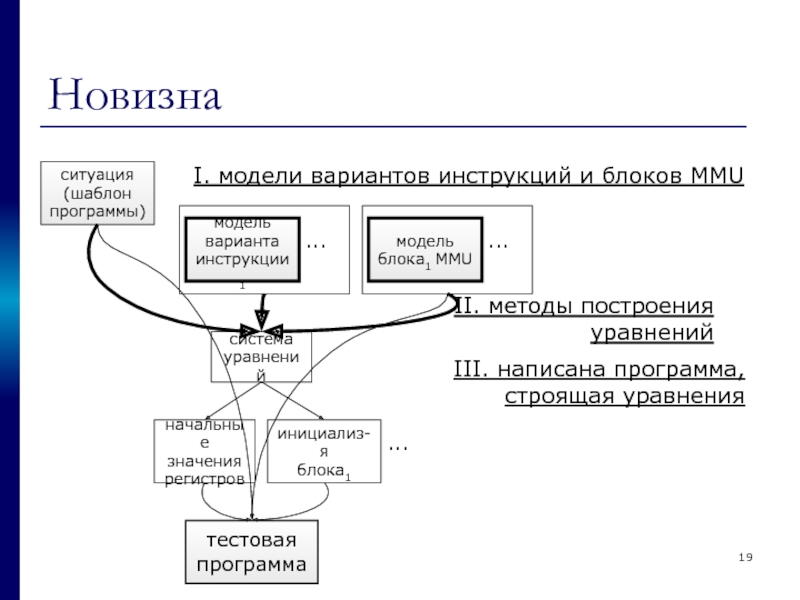

Слайд 19Новизна

ситуация

(шаблон

программы)

модель

варианта

инструкции1

...

модель

блока1 MMU

...

система

уравнений

начальные

значения

регистров

инициализ-я

блока1

...

тестовая

программа

I. модели вариантов инструкций и блоков MMU

II. методы построения

уравнений

III.

Слайд 20Особенности предлагаемых методов

блоки инициализируются цепочкой обращений в них по адресам –

единая система уравнений

компактность уравнений (в них выражается не изменение состояния, а зависимости адресов)

Слайд 21Где предлагаемые методы работают

многоуровневая кэш-память

обращение в память с / без

сквозная запись / отложенная запись

доп.условия на строки кэш-памяти

virtually indexed кэш-память

virtually tagged кэш-память

Слайд 22Направления развития

псевдослучайное вытеснение

псевдослучайный выбор блоков MMU в инструкции

временные ограничения (длительности,

циклические действия (например, sqrt)

кэш-память инструкций

тестирование, нацеленное на эти особенности, надо проводить иначе

Слайд 23Реализация

существующий

генератор

шаблонов

модели

вариантов

инструкций

(xml)

конструктор

текстов asm

(Java)

~100стр.

на вариант

исполнения

инструкции

~2000стр.

~1000стр.

уравнения

(smt)

100-500стр.

генератор

уравнений

(ruby)

модели

блоков MMU

(xml)

~10стр.

на блок

шаблон

теста

решение

равнений

тесты

(asm)

Слайд 24Эксперименты

увеличение допустимого размера шаблонов

(было 2-3, стало 9-12)

среднее время построения

одного теста –

Слайд 25Практическое использование

микропроцессор архитектуры MIPS

блоки MMU в микропроцессоре:

кэш L1 16кБ

кэш L2 256кБ

TLB

microTLB 4 строки

Слайд 26Результаты

модель блока MMU, описывающая его характеристики

модель инструкции в виде совокупности отдельных

метод построения разрешаемых уравнений для шаблонов в виде уравнений над битовыми строками без описания изменения состояния MMU

методы описания стратегий вытеснения c помощью уравнений над битовыми строками и ограничениями сумм бит

Слайд 27Публикации

1. статья в «Программировании»

[из списка ВАК]

2. статья в «Вычислительных методах

3-4. статьи на SYRCoSE-2008 и 2009

5. статья на EWDTS-2009

6-7. статьи в сборниках трудов ИСП РАН (тт.15, 17)

Слайд 28Примеры описаний инструкций

rs

rt

rs

rt

арифметическое

переполнение

ADD rd, rs, rt

Слайд 31Теоремы о количестве адресов, инициализирующих блок

общий случай: m ≤ n ·

для LRU: m ≤ n · w + M

n – количество промахов/попаданий (~ длина шаблона)

M – количество промахов

w – ассоциативность блока

Слайд 32Метод построения уравнений для стратегий вытеснения

Ev(x1,…,xi;x) = ( ux(x1) + …

C – константа (значение зависит от стратегии вытеснения)

ux(xk) = 1, если xk «способствует вытеснению» x; 0, иначе

для LRU: ux(xk) = ( x∉{xk,…,xi} Λ xk∉{xk+1,…,xi} )

Слайд 33Схема предлагаемого подхода

ситуация S

(шаблон

программы)

модель

инструкции1

в ситуации S

...

модель

блока1 MMU

...

1. формализовать

микропроцессор

система

уравнений

начальные

значения

регистров

инициализ-я

блока1

...

тестовая

программа

2. построение уравнений

3. решение

4. составление текста

тестовой программы

ручная работа

автоматизированная

Слайд 34Шаблоны и их связь с моделями инструкций и моделями блоков MMU

DIV

LOAD y, x, c «промах в L1»

ситуация в виде

шаблона программы

DIV (x,y,z) «деление на 0» {

…

}

LOAD (y,x,c) «промах в L1» {

…

... L1 ...

}

модели инструкций

модели блоков MMU

L1 {

…

}

модели инструкций формализуют, как должны работать инструкции

модели блоков MMU формализуют кэши, таблицы страниц, ...

пути выполнения инструкций

![Место задачи в разработке аппаратного обеспечения...output sm_out;reg [1:0] c, next_state; always @ (posedge sm_cl) begin](/img/tmb/2/100657/ddf4e7b9d4a88730f311be91bf9f0595-800x.jpg)

![Построение уравнений: этап 2hit(miss) piload(store) qi,diphys[1:0] = 0^2(свойства битовых строк)система уравнений (битовая и целочисленная арифметика)Hit](/img/tmb/2/100657/65ff38f0d576358f2297cb5757568c6b-800x.jpg)

![Публикации1. статья в «Программировании» [из списка ВАК] 2. статья в «Вычислительных методах и программировании»3-4. статьи](/img/tmb/2/100657/4ffed76f892ede903bf48238eed12f1a-800x.jpg)