markova@ssd.sscc.ru

Киреев Сергей Евгеньевич, kireev@ssd.sscc.ru

Перепелкин Владислав Александрович, perepelkin@ssd.sscc.ru

- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Организация ЭВМ и систем презентация

Содержание

- 1. Организация ЭВМ и систем

- 2. Определение архитектуры компьютера Архитектура компьютера – логическая

- 3. ENIAC (Electronic Numerical Integrator and Computer)

- 4. Архитектурные принципы компьютера фон Неймана Принцип программного

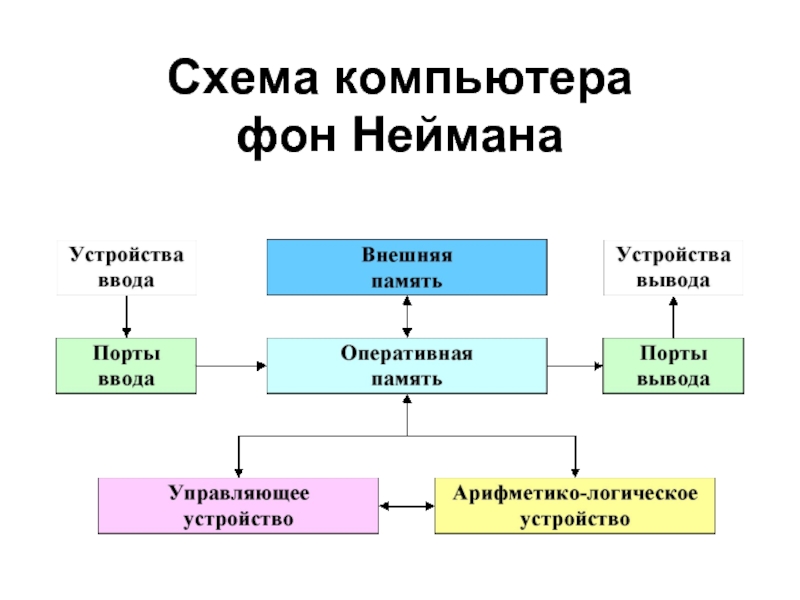

- 5. Схема компьютера фон Неймана

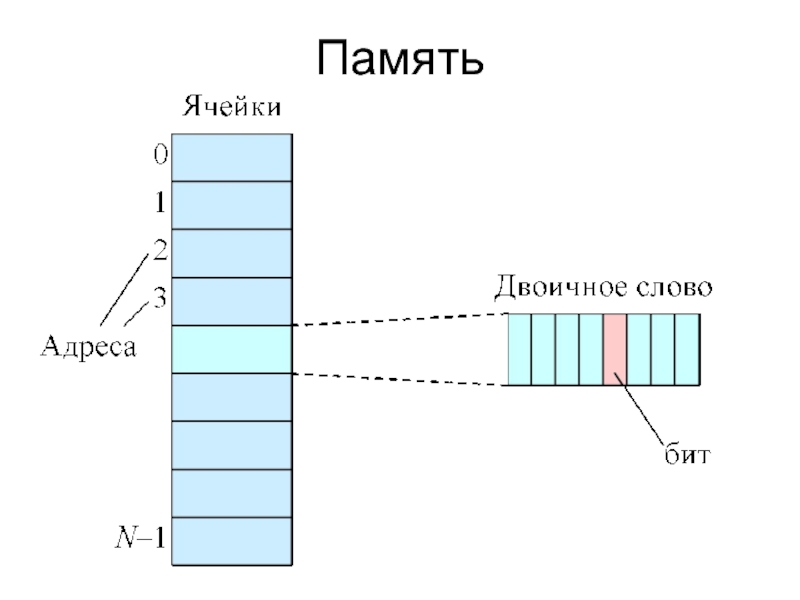

- 6. Память

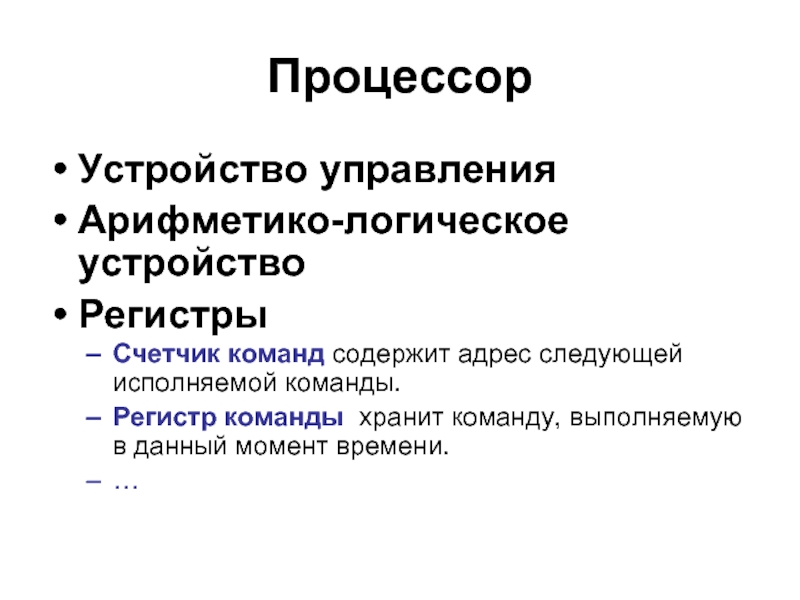

- 7. Процессор Устройство управления Арифметико-логическое устройство Регистры Счетчик

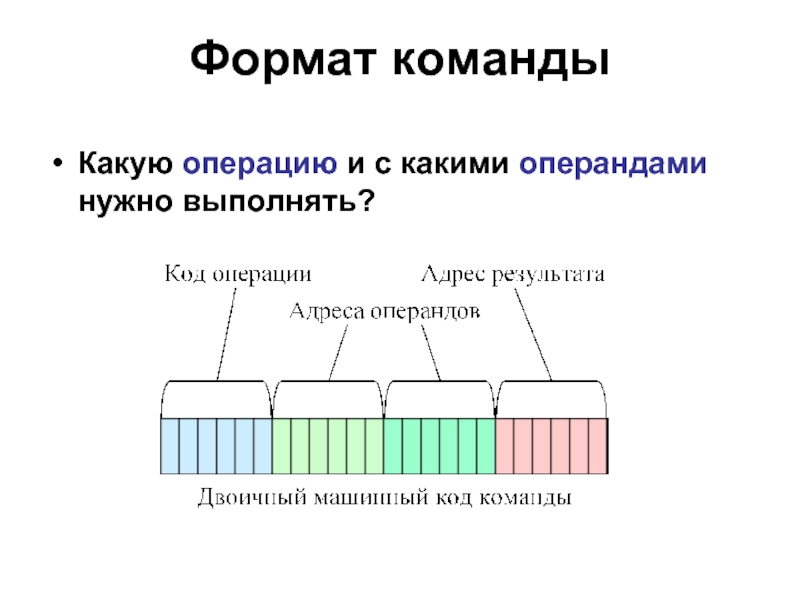

- 8. Формат команды Какую операцию и с какими операндами нужно выполнять?

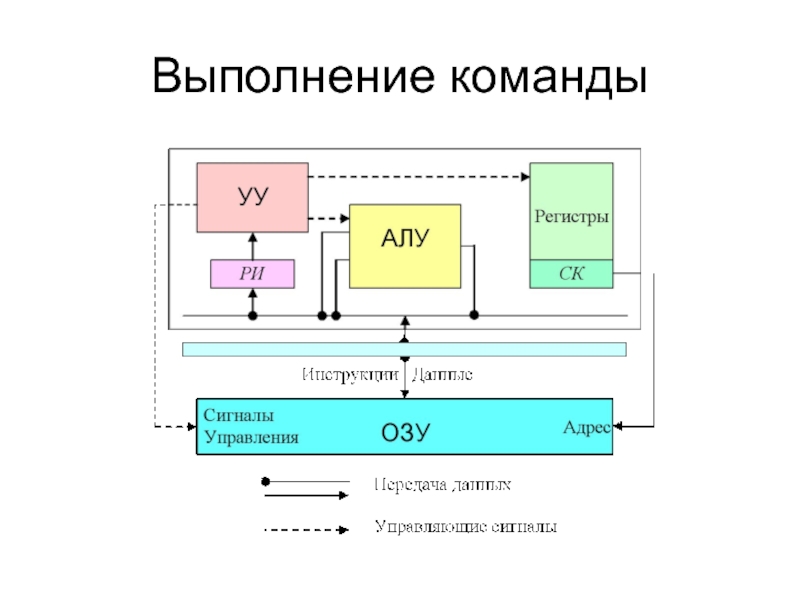

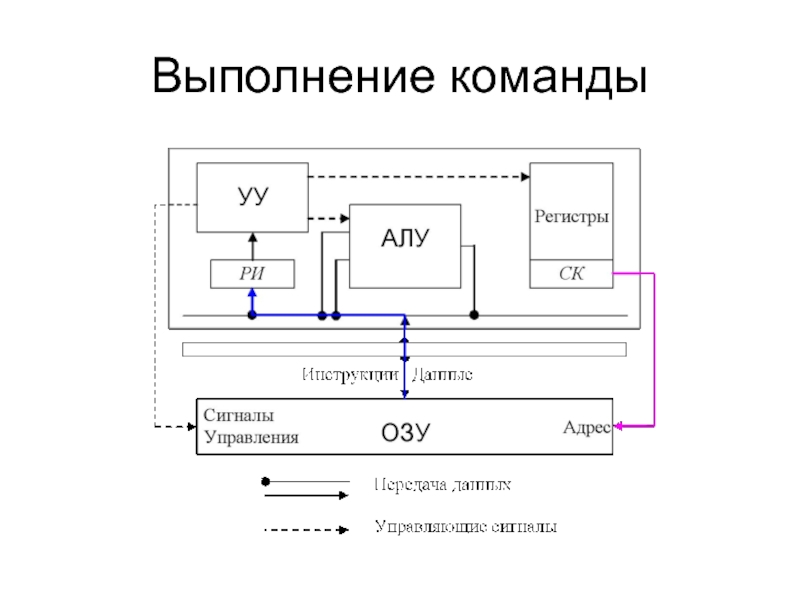

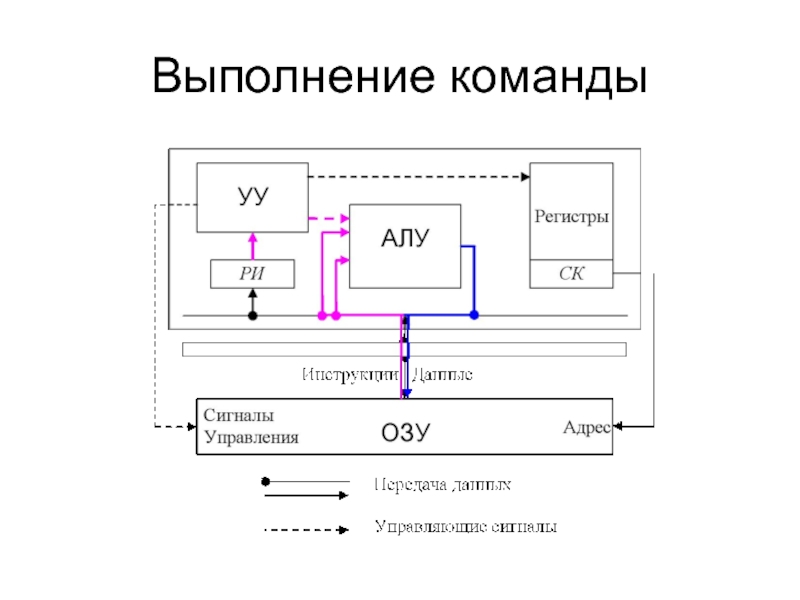

- 9. Выполнение команды

- 10. Выполнение команды

- 11. Выполнение команды

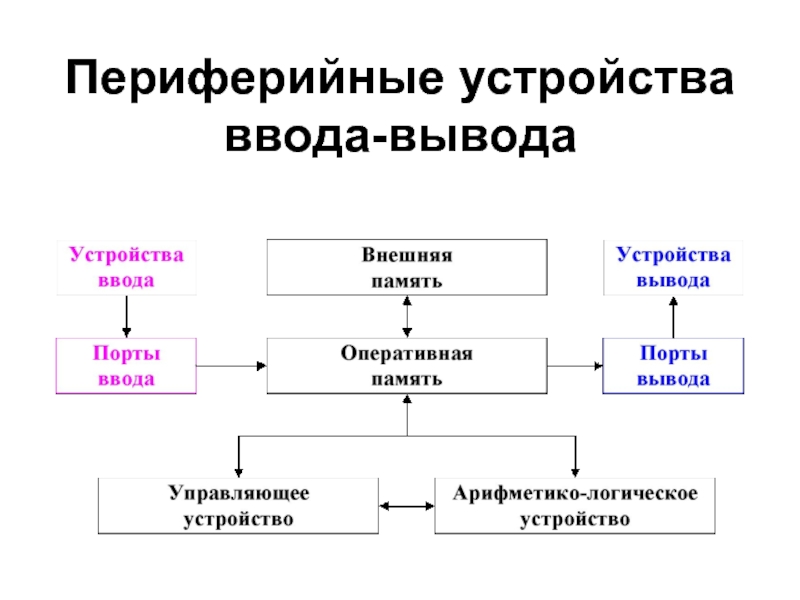

- 12. Периферийные устройства ввода-вывода

- 13. Машины потока команд

- 14. Управляющие стратегии вычислений Команда выполняется,

- 15. Узкие места архитектуры фон Неймана Последовательное выполнение

- 16. Такт работы процессора Время выполнения команды: Время доступа в память Время вычисления операции

- 17. 1951-53 гг. С. Лебедев, МЭСМ и БЭСМ 8-10 тыс. оп/сек

- 18. Усовершенствования архитектуры фон Неймана Усовершенствования в области

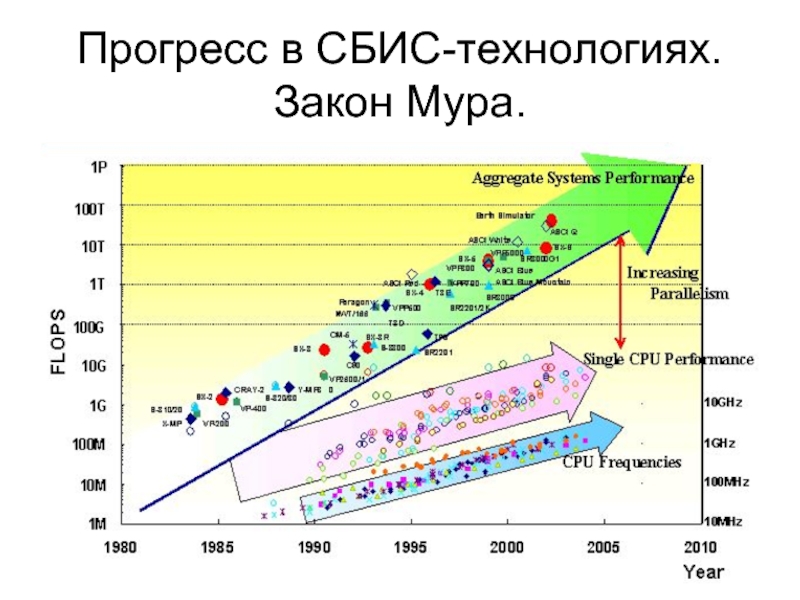

- 19. Прогресс в СБИС-технологиях. Закон Мура.

- 20. Усовершенствование ПО Языки программирования высокого уровня Компиляторы Библиотеки подпрограмм Параллельные языки программирования Коммуникационные библиотеки

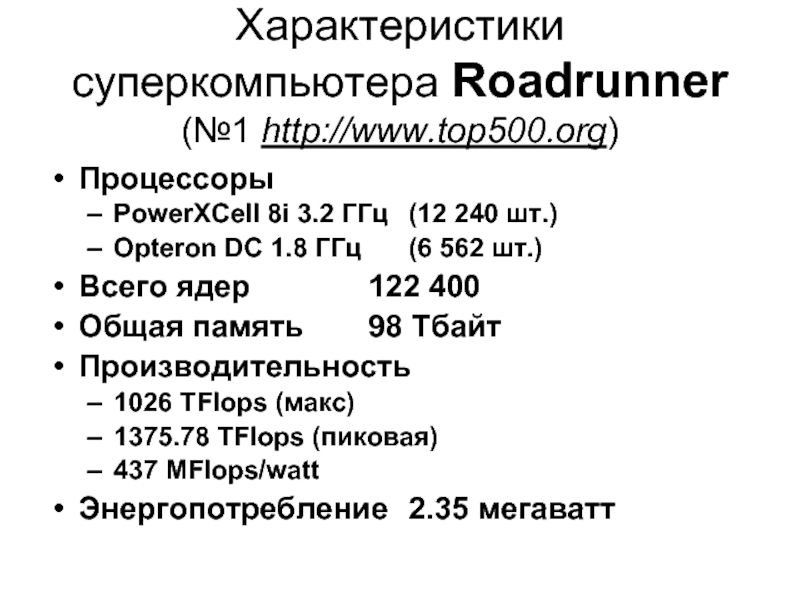

- 21. Характеристики суперкомпьютера Roadrunner (№1 http://www.top500.org) Процессоры PowerXCell

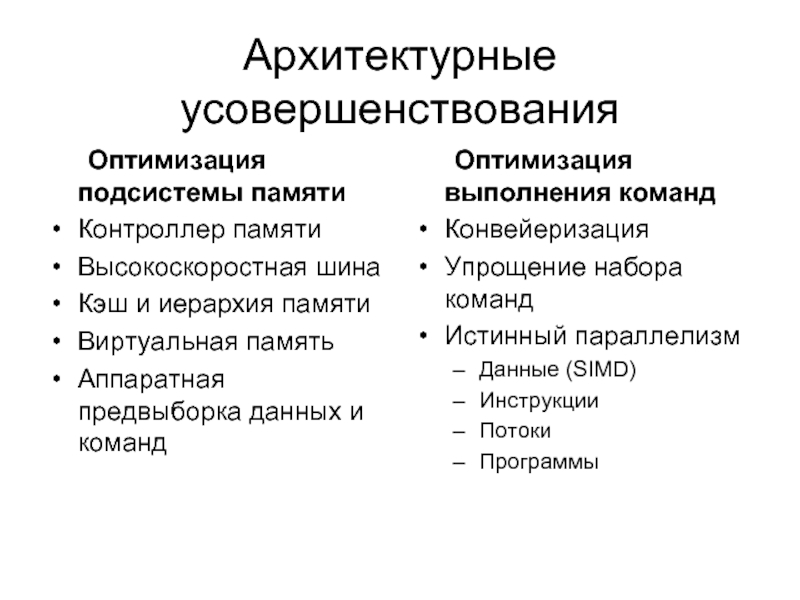

- 22. Архитектурные усовершенствования Оптимизация подсистемы памяти Контроллер памяти

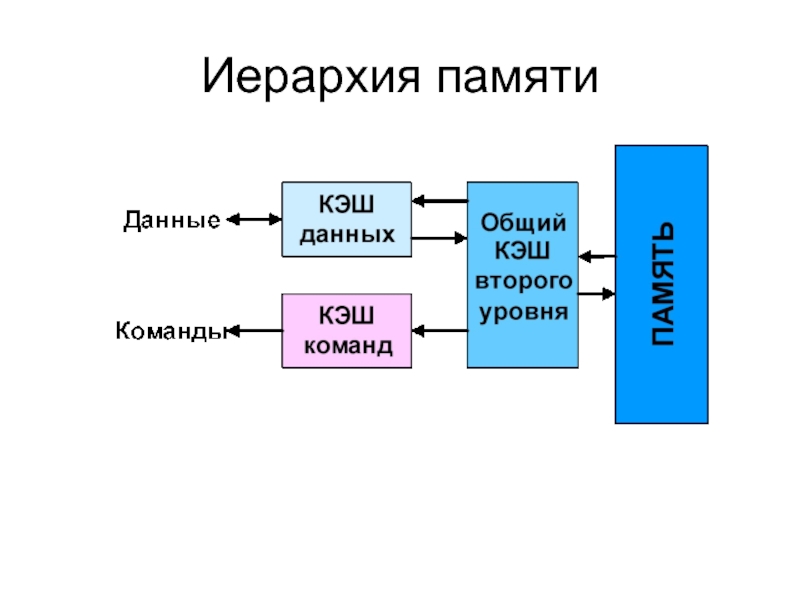

- 23. Иерархия памяти

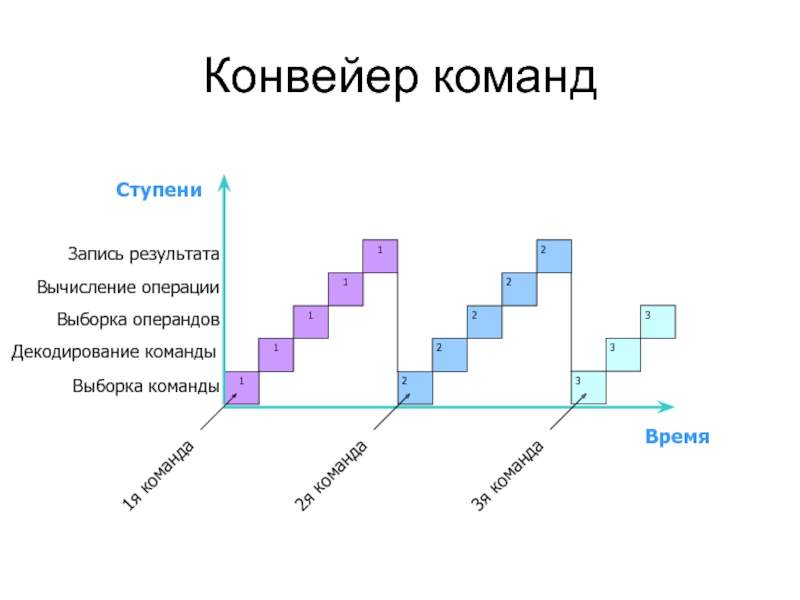

- 24. Конвейер команд 1 2 1 2 1

- 25. Конвейер команд 1 2 3 4 5

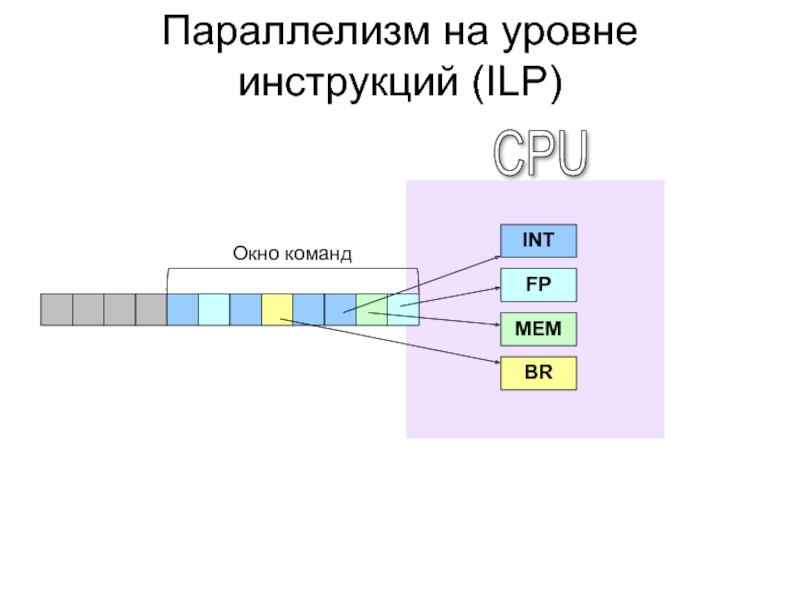

- 26. Параллелизм на уровне инструкций (ILP) INT

- 27. Параллелизм на уровне инструкций (ILP)

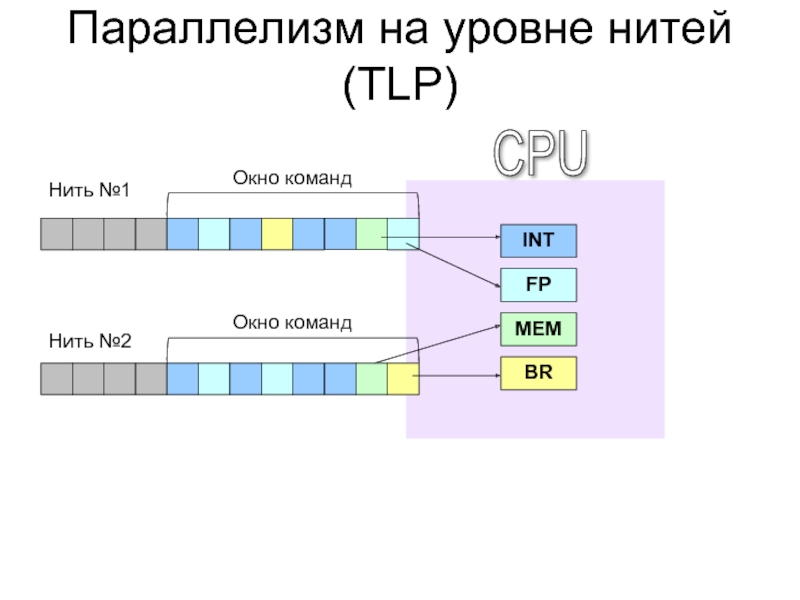

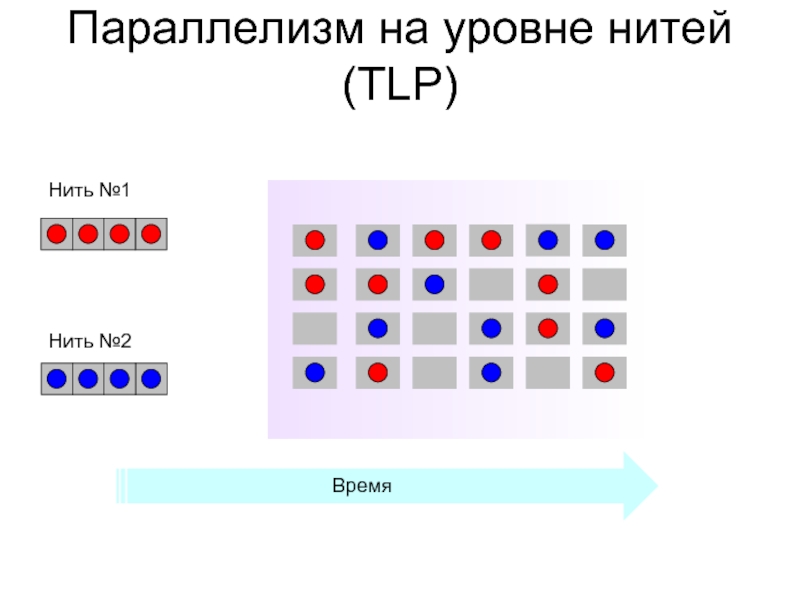

- 28. Параллелизм на уровне нитей (TLP) INT

- 29. Параллелизм на уровне нитей (TLP)

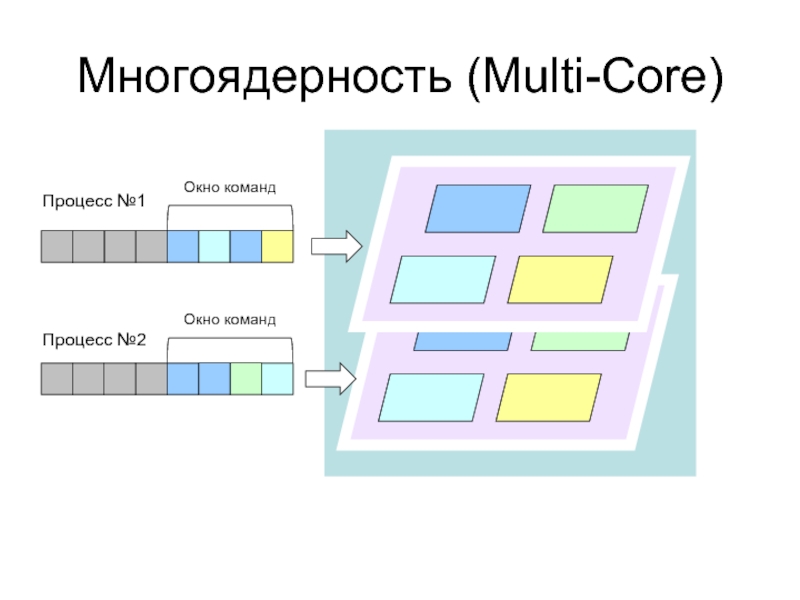

- 30. Многоядерность (Multi-Core)

- 31. Конец.

Слайд 2Определение архитектуры компьютера

Архитектура компьютера – логическая организация компьютера с точки зрения

программиста, (программно-видимые средства)

Intel Core, AMD x86-64, STI Cell, IBM POWER

Микроархитектура компьютера – совокупность аппаратных решений для серии процессоров, реализующих ее программную модель

IA-32 (Intel Architecture 32 bit) представлена двумя микроархитектурами:

P6 (Pentium Pro, Pentium II и Pentium III)

NetBurst (Celeron, Pentium 4, Xeon ,….)

Intel Core, AMD x86-64, STI Cell, IBM POWER

Микроархитектура компьютера – совокупность аппаратных решений для серии процессоров, реализующих ее программную модель

IA-32 (Intel Architecture 32 bit) представлена двумя микроархитектурами:

P6 (Pentium Pro, Pentium II и Pentium III)

NetBurst (Celeron, Pentium 4, Xeon ,….)

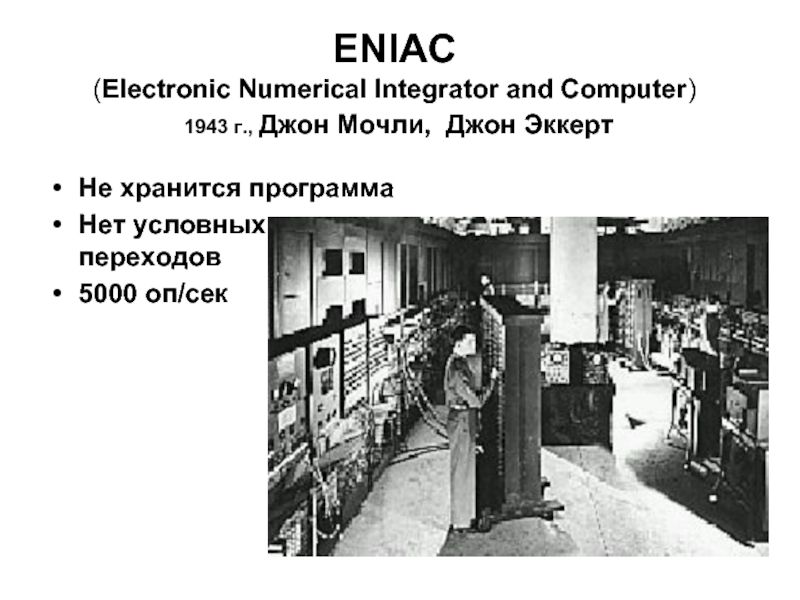

Слайд 3ENIAC

(Electronic Numerical Integrator and Computer)

1943 г., Джон Мочли, Джон Эккерт

Не

хранится программа

Нет условных переходов

5000 оп/сек

Нет условных переходов

5000 оп/сек

Слайд 4Архитектурные принципы компьютера фон Неймана

Принцип программного управления

Принцип хранимой программы

Синхронное функционирование

Принцип условного

перехода

Принцип использования двоичной системы счисления

Принцип иерархичности ЗУ

Принцип использования двоичной системы счисления

Принцип иерархичности ЗУ

Слайд 7Процессор

Устройство управления

Арифметико-логическое устройство

Регистры

Счетчик команд содержит адрес следующей исполняемой команды.

Регистр команды хранит

команду, выполняемую в данный момент времени.

…

…

Слайд 13Машины потока команд

Таким образом,

характерной чертой компьютеров фон Неймана является наличие глобально адресуемой памяти и счетчика команд, которые позволяют УУ многократно повторять один и тот же цикл действий:

извлечение очередной команды машинного кода,

декодирование и выполнение команды

в автоматическом режиме. В результате глобально адресуемая память и счетчик команд создают поток команд, которые УУ декодирует, а АЛУ исполняют.

извлечение очередной команды машинного кода,

декодирование и выполнение команды

в автоматическом режиме. В результате глобально адресуемая память и счетчик команд создают поток команд, которые УУ декодирует, а АЛУ исполняют.

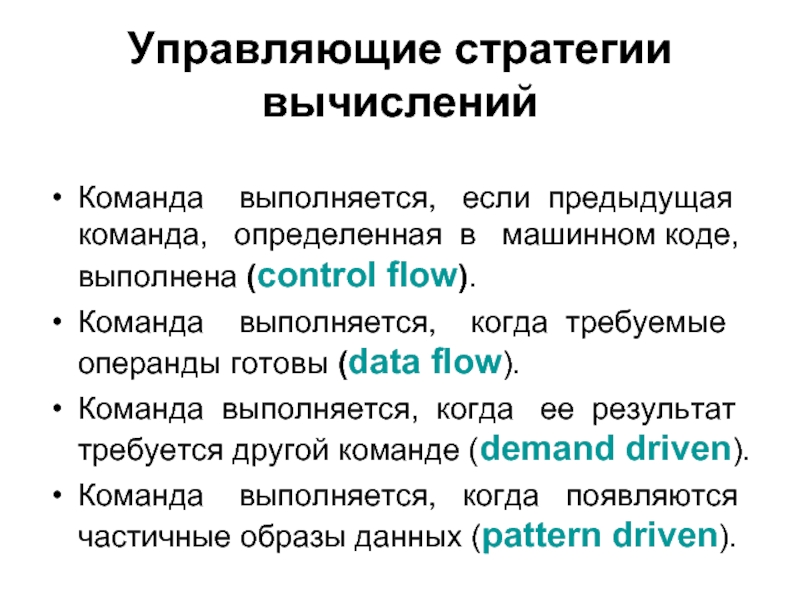

Слайд 14Управляющие стратегии вычислений

Команда выполняется, если предыдущая команда, определенная

в машинном коде, выполнена (control flow).

Команда выполняется, когда требуемые операнды готовы (data flow).

Команда выполняется, когда ее результат требуется другой команде (demand driven).

Команда выполняется, когда появляются частичные образы данных (pattern driven).

Команда выполняется, когда требуемые операнды готовы (data flow).

Команда выполняется, когда ее результат требуется другой команде (demand driven).

Команда выполняется, когда появляются частичные образы данных (pattern driven).

Слайд 15Узкие места архитектуры фон Неймана

Последовательное выполнение команд

Хранение данных и программы в

одном ОЗУ

Один канал связи

Один канал связи

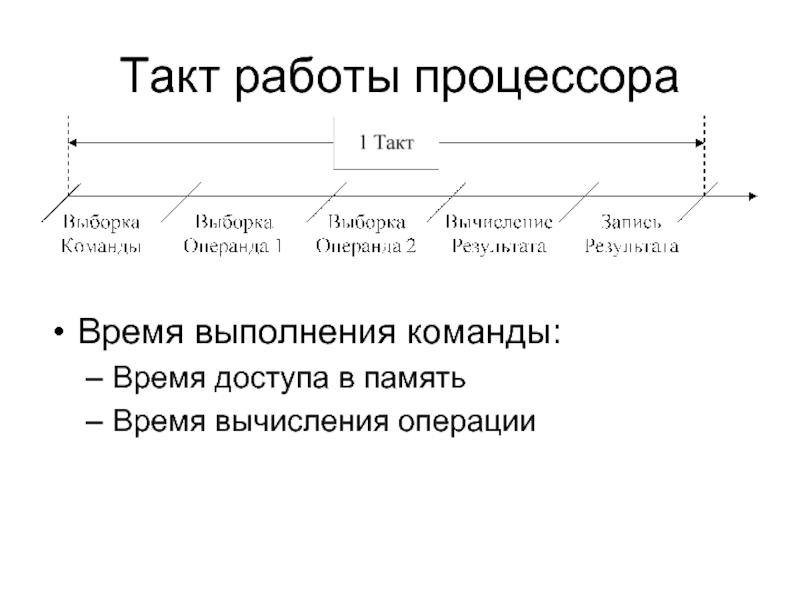

Слайд 16Такт работы процессора

Время выполнения команды:

Время доступа в память

Время вычисления операции

Слайд 18Усовершенствования архитектуры фон Неймана

Усовершенствования в области

CБИС-технологий.

Программного обеспечения.

Архитектурные

усовершенствования.

Слайд 20Усовершенствование ПО

Языки программирования

высокого уровня

Компиляторы

Библиотеки подпрограмм

Параллельные языки программирования

Коммуникационные библиотеки

Слайд 21Характеристики суперкомпьютера Roadrunner

(№1 http://www.top500.org)

Процессоры

PowerXCell 8i 3.2 ГГц (12 240 шт.)

Opteron DC 1.8

ГГц (6 562 шт.)

Всего ядер 122 400

Общая память 98 Тбайт

Производительность

1026 TFlops (макс)

1375.78 TFlops (пиковая)

437 MFlops/watt

Энергопотребление 2.35 мегаватт

Всего ядер 122 400

Общая память 98 Тбайт

Производительность

1026 TFlops (макс)

1375.78 TFlops (пиковая)

437 MFlops/watt

Энергопотребление 2.35 мегаватт

Слайд 22Архитектурные усовершенствования

Оптимизация подсистемы памяти

Контроллер памяти

Высокоскоростная шина

Кэш и иерархия памяти

Виртуальная память

Аппаратная предвыборка

данных и команд

Оптимизация выполнения команд

Конвейеризация

Упрощение набора команд

Истинный параллелизм

Данные (SIMD)

Инструкции

Потоки

Программы