- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Наноэлектроника: устройства, цепи, архитектура презентация

Содержание

- 1. Наноэлектроника: устройства, цепи, архитектура

- 2. OUTLINE 1. Microelectronics: Present

- 3. Из пещер к цифровому обществу

- 4. CMOS MEMORY AND PROCESSORS КМОП память и

- 5. SILICON MOSFET: THE CONCEPT Концепция полевого МОП

- 6. Современные полевые МОП транзисторы

- 7. CMOS LOGIC Inverter NAND gate CMOS cross-section FET notation: n-channel p-channel

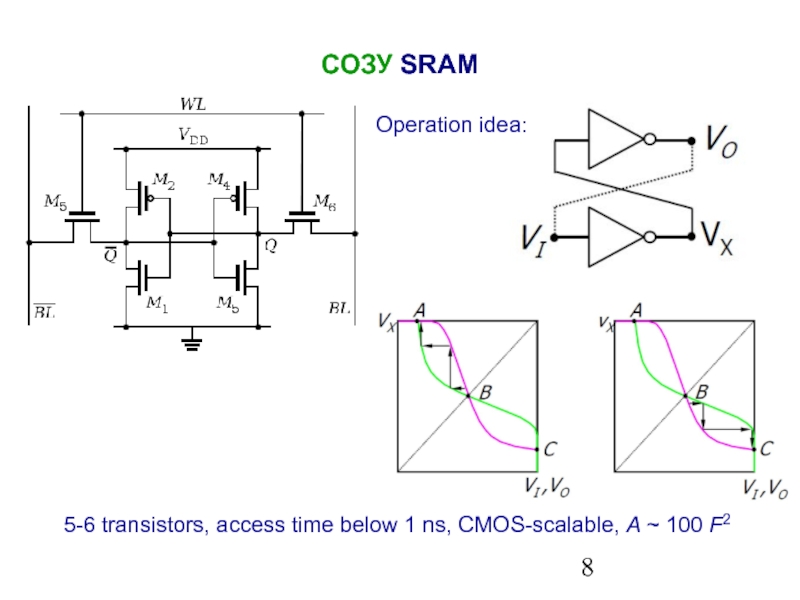

- 8. СОЗУ SRAM 5-6 transistors, access time below

- 9. ДОЗУ DRAM 1 transistor, access in 10s

- 10. NAND FLASH MEMORY: CELL Drain

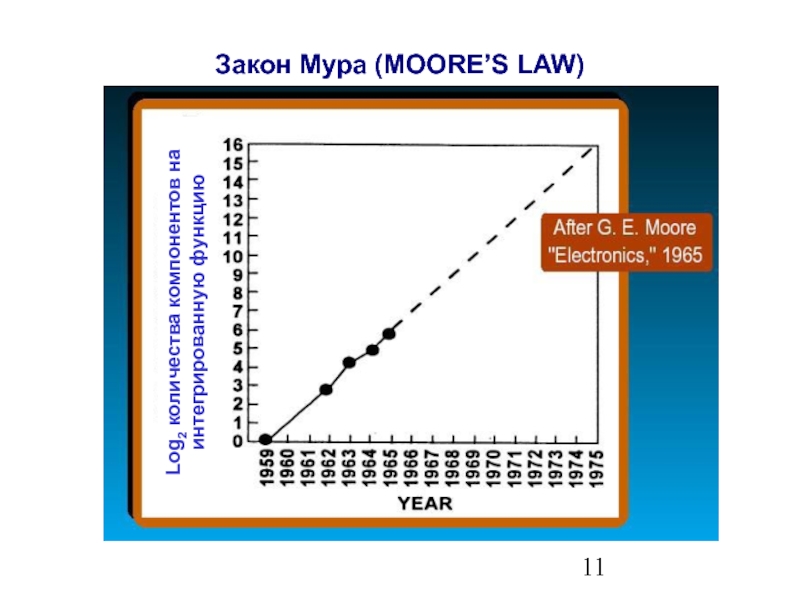

- 11. Закон Мура (MOORE’S LAW) Log2 количества компонентов на интегрированную функцию

- 12. Закон Мура для интегрированных схем Figure: Intel Сложность интегрированных схем

- 13. Закон Мура для минимального размера Технологический размер, мкм 0,5 шага ДОЗУ

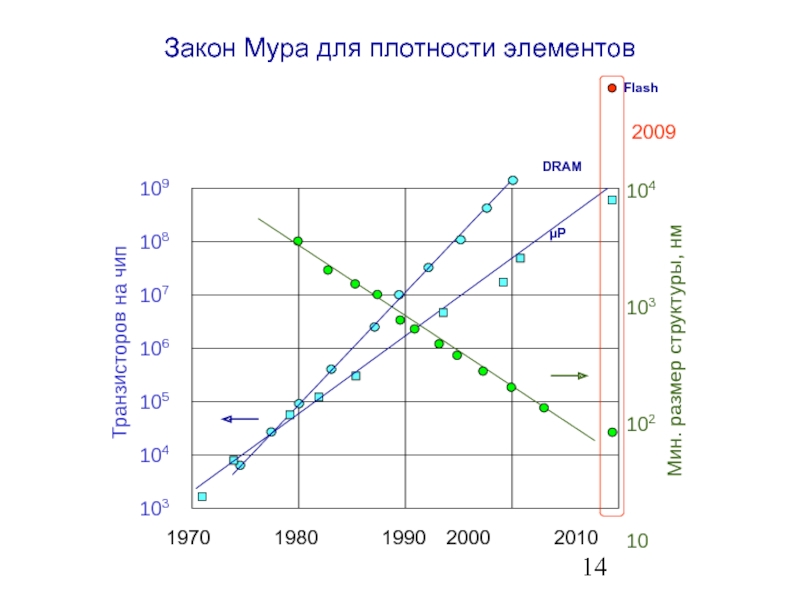

- 14. 1970 1980

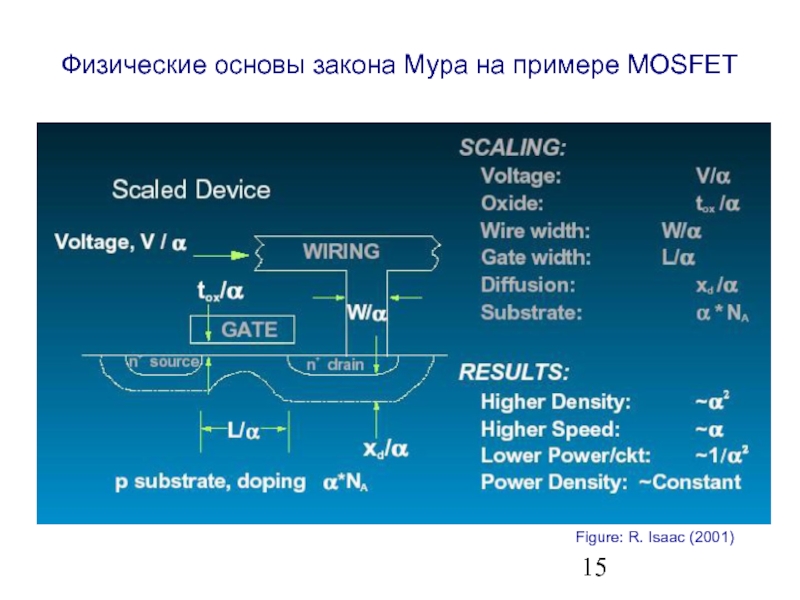

- 15. Физические основы закона Мура на примере MOSFET Figure: R. Isaac (2001)

- 16. Экономические основы закона Мура Стоимость микропроцессоров NAND

- 17. 1 THz

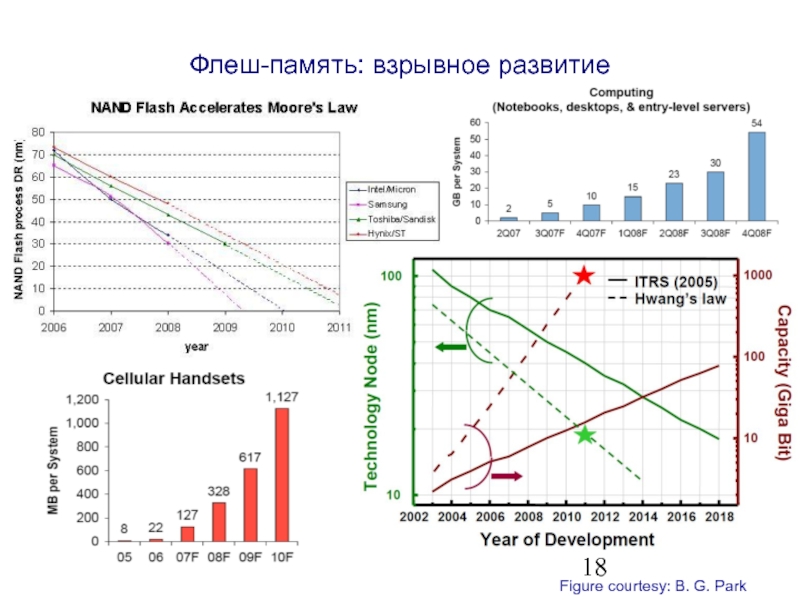

- 18. Флеш-память: взрывное развитие Figure courtesy: B. G. Park

- 19. Courtesy: U. Mastromatteo, STMicroelectronics MAGNETIC RECORDING

- 20. MAGNETIC RECORDING: AREAL DENSITY AS OF 2001

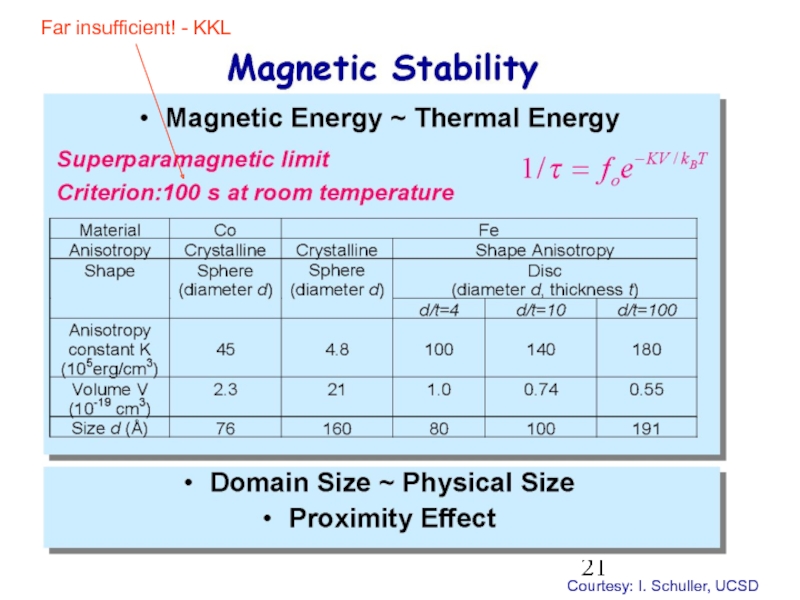

- 21. Courtesy: I. Schuller, UCSD Far insufficient! - KKL

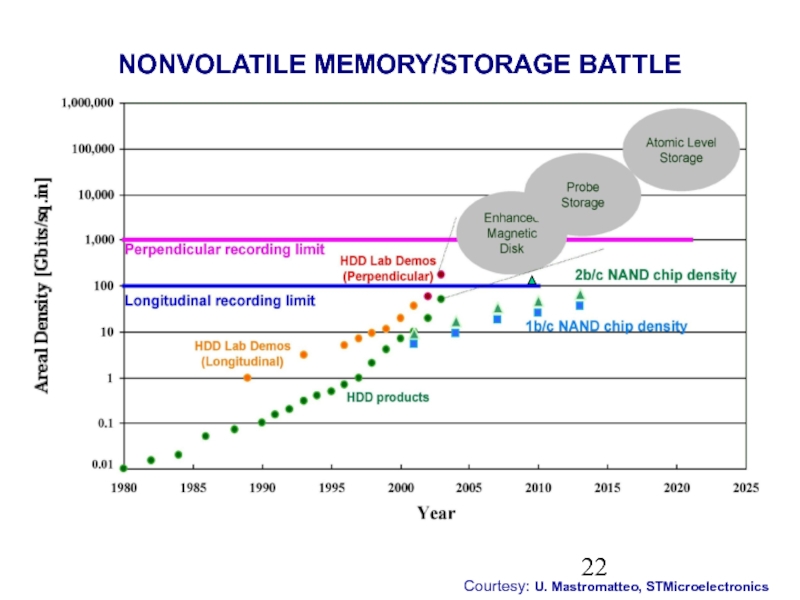

- 22. NONVOLATILE MEMORY/STORAGE BATTLE Courtesy: U. Mastromatteo, STMicroelectronics

Слайд 2

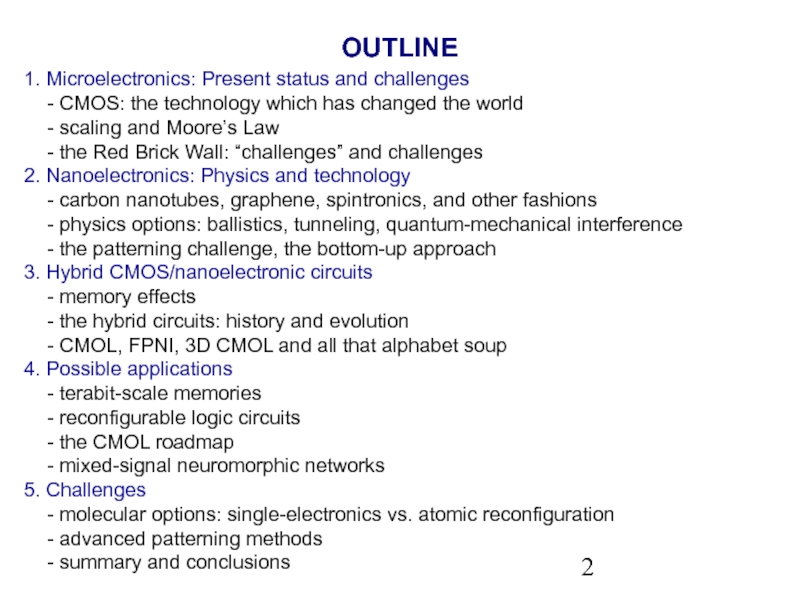

OUTLINE

1. Microelectronics: Present status and challenges

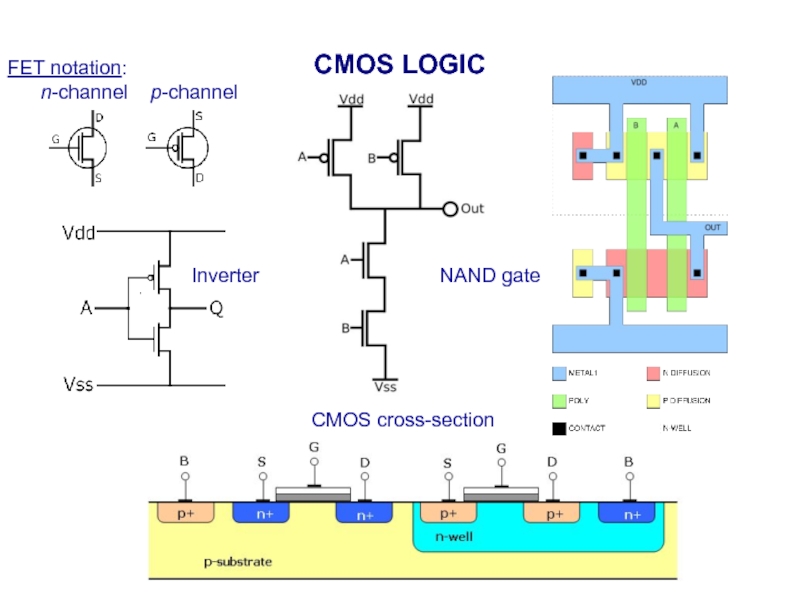

- CMOS: the technology

- scaling and Moore’s Law

- the Red Brick Wall: “challenges” and challenges

2. Nanoelectronics: Physics and technology

- carbon nanotubes, graphene, spintronics, and other fashions

- physics options: ballistics, tunneling, quantum-mechanical interference

- the patterning challenge, the bottom-up approach

3. Hybrid CMOS/nanoelectronic circuits

- memory effects

- the hybrid circuits: history and evolution

- CMOL, FPNI, 3D CMOL and all that alphabet soup

4. Possible applications

- terabit-scale memories

- reconfigurable logic circuits

- the CMOL roadmap

- mixed-signal neuromorphic networks

5. Challenges

- molecular options: single-electronics vs. atomic reconfiguration

- advanced patterning methods

- summary and conclusions

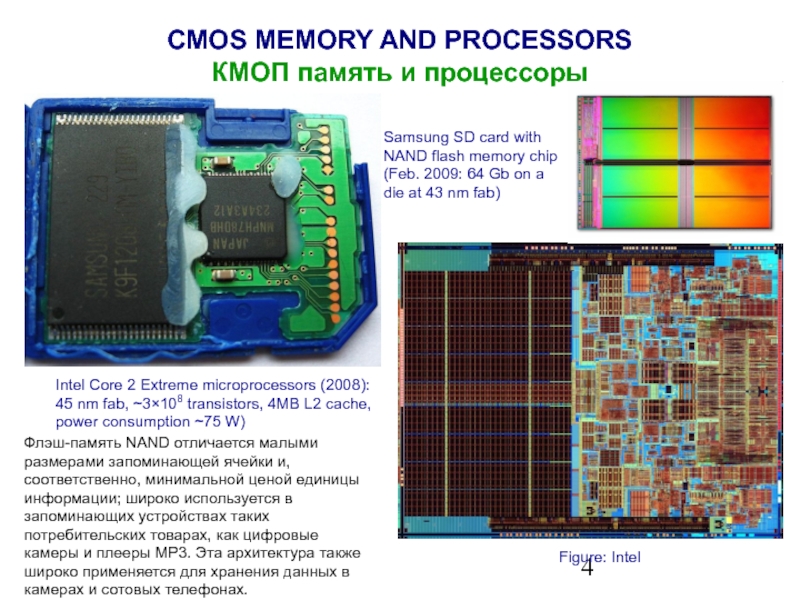

Слайд 4CMOS MEMORY AND PROCESSORS

КМОП память и процессоры

Intel Core 2 Extreme microprocessors

Samsung SD card with NAND flash memory chip (Feb. 2009: 64 Gb on a die at 43 nm fab)

Figure: Intel

Флэш-память NAND отличается малыми размерами запоминающей ячейки и, соответственно, минимальной ценой единицы информации; широко используется в запоминающих устройствах таких потребительских товарах, как цифровые камеры и плееры MP3. Эта архитектура также широко применяется для хранения данных в камерах и сотовых телефонах.

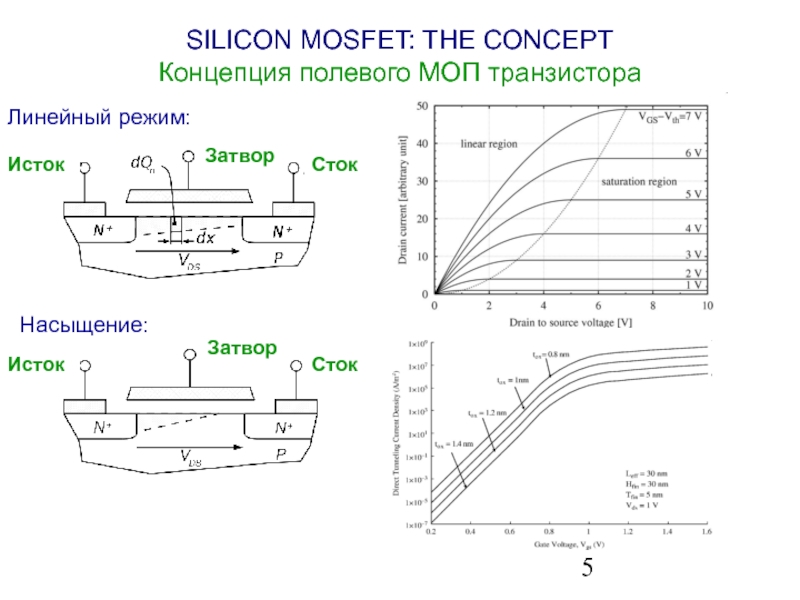

Слайд 5SILICON MOSFET: THE CONCEPT

Концепция полевого МОП транзистора

Линейный режим:

Насыщение:

Исток

Исток

Сток

Сток

Затвор

Затвор

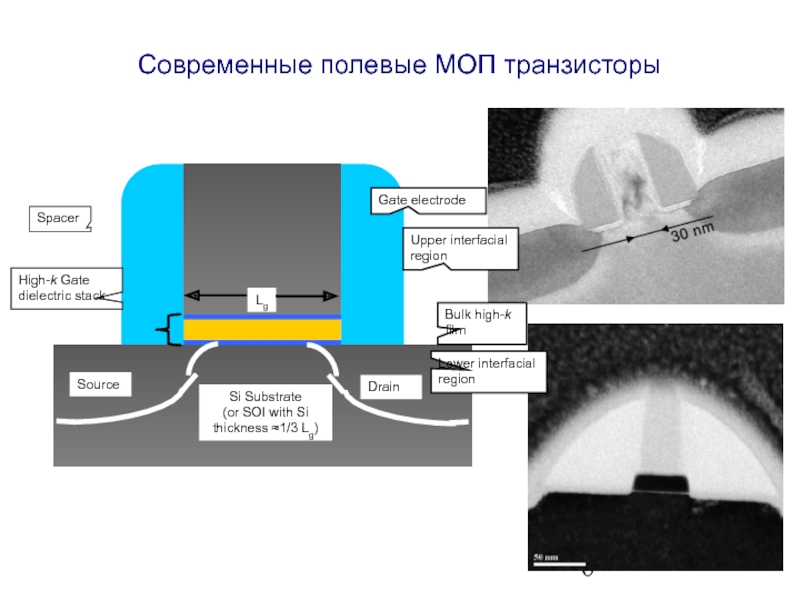

Слайд 6Современные полевые МОП транзисторы

Upper interfacial region

Bulk high-k film

Lower interfacial region

Gate electrode

Si

Source

Drain

Spacer

High-k Gate dielectric stack

Lg

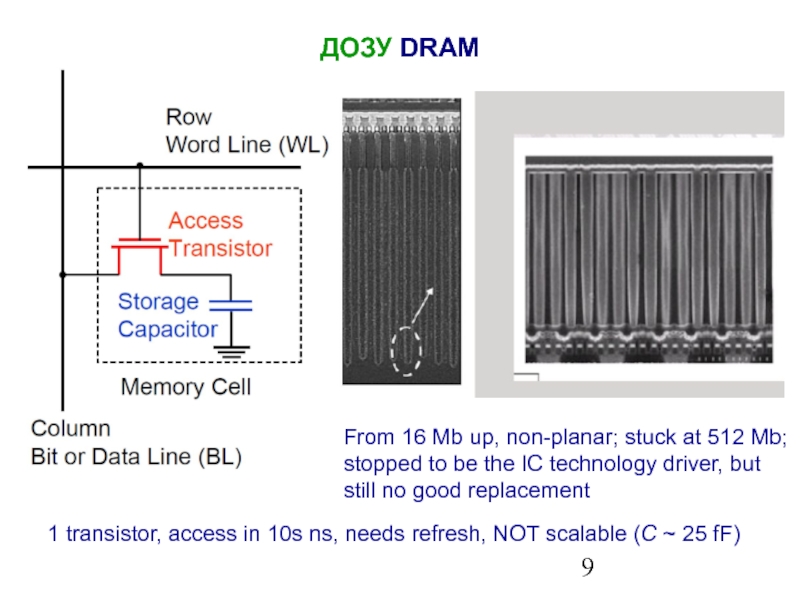

Слайд 9ДОЗУ DRAM

1 transistor, access in 10s ns, needs refresh, NOT scalable

From 16 Mb up, non-planar; stuck at 512 Mb;

stopped to be the IC technology driver, but still no good replacement

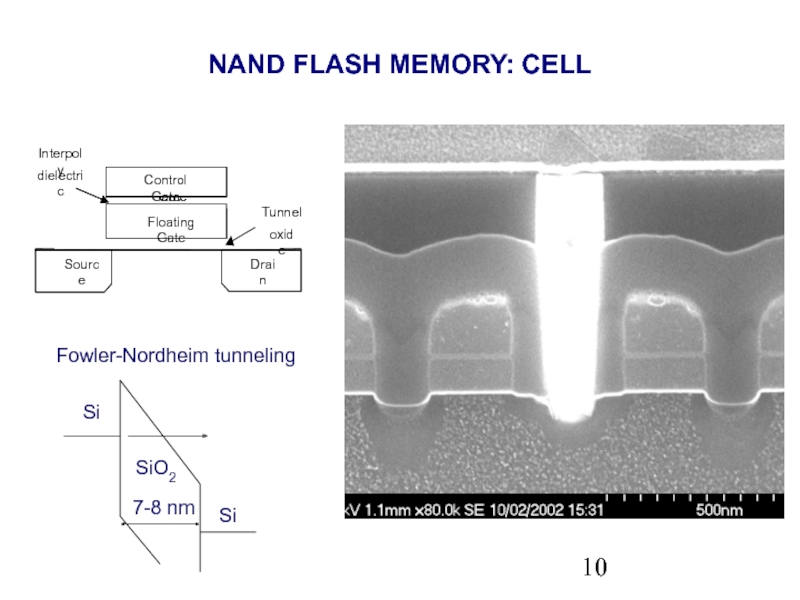

Слайд 10NAND FLASH MEMORY: CELL

Drain

Source

Control Gate

Interpoly

Drain

Source

Control Gate

Drain

Source

Floating Gate

Control Gate

dielectric

Tunnel

oxide

Fowler-Nordheim tunneling

Si

Si

SiO2

7-8 nm

Слайд 141970 1980 1990

Закон Мура для плотности элементов

Транзисторов на чип

109

108

107

106

105

104

103

Мин. размер структуры, нм

104

103

102

10

DRAM

μP

Flash

2009

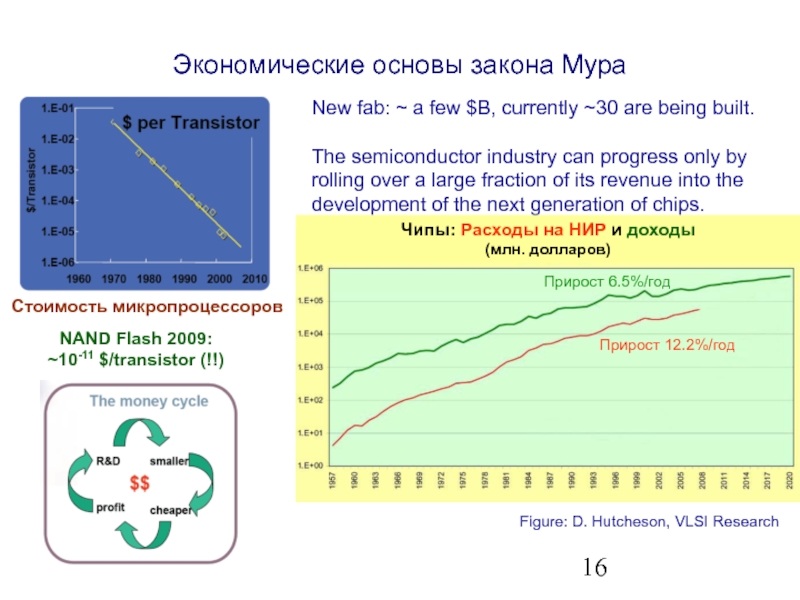

Слайд 16Экономические основы закона Мура

Стоимость микропроцессоров

NAND Flash 2009:

~10-11 $/transistor (!!)

Figure: D.

Прирост 6.5%/год

Прирост 12.2%/год

New fab: ~ a few $B, currently ~30 are being built.

The semiconductor industry can progress only by rolling over a large fraction of its revenue into the development of the next generation of chips.

Чипы: Расходы на НИР и доходы

(млн. долларов)

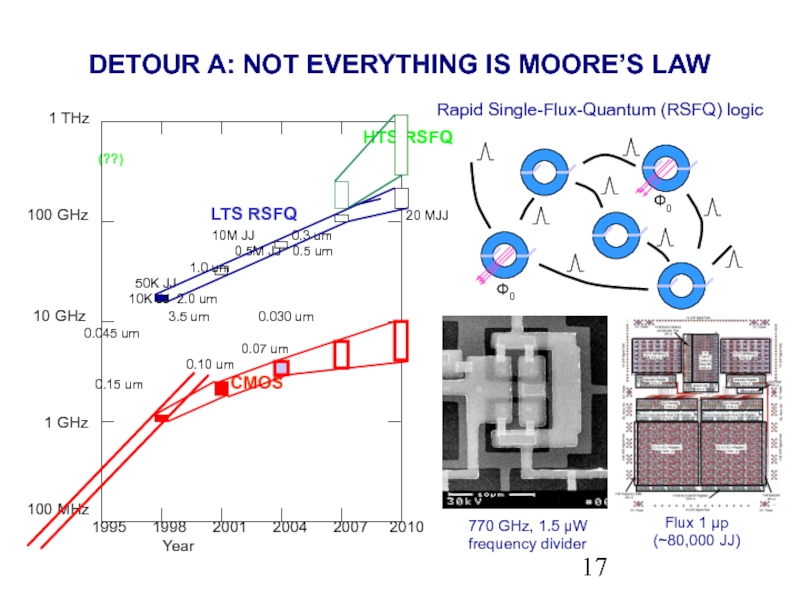

Слайд 17 1 THz

HTS RSFQ (??)

100 GHz LTS RSFQ 20 MJJ

10M JJ 0.3 um

0.5M JJ 0.5 um

1.0 um

50K JJ

10K JJ 2.0 um

10 GHz 3.5 um 0.030 um 0.045 um

0.07 um

0.10 um

0.15 um CMOS

1 GHz

100 MHz

1995 1998 2001 2004 2007 2010

Year

DETOUR A: NOT EVERYTHING IS MOORE’S LAW

Rapid Single-Flux-Quantum (RSFQ) logic

770 GHz, 1.5 μW frequency divider

Flux 1 μp (~80,000 JJ)

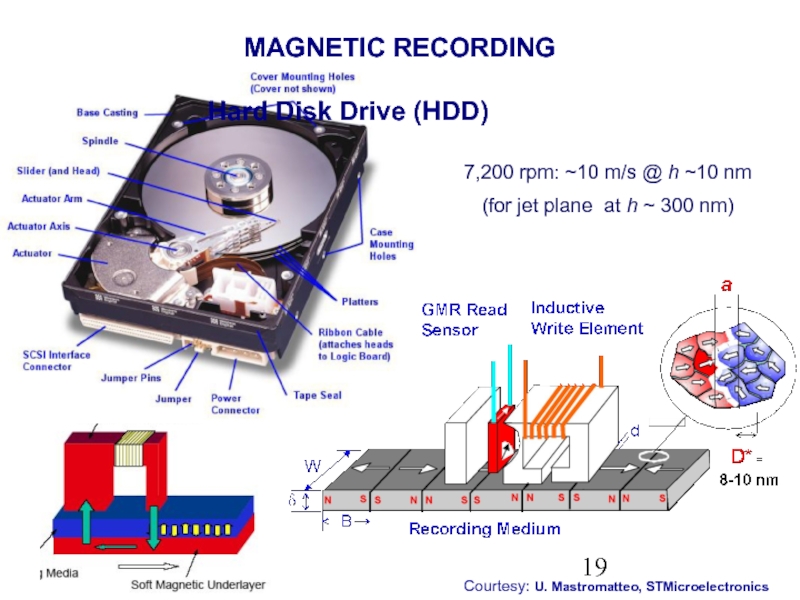

Слайд 19Courtesy: U. Mastromatteo, STMicroelectronics

MAGNETIC RECORDING

Hard Disk Drive (HDD)

7,200 rpm: ~10 m/s

(for jet plane at h ~ 300 nm)