- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Характеристики ядра процессора презентация

Содержание

- 1. Характеристики ядра процессора

- 2. Конвейер Конвейер(ы) Глубина Время «доступности» регистра «Цена» условного перехода Количество конвейеров

- 3. Память Шины памяти Количество шин (Шина

- 4. Набор инструкций Работы с памятью Режимы адресации

- 5. Набор инструкций Логические Инструкции сдвига Логический:

- 6. Набор инструкций Инструкции перехода, условное выполнение Условный

- 7. Приёмы оптимизации Подготовка кода Компиляция под архитектуру

- 8. Приёмы оптимизации Разворачивание циклов for(i=0;i

- 9. Спасибо за внимание!!!

Слайд 1Характеристики ядра процессора

Регистры

Количество

Типы регистров

Общего назначения

Адресные

Регистры флагов

Вычислительные устройства

ALU: Fixed-point и Floating-point

Умножители

Адресное АЛУ (TI C54: MAC *AR2+,*AR3+,A)

Устройство сдвига (shifter)

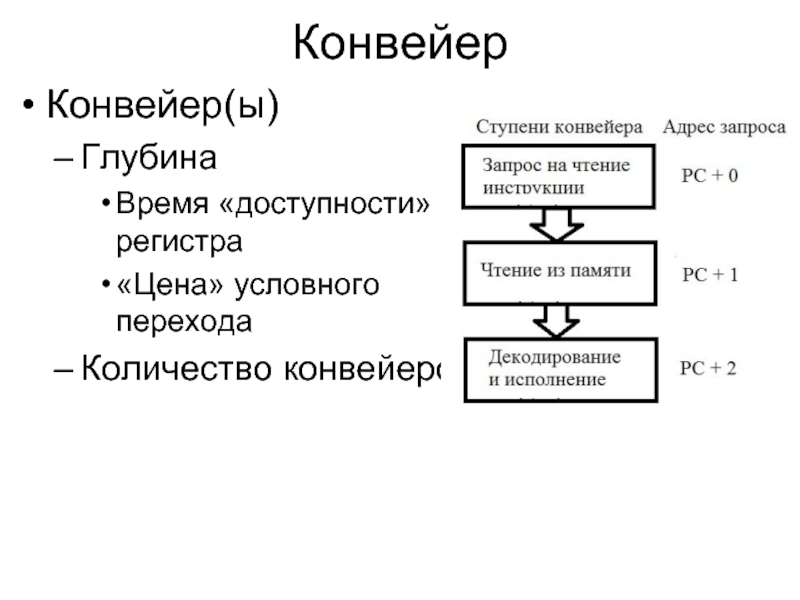

Слайд 2Конвейер

Конвейер(ы)

Глубина

Время «доступности» регистра

«Цена» условного перехода

Количество конвейеров

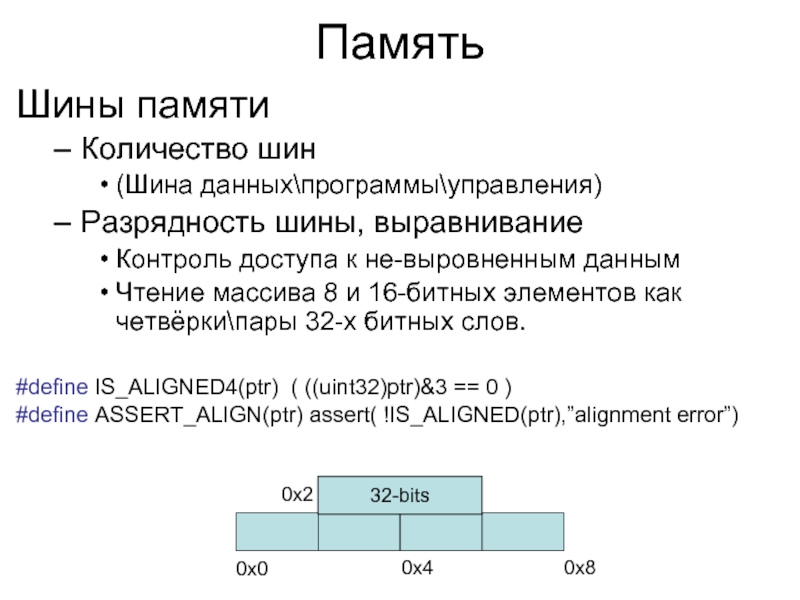

Слайд 3Память

Шины памяти

Количество шин

(Шина данных\программы\управления)

Разрядность шины, выравнивание

Контроль доступа к не-выровненным данным

Чтение

массива 8 и 16-битных элементов как четвёрки\пары 32-х битных слов.

#define IS_ALIGNED4(ptr) ( ((uint32)ptr)&3 == 0 )

#define ASSERT_ALIGN(ptr) assert( !IS_ALIGNED(ptr),”alignment error”)

#define IS_ALIGNED4(ptr) ( ((uint32)ptr)&3 == 0 )

#define ASSERT_ALIGN(ptr) assert( !IS_ALIGNED(ptr),”alignment error”)

0x0

0x4

0x8

32-bits

0x2

Слайд 4Набор инструкций

Работы с памятью

Режимы адресации

Абсолютное значение

Значение из регистра

Регистр + абсолютное значение

Автоинкремент\автодекремент

Циклический

автоинкремент\автодекремент

Множественная загрузка: ARM

LDMIA r8!, {r0-r7} – загрузка регистров r0-r7

Эффективное использование регистров

Язык C: Переменные типа register.

Арифметические

«Сложные» инструкции

MAC – multiply + accumulate

ARM: сдвиг + арифметическая инструкция

ADD r0, r2, r1 LSL #16 ; сложение с R1, умноженным на 65537

ADD r0, r0,r1 ;

Множественная загрузка: ARM

LDMIA r8!, {r0-r7} – загрузка регистров r0-r7

Эффективное использование регистров

Язык C: Переменные типа register.

Арифметические

«Сложные» инструкции

MAC – multiply + accumulate

ARM: сдвиг + арифметическая инструкция

ADD r0, r2, r1 LSL #16 ; сложение с R1, умноженным на 65537

ADD r0, r0,r1 ;

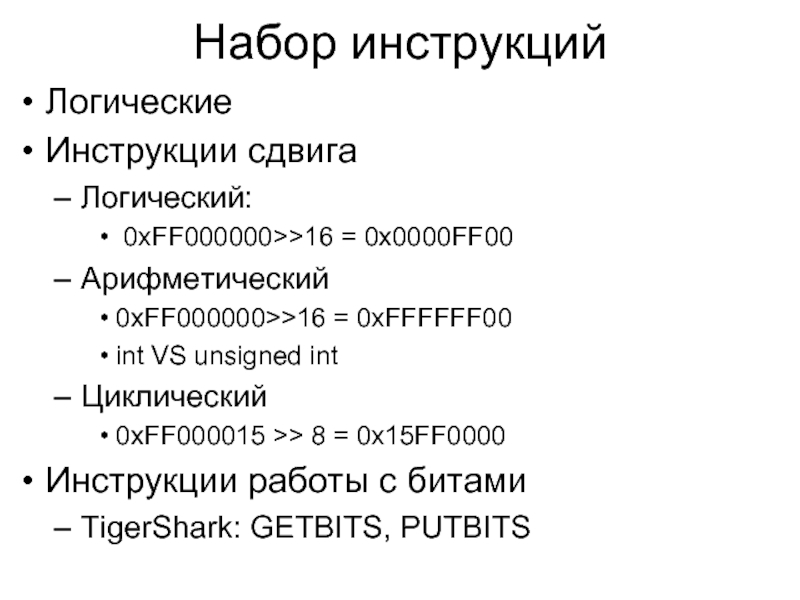

Слайд 5Набор инструкций

Логические

Инструкции сдвига

Логический:

0xFF000000>>16 = 0x0000FF00

Арифметический

0xFF000000>>16 = 0xFFFFFF00

int VS unsigned

int

Циклический

0xFF000015 >> 8 = 0x15FF0000

Инструкции работы с битами

TigerShark: GETBITS, PUTBITS

Циклический

0xFF000015 >> 8 = 0x15FF0000

Инструкции работы с битами

TigerShark: GETBITS, PUTBITS

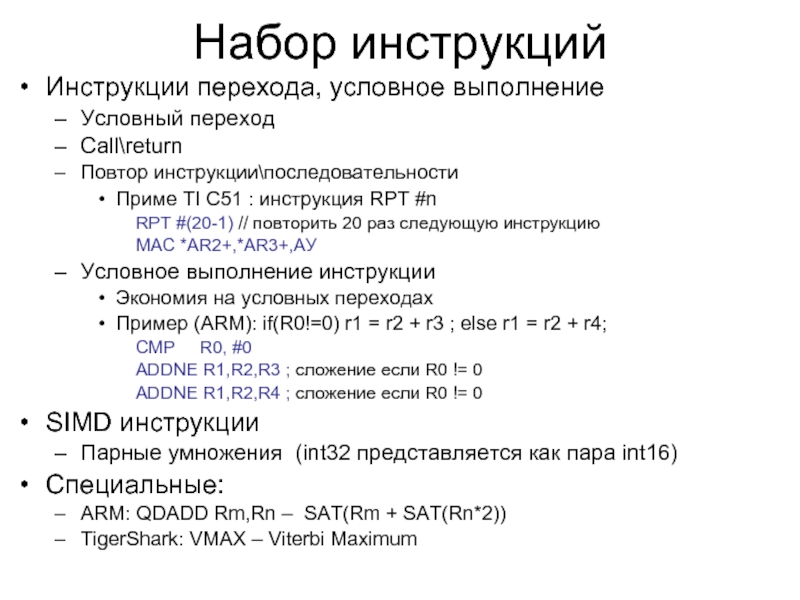

Слайд 6Набор инструкций

Инструкции перехода, условное выполнение

Условный переход

Call\return

Повтор инструкции\последовательности

Приме TI C51 : инструкция

RPT #n

RPT #(20-1) // повторить 20 раз следующую инструкцию

MAC *AR2+,*AR3+,AУ

Условное выполнение инструкции

Экономия на условных переходах

Пример (ARM): if(R0!=0) r1 = r2 + r3 ; else r1 = r2 + r4;

CMP R0, #0

ADDNE R1,R2,R3 ; сложение если R0 != 0

ADDNE R1,R2,R4 ; сложение если R0 != 0

SIMD инструкции

Парные умножения (int32 представляется как пара int16)

Специальные:

ARM: QDADD Rm,Rn – SAT(Rm + SAT(Rn*2))

TigerShark: VMAX – Viterbi Maximum

RPT #(20-1) // повторить 20 раз следующую инструкцию

MAC *AR2+,*AR3+,AУ

Условное выполнение инструкции

Экономия на условных переходах

Пример (ARM): if(R0!=0) r1 = r2 + r3 ; else r1 = r2 + r4;

CMP R0, #0

ADDNE R1,R2,R3 ; сложение если R0 != 0

ADDNE R1,R2,R4 ; сложение если R0 != 0

SIMD инструкции

Парные умножения (int32 представляется как пара int16)

Специальные:

ARM: QDADD Rm,Rn – SAT(Rm + SAT(Rn*2))

TigerShark: VMAX – Viterbi Maximum

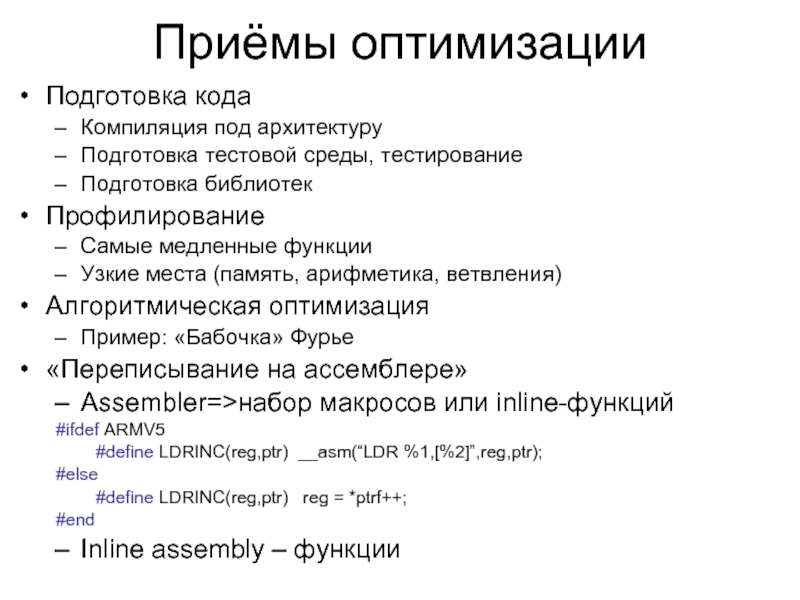

Слайд 7Приёмы оптимизации

Подготовка кода

Компиляция под архитектуру

Подготовка тестовой среды, тестирование

Подготовка библиотек

Профилирование

Самые медленные функции

Узкие

места (память, арифметика, ветвления)

Алгоритмическая оптимизация

Пример: «Бабочка» Фурье

«Переписывание на ассемблере»

Assembler=>набор макросов или inline-функций

#ifdef ARMV5

#define LDRINC(reg,ptr) __asm(“LDR %1,[%2]”,reg,ptr);

#else

#define LDRINC(reg,ptr) reg = *ptrf++;

#end

Inline assembly – функции

Алгоритмическая оптимизация

Пример: «Бабочка» Фурье

«Переписывание на ассемблере»

Assembler=>набор макросов или inline-функций

#ifdef ARMV5

#define LDRINC(reg,ptr) __asm(“LDR %1,[%2]”,reg,ptr);

#else

#define LDRINC(reg,ptr) reg = *ptrf++;

#end

Inline assembly – функции

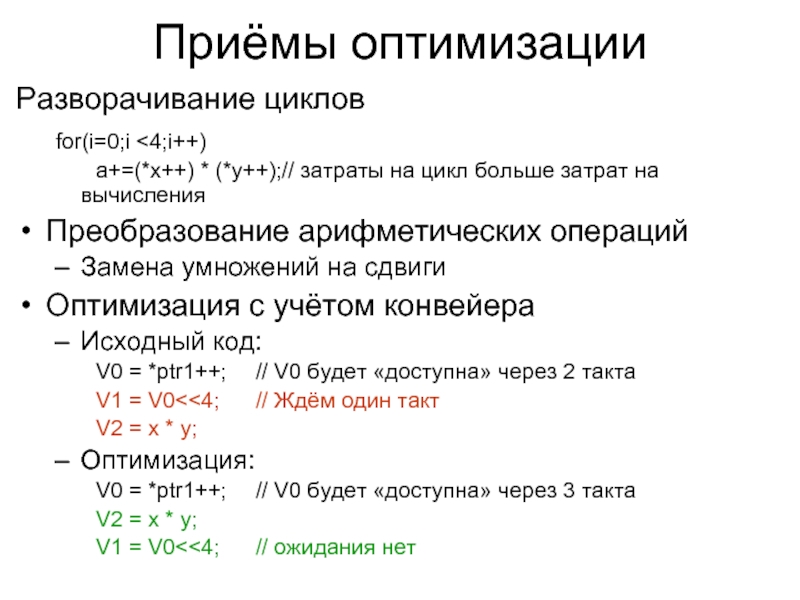

Слайд 8Приёмы оптимизации

Разворачивание циклов

for(i=0;i

затрат на вычисления

Преобразование арифметических операций

Замена умножений на сдвиги

Оптимизация с учётом конвейера

Исходный код:

V0 = *ptr1++; // V0 будет «доступна» через 2 такта

V1 = V0<<4; // Ждём один такт

V2 = x * y;

Оптимизация:

V0 = *ptr1++; // V0 будет «доступна» через 3 такта

V2 = x * y;

V1 = V0<<4; // ожидания нет

Преобразование арифметических операций

Замена умножений на сдвиги

Оптимизация с учётом конвейера

Исходный код:

V0 = *ptr1++; // V0 будет «доступна» через 2 такта

V1 = V0<<4; // Ждём один такт

V2 = x * y;

Оптимизация:

V0 = *ptr1++; // V0 будет «доступна» через 3 такта

V2 = x * y;

V1 = V0<<4; // ожидания нет