- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Архитектура набора команд презентация

Содержание

- 1. Архитектура набора команд

- 2. Размер команды Фиксированный переменный

- 3. Структура команды Битовые поля: Адреса операндов Код команды Уточнения типа операции Методы адресации Размер операндов

- 4. Ассемблер Автокодовый язык Взаимно-однозначное соответствие команды процессора и записи на языке ассемблера Макровозможности ассемблера

- 5. Регистры pdp11 Общего назначения: R0 R1

- 6. Служебные регистры SP (KSP, SSP, USP) PC PSW

- 7. Структура команды Двухадресная Р КОП М1

- 8. Методы адресации 0 регистровый 1 регистровый косвенный

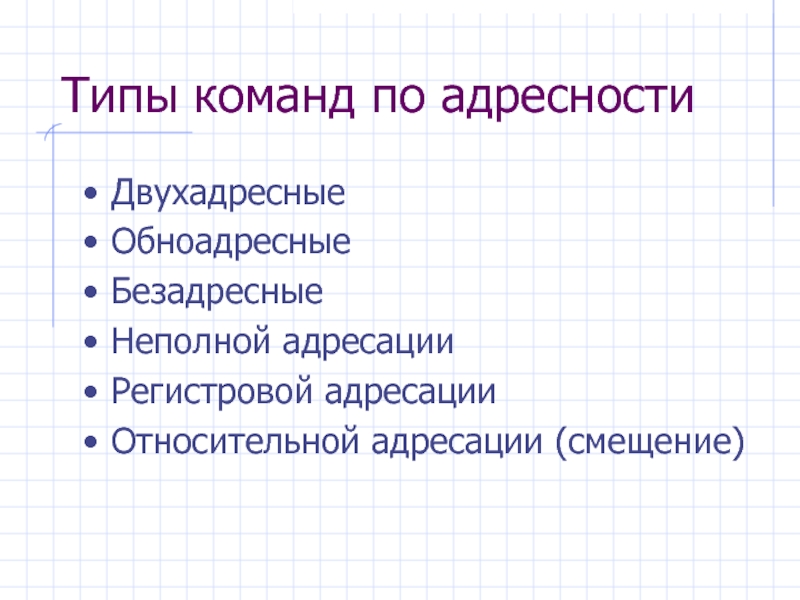

- 9. Типы команд по адресности Двухадресные Обноадресные Безадресные Неполной адресации Регистровой адресации Относительной адресации (смещение)

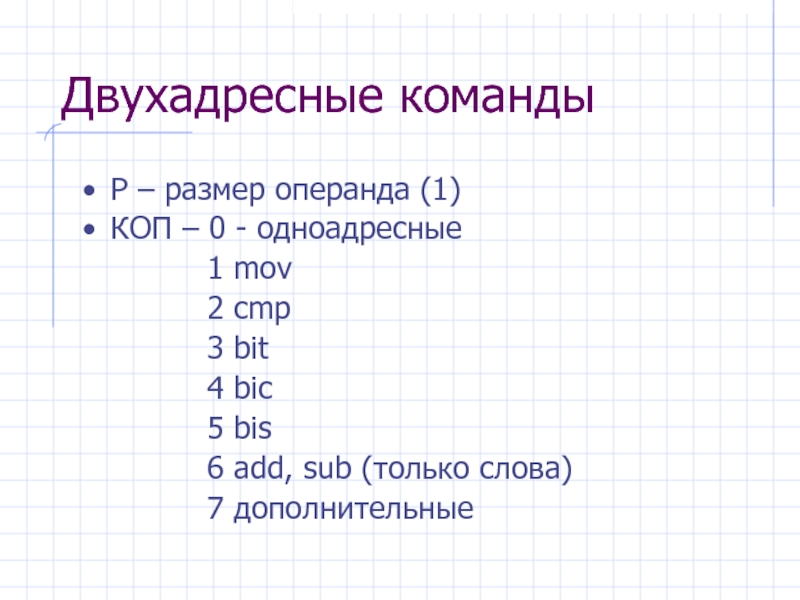

- 10. Двухадресные команды Р – размер операнда (1)

- 11. Одноадресные команды Р – размер операнда (1) КОП (6)

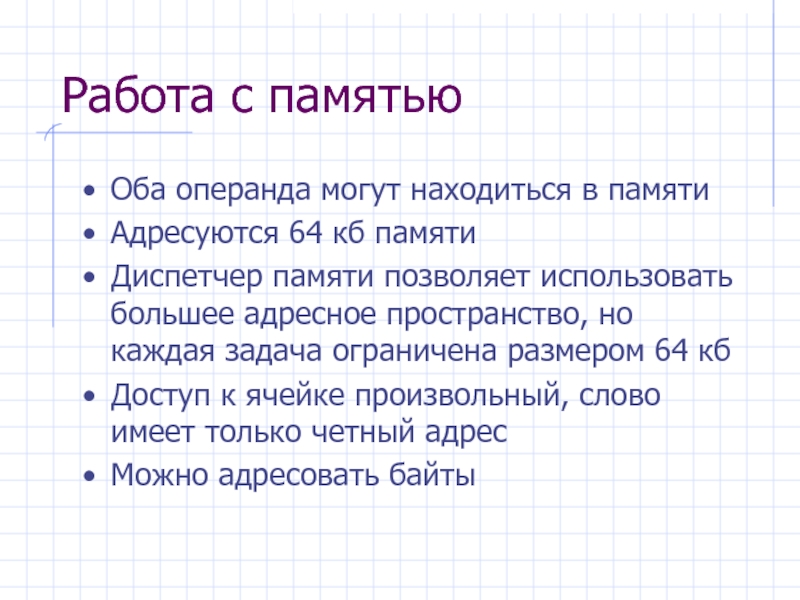

- 12. Работа с памятью Оба операнда могут находиться

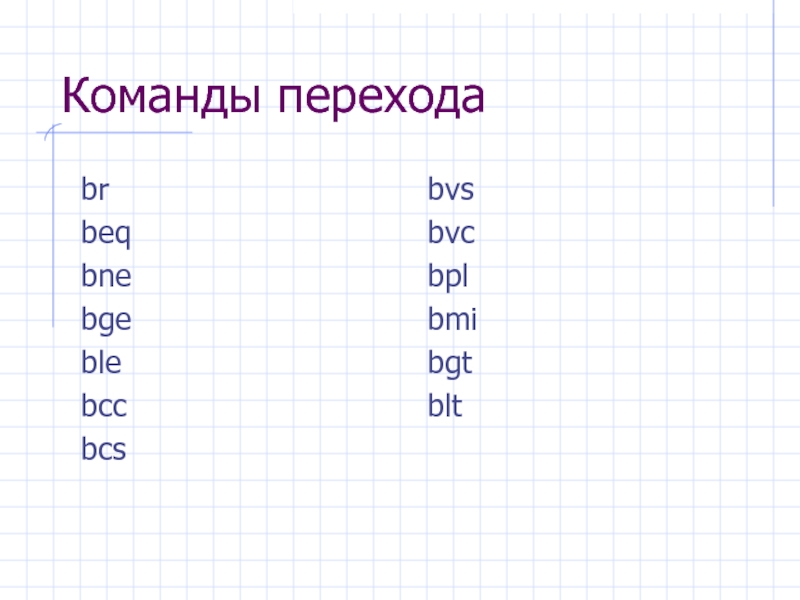

- 13. Команды перехода br beq bne bge

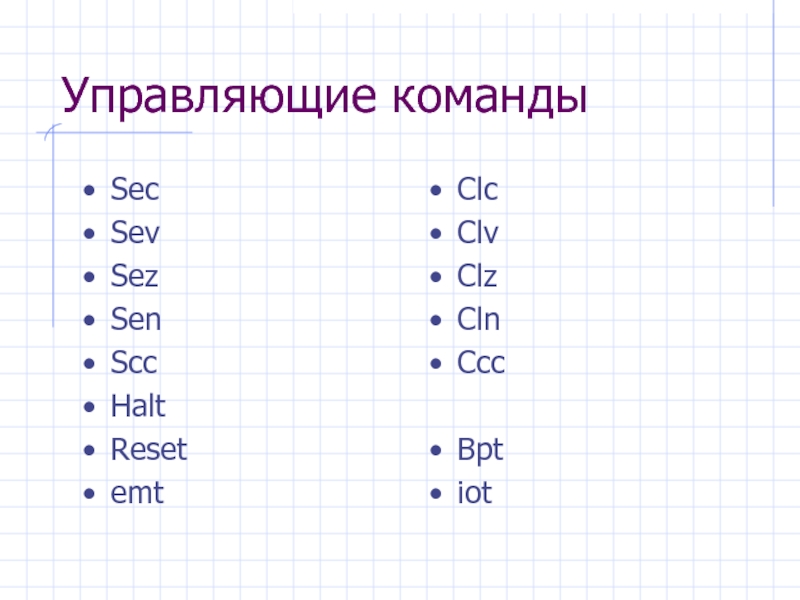

- 14. Управляющие команды Sec Sev Sez Sen Scc

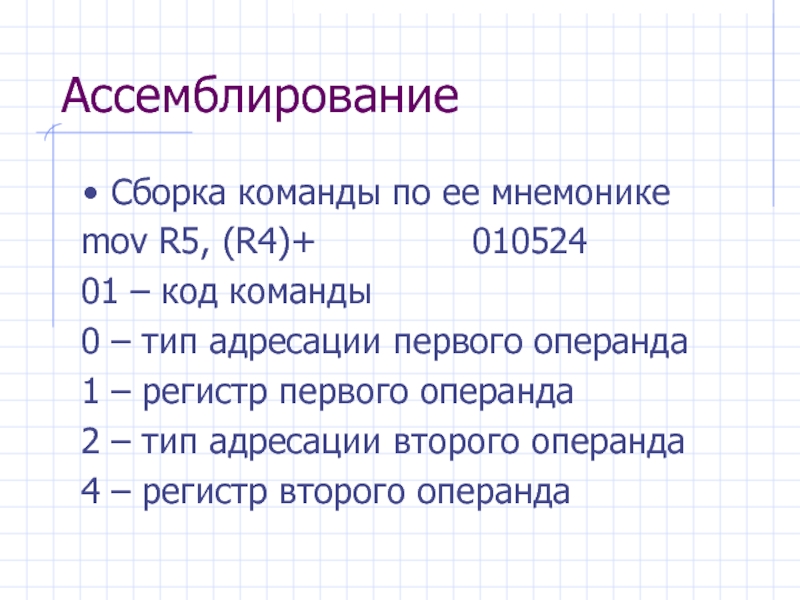

- 15. Ассемблирование Сборка команды по ее мнемонике

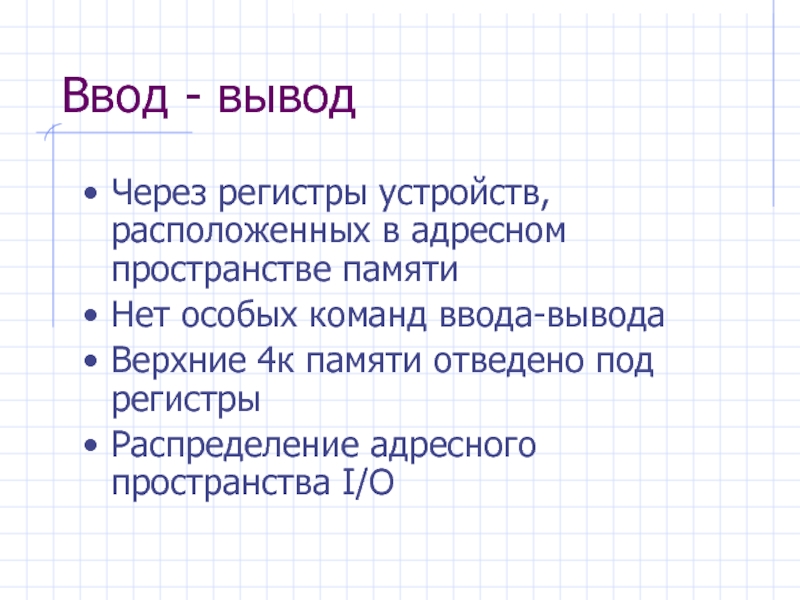

- 16. Ввод - вывод Через регистры устройств, расположенных

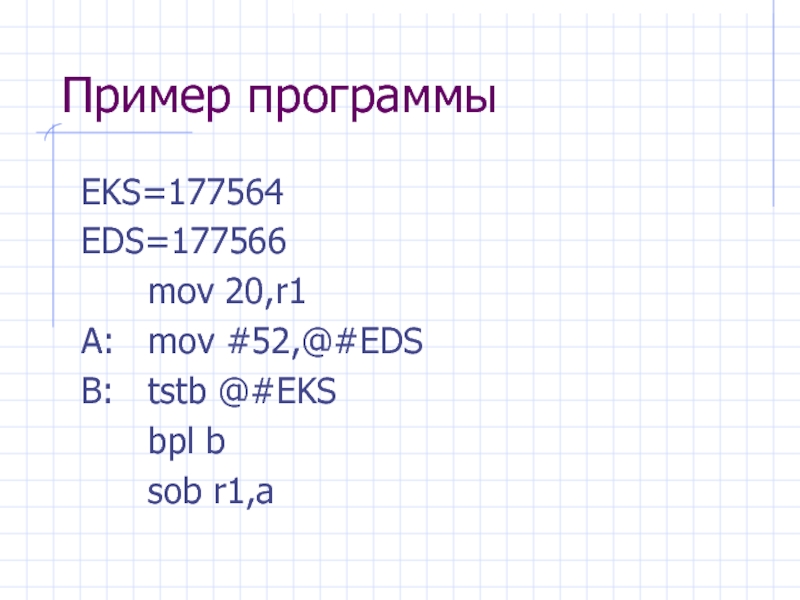

- 17. Пример программы EKS=177564 EDS=177566

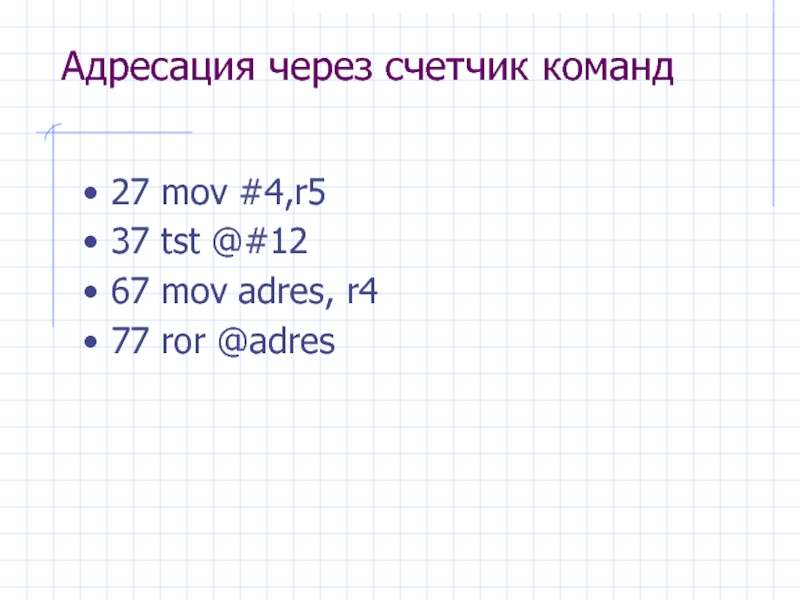

- 18. Адресация через счетчик команд 27 mov #4,r5

- 19. Характеристики набора команд НАЛИЧИЕ команд Арифметических

Слайд 3Структура команды

Битовые поля:

Адреса операндов

Код команды

Уточнения типа операции

Методы адресации

Размер операндов

Слайд 4Ассемблер

Автокодовый язык

Взаимно-однозначное соответствие команды процессора и записи на языке ассемблера

Макровозможности ассемблера

Слайд 5Регистры pdp11

Общего назначения:

R0 R1 R2 R3 R4 R5 R6 R7

R6 –

указатель стека

R7 – счетчик команд

R7 – счетчик команд

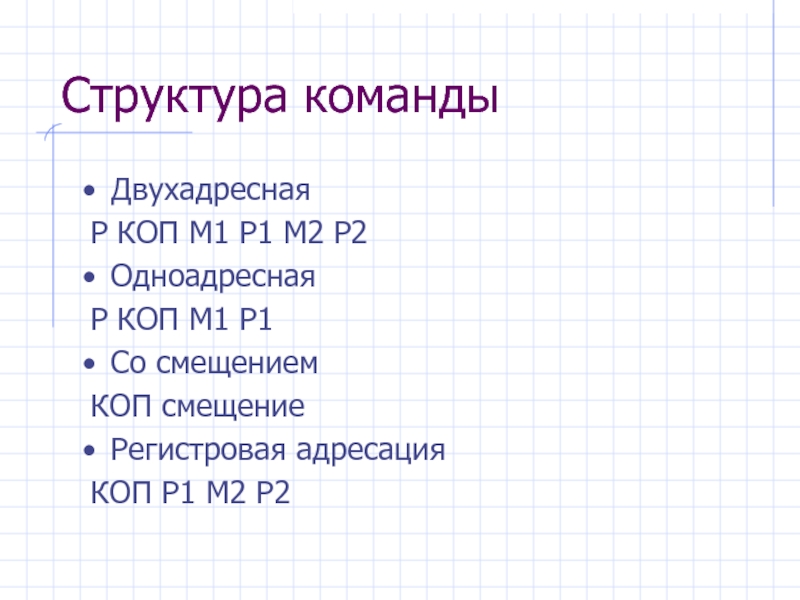

Слайд 7Структура команды

Двухадресная

Р КОП М1 Р1 М2 Р2

Одноадресная

Р КОП М1

Р1

Со смещением

КОП смещение

Регистровая адресация

КОП Р1 М2 Р2

Со смещением

КОП смещение

Регистровая адресация

КОП Р1 М2 Р2

Слайд 8Методы адресации

0 регистровый

1 регистровый косвенный

2 регистровый с автоувеличением

3 косвенно-регистровый с автоувеличением

4

регистровый с автоуменьшением

5 косвенно-регистровый с автоуменьшением

6 индексный

7 косвенно-индексный

5 косвенно-регистровый с автоуменьшением

6 индексный

7 косвенно-индексный

Слайд 9Типы команд по адресности

Двухадресные

Обноадресные

Безадресные

Неполной адресации

Регистровой адресации

Относительной адресации (смещение)

Слайд 10Двухадресные команды

Р – размер операнда (1)

КОП – 0 - одноадресные

1 mov

2 cmp

3 bit

4 bic

5 bis

6 add, sub (только слова)

7 дополнительные

2 cmp

3 bit

4 bic

5 bis

6 add, sub (только слова)

7 дополнительные

Слайд 12Работа с памятью

Оба операнда могут находиться в памяти

Адресуются 64 кб памяти

Диспетчер

памяти позволяет использовать большее адресное пространство, но каждая задача ограничена размером 64 кб

Доступ к ячейке произвольный, слово имеет только четный адрес

Можно адресовать байты

Доступ к ячейке произвольный, слово имеет только четный адрес

Можно адресовать байты

Слайд 15Ассемблирование

Сборка команды по ее мнемонике

mov R5, (R4)+

010524

01 – код команды

0 – тип адресации первого операнда

1 – регистр первого операнда

2 – тип адресации второго операнда

4 – регистр второго операнда

01 – код команды

0 – тип адресации первого операнда

1 – регистр первого операнда

2 – тип адресации второго операнда

4 – регистр второго операнда

Слайд 16Ввод - вывод

Через регистры устройств, расположенных в адресном пространстве памяти

Нет особых

команд ввода-вывода

Верхние 4к памяти отведено под регистры

Распределение адресного пространства I/O

Верхние 4к памяти отведено под регистры

Распределение адресного пространства I/O

Слайд 19Характеристики набора команд

НАЛИЧИЕ команд

Арифметических

Логических

Сдвиговых

Переходов по условию

Управления

богатство методов адресации

,

основа ISA последующих ЭВМ CISC

основа ISA последующих ЭВМ CISC