- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Архитектура 32-битных процессоров IA-32. (Лекция 3) презентация

Содержание

- 1. Архитектура 32-битных процессоров IA-32. (Лекция 3)

- 2. Структура микропроцессора Intel 80386 Циклический

- 3. Регистры ЦП 80386

- 4. Режимы работы ЦП 80386 Реальный режим или

- 5. ЦП 80386 (переключение режимов)

- 6. Формирование линейного адреса без участия селекторов

- 7. Формирование линейного адреса в защищенном режиме

- 8. Сегментная и страничная организация памяти Селектор Смещение

- 9. Многозадачность в ЦП 80386

- 10. В адресное пространство задачи входят

- 11. Сравнительные характеристики режимов работы процессора

- 12. ЦП 80386 (формат команды) ПРЕФИКС

- 13. Формат команды КОП - код операции. Байт

- 14. Структура микропроцессора Intel 80486 Шинный

- 15. Режим пакетирования Средство блочной передачи: 64 бита за 1 раз.

- 16. Уровни привилегий в IA32

- 17. ЦП 80486 (уровни привилегий)

- 18. Структуры с привилегиями CPL – текущий

- 19. Доступ к данным разрешен, если max(CPL,RPL)

- 20. Вопросы для самоконтроля Какие регистры составляют программная

- 21. Вопросы для самоконтроля В каких режимах работы

Слайд 1Организация ЭВМ и систем

Лекция № 3

Архитектура 32-битных процессоров IA-32

ЦП

Страничная и сегментная организация памяти. Многозадачность. Формат команд

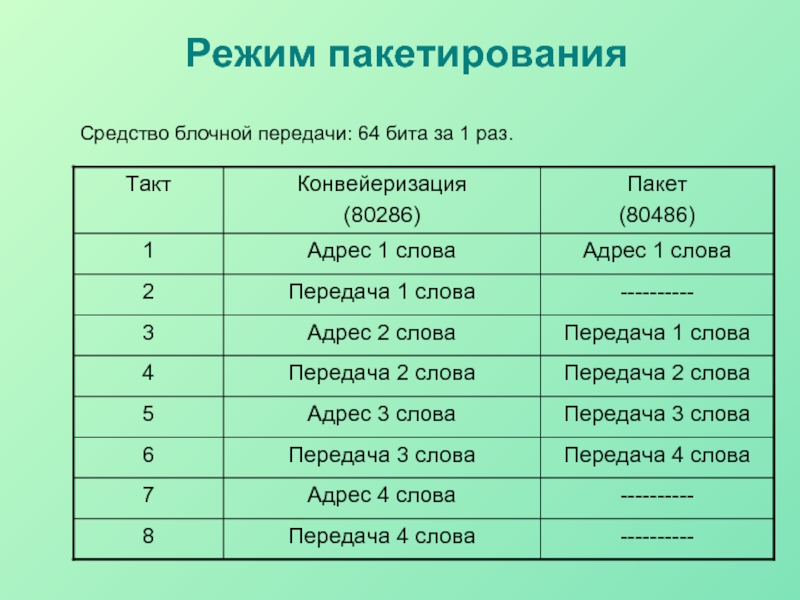

ЦП 80486 – режим пакетирования

Слайд 2Структура микропроцессора

Intel 80386

Циклический

сдвигатель,

сумматор

Умножитель/

делитель

Набор

регистров

Декодирование

и упорядочение

Управляющее

ПЗУ

Декодер

команд

Очередь

декодированных

команд

Устройство

предварительной

выборки

16-байтная

очередь

кодов

Трехвходовый

сумматор

Регистры

дескрипторов

ПЛМ границ

и атрибутов

Сумматор

Кэш страниц

ПЛМ управления

и атрибутов

Блок

защиты

Арбитр

запросов

Драйвер

адреса

Управление

размером

шины,

конвейером

Мультиплексор,

приемопере-

датчики

АЛУ

Управление

Предварительное

декодирование

команд

Предварительная

выборка команд

Специализированная шина АЛУ

32

Шина исполнительного адреса

32

Шина исполнительного адреса

32

Внутренняя

шина

управления

Шина смещений

32

Шина линейного адреса

Выборка кодов,

Таблицы страниц

Блок сегментации

Блок разбивки

на страницы

Управление шиной

Управление

Шина физического

адреса

34

32

32

Слайд 3Регистры ЦП 80386

Программно доступные регистры:

8 регистров

Регистр флагов (EFLAGS – 32-разрядный).

Счетчик команд (EIP – 32-разрядный).

6 сегментных регистров (16-разрядные).

Системные регистры:

4 регистра управления: CR0, CR1, CR2, CR3 (сохраняют состояние микропроцессора).

8 отладочных регистра: DR0-DR3, DR6, DR7, (DR4, DR5 – зарезервированные ф. Intel).

4 регистра защищенного режима: GDTR, IDTR – 48-разрядные; LDTR, TR – 16-разрядные.

2 регистра страничных проверок: TR6, TR7.

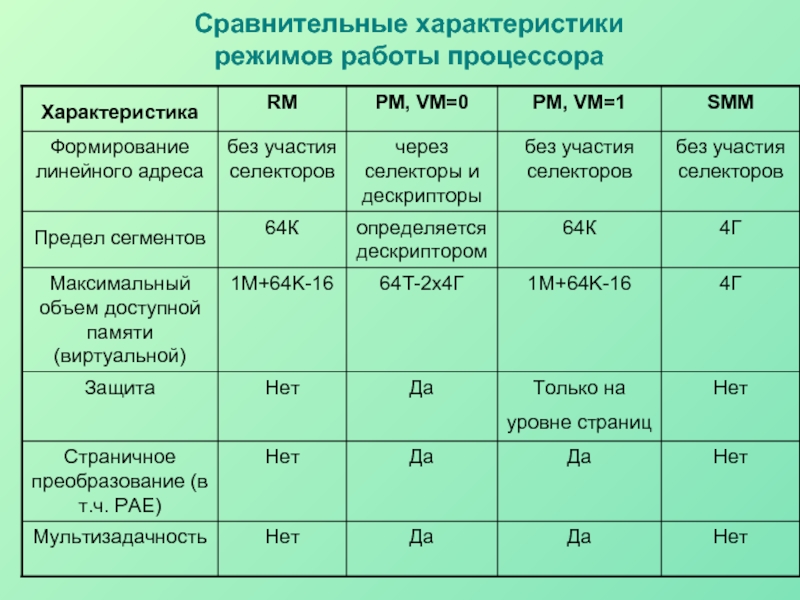

Слайд 4Режимы работы ЦП 80386

Реальный режим или режим реальных адресов.

Виртуальный режим или режим виртуального 8086.

Защищенный режим – полностью 32-разрядный процессор.

Слайд 6Формирование линейного адреса

без участия селекторов

В этом случае базовый адрес сегмента берется из сегментного регистра. Значение в сегментном регистре представляет собой биты 4-19 базового адреса сегмента. Из этого следует, что сегменты в этих режимах выровнены по 16-байтной границе и все сегменты начинаются в пределах нижнего мегабайта линейного адресного пространства. Предел для всех сегментов одинаков. В режиме реального адреса и для задачи в состоянии VM86 предел сегмента - 64Кбайт, а в режиме системного управления - 4Гбайт.

Слайд 7Формирование линейного адреса в защищенном режиме

Если в

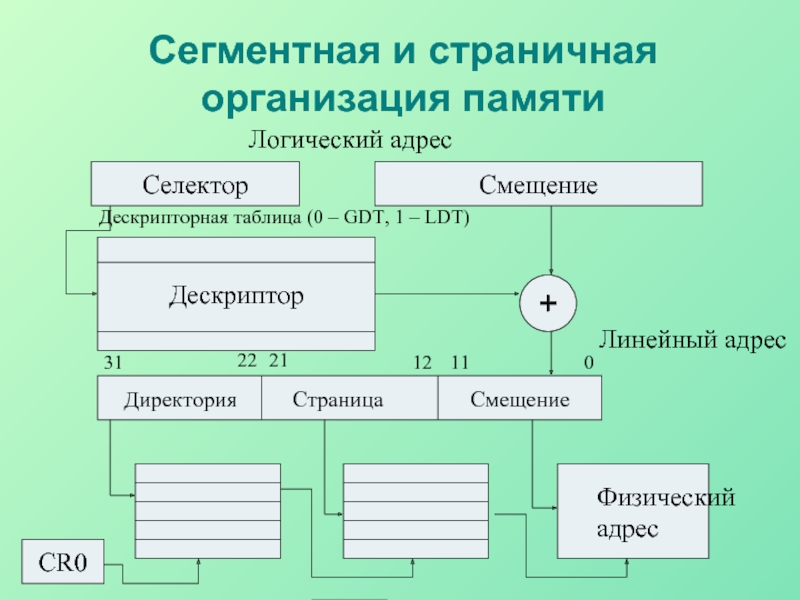

В процессе страничной трансляции адресов полученный линейный адрес разбивается на три части. Старшие десять бит линейного адреса являются индексом элемента из каталога таблиц. По этому элементу определяется физический адрес таблицы страниц. Биты 21-12 линейного адреса выбирают элемент из этой таблицы страниц. Выбранный элемент определяет физический адрес страницы. Младшие 12 бит линейного адреса определяют смещение от начала страницы.

Слайд 8Сегментная и страничная организация памяти

Селектор

Смещение

Дескриптор

CR0

Линейный адрес

Логический адрес

Физический

адрес

Дескрипторная таблица (0 – GDT,

Директория

Страница

Смещение

0

11

12

21

22

31

+

Слайд 9Многозадачность в ЦП 80386

Многозадачность - это метод

Задачу составляют два компонента: адресное пространство задачи и сегмент состояния задачи (Task State Segment - TSS).

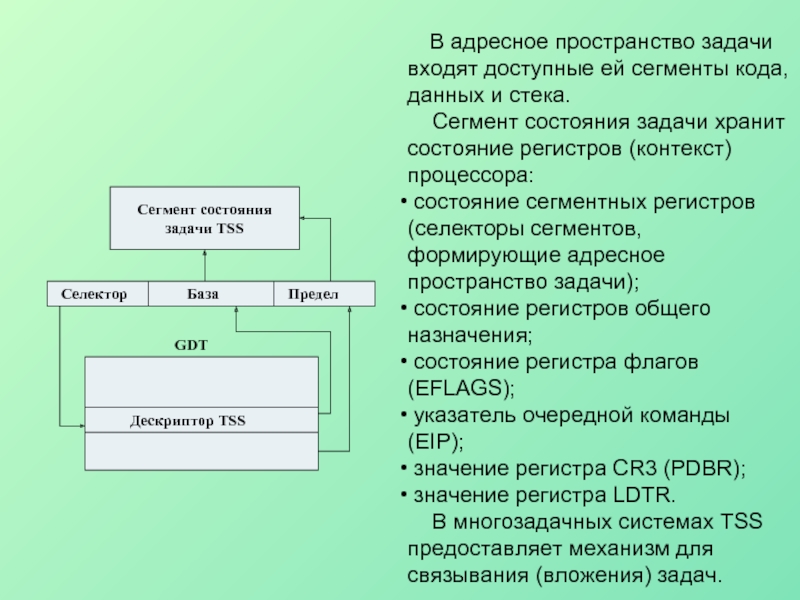

Слайд 10 В адресное пространство задачи входят доступные ей сегменты кода,

данных

Сегмент состояния задачи хранит состояние регистров (контекст) процессора:

состояние сегментных регистров (селекторы сегментов, формирующие адресное пространство задачи);

состояние регистров общего назначения;

состояние регистра флагов (EFLAGS);

указатель очередной команды (EIP);

значение регистра CR3 (PDBR);

значение регистра LDTR.

В многозадачных системах TSS предоставляет механизм для связывания (вложения) задач.

Дескриптор TSS

GDT

Селектор

База

Предел

Сегмент состояния

задачи TSS

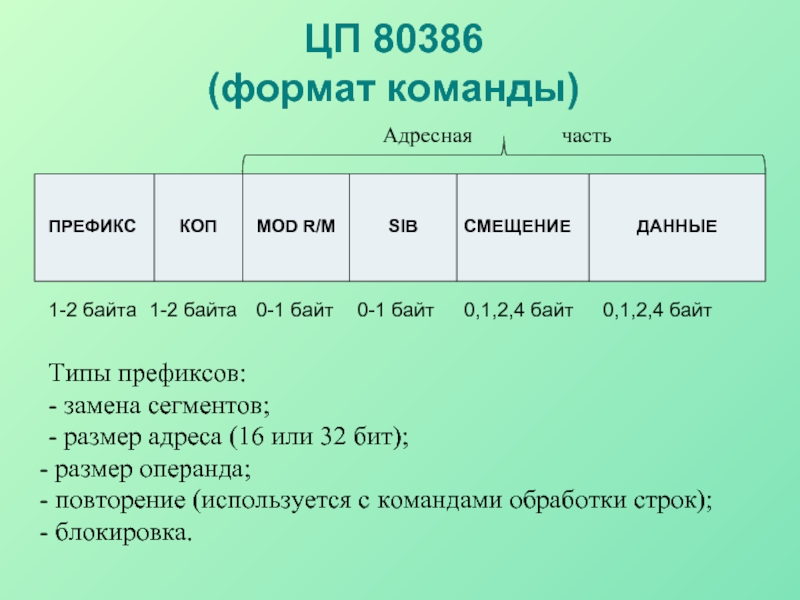

Слайд 12ЦП 80386

(формат команды)

ПРЕФИКС

КОП

MOD R/M

SIB

СМЕЩЕНИЕ

ДАННЫЕ

1-2 байта

1-2 байта

0-1 байт

0-1 байт

0,1,2,4 байт

0,1,2,4 байт

Адресная часть

Типы префиксов:

- замена сегментов;

- размер адреса (16 или 32 бит);

размер операнда;

повторение (используется с командами обработки строк);

блокировка.

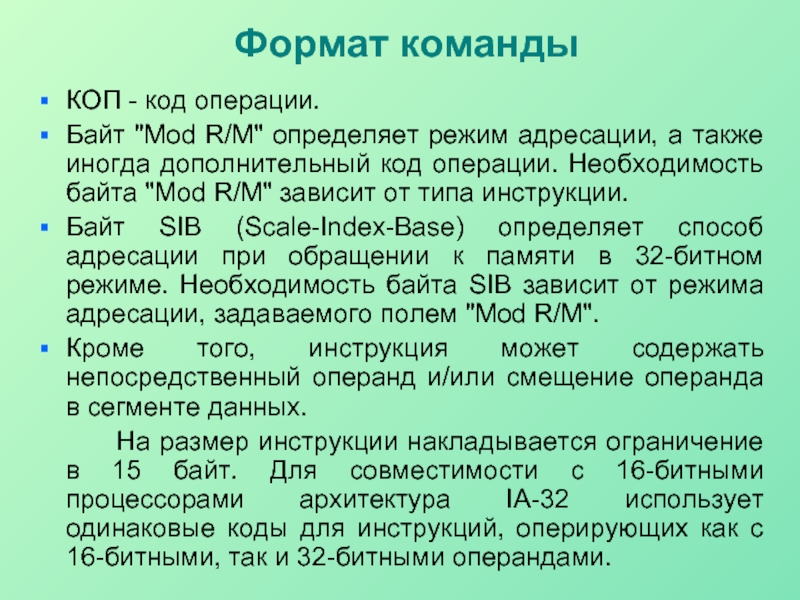

Слайд 13Формат команды

КОП - код операции.

Байт "Mod R/M" определяет режим адресации, а

Байт SIB (Scale-Index-Base) определяет способ адресации при обращении к памяти в 32-битном режиме. Необходимость байта SIB зависит от режима адресации, задаваемого полем "Mod R/M".

Кроме того, инструкция может содержать непосредственный операнд и/или смещение операнда в сегменте данных.

На размер инструкции накладывается ограничение в 15 байт. Для совместимости с 16-битными процессорами архитектура IA-32 использует одинаковые коды для инструкций, оперирующих как с 16-битными, так и 32-битными операндами.

Слайд 14Структура микропроцессора

Intel 80486

Шинный интерфейс

Драйверы

адреса

Буферы записи

Приемо-

передатчики

данных

Управление

шиной

Управление

пакетами

Управление

размером

Управление

кэш-памятью

Управление

паритетом

Адрес

Данные

Управление

Кэш-память 8К

Устройство

предвыборки

команд

Очередь

кода

32

32

32

Устройство

страничного

преобразования

Ассоциативный

буфер

PCD

PWT

Физи-

ческий

адрес

128

Устройство

сегментации

Регистры

дескрипторов

Контроль предела

и атрибутов

Парал-ный

сдвигатель

Регистры

АЛУ

32

Дешифратор

команд

24

Устройство

управления

Управляющее

ПЗУ

Дешифрированная

команда

Устройство

с плавающей

точкой

Регистры

Микрокоманда

Шина смещения

32

База

Команды

Шина линейного адреса

32

Шина данных

32

Шина данных

32

64-битная внутренняя шина

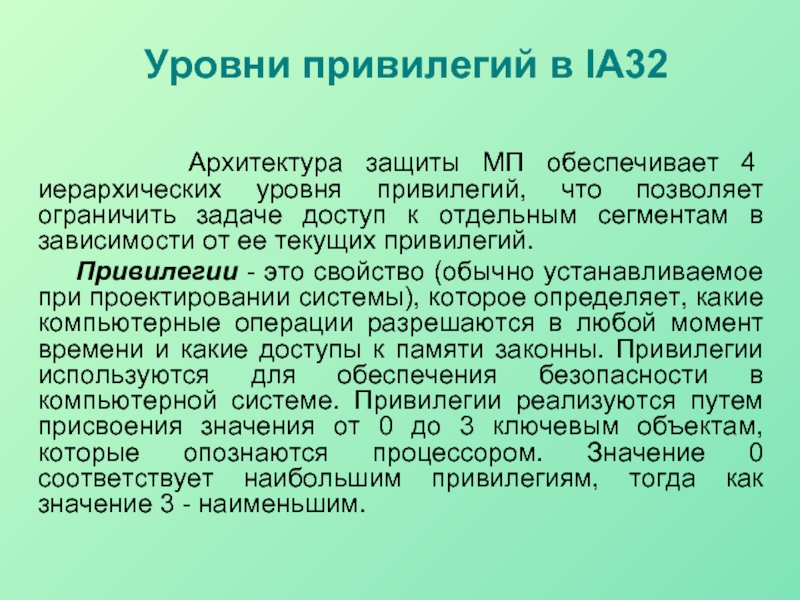

Слайд 16Уровни привилегий в IA32

Архитектура защиты МП

Привилегии это свойство (обычно устанавливаемое при проектировании системы), которое определяет, какие компьютерные операции разрешаются в любой момент времени и какие доступы к памяти законны. Привилегии используются для обеспечения безопасности в компьютерной системе. Привилегии реализуются путем присвоения значения от 0 до 3 ключевым объектам, которые опознаются процессором. Значение 0 соответствует наибольшим привилегиям, тогда как значение 3 наименьшим.

Слайд 17 ЦП 80486

(уровни привилегий)

0

1

2

3

0 – Ядро ОС

1 – ОС

2 –

3 – Прикладные программы

Направление обращения к данным

Привилегированные команды выполняются только на «0» - уровне привилегий, на всех других уровнях вызывается исключение №13 – нарушение общей защиты.

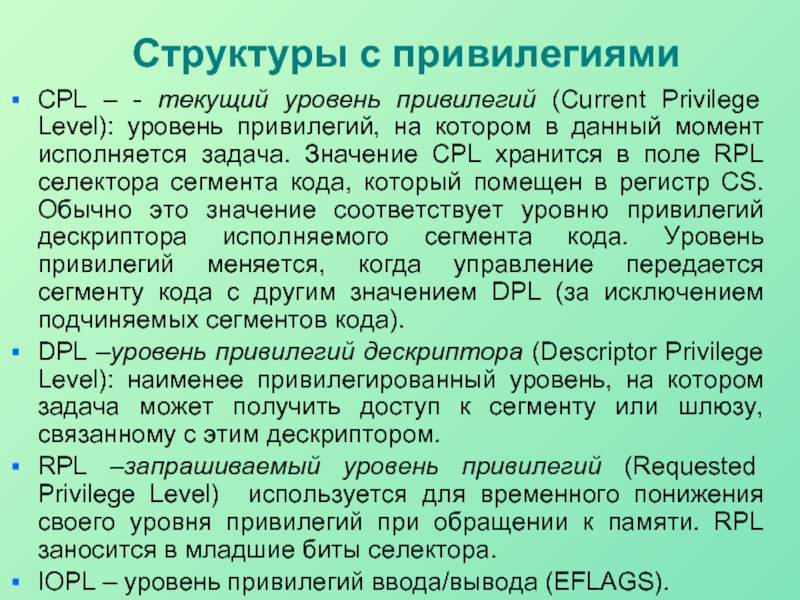

Слайд 18Структуры с привилегиями

CPL – текущий уровень привилегий (Current Privilege Level):

DPL –уровень привилегий дескриптора (Descriptor Privilege Level): наименее привилегированный уровень, на котором задача может получить доступ к сегменту или шлюзу, связанному с этим дескриптором.

RPL –запрашиваемый уровень привилегий (Requested Privilege Level) используется для временного понижения своего уровня привилегий при обращении к памяти. RPL заносится в младшие биты селектора.

IOPL – уровень привилегий ввода/вывода (EFLAGS).

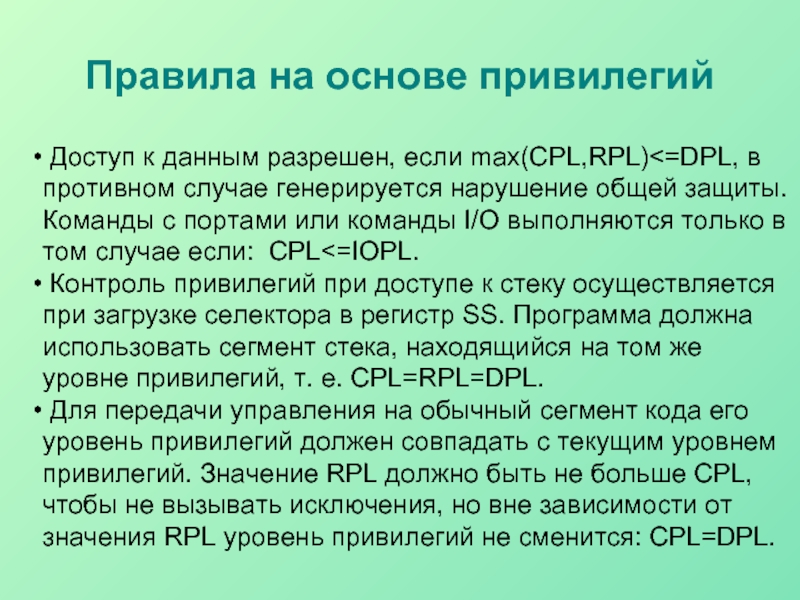

Слайд 19 Доступ к данным разрешен, если max(CPL,RPL)

Контроль привилегий при доступе к стеку осуществляется при загрузке селектора в регистр SS. Программа должна использовать сегмент стека, находящийся на том же уровне привилегий, т. е. CPL=RPL=DPL.

Для передачи управления на обычный сегмент кода его уровень привилегий должен совпадать с текущим уровнем привилегий. Значение RPL должно быть не больше CPL, чтобы не вызывать исключения, но вне зависимости от значения RPL уровень привилегий не сменится: CPL=DPL.

Правила на основе привилегий

Слайд 20Вопросы для самоконтроля

Какие регистры составляют программная модель ЦП 80386?

В каких режимах

Как формируется физический адрес при сегментной адресации?

Как формируется физический адрес при страничной адресации?

Сколько бит линейного адреса определяют смещение от начала страницы?

Что такое многозадачность? Какими средствами она поддерживается?

Какая информация хранится в сегменте состояния задачи?

Слайд 21Вопросы для самоконтроля

В каких режимах работы ЦП 80386 предел сегмента –

В каких режимах работы ЦП 80386 поддерживается страничное преобразование адреса?

Какие поля составляют команду ЦП 80386?

Что такое пакетирование? В чем его преимущество?

С каких уровней можно обратиться к данным, находящимся на 3 уровне привилегий?

Какое правило на основе привилегий применяется для защиты сегмента кода?