- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

25.05.2010 презентация

Содержание

- 1. 25.05.2010

- 2. Особенности языка Verilog Вычисления управляются потоком данных

- 3. Иерархия уровней моделирования Системный уровень Уровень регистровых

- 4. Области применения языка Verilog Проектирование СБИС

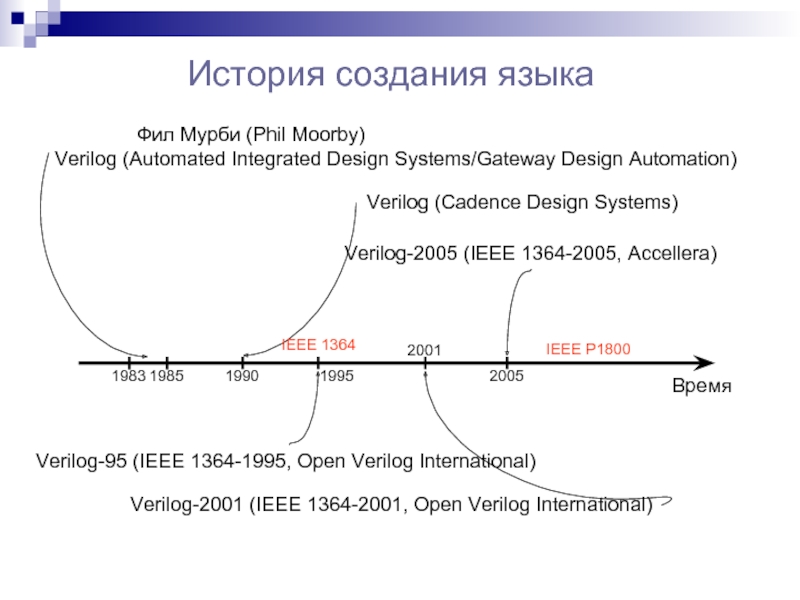

- 5. История создания языка Verilog (Automated Integrated Design

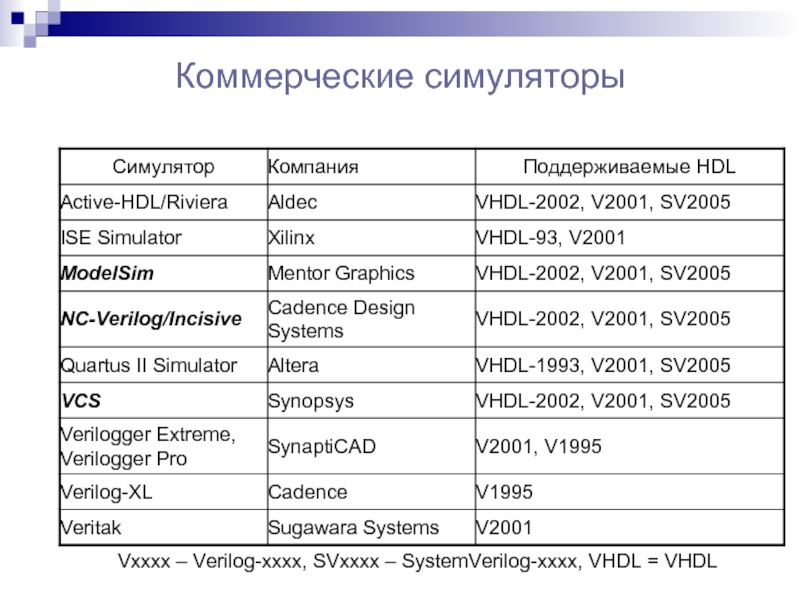

- 6. Коммерческие симуляторы Vxxxx – Verilog-xxxx, SVxxxx – SystemVerilog-xxxx, VHDL = VHDL

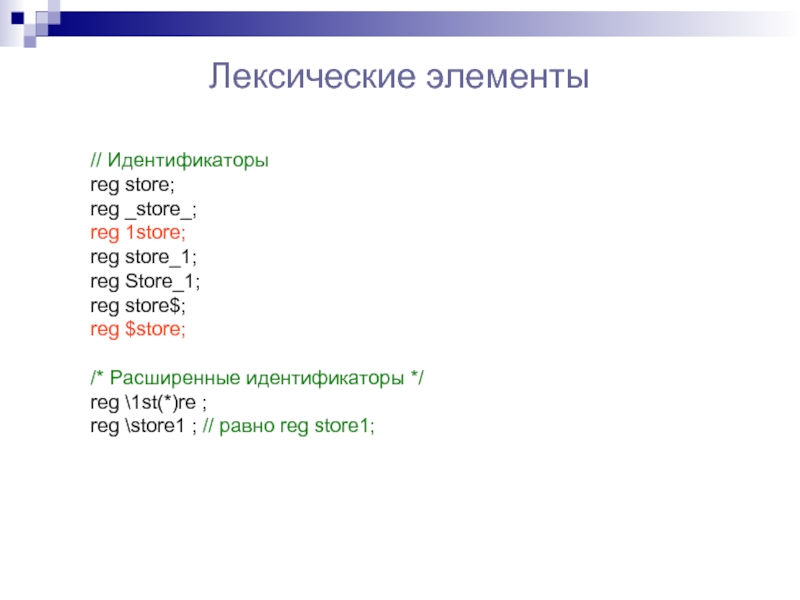

- 7. Лексические элементы // Идентификаторы reg store; reg

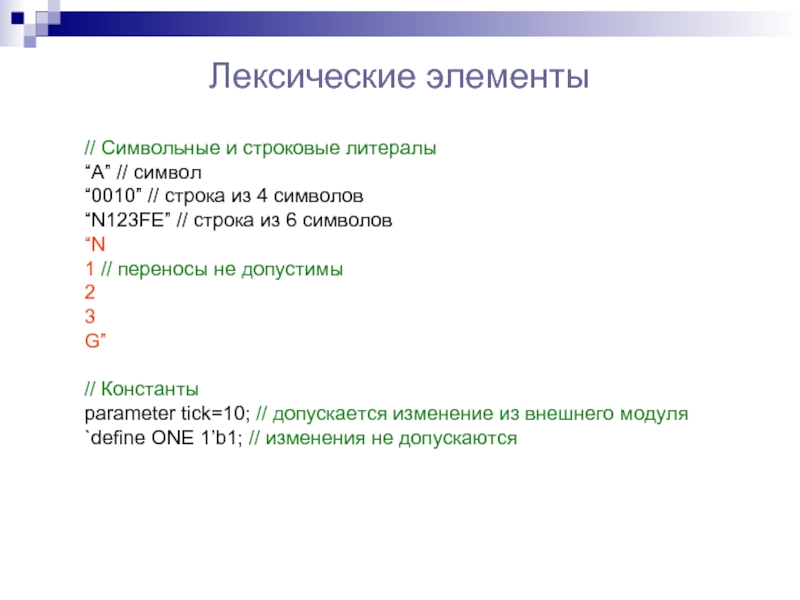

- 8. Лексические элементы // Символьные и строковые литералы

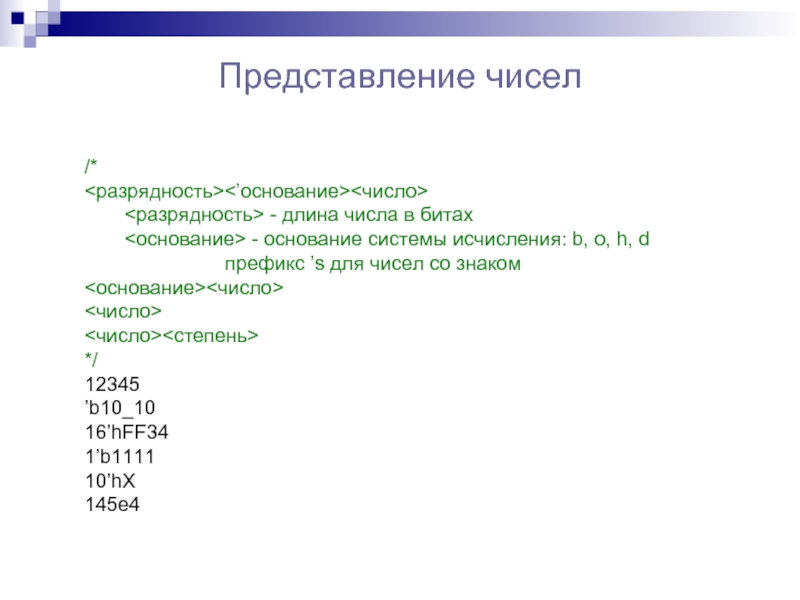

- 9. Представление чисел /* - длина

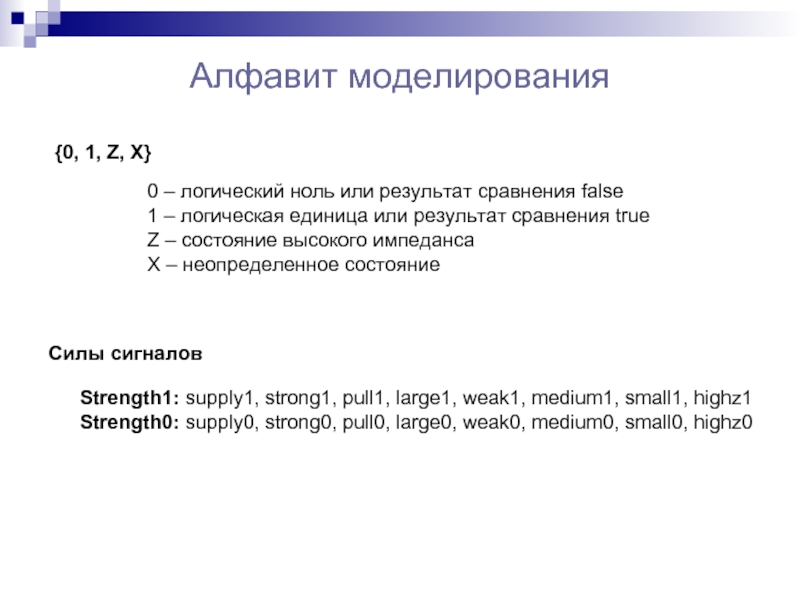

- 10. Алфавит моделирования {0, 1, Z, X} 0

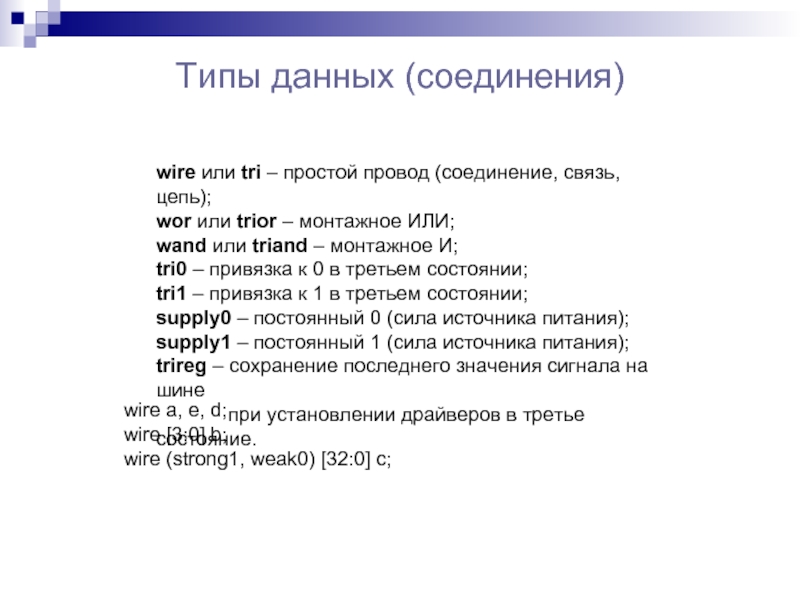

- 11. Типы данных (соединения) wire или tri –

- 12. Типы данных (переменные) reg – вектор любого

- 13. Арифметические операции `+’ – сложение 2

- 14. Логические операции `&&’ – логическое И 4’b1011

- 15. Поразрядные логические операции `&’ – поразрядное И

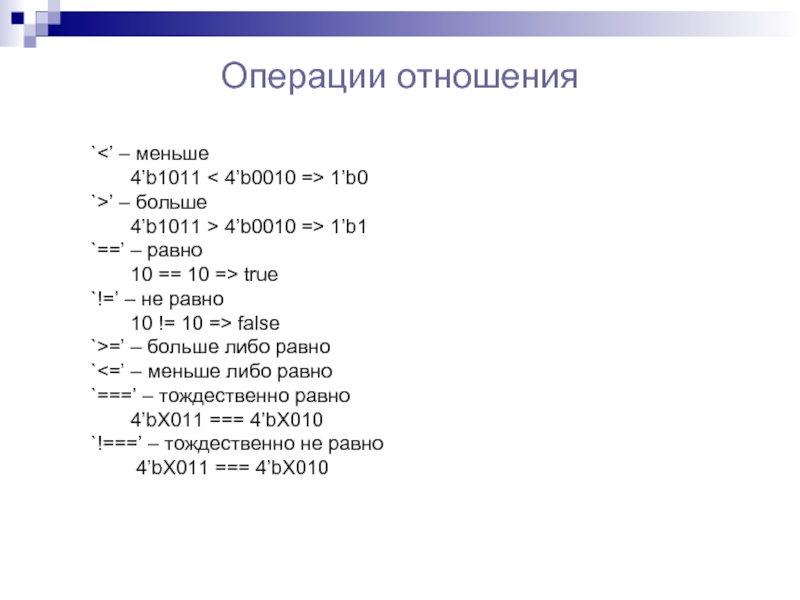

- 16. Операции отношения ` 1’b0 `>’ – больше

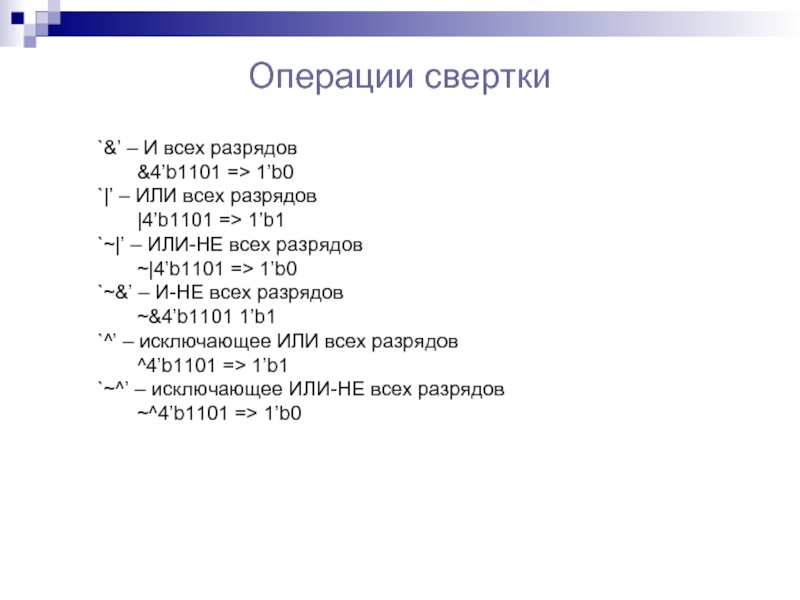

- 17. Операции свертки `&’ – И всех разрядов

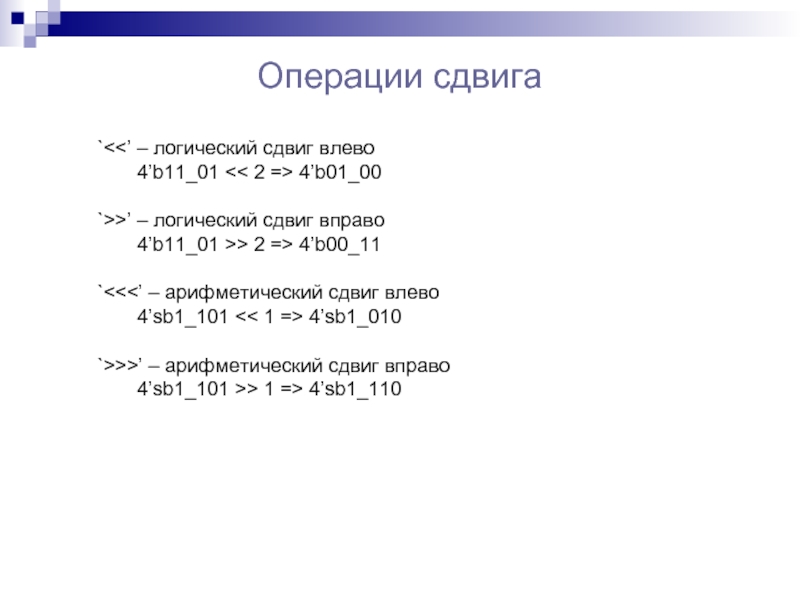

- 18. Операции сдвига `’ – логический сдвиг вправо

- 19. Операторы конкатенации и повторения {переменная1, переменная2, …

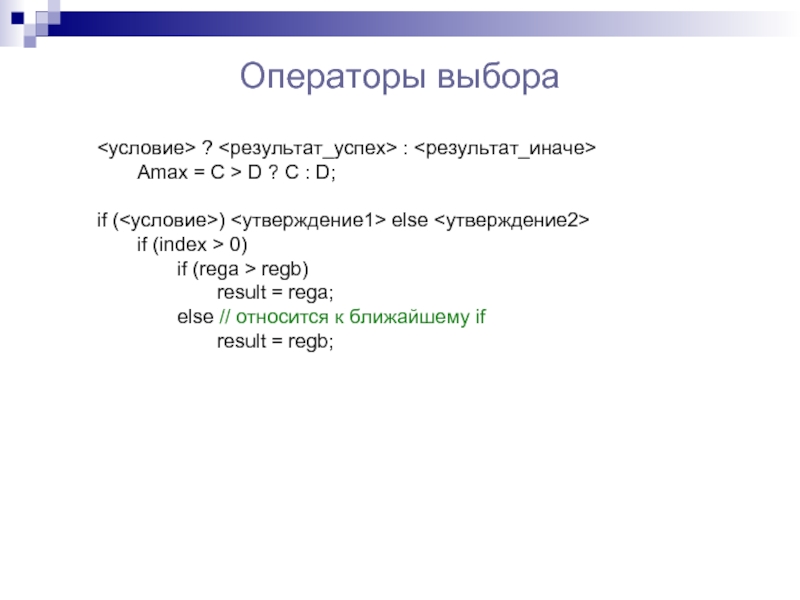

- 20. Операторы выбора ? : Amax

- 21. reg [31:0] instruction; reg [2:0] aluOp; casez

- 22. Оператор цикла repeat parameter size = 8,

- 23. Оператор цикла while begin: count1s reg [7:0]

- 24. Оператор цикла for begin :init_mem reg [7:0]

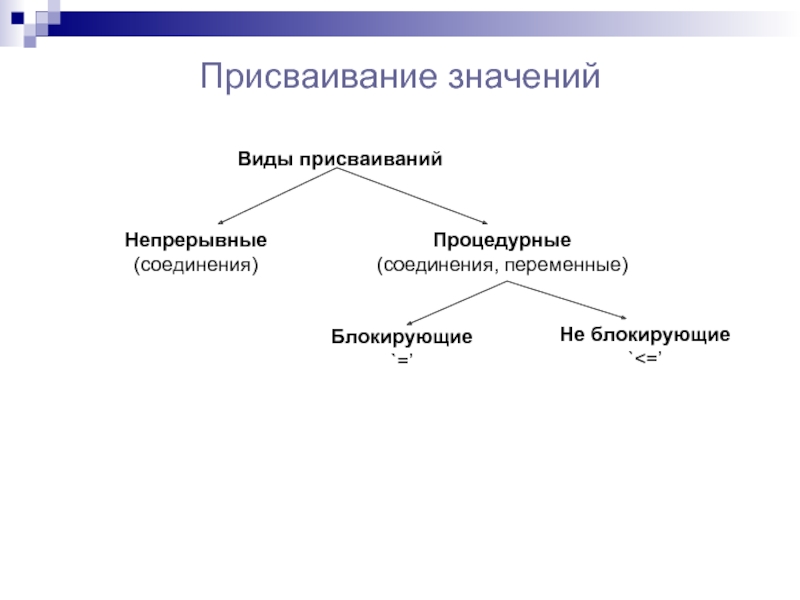

- 25. Присваивание значений Виды присваиваний Непрерывные (соединения) Процедурные (соединения, переменные) Блокирующие `=’ Не блокирующие `

- 26. Непрерывное присваивание wire [15:0] sum, a, b;

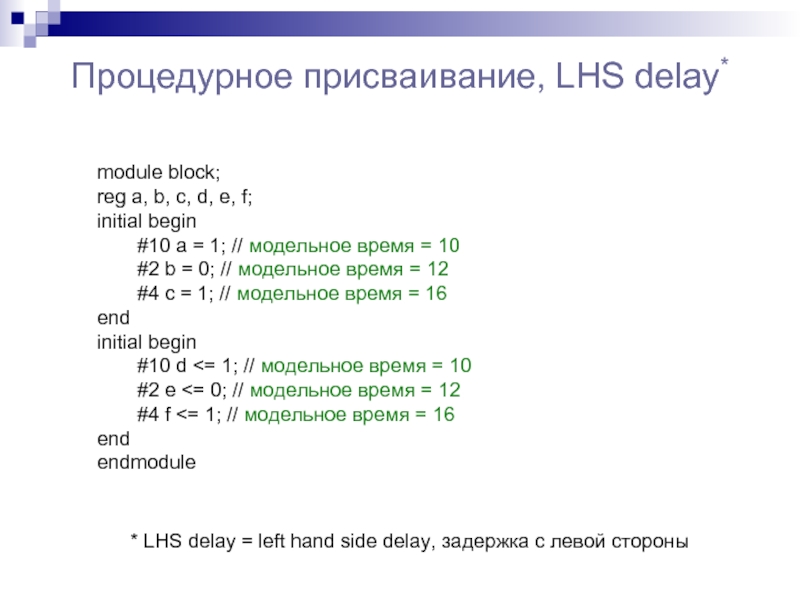

- 27. Процедурное присваивание, LHS delay* module block; reg

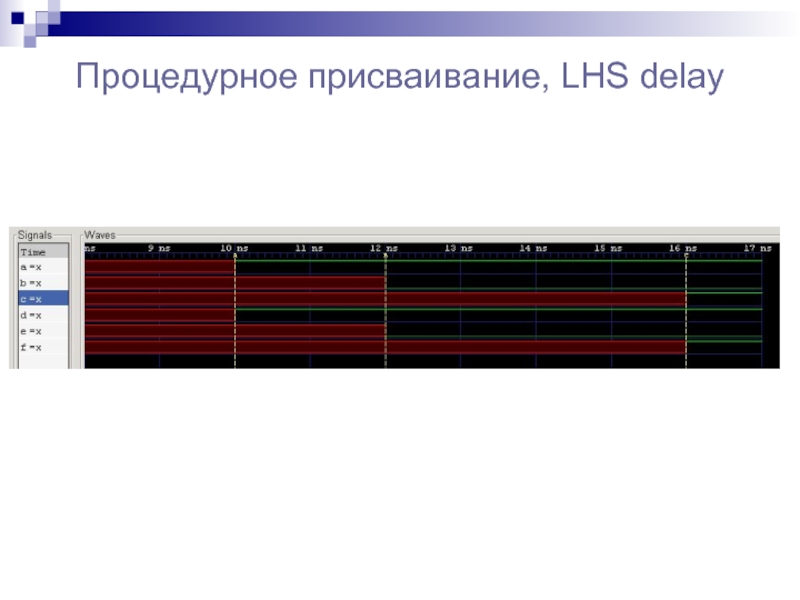

- 28. Процедурное присваивание, LHS delay

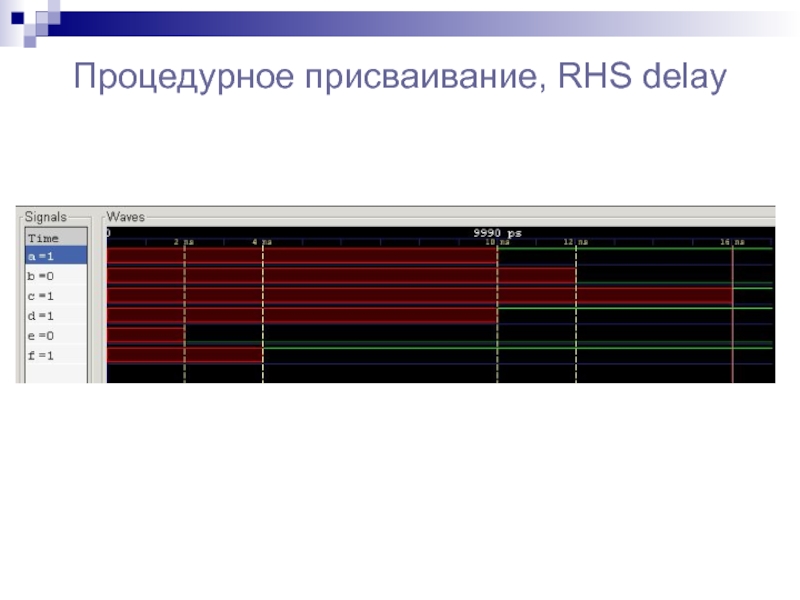

- 29. Процедурное присваивание, RHS delay* module block; reg

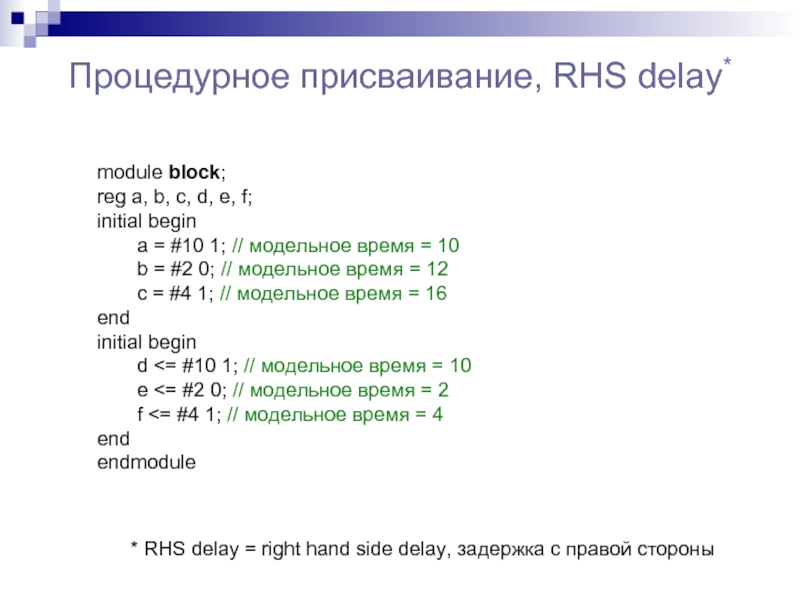

- 30. Процедурное присваивание, RHS delay

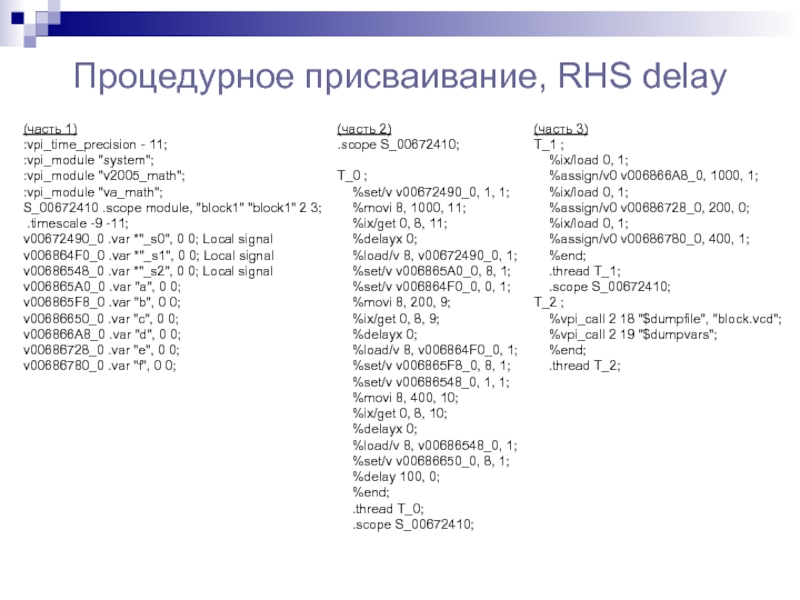

- 31. (часть 1) :vpi_time_precision - 11; :vpi_module "system";

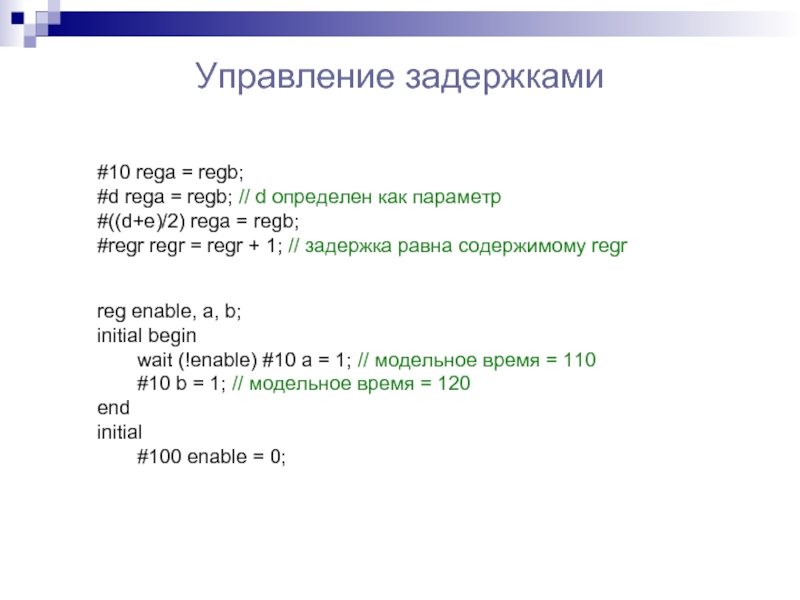

- 32. Управление задержками #10 rega = regb; #d

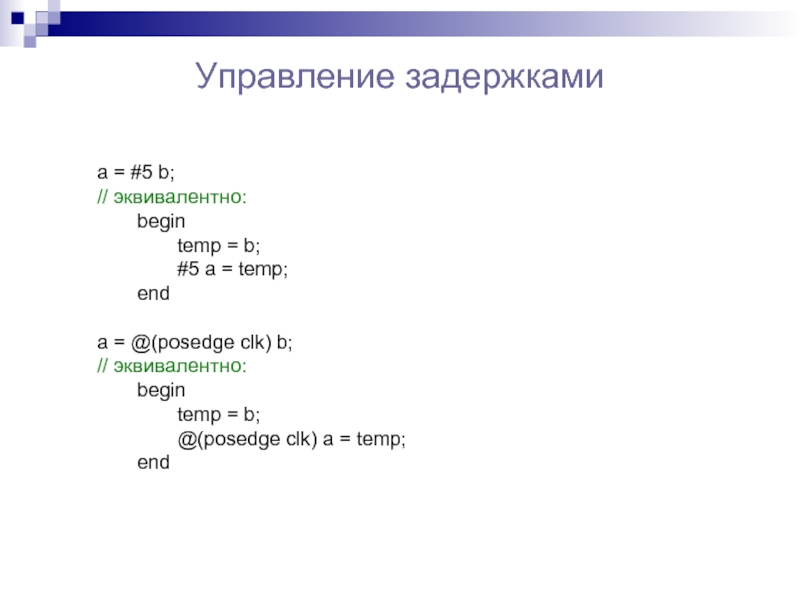

- 33. Управление задержками a = #5 b; //

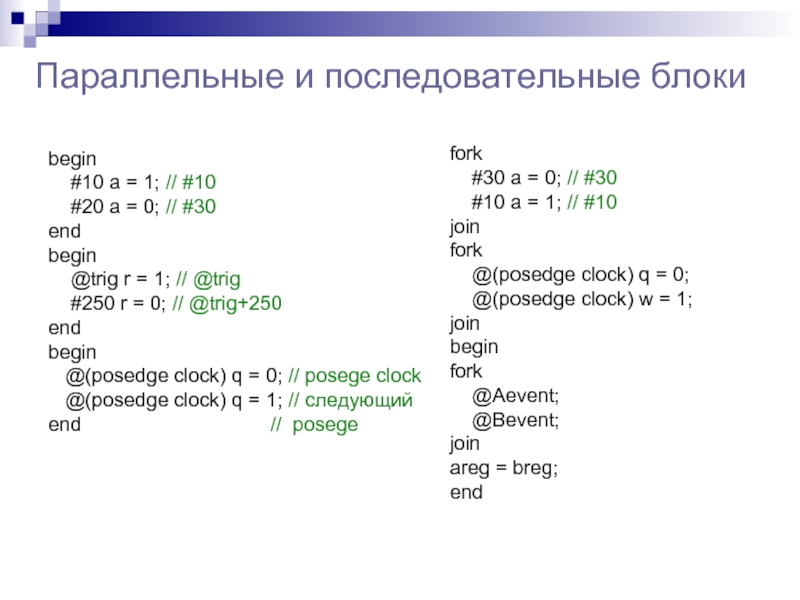

- 34. Параллельные и последовательные блоки begin

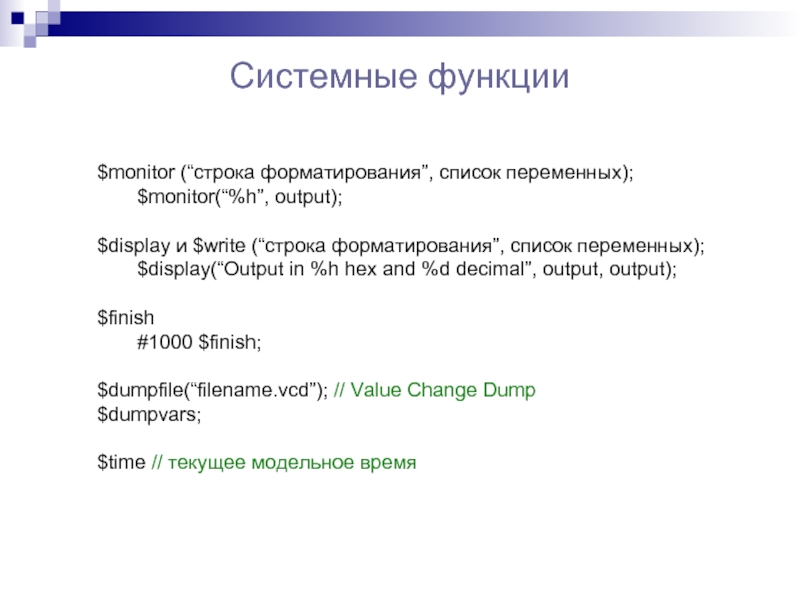

- 35. Системные функции $monitor (“строка форматирования”, список переменных);

- 36. Модульная структура // Файл lazy.v: module lazy

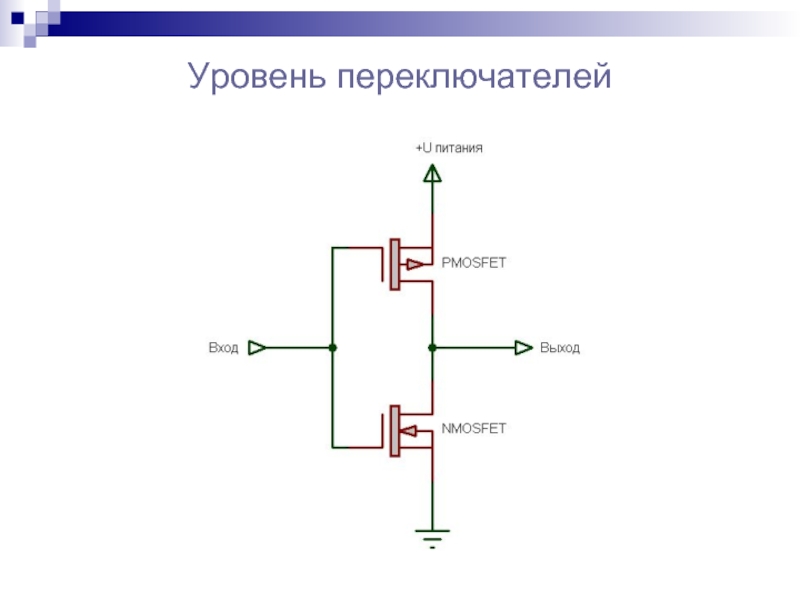

- 37. Уровень переключателей

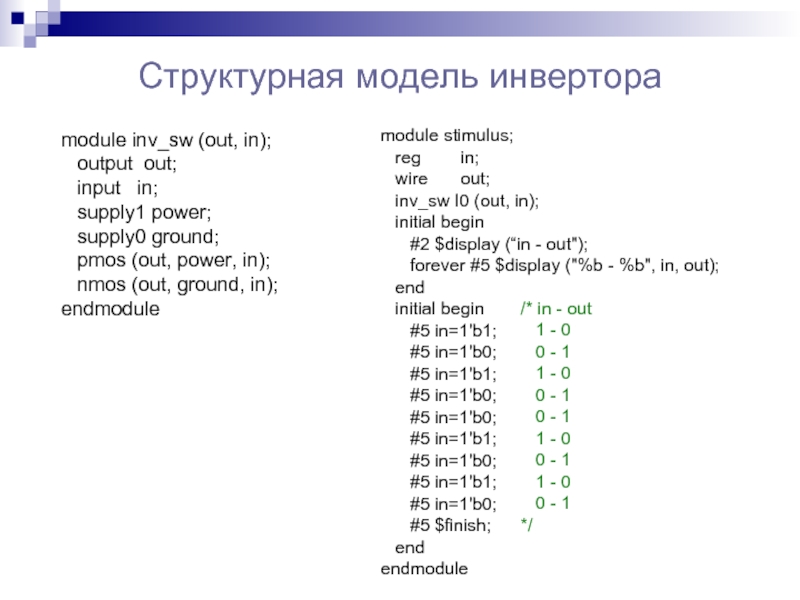

- 38. Структурная модель инвертора module inv_sw (out, in);

- 39. module mux(in0, in1, in2, in3, sel, out);

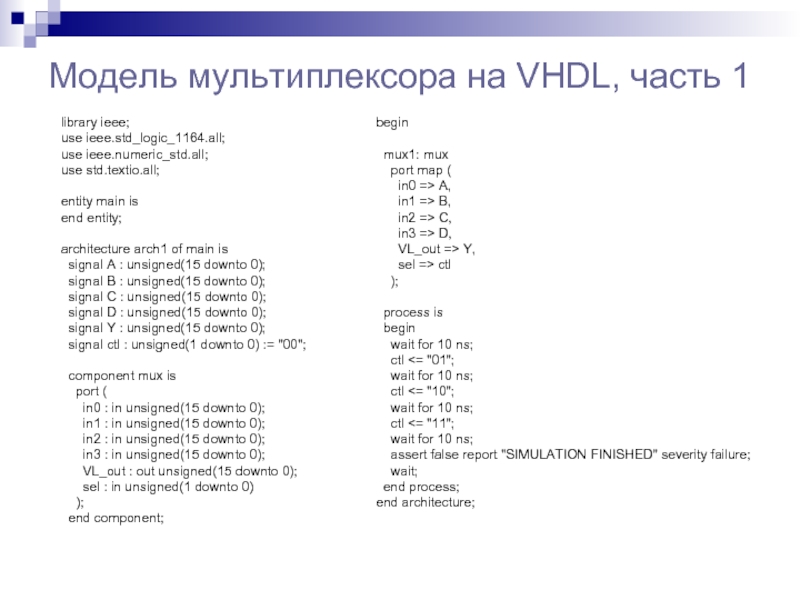

- 40. library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use

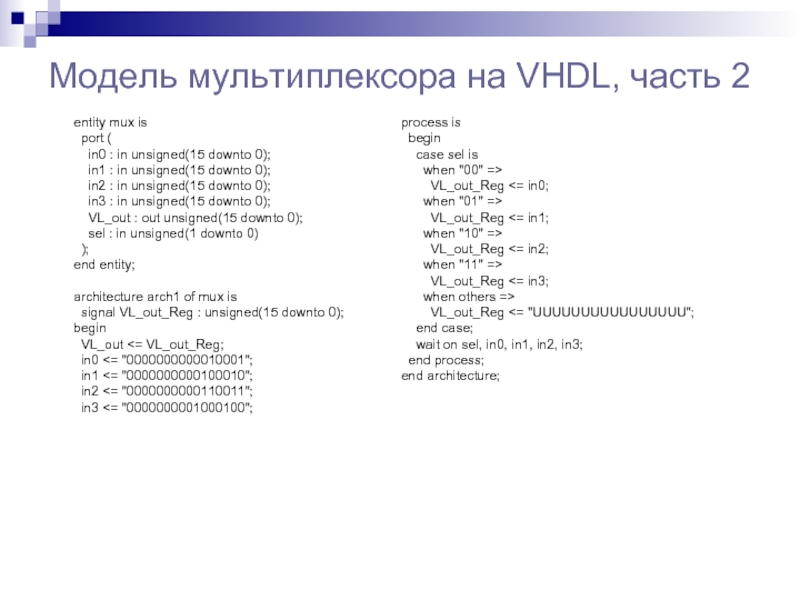

- 41. entity mux is port (

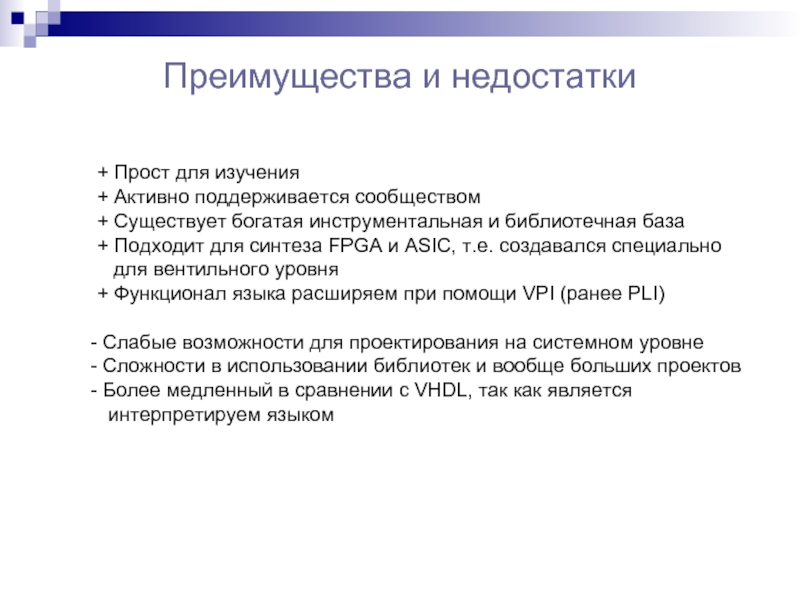

- 42. Преимущества и недостатки + Прост для изучения

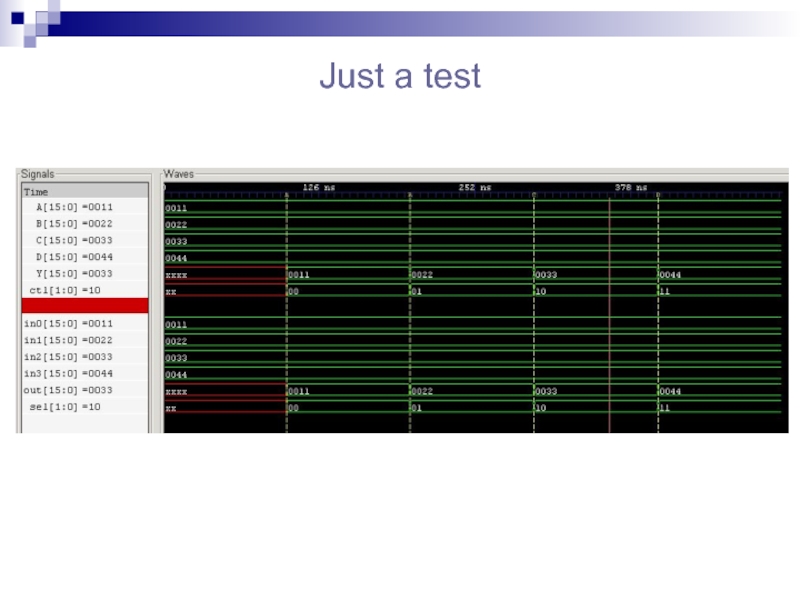

- 43. Just a test

Слайд 2Особенности языка Verilog

Вычисления управляются потоком данных

Есть поддержка параллельных процессов, событий

Существует понятие

Присутствуют типы данных, отражающие схемотехнические понятия

(сила сигнала, уровень сигнала, регистр, проводник и т.д.)

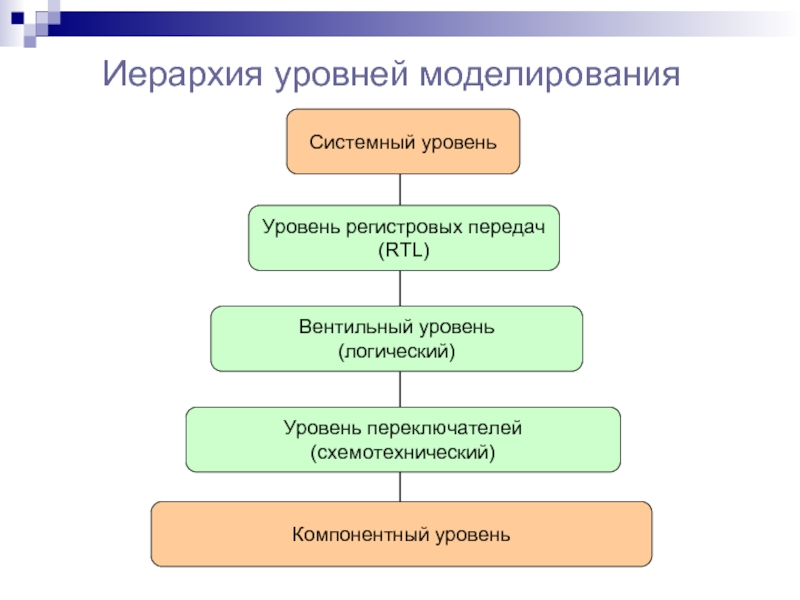

Слайд 3Иерархия уровней моделирования

Системный уровень

Уровень регистровых передач

(RTL)

Вентильный уровень

(логический)

Уровень переключателей

(схемотехнический)

Компонентный уровень

Слайд 4Области применения языка Verilog

Проектирование

СБИС

заказных микросхем (ASIC)

конфигураций перепрограммируемых логических ИС

Верификация

Слайд 5История создания языка

Verilog (Automated Integrated Design Systems/Gateway Design Automation)

Verilog (Cadence Design

Verilog-95 (IEEE 1364-1995, Open Verilog International)

Verilog-2001 (IEEE 1364-2001, Open Verilog International)

Verilog-2005 (IEEE 1364-2005, Accellera)

Время

IEEE 1364

IEEE P1800

2001

2005

1995

1983

1985

1990

Фил Мурби (Phil Moorby)

Слайд 7Лексические элементы

// Идентификаторы

reg store;

reg _store_;

reg 1store;

reg store_1;

reg Store_1;

reg store$;

reg $store;

/* Расширенные

reg \1st(*)re ;

reg \store1 ; // равно reg store1;

Слайд 8Лексические элементы

// Символьные и строковые литералы

“A” // символ

“0010” // строка из

“N123FE” // строка из 6 символов

“N

1 // переносы не допустимы

2

3

G”

// Константы

parameter tick=10; // допускается изменение из внешнего модуля

`define ONE 1’b1; // изменения не допускаются

Слайд 9Представление чисел

/*

- длина числа в битах

- основание системы исчисления:

префикс ’s для чисел со знаком

<основание><число>

<число>

<число><степень>

*/

12345

’b10_10

16’hFF34

1’b1111

10’hX

145e4

Слайд 10Алфавит моделирования

{0, 1, Z, X}

0 – логический ноль или результат сравнения

1 – логическая единица или результат сравнения true

Z – состояние высокого импеданса

Х – неопределенное состояние

Strength1: supply1, strong1, pull1, large1, weak1, medium1, small1, highz1

Strength0: supply0, strong0, pull0, large0, weak0, medium0, small0, highz0

Силы сигналов

Слайд 11Типы данных (соединения)

wire или tri – простой провод (соединение, связь, цепь);

wor

wand или triand – монтажное И;

tri0 – привязка к 0 в третьем состоянии;

tri1 – привязка к 1 в третьем состоянии;

supply0 – постоянный 0 (сила источника питания);

supply1 – постоянный 1 (сила источника питания);

trireg – сохранение последнего значения сигнала на шине

при установлении драйверов в третье состояние.

wire a, e, d;

wire [3:0] b;

wire (strong1, weak0) [32:0] c;

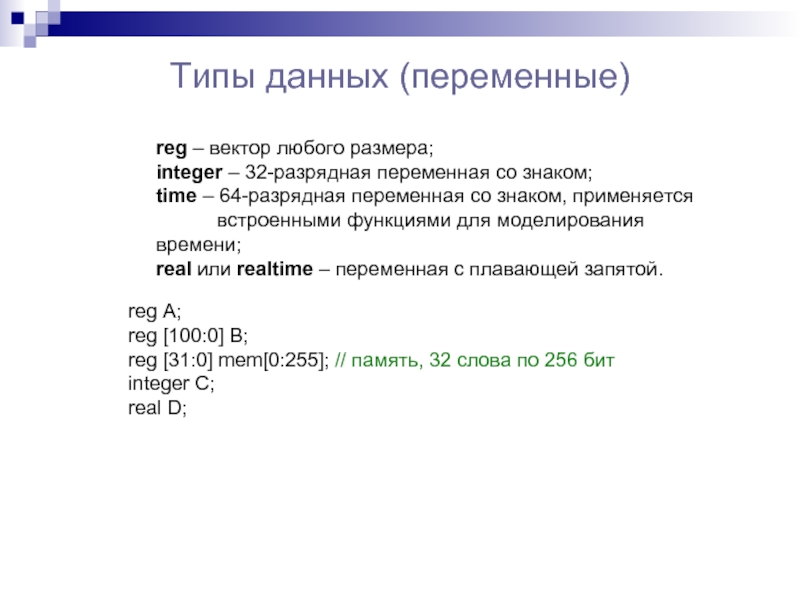

Слайд 12Типы данных (переменные)

reg – вектор любого размера;

integer – 32-разрядная переменная со

time – 64-разрядная переменная со знаком, применяется

встроенными функциями для моделирования времени;

real или realtime – переменная с плавающей запятой.

reg A;

reg [100:0] B;

reg [31:0] mem[0:255]; // память, 32 слова по 256 бит

integer C;

real D;

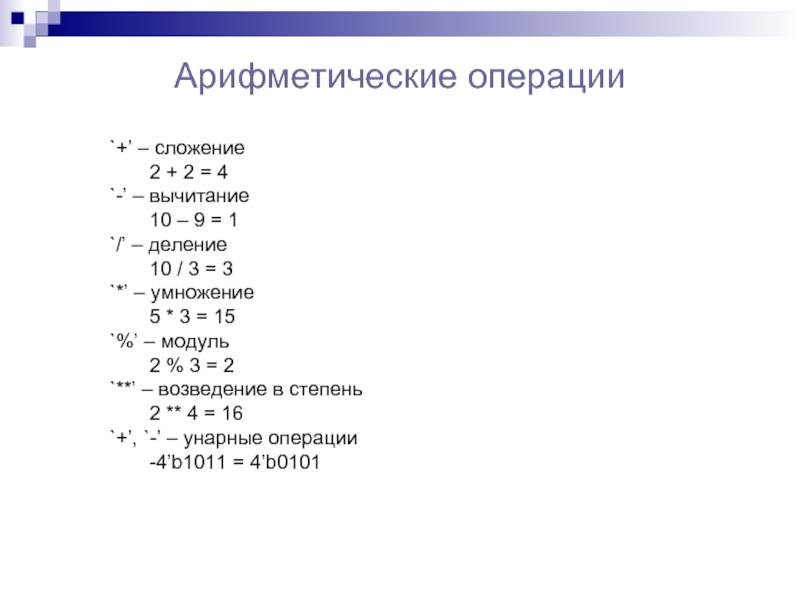

Слайд 13Арифметические операции

`+’ – сложение

2 + 2 = 4

`-’ – вычитание

10

`/’ – деление

10 / 3 = 3

`*’ – умножение

5 * 3 = 15

`%’ – модуль

2 % 3 = 2

`**’ – возведение в степень

2 ** 4 = 16

`+’, `-’ – унарные операции

-4’b1011 = 4’b0101

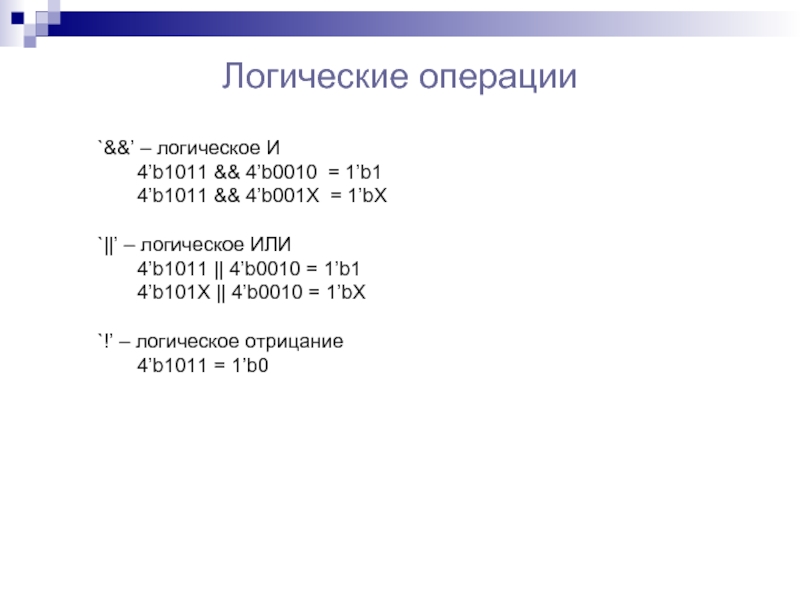

Слайд 14Логические операции

`&&’ – логическое И

4’b1011 && 4’b0010 = 1’b1

4’b1011 && 4’b001X

`||’ – логическое ИЛИ

4’b1011 || 4’b0010 = 1’b1

4’b101X || 4’b0010 = 1’bX

`!’ – логическое отрицание

4’b1011 = 1’b0

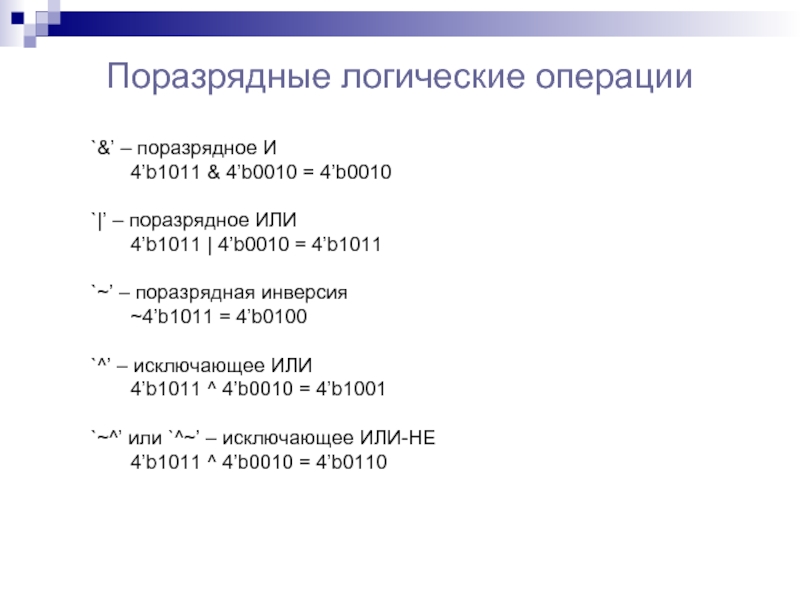

Слайд 15Поразрядные логические операции

`&’ – поразрядное И

4’b1011 & 4’b0010 = 4’b0010

`|’ –

4’b1011 | 4’b0010 = 4’b1011

`~’ – поразрядная инверсия

~4’b1011 = 4’b0100

`^’ – исключающее ИЛИ

4’b1011 ^ 4’b0010 = 4’b1001

`~^’ или `^~’ – исключающее ИЛИ-НЕ

4’b1011 ^ 4’b0010 = 4’b0110

Слайд 16Операции отношения

` 1’b0

`>’ – больше

4’b1011 >

`==’ – равно

10 == 10 => true

`!=’ – не равно

10 != 10 => false

`>=’ – больше либо равно

`<=’ – меньше либо равно

`===’ – тождественно равно

4’bX011 === 4’bX010

`!===’ – тождественно не равно

4’bX011 === 4’bX010

Слайд 17Операции свертки

`&’ – И всех разрядов

&4’b1101 => 1’b0

`|’ – ИЛИ

|4’b1101 => 1’b1

`~|’ – ИЛИ-НЕ всех разрядов

~|4’b1101 => 1’b0

`~&’ – И-НЕ всех разрядов

~&4’b1101 1’b1

`^’ – исключающее ИЛИ всех разрядов

^4’b1101 => 1’b1

`~^’ – исключающее ИЛИ-НЕ всех разрядов

~^4’b1101 => 1’b0

Слайд 18Операции сдвига

`’ –

4’b11_01 >> 2 => 4’b00_11

`<<<’ – арифметический сдвиг влево

4’sb1_101 << 1 => 4’sb1_010

`>>>’ – арифметический сдвиг вправо

4’sb1_101 >> 1 => 4’sb1_110

Слайд 19Операторы конкатенации и повторения

{переменная1, переменная2, … переменнаяN}

{a[3:0], b[10:7]} => вектор длиной

{3’b100, 2’b11} => 5’b10011

{N{переменная}}

{4{2’b01}} => 8’b01010101

{3{a}} => {a, a, a}

{4{a,b}} => {a, b, a, b, a, b, a, b}

Слайд 20Операторы выбора

? :

Amax = C > D ?

if (<условие>) <утверждение1> else <утверждение2>

if (index > 0)

if (rega > regb)

result = rega;

else // относится к ближайшему if

result = regb;

Слайд 21reg [31:0] instruction;

reg [2:0] aluOp;

casez (instruction[31:26])

6'b00????: aluOp = 3'b000;

6'b100???: aluOp

6'b101???: aluOp = 3'b010;

6'b1100??: aluOp = 3'b001;

6'b11010?: aluOp = 3'b100;

6'b110110: aluOp = 3'b101;

endcase

Операторы case, casex, casez

reg [1:0] sel;

reg [15:0] in0, in1, in2, in3, out;

case (sel)

2'b00: out = in0;

2'b01: out = in1;

2'b10: out = in2;

2'b11: out = in3;

default out = 16'bx;

endcase

reg [1:0] sel, flag;

reg [15:0] in0, in1, in2, in3, out;

casex (sel)

2'b00: out = in0;

2'b01: out = in1;

2'b0x,

2'b0z: out = flag ? 16'bx : 16'b0;

2'b10: out = in2;

2'b11: out = in3;

2'bx0, 2'bz0: out = flag ? 16'bx: 16'b0;

default out = 16'bx;

endcase

Слайд 22Оператор цикла repeat

parameter size = 8, longsize = 16;

reg [size:1] opa,

reg [longsize:1] result;

begin: mult

reg [longsize:1] shift_opa, shift_opb;

shift_opa = opa;

shift_opb = opb;

result = 0;

repeat (size)

begin

if (shift_opb[1])

result = result + shift_opa;

shift_opa = shift_opa << 1;

shift_opb = shift_opb >> 1;

end

end

Слайд 23Оператор цикла while

begin: count1s

reg [7:0] tempreg;

count = 0;

tempreg = rega;

while (tempreg)

begin

if

tempreg = tempreg >> 1;

end

end

Слайд 24Оператор цикла for

begin :init_mem

reg [7:0] tempi;

for (tempi = 0; tempi

memory[tempi] = 0;

end

begin : search_first

reg [7:0] tempi;

for (tempi = 0; tempi < memsize; tempi = tempi + 1)

begin: search

if (memory[tempi] == 0)

disable search;

end

end

Слайд 25Присваивание значений

Виды присваиваний

Непрерывные

(соединения)

Процедурные

(соединения, переменные)

Блокирующие

`=’

Не блокирующие

`

Слайд 26Непрерывное присваивание

wire [15:0] sum, a, b;

wire cin, cout;

assign

{cout,

Слайд 27Процедурное присваивание, LHS delay*

module block;

reg a, b, c, d, e, f;

initial

#10 a = 1; // модельное время = 10

#2 b = 0; // модельное время = 12

#4 c = 1; // модельное время = 16

end

initial begin

#10 d <= 1; // модельное время = 10

#2 e <= 0; // модельное время = 12

#4 f <= 1; // модельное время = 16

end

endmodule

* LHS delay = left hand side delay, задержка с левой стороны

Слайд 29Процедурное присваивание, RHS delay*

module block;

reg a, b, c, d, e, f;

initial

a = #10 1; // модельное время = 10

b = #2 0; // модельное время = 12

c = #4 1; // модельное время = 16

end

initial begin

d <= #10 1; // модельное время = 10

e <= #2 0; // модельное время = 2

f <= #4 1; // модельное время = 4

end

endmodule

* RHS delay = right hand side delay, задержка с правой стороны

Слайд 31(часть 1)

:vpi_time_precision - 11;

:vpi_module "system";

:vpi_module "v2005_math";

:vpi_module "va_math";

S_00672410 .scope module, "block1" "block1"

.timescale -9 -11;

v00672490_0 .var *"_s0", 0 0; Local signal

v006864F0_0 .var *"_s1", 0 0; Local signal

v00686548_0 .var *"_s2", 0 0; Local signal

v006865A0_0 .var "a", 0 0;

v006865F8_0 .var "b", 0 0;

v00686650_0 .var "c", 0 0;

v006866A8_0 .var "d", 0 0;

v00686728_0 .var "e", 0 0;

v00686780_0 .var "f", 0 0;

Процедурное присваивание, RHS delay

(часть 2)

.scope S_00672410;

T_0 ;

%set/v v00672490_0, 1, 1;

%movi 8, 1000, 11;

%ix/get 0, 8, 11;

%delayx 0;

%load/v 8, v00672490_0, 1;

%set/v v006865A0_0, 8, 1;

%set/v v006864F0_0, 0, 1;

%movi 8, 200, 9;

%ix/get 0, 8, 9;

%delayx 0;

%load/v 8, v006864F0_0, 1;

%set/v v006865F8_0, 8, 1;

%set/v v00686548_0, 1, 1;

%movi 8, 400, 10;

%ix/get 0, 8, 10;

%delayx 0;

%load/v 8, v00686548_0, 1;

%set/v v00686650_0, 8, 1;

%delay 100, 0;

%end;

.thread T_0;

.scope S_00672410;

(часть 3)

T_1 ;

%ix/load 0, 1;

%assign/v0 v006866A8_0, 1000, 1;

%ix/load 0, 1;

%assign/v0 v00686728_0, 200, 0;

%ix/load 0, 1;

%assign/v0 v00686780_0, 400, 1;

%end;

.thread T_1;

.scope S_00672410;

T_2 ;

%vpi_call 2 18 "$dumpfile", "block.vcd";

%vpi_call 2 19 "$dumpvars";

%end;

.thread T_2;

Слайд 32Управление задержками

#10 rega = regb;

#d rega = regb; // d определен

#((d+e)/2) rega = regb;

#regr regr = regr + 1; // задержка равна содержимому regr

reg enable, a, b;

initial begin

wait (!enable) #10 a = 1; // модельное время = 110

#10 b = 1; // модельное время = 120

end

initial

#100 enable = 0;

Слайд 33Управление задержками

a = #5 b;

// эквивалентно:

begin

temp = b;

#5 a = temp;

end

a

// эквивалентно:

begin

temp = b;

@(posedge clk) a = temp;

end

Слайд 34Параллельные и последовательные блоки

begin

#10 a = 1; // #10

end

begin

@trig r = 1; // @trig

#250 r = 0; // @trig+250

end

begin

@(posedge clock) q = 0; // posege clock

@(posedge clock) q = 1; // следующий

end // posege

fork

#30 a = 0; // #30

#10 a = 1; // #10

join

fork

@(posedge clock) q = 0;

@(posedge clock) w = 1;

join

begin

fork

@Aevent;

@Bevent;

join

areg = breg;

end

Слайд 35Системные функции

$monitor (“строка форматирования”, список переменных);

$monitor(“%h”, output);

$display и $write (“строка форматирования”,

$display(“Output in %h hex and %d decimal”, output, output);

$finish

#1000 $finish;

$dumpfile(“filename.vcd”); // Value Change Dump

$dumpvars;

$time // текущее модельное время

Слайд 36Модульная структура

// Файл lazy.v:

module lazy (out, in, clk);

parameter size = 1,

input [0:size-1] in;

input clk;

output [0:size-1] out;

reg [0:size-1] out;

always @(posedge clk)

#delay out = in;

endmodule

// Файл main.v:

`include lazy.v

module main;

reg clk;

wire [1:10] out_a, in_a;

wire [1:5] out_b, in_b;

lazy #(10, 15) mod_a (out_a, in_a, clk);

lazy mod_b (out_b, in_b, clk);

#800 $finish;

always

#100 clk = ~clk;

initial begin

clk = 0;

in_a = 10’b11111_01011;

in_b = 5’b10101;

end

endmodule

Слайд 38Структурная модель инвертора

module inv_sw (out, in);

output out;

input

supply1 power;

supply0 ground;

pmos (out, power, in);

nmos (out, ground, in);

endmodule

module stimulus;

reg in;

wire out;

inv_sw I0 (out, in);

initial begin

#2 $display (“in - out");

forever #5 $display ("%b - %b", in, out);

end

initial begin

#5 in=1'b1;

#5 in=1'b0;

#5 in=1'b1;

#5 in=1'b0;

#5 in=1'b0;

#5 in=1'b1;

#5 in=1'b0;

#5 in=1'b1;

#5 in=1'b0;

#5 $finish;

end

endmodule

/* in - out

1 - 0

0 - 1

1 - 0

0 - 1

0 - 1

1 - 0

0 - 1

1 - 0

0 - 1

*/

Слайд 39module mux(in0, in1, in2, in3, sel, out);

output [15:0] out;

reg [15:0] out;

input

input [15:0] in0, in1, in2, in3;

always @*

begin

case (sel)

2'b00: out = in0;

2'b01: out = in1;

2'b10: out = in2;

2'b11: out = in3;

default out = 16'bx;

endcase

end

endmodule

Поведенческая модель мультиплексора

module main();

reg [1:0] ctl;

wire [15:0] A, B, C, D;

wire [15:0] Y;

assign A = 'h11;

assign B = 'h22;

assign C = 'h33;

assign D = 'h44;

mux mux1(A, B, C, D, ctl, Y);

initial

begin

#10 ctl = 2'b00;

#10 ctl = 2'b01;

#10 ctl = 2'b10;

#10 ctl = 2'b11;

#10;

$finish;

end

endmodule

Слайд 40library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use std.textio.all;

entity main is

end entity;

architecture arch1 of

signal A : unsigned(15 downto 0);

signal B : unsigned(15 downto 0);

signal C : unsigned(15 downto 0);

signal D : unsigned(15 downto 0);

signal Y : unsigned(15 downto 0);

signal ctl : unsigned(1 downto 0) := "00";

component mux is

port (

in0 : in unsigned(15 downto 0);

in1 : in unsigned(15 downto 0);

in2 : in unsigned(15 downto 0);

in3 : in unsigned(15 downto 0);

VL_out : out unsigned(15 downto 0);

sel : in unsigned(1 downto 0)

);

end component;

Модель мультиплексора на VHDL, часть 1

begin

mux1: mux

port map (

in0 => A,

in1 => B,

in2 => C,

in3 => D,

VL_out => Y,

sel => ctl

);

process is

begin

wait for 10 ns;

ctl <= "01";

wait for 10 ns;

ctl <= "10";

wait for 10 ns;

ctl <= "11";

wait for 10 ns;

assert false report "SIMULATION FINISHED" severity failure;

wait;

end process;

end architecture;

Слайд 41entity mux is

port (

in0 : in unsigned(15 downto

in1 : in unsigned(15 downto 0);

in2 : in unsigned(15 downto 0);

in3 : in unsigned(15 downto 0);

VL_out : out unsigned(15 downto 0);

sel : in unsigned(1 downto 0)

);

end entity;

architecture arch1 of mux is

signal VL_out_Reg : unsigned(15 downto 0);

begin

VL_out <= VL_out_Reg;

in0 <= "0000000000010001";

in1 <= "0000000000100010";

in2 <= "0000000000110011";

in3 <= "0000000001000100";

process is

begin

case sel is

when "00" =>

VL_out_Reg <= in0;

when "01" =>

VL_out_Reg <= in1;

when "10" =>

VL_out_Reg <= in2;

when "11" =>

VL_out_Reg <= in3;

when others =>

VL_out_Reg <= "UUUUUUUUUUUUUUUU";

end case;

wait on sel, in0, in1, in2, in3;

end process;

end architecture;

Модель мультиплексора на VHDL, часть 2

Слайд 42Преимущества и недостатки

+ Прост для изучения

+ Активно поддерживается сообществом

+ Существует богатая

+ Подходит для синтеза FPGA и ASIC, т.е. создавался специально

для вентильного уровня

+ Функционал языка расширяем при помощи VPI (ранее PLI)

Слабые возможности для проектирования на системном уровне

Сложности в использовании библиотек и вообще больших проектов

Более медленный в сравнении с VHDL, так как является

интерпретируем языком

![Операторы конкатенации и повторения{переменная1, переменная2, … переменнаяN} {a[3:0], b[10:7]} => вектор длиной 8 бит {3’b100, 2’b11} =>](/img/tmb/2/184705/c267a735180d17673a9ab3cf8ad8f650-800x.jpg)

![reg [31:0] instruction;reg [2:0] aluOp;casez (instruction[31:26]) 6'b00????: aluOp = 3'b000; 6'b100???: aluOp = 3'b001; 6'b101???: aluOp =](/img/tmb/2/184705/45bf211d5cb6ef27d044133093bc62e2-800x.jpg)

![Оператор цикла repeatparameter size = 8, longsize = 16;reg [size:1] opa, opb;reg [longsize:1] result;begin: mult](/img/tmb/2/184705/b943edd3ff6f5a97a35737f8261d4fd8-800x.jpg)

![Оператор цикла whilebegin: count1s reg [7:0] tempreg; count = 0; tempreg = rega; while (tempreg) begin if (tempreg[0]) count = count](/img/tmb/2/184705/e8fd576900b4a30fbae8e4111e43f6b7-800x.jpg)

![Оператор цикла forbegin :init_mem reg [7:0] tempi; for (tempi = 0; tempi < memsize; tempi = tempi](/img/tmb/2/184705/8505f8251f53cc998f67796adb8ef17c-800x.jpg)

![Непрерывное присваиваниеwire [15:0] sum, a, b; wire cin, cout; assign {cout, sum} = a +](/img/tmb/2/184705/fd09049b448a78eddc735efb0243dd34-800x.jpg)

![Модульная структура// Файл lazy.v:module lazy (out, in, clk);parameter size = 1, delay = 1;input [0:size-1]](/img/tmb/2/184705/22339298cd533b0253dff908c7c3de69-800x.jpg)

![module mux(in0, in1, in2, in3, sel, out);output [15:0] out;reg [15:0] out;input [1:0] sel;input [15:0] in0,](/img/tmb/2/184705/7d4fe9e3a6418dc3de6359424f2b0ddf-800x.jpg)