- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Шифраторы и дешифраторы. Сумматоры и полусумматоры. (Тема 9) презентация

Содержание

- 1. Шифраторы и дешифраторы. Сумматоры и полусумматоры. (Тема 9)

- 2. Шифраторы, дешифраторы и преобразователи кодов Шифратор

- 3. Шифратор иногда называют «кодером» (от англ.

- 4. Если количество входов настолько велико, что в

- 5. Число входов и выходов в полном шифраторе

- 6. Рассмотрим пример построения шифратора для преобразования десятиразрядного

- 7. При этом предполагается, что сигнал, соответствующий логической

- 8. Представим на рис. 9.1 схему такого шифратора, используя элементы ИЛИ. Рисунок 9.1

- 9. Рисунок 9.2 На практике часто используют

- 10. Рассмотрим в качестве примера (рис. 9.3) шифратор

- 11. Шифратор имеет 9 инверсных входов, обозначенных через

- 12. Если на всех входах — логическая единица,

- 13. Например, если на входе PR1 — логический

- 14. Если на входе PR9 логический ноль, то

- 15. Основное назначение шифратора — преобразование номера источника

- 16. Для получения шифраторов с большим числом входов,

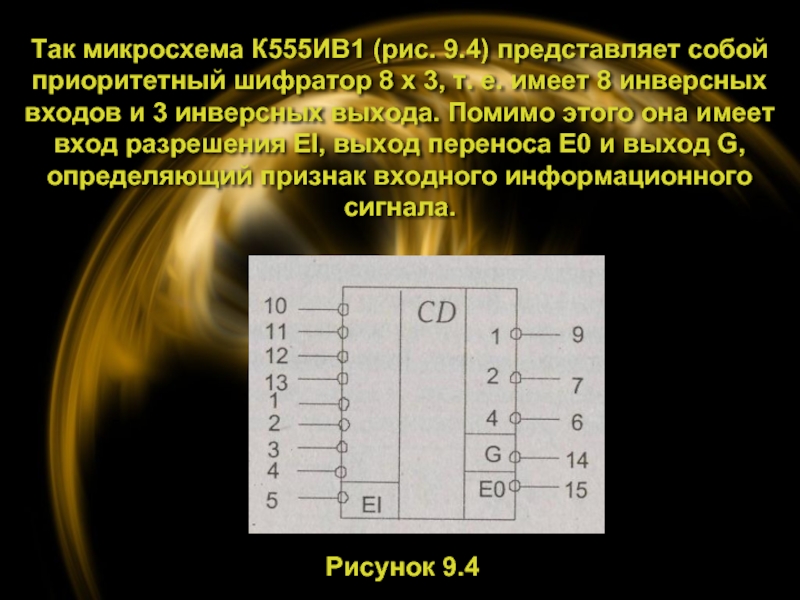

- 17. Так микросхема К555ИВ1 (рис. 9.4) представляет собой

- 18. Если на всех информационных входах логическая 1,

- 19. Если активизировать один из информационных входов

- 20. Если же микросхема не активизирована, т. е.

- 21. Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный

- 22. Число входов и выходов в так называемом

- 23. Дешифратор имеет 4 прямых входа, обозначенных через

- 24. Дешифратор имеет 10 инверсных выходов У0, ...

- 25. Например, если на всех входах — логические

- 26. Если на входе А2 — логическая единица,

- 27. Если на входе — двоичное число, превышающее

- 28. Помимо информационных имеется один или более входов,

- 29. Сумматоры и полусумматоры

- 30. Сумматоры

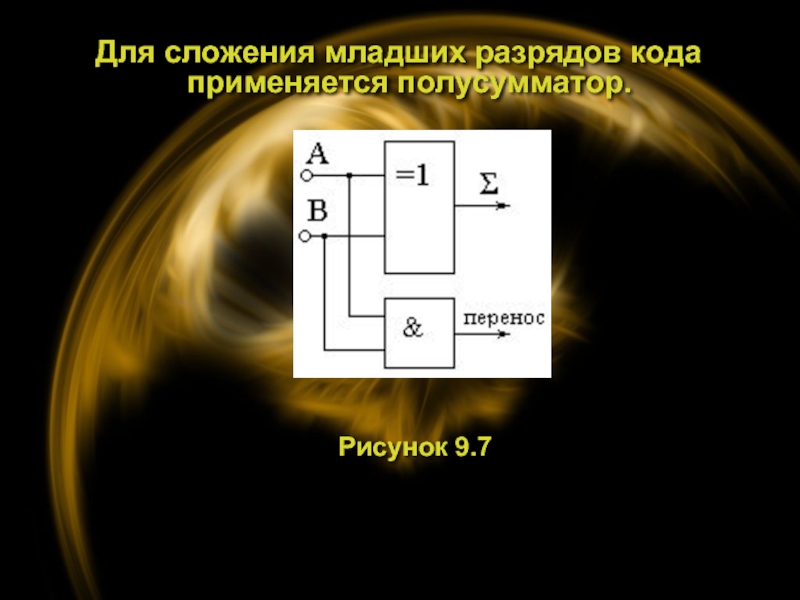

- 31. Для сложения младших разрядов кода применяется

- 32. Для сложения младших разрядов кода применяется

- 33. Во всех последующих разрядах может появиться

- 35. Сумматор последовательного типа Сумматор последовательного действия. Состоит

- 36. Мультиплексоры и демультиплексоры Мультиплексор - это устройство,

- 37. Мультиплексоры и демультиплексоры Демультиплексор - устройство, обратное

Слайд 2Шифраторы, дешифраторы и преобразователи кодов

Шифратор — это комбинационное устройство, преобразующее десятичные

Слайд 3Шифратор иногда называют

«кодером» (от англ. coder)

и используют, например, для

Слайд 4Если количество входов настолько велико, что в шифраторе используются все возможные

Слайд 5Число входов и выходов в полном шифраторе связано соотношением n =

Так, для преобразования кода кнопочного пульта в четырехразрядное двоичное число достаточно использовать лишь 10 входов, в то время как полное число возможных входов будет равно

16 (n = 24 = 16),

поэтому шифратор 10x4 (из 10 в 4) будет неполным.

Слайд 6Рассмотрим пример построения шифратора для преобразования десятиразрядного единичного кода (десятичных чисел

Слайд 7При этом предполагается, что сигнал, соответствующий логической единице, в каждый момент

У1 = X1 + Х3 + Х5 + Х7 + X9.

Аналогично получаем

У2 = X2 + X3 + X6 + X7

У3 = X4 + X5 + X6 + Х7, у4 = Х8+ Х9.

Слайд 9Рисунок 9.2

На практике часто используют шифратор с приоритетом. В таких

Слайд 10Рассмотрим в качестве примера (рис. 9.3) шифратор с приоритетом (приоритетный шифратор)

Рисунок 9.3

Слайд 11Шифратор имеет 9 инверсных входов, обозначенных через

PR1, ... , РР9.

Аббревиатура PR обозначает «приоритет».

Шифратор имеет четыре инверсных выхода

В1, ... , В8.

Аббревиатура В означает «шина» (от англ. bus). Цифры определяют значение активного уровня (нуля) в соответствующем разряде двоичного числа.

Например, В8 обозначает, что ноль на этом выходе соответствует числу 8.

Очевидно, что это неполный шифратор.

Слайд 12Если на всех входах — логическая единица, то на всех выходах

Слайд 13Например, если на входе PR1 — логический ноль, а на всех

В1 - О, В2 -1, В4 -1, В8 -1,

что соответствует числу 1 в инверсном коде (1110).

Слайд 14Если на входе PR9 логический ноль, то независимо от других входных

Слайд 15Основное назначение шифратора — преобразование номера источника сигнала в код

(например,

Слайд 16Для получения шифраторов с большим числом входов, т. е. наращивания размерности

Слайд 17Так микросхема К555ИВ1 (рис. 9.4) представляет собой приоритетный шифратор 8 х

Рисунок 9.4

Слайд 18Если на всех информационных входах логическая 1, то при подаче на

Слайд 19Если активизировать один из информационных входов

(подать на него логический 0),

на входе G — логический 0, являющийся признаком подачи входного сигнала,

а на выходе ЕО — логическая 1.

Слайд 20Если же микросхема не активизирована, т. е. на вход разрешения Е1

Слайд 21Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал,

Слайд 22Число входов и выходов в так называемом полном дешифраторе связано соотношением

Слайд 23Дешифратор имеет 4 прямых входа, обозначенных через А1, ..., A8. Аббревиатура

Рисунок 9.5

Слайд 24Дешифратор имеет 10 инверсных выходов У0, ... , У9. Цифры определяют

Слайд 25Например, если на всех входах — логические нули, то на выходе

У0— логический ноль, а на остальных выходах — логическая единица.

Слайд 26Если на входе А2 — логическая единица, а на остальных

входах

а на остальных выходах — логическая единица.

Слайд 27Если на входе — двоичное число, превышающее 9

(например, на всех

то на всех выходах — логическая единица.

Слайд 28Помимо информационных имеется один или более входов, называемых входами разрешения, или

Рисунок 9.6

Слайд 30Сумматоры

Сумматор – устройство, осуществляющее операцию сложения

двоичных

0+0 = 0,

0+1 = 1,

1+0 = 1 ,

1+1 = 0 и 1- перенос

Слайд 33 Во всех последующих разрядах может появиться перенос из предыдущих

Таблица 1 реализуется в виде более сложной комбинации логических элементов, которые образуют полный сумматор, содержащий 3 входа и 2 выхода.

Таблица 1 Алгоритм суммирования

Слайд 35Сумматор последовательного типа

Сумматор последовательного действия. Состоит из одноразрядного

сумматора, выход pi

Слайд 36Мультиплексоры и демультиплексоры

Мультиплексор - это устройство, которое осуществляет выборку одного из

A B Y

0 0 X0

0 1 X1

1 0 X2

1 1 X3