- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Микросхемы процессоров и шины презентация

Содержание

- 1. Микросхемы процессоров и шины

- 2. Микросхемы процессоров Выводы микросхемы ЦП:

- 3. Микросхемы процессоров Вызов команды: ЦП посылает

- 4. Микросхемы процессоров Производительность ЦП определяется: числом

- 5. Микросхемы процессоров Управляющие выводы позволяют регулировать

- 6. Микросхемы процессоров арбитраж шины [выводы арбитража

- 7. Микросхемы процессоров Цоколевка типичного

- 8. Компьютерные шины Шина – это несколько

- 9. Компьютерные шины Компьютерная система с несколькими

- 10. Компьютерные шины Протокол шины – правила

- 11. Компьютерные шины Как работают шины: некоторые

- 12. Компьютерные шины Задающие устройства обычно связаны

- 13. Ширина шины Ширина (количество адресных линий)

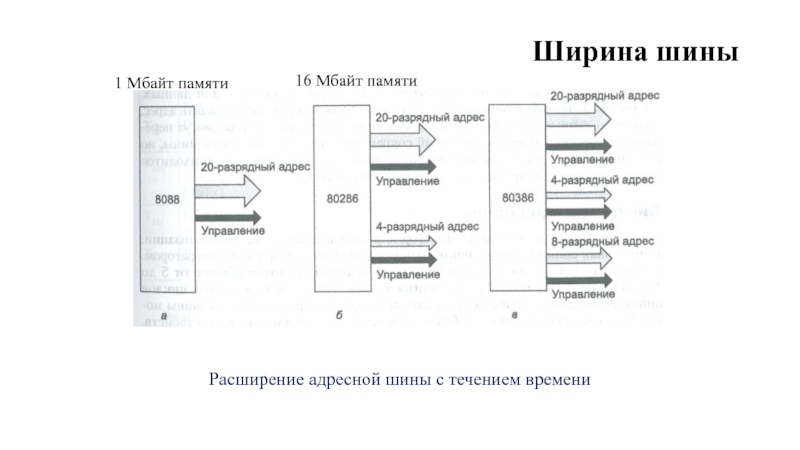

- 14. Ширина шины Расширение адресной шины с течением времени 1 Мбайт памяти 16 Мбайт памяти

- 15. Ширина шины Пропускную способность шины можно

- 16. Ширина шины Решение: мультиплексная шина.

- 17. Синхронизация шины В зависимости от их синхронизации

- 18. Временная диаграмма процесса считывания на синхронной шине

- 19. Временная диаграмма процесса считывания на синхронной шине

- 20. Синхронные шины (пример) Для чтения слова понадобится

- 21. Синхронные шины Plus: удобно использовать

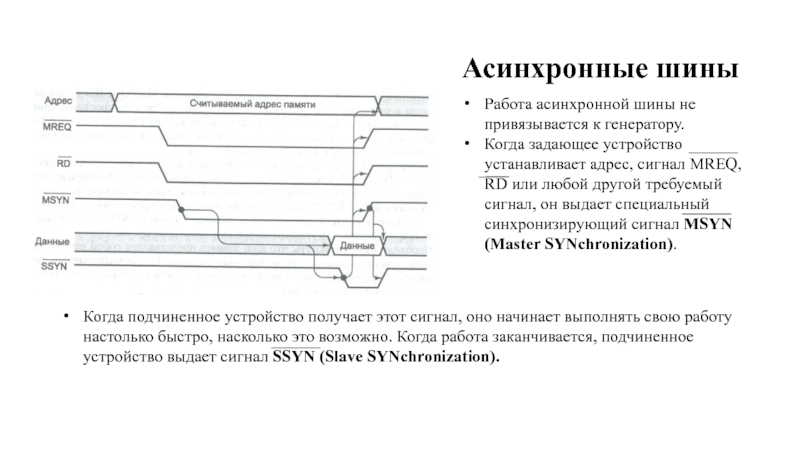

- 22. Асинхронные шины Работа асинхронной шины не привязывается

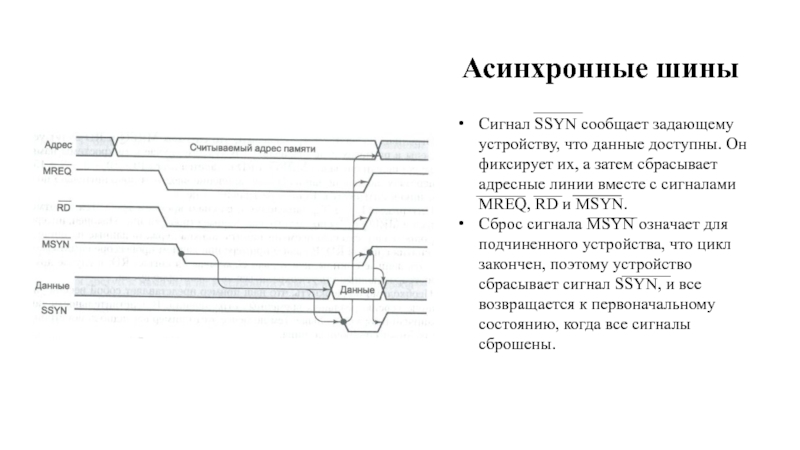

- 23. Асинхронные шины Сигнал SSYN сообщает задающему устройству,

- 24. Асинхронные шины Набор таких взаимообусловленных сигналов называется

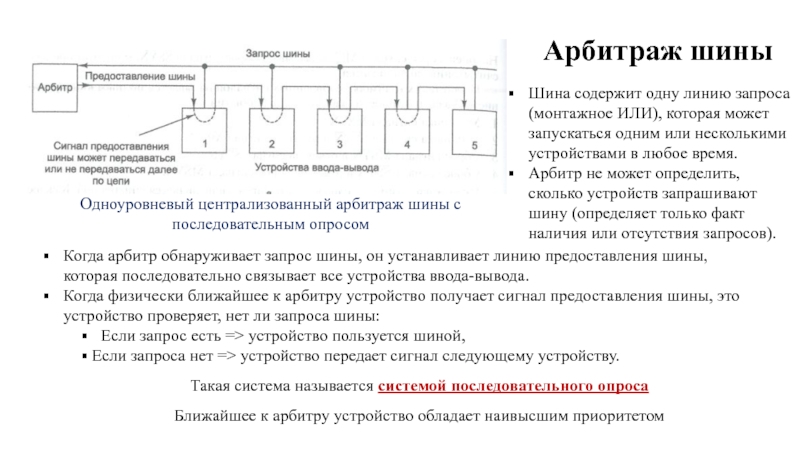

- 25. Арбитраж шины Что происходит, когда задающим устройством

- 26. Арбитраж шины Когда арбитр обнаруживает запрос шины,

- 27. Арбитраж шины Каждое устройство связано с одним

- 28. Арбитраж шины Некоторые арбитры содержат третью линию,

- 29. Арбитраж шины В системах, где память связана

- 30. Арбитраж шины Децентрализованный арбитраж шины Например,

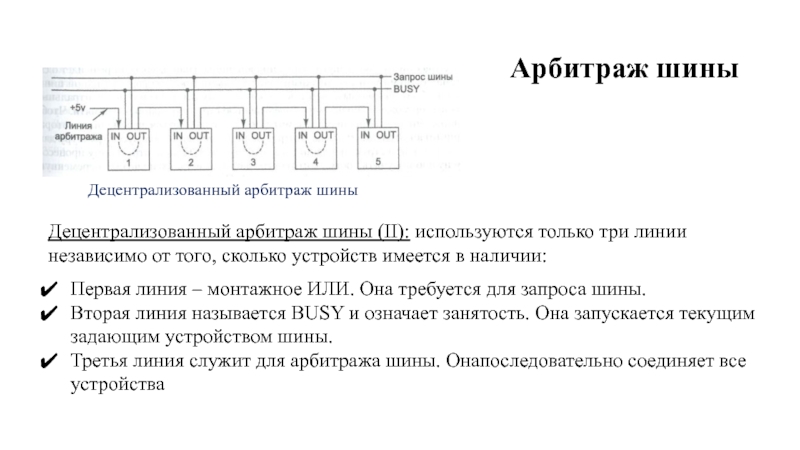

- 31. Арбитраж шины Децентрализованный арбитраж шины (II): используются

- 32. Арбитраж шины Когда шина не требуется ни

- 33. Принципы работы шины Передача блоками может быть

- 34. Принципы работы шины BLOCK – указывает, что

- 35. Принципы работы шины Системы с двумя или

- 36. Принципы работы шины Цикл обработки прерываний: Когда

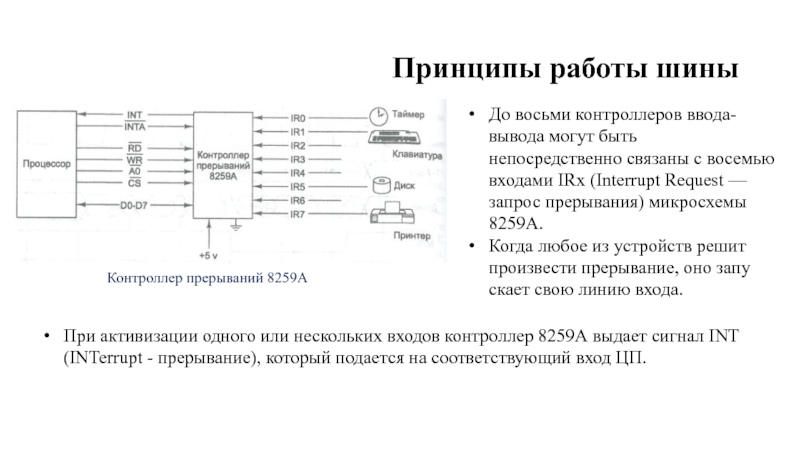

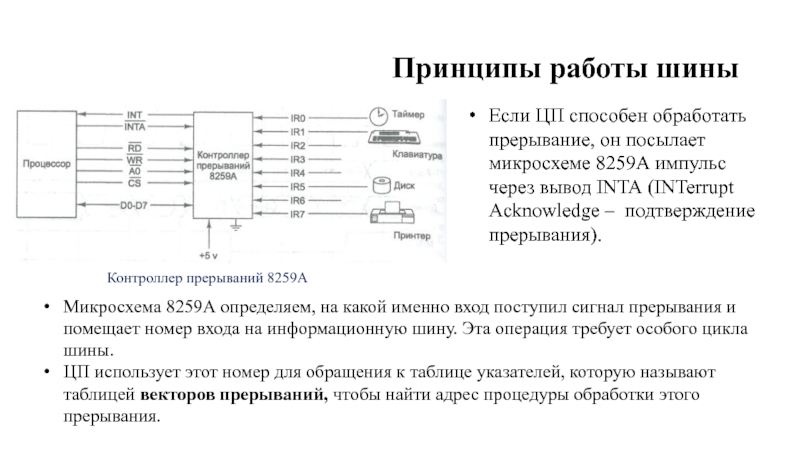

- 37. Принципы работы шины До восьми контроллеров ввода-вывода

- 38. Принципы работы шины Если ЦП способен обработать

- 39. Принципы работы шины Микросхема 8259А содержит несколько

- 40. Принципы работы шины При наличии более 8

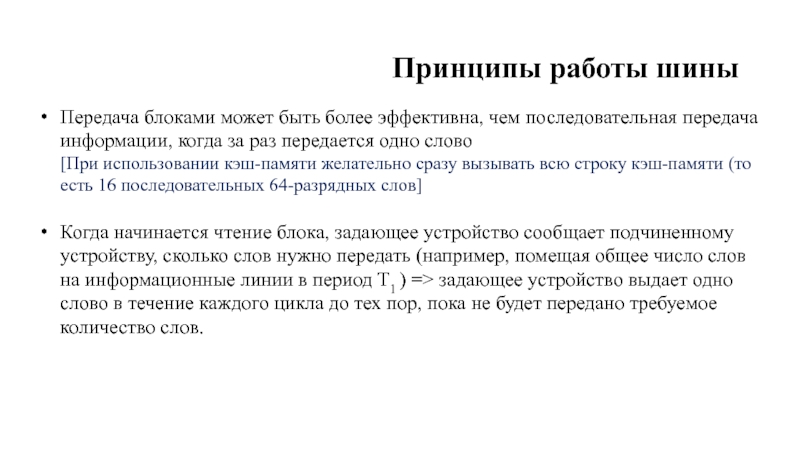

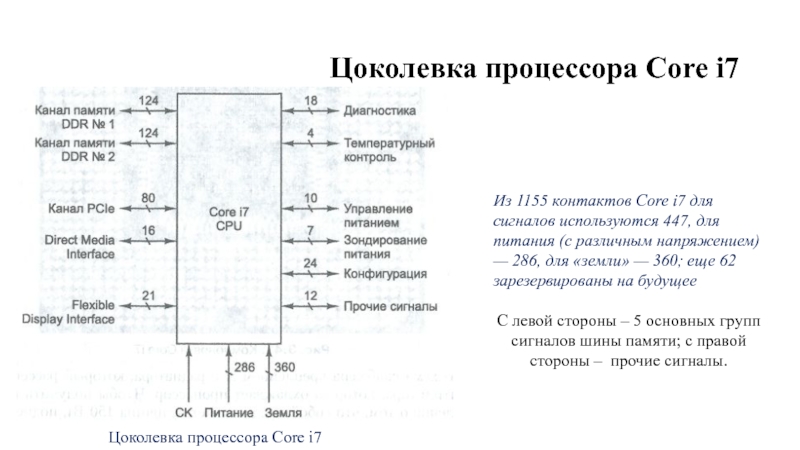

- 41. Цоколевка процессора Core i7 Из 1155 контактов

- 42. Цоколевка процессора Core i7 =>Каналы памяти DDR

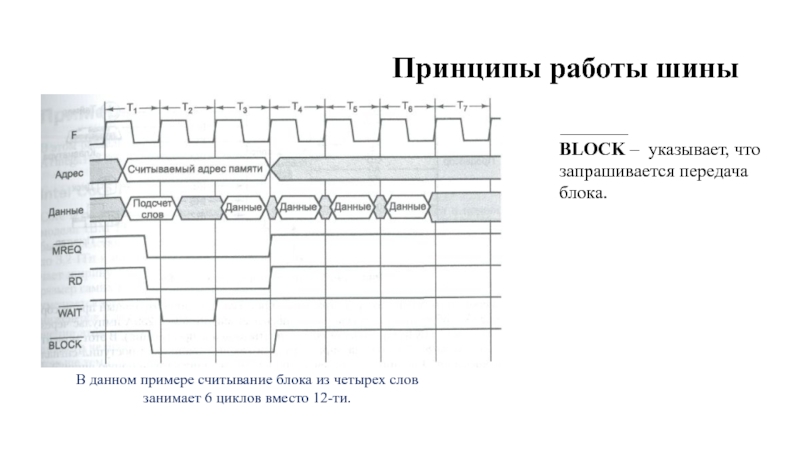

- 43. Цоколевка процессора Core i7 Прерывания Core i7:

- 44. Цоколевка процессора Core i7 Группа сигналов тактовой

- 45. Конвейерный режим шины памяти DDR3 процессора Core

- 46. Конвейерный режим шины памяти DDR3 процессора Core

- 47. Конвейерный режим шины памяти DDR3 процессора Core

- 48. Конвейерный режим шины памяти DDR3 процессора Core

- 49. Конвейерный режим шины памяти DDR3 процессора Core

- 50. Шина PCI PCI (Peripheral Component Interconnect —

- 51. Шина PCI Платы PCI отличаются: потребляемой мощностью

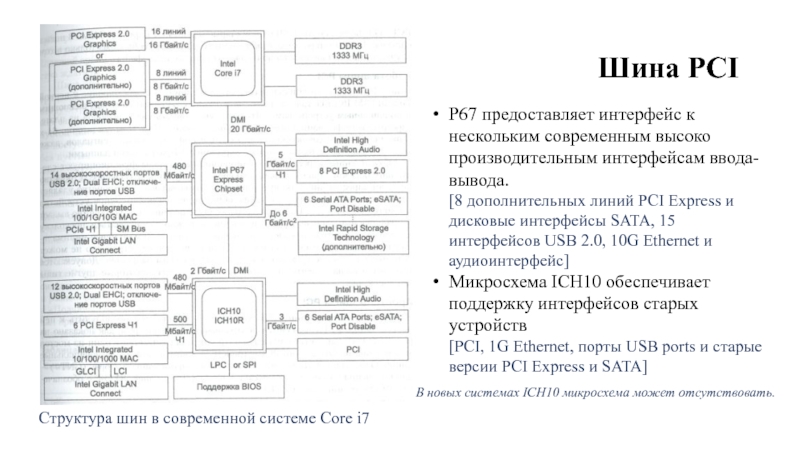

- 52. Шина PCI Структура шин в современной системе

- 53. Работа шины PCI Шины PCI являются синхронными

- 54. Арбитраж шины PCI REQ# – запрос шины

- 55. Арбитраж шины PCI Транзакции: шина предоставляется для

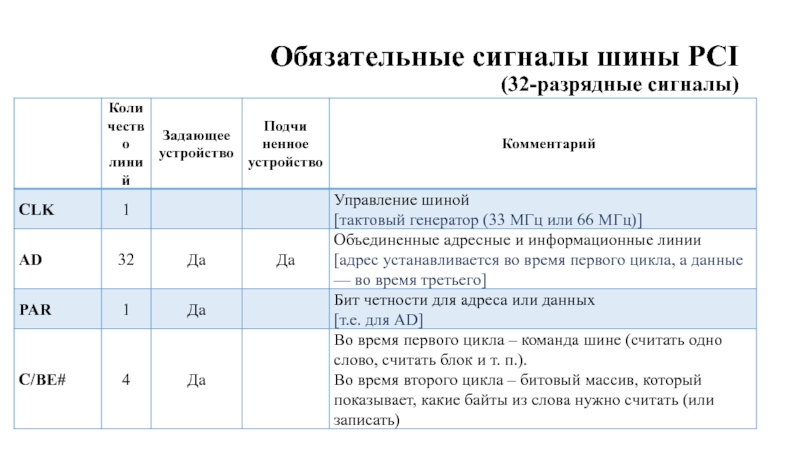

- 56. Обязательные сигналы шины PCI (32-разрядные сигналы)

- 57. Обязательные сигналы шины PCI (32-разрядные сигналы)

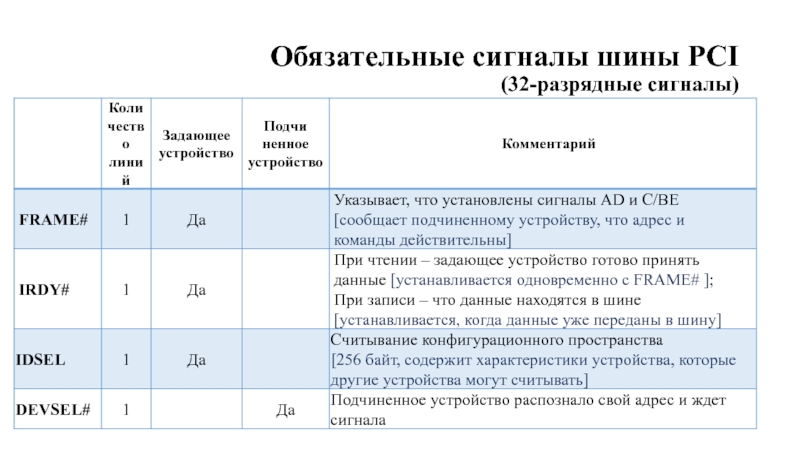

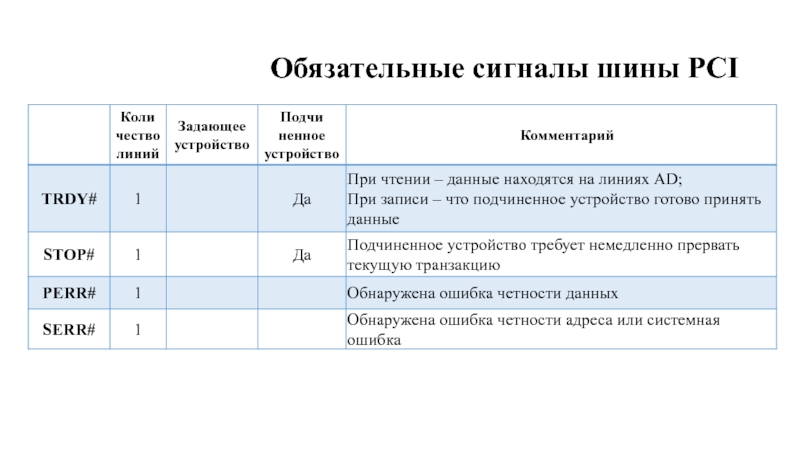

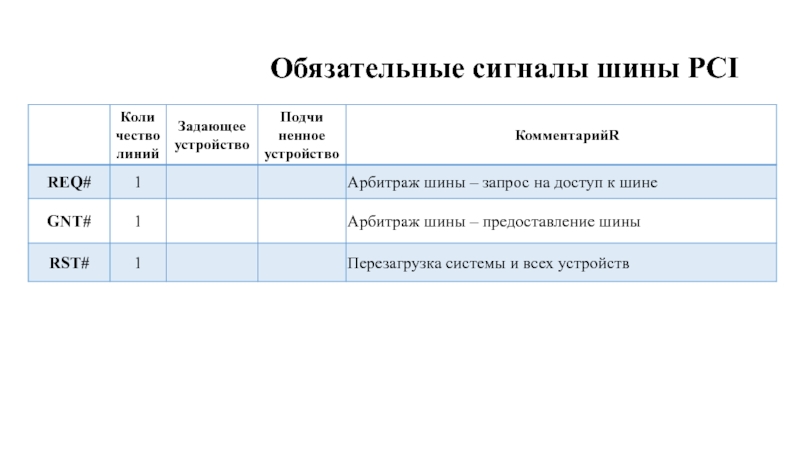

- 58. Обязательные сигналы шины PCI

- 59. Обязательные сигналы шины PCI

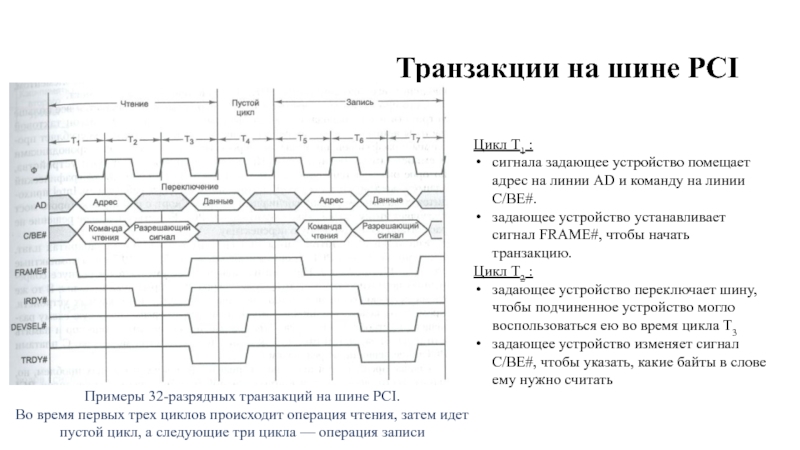

- 60. Транзакции на шине PCI Примеры 32-разрядных транзакций

- 61. Транзакции на шине PCI Цикл Т3 :

Слайд 2Микросхемы процессоров

Выводы микросхемы ЦП:

адресные

информационные

управляющие

Эти выводы связаны

ЦП обменивается информацией с памятью и УВВ, подавая сигналы на выводы и принимая сигналы на входы.

[Другого способа обмена информацией не существует]

Слайд 3Микросхемы процессоров

Вызов команды:

ЦП посылает в память адрес этой команды по адресным

Затем ЦП задействует одну или несколько линий управления, чтобы сообщить памяти, что ему нужно (например, прочитать слово).

Память помещает требуемое слово на информационные выводы ЦП и посылает сигнал о том, что это сделано.

Когда ЦП получает этот сигнал, он считывает слово и выполняет вызванную команду.

Слайд 4Микросхемы процессоров

Производительность ЦП определяется:

числом адресных выводов

m адресных выводов =>м/обратиться к

числом информационных выводов

n информационных выводов => м/ считывать (записывать) n-разрядное слово за одну операцию [ n =8, 32, 64]

ЦП с 8 информационными выводами понадобится 4 операции, чтобы считать 32-разрядное слово, а ЦП, имеющий 32 информационных вывода, может сделать ту же работу в рамках одной операции =>микросхема с 32 информационными выводами работает гораздо быстрее, но и стоит гораздо дороже

Слайд 5Микросхемы процессоров

Управляющие выводы позволяют регулировать и синхронизировать поток данных к процессору

Основные категорий управляющих выводов:

управление шиной

[выходы из ЦП в шину, позволяют сообщить, что процессор хочет считать (записать) информацию из памяти или сделать что-нибудь еще];

прерывания

[входы из УВВ в процессор. ЦП может дать сигнал УВВ начать операцию, а затем приступить к какому-нибудь другому действию, пока УВВ выполняет свою работу. Когда УВВ ее завершит, контроллер ввода-вывода посылает сигнал на один из выводов прерывания, чтобы прервать работу ЦП и заставить его обслужить УВВ (например, проверить ошибки ввода-вывода)]

Слайд 6Микросхемы процессоров

арбитраж шины [выводы арбитража нужны для регулировки потока информации в

сигналы сопроцессора [обмен информацией между процессором и сопроцессором, например, с графическими процессорами, процессорами для обработки вещественных данных и т. п. ];

cостояние [принимают информацию о состоянии];

разное [например, выводы для перезагрузки компьютера, обеспечение совместимость со старыми микросхемами устройств ввода-вывода].

Все процессоры содержат выводы для питания (обычно +1,2 В или +1,5 В), заземления и синхронизирующего сигнала (меандра).

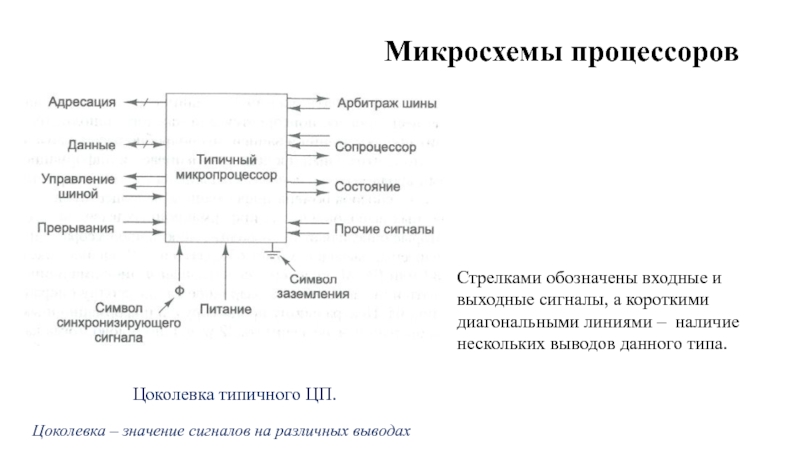

Слайд 7Микросхемы процессоров

Цоколевка типичного ЦП.

Цоколевка – значение сигналов на различных выводах

Стрелками

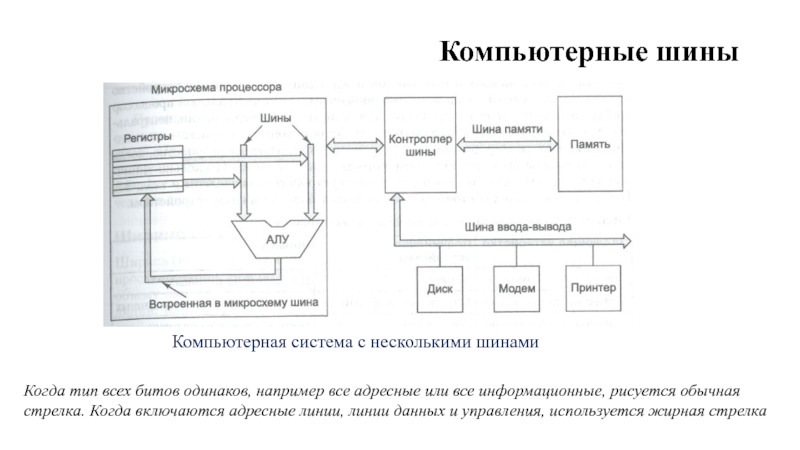

Слайд 8Компьютерные шины

Шина – это несколько проводников, соединяющих несколько устройств:

могут быть внутренними

могут быть внешними по отношению к процессору и связывать процессор с памятью или устройствами ввода-вывода.

Современные персональные компьютеры обычно содержат специальную шину между ЦП и памятью, системную,

и по крайней мере еще одну шину для УВВ

Слайд 9Компьютерные шины

Компьютерная система с несколькими шинами

Когда тип всех битов одинаков, например

Слайд 10Компьютерные шины

Протокол шины – правила о том, как работает шина и

Примеры шин :

Omnibus [PDP-8]

Unibus [PDP-11]

Multibus [8086]

VME [оборудование для физической лаборатории]

IBM PC [PC/XT]

ISA [PC/AT]

EISA [80386]

MicroChannel [PS/2]

Nubus [Macintosh]

PCI [различные персональные компьютеры]

SCSI [различные персональные компьютеры и рабочие станции]

Universal Serial Bus

[современные персональные компьютеры]

Fire Wire [бытовая электроника]

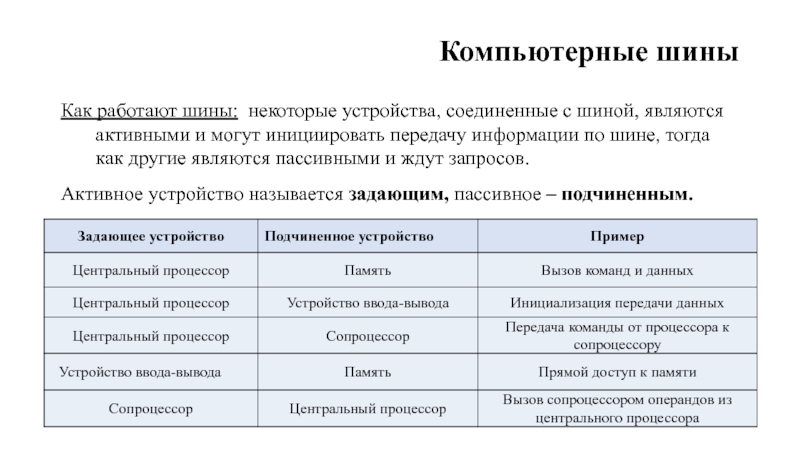

Слайд 11Компьютерные шины

Как работают шины: некоторые устройства, соединенные с шиной, являются активными

Активное устройство называется задающим, пассивное – подчиненным.

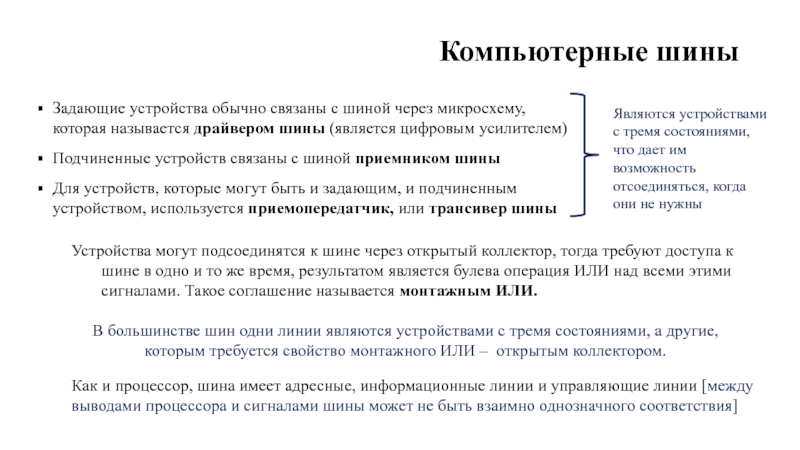

Слайд 12Компьютерные шины

Задающие устройства обычно связаны с шиной через микросхему, которая называется

Подчиненные устройств связаны с шиной приемником шины

Для устройств, которые могут быть и задающим, и подчиненным устройством, используется приемопередатчик, или трансивер шины

Являются устройствами с тремя состояниями, что дает им возможность отсоединяться, когда они не нужны

Устройства могут подсоединятся к шине через открытый коллектор, тогда требуют доступа к шине в одно и то же время, результатом является булева операция ИЛИ над всеми этими сигналами. Такое соглашение называется монтажным ИЛИ.

В большинстве шин одни линии являются устройствами с тремя состояниями, а другие, которым требуется свойство монтажного ИЛИ – открытым коллектором.

Как и процессор, шина имеет адресные, информационные линии и управляющие линии [между выводами процессора и сигналами шины может не быть взаимно однозначного соответствия]

Слайд 13Ширина шины

Ширина (количество адресных линий) шины – самый очевидный параметр при

Чем больше адресных линий содержит шина, тем к большему объему памяти может обращаться процессор [n адресных линий => 2п ячеек памяти]

Проблема:

для широких шин требуется больше проводов, чем для узких

широкие шины занимают больше физического пространства и для них нужны разъемы большего размера

Система с шиной, содержащей 64 адресные линии, и памятью в 232 байт будет стоить дороже, чем система с шиной, содержащей 32 адресные линии, и такой же памятью в 232 байт.

Слайд 15Ширина шины

Пропускную способность шины можно увеличить двумя способами:

сократить время цикла шины

увеличить ширину шины данных (то есть увеличить количество битов, передаваемых за цикл).

Проблемы в случае увеличения скорости работы шины:

сигналы на разных линиях передаются с разной скоростью, это явление называется расфазировкой шины, поэтому чем быстрее работает шина, тем больше расфазировка.

шина становится несовместимой с предыдущими версиями

Слайд 16Ширина шины

Решение: мультиплексная шина.

нет разделения на адресные и информационные линии

Может

В случае с отдельными линиями адреса и данные могут передаваться вместе.

Слайд 17Синхронизация шины

В зависимости от их синхронизации

Синхронная шина содержит линию, которая запускается

cигнал – меандр с частотой обычно от 5 до 133 МГц

любое действие шины занимает целое число, т. наз. циклов шины.

Асинхронная шина не содержит задающего генератора.

циклы шины могут быть произвольными и не обязательно одинаковыми для всех пар устройств.

Слайд 18Временная диаграмма процесса считывания на синхронной шине

Задающий генератор на

100 МГц,

Предполагаем, что считывание информации из памяти занимает 15 нс с момента установки адреса.

MREQ – указывает, что осуществляется доступ к памяти, а не к устройству ввода-вывода

RD – осуществляется чтение, а не запись

WAIT – ввод периодов ожидания

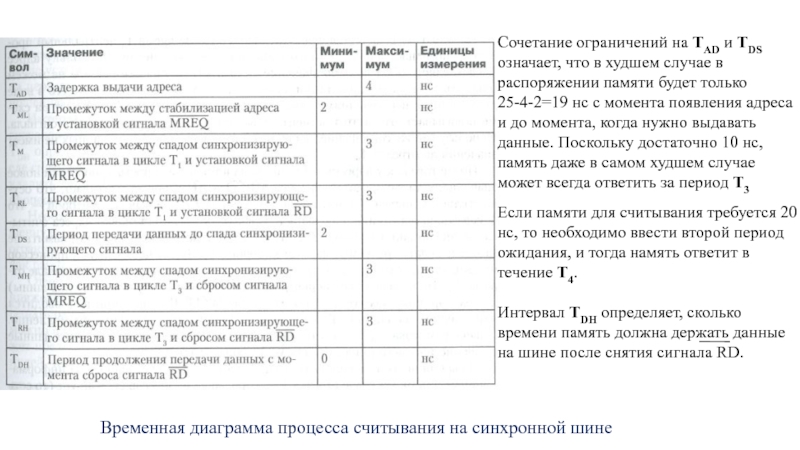

Слайд 19Временная диаграмма процесса считывания на синхронной шине

Сочетание ограничений на TAD и

25-4-2=19 нс с момента появления адреса и до момента, когда нужно выдавать данные. Поскольку достаточно 10 нс, память даже в самом худшем случае может всегда ответить за период Т3

Если памяти для считывания требуется 20 нс, то необходимо ввести второй период ожидания, и тогда намять ответит в течение Т4.

Интервал ТDH определяет, сколько времени память должна держать данные на шине после снятия сигнала RD.

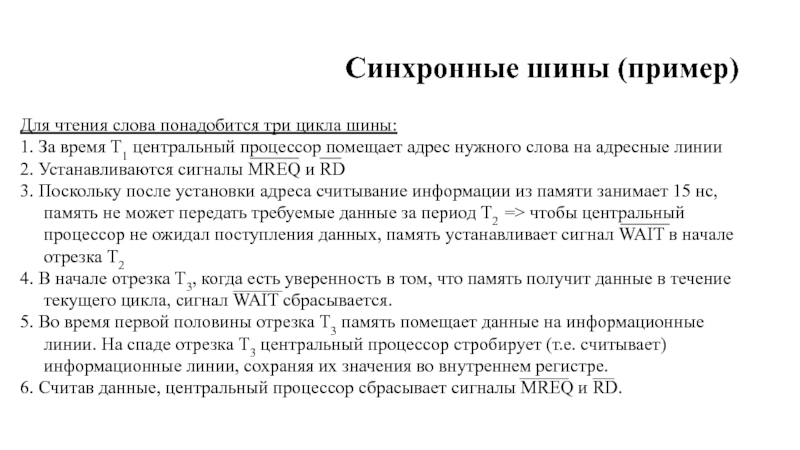

Слайд 20Синхронные шины (пример)

Для чтения слова понадобится три цикла шины:

1. За время

2. Устанавливаются сигналы MREQ и RD

3. Поскольку после установки адреса считывание информации из памяти занимает 15 нс, память не может передать требуемые данные за период Т2 => чтобы центральный процессор не ожидал поступления данных, память устанавливает сигнал WAIT в начале отрезка Т2

4. В начале отрезка Т3, когда есть уверенность в том, что память получит данные в течение текущего цикла, сигнал WAIT сбрасывается.

5. Во время первой половины отрезка Т3 память помещает данные на информационные линии. На спаде отрезка Т3 центральный процессор стробирует (т.е. считывает) информационные линии, сохраняя их значения во внутреннем регистре.

6. Считав данные, центральный процессор сбрасывает сигналы MREQ и RD.

Слайд 21Синхронные шины

Plus:

удобно использовать благодаря дискретным временным интервалам

синхронную систему построить

разработку синхронных шин вложено очень много ресурсов

Minus:

если процессор и память способны закончить передачу за 3,1 цикла, они вынуждены продлить ее до 4,0 цикла, поскольку неполные циклы запрещены

трудно делать технологические усовершенствования

если синхронная шина соединяет ряд устройств, одни из которых работают быстро, а другие медленно, шина подстраивается под самое медленное устройство, а более быстрые не могут использовать свой потенциал полностью

=> асинхронные шины, то есть шины без задающего генератора

Слайд 22Асинхронные шины

Работа асинхронной шины не привязывается к генератору.

Когда задающее устройство

Когда подчиненное устройство получает этот сигнал, оно начинает выполнять свою работу настолько быстро, насколько это возможно. Когда работа заканчивается, подчиненное устройство выдает сигнал SSYN (Slave SYNchronization).

Слайд 23Асинхронные шины

Сигнал SSYN сообщает задающему устройству, что данные доступны. Он фиксирует

Сброс сигнала MSYN означает для подчиненного устройства, что цикл закончен, поэтому устройство сбрасывает сигнал SSYN, и все возвращается к первоначальному состоянию, когда все сигналы сброшены.

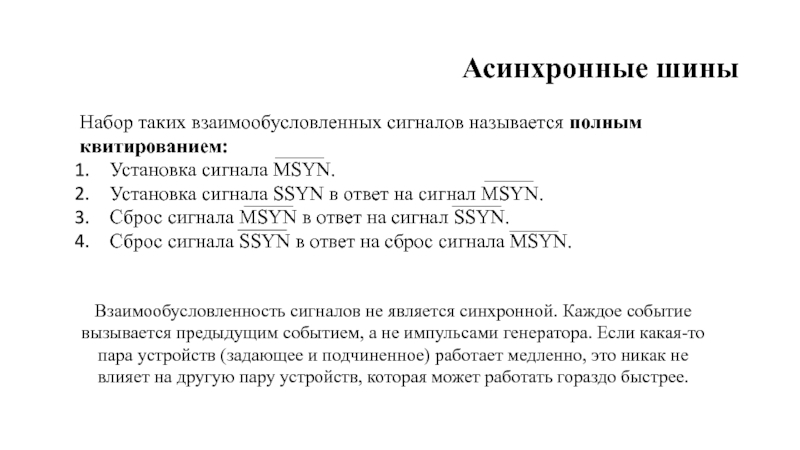

Слайд 24Асинхронные шины

Набор таких взаимообусловленных сигналов называется полным квитированием:

Установка сигнала MSYN.

Установка

Сброс сигнала MSYN в ответ на сигнал SSYN.

Сброс сигнала SSYN в ответ на сброс сигнала MSYN.

Взаимообусловленность сигналов не является синхронной. Каждое событие вызывается предыдущим событием, а не импульсами генератора. Если какая-то пара устройств (задающее и подчиненное) работает медленно, это никак не влияет на другую пару устройств, которая может работать гораздо быстрее.

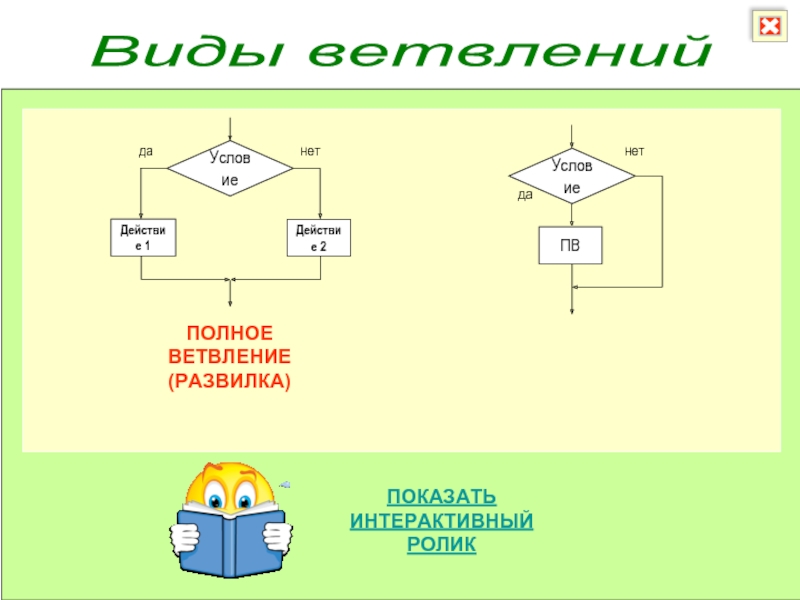

Слайд 25Арбитраж шины

Что происходит, когда задающим устройством шины становятся два или более

[микросхемы вода-вывода, cопроцессоры]

=> используется механизм – арбитраж шины.

Арбитраж:

централизованный

децентрализованный

Слайд 26Арбитраж шины

Когда арбитр обнаруживает запрос шины, он устанавливает линию предоставления шины,

Когда физически ближайшее к арбитру устройство получает сигнал предоставления шины, это устройство проверяет, нет ли запроса шины:

Если запрос есть => устройство пользуется шиной,

Если запроса нет => устройство передает сигнал следующему устройству.

Такая система называется системой последовательного опроса

Ближайшее к арбитру устройство обладает наивысшим приоритетом

Одноуровневый централизованный арбитраж шины с последовательным опросом

Шина содержит одну линию запроса (монтажное ИЛИ), которая может запускаться одним или несколькими устройствами в любое время.

Арбитр не может определить, сколько устройств запрашивают шину (определяет только факт наличия или отсутствия запросов).

Слайд 27Арбитраж шины

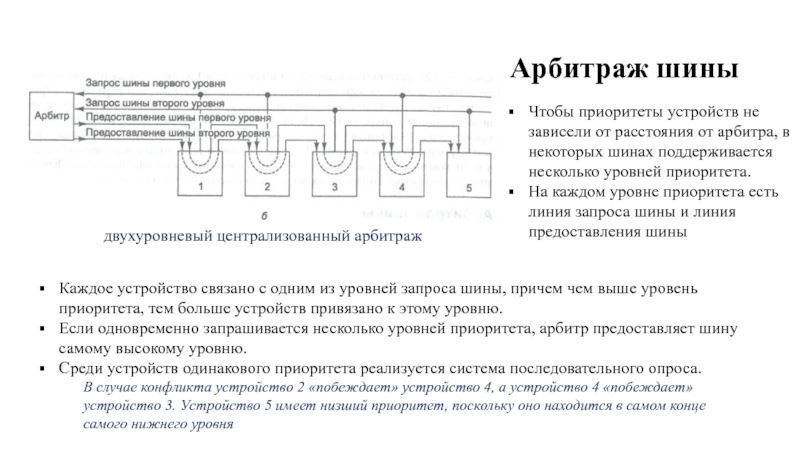

Каждое устройство связано с одним из уровней запроса шины, причем

Если одновременно запрашивается несколько уровней приоритета, арбитр предоставляет шину самому высокому уровню.

Среди устройств одинакового приоритета реализуется система последовательного опроса.

В случае конфликта устройство 2 «побеждает» устройство 4, а устройство 4 «побеждает» устройство 3. Устройство 5 имеет низший приоритет, поскольку оно находится в самом конце самого нижнего уровня

двухуровневый централизованный арбитраж

Чтобы приоритеты устройств не зависели от расстояния от арбитра, в некоторых шинах поддерживается несколько уровней приоритета.

На каждом уровне приоритета есть линия запроса шины и линия предоставления шины

Слайд 28Арбитраж шины

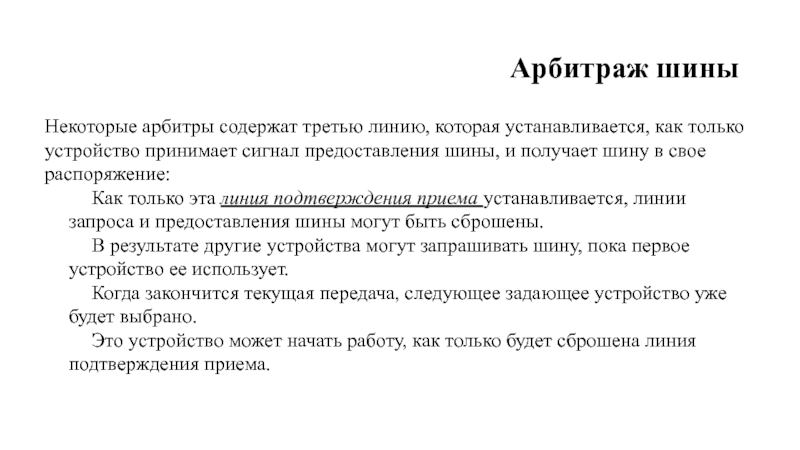

Некоторые арбитры содержат третью линию, которая устанавливается, как только устройство

Как только эта линия подтверждения приема устанавливается, линии запроса и предоставления шины могут быть сброшены.

В результате другие устройства могут запрашивать шину, пока первое устройство ее использует.

Когда закончится текущая передача, следующее задающее устройство уже будет выбрано.

Это устройство может начать работу, как только будет сброшена линия подтверждения приема.

Слайд 29Арбитраж шины

В системах, где память связана с главной шиной, ЦП должен

ЦП устанавливают самый низкий приоритет [ЦП всегда может подождать, а устройства ввода-вывода должны получить доступ к шине как можно быстрее, чтобы не потерять данные]

Во многих современных компьютерах для решения этой проблемы память помещается на одну шину, а устройства ввода-вывода – на другую, поэтому им не приходится завершать работу, чтобы предоставить доступ к шине.

Слайд 30Арбитраж шины

Децентрализованный арбитраж шины

Например, компьютер может содержать 16 приоритетных линий запроса

Minus: число устройств ограничивается числом линий запроса.

Слайд 31Арбитраж шины

Децентрализованный арбитраж шины (II): используются только три линии независимо от

Первая линия – монтажное ИЛИ. Она требуется для запроса шины.

Вторая линия называется BUSY и означает занятость. Она запускается текущим задающим устройством шины.

Третья линия служит для арбитража шины. Онапоследовательно соединяет все устройства

Децентрализованный арбитраж шины

Слайд 32Арбитраж шины

Когда шина не требуется ни одному из устройств, линия арбитража

Чтобы получить доступ к шине, устройство сначала проверяет, свободна ли шина и установлен ли сигнал арбитража IN.

Если сигнал IN не установлен, устройство не может стать задающим устройством шины. В этом случае оно сбрасывает сигнал OUT.

Если сигнал IN установлен, устройство также сбрасывает сигнал OUT, в результате чего следующее устройство не получает сигнала IN и, в свою очередь, сбрасывает сигнал OUT => все следующие по цепи устройства не получают сигнал IN и сбрасывают сигнал OUT.

В результате остается только одно устройство, у которого сигнал IN установлен, а сигнал OUT сброшен. Оно становится задающим устройством шины, устанавливает линию BUSY и сигнал OUT, после чего начинает передачу данных.

Слайд 33Принципы работы шины

Передача блоками может быть более эффективна, чем последовательная передача

Когда начинается чтение блока, задающее устройство сообщает подчиненному устройству, сколько слов нужно передать (например, помещая общее число слов на информационные линии в период Т1 ) => задающее устройство выдает одно слово в течение каждого цикла до тех пор, пока не будет передано требуемое количество слов.

Слайд 34Принципы работы шины

BLOCK – указывает, что запрашивается передача блока.

В данном

Слайд 35Принципы работы шины

Системы с двумя или несколькими ЦП на одной шине:

в

в памяти содержится переменная, которая принимает значение 0, когда ЦП использует структуру данных, и 1, когда структура данных не используется.

если центральному процессору нужно получить доступ к структуре данных, он должен считать переменную, и если она равна 0, придать ей значение 1.

В мультипроцессорных системах предусмотрен специальный цикл шины, который дает возможность любому процессору считать слово из памяти, проверить и изменить его, а затем записать обратно в память; весь этот процесс происходит без освобождения шины =>

другие ЦП не используют шину и не мешают работе первого процессора

Слайд 36Принципы работы шины

Цикл обработки прерываний:

Когда центральный процессор командует устройству ввода-вывода произвести

Для сигнала прерывания нужна шина.

Разрешение конфликтных ситуаций

несколько устройств одновременно захотят выполнить прерывание

каждому устройству приписывают определенный приоритет

для распределения приоритетов поддерживать централизованный арбитраж.

Стандартный, широко используемый интерфейс прерываний:

микросхема Intel 8259А

Слайд 37Принципы работы шины

До восьми контроллеров ввода-вывода могут быть непосредственно связаны с

Когда любое из устройств решит произвести прерывание, оно запускает свою линию входа.

Контроллер прерываний 8259А

При активизации одного или нескольких входов контроллер 8259А выдает сигнал INT (INTerrupt - прерывание), который подается на соответствующий вход ЦП.

Слайд 38Принципы работы шины

Если ЦП способен обработать прерывание, он посылает микросхеме 8259А

Контроллер прерываний 8259А

Микросхема 8259А определяем, на какой именно вход поступил сигнал прерывания и помещает номер входа на информационную шину. Эта операция требует особого цикла шины.

ЦП использует этот номер для обращения к таблице указателей, которую называют таблицей векторов прерываний, чтобы найти адрес процедуры обработки этого прерывания.

Слайд 39Принципы работы шины

Микросхема 8259А содержит несколько регистров, которые ЦП может считывать

Когда программное обеспечение обработало прерывание и готово получить следующее, оно записывает специальный код в один из регистров, который вызывает сброс сигнала INT микросхемой 8259А, если не появляется другое прерывание.

Регистры также могут записываться для того, чтобы перевести микросхему 8259А в один из нескольких режимов, и для выполнения некоторых других функций.

Слайд 40Принципы работы шины

При наличии более 8 устройств ввода-вывода, микросхемы 8259А могут

Контроллер-концентратор ввода/вывода Intel ICH10 I/O, одна из микросхем чипсета Core i7, содержат два контроллера прерываний 8259А.

ICH10 имеет 15 внешних прерываний - на 1 меньше 16 прерываний двух контроллеров 8259А, так как одно из прерываний используется для каскадного подключения второго контроллера 8259А.

Слайд 41Цоколевка процессора Core i7

Из 1155 контактов Core i7 для сигналов используются

С левой стороны – 5 основных групп сигналов шины памяти; с правой стороны – прочие сигналы.

Цоколевка процессора Core i7

Слайд 42Цоколевка процессора Core i7

=>Каналы памяти DDR № 1, № 2: используются

=> Интерфейс PCI: предназначен для прямой связи периферийных устройств с центральным процессором Core i7.

=> Интерфейс DMI (Direct Media Interface): используется для связи процессора Core i7 с комплектным чипсетом

Чипсет Core i7 состоит из микросхем:

Р67 – обеспечивает поддержку интерфейсов SATA, USB, аудио, PCIe и флэш-памяти

ICH10 – обеспечивает поддержку наследных интерфейсов, включая интерфейс PCI и функциональность контроллера прерываний 8259А

Слайд 43Цоколевка процессора Core i7

Прерывания Core i7:

может осуществлять тем же способом, что

Группа сигналов температурного контроля позволяет процессору оповещать окружающие устройства об опасности перегрева (t>130 °С).

Если внутренние датчики обнаруживают, что процессор вскоре перегреется, они запускают терморегуляцию — механизм, быстро снижающий выделение тепла за счет того, что процессор работает только на каждом N-м такте. Чем выше значение N, тем сильнее замедляется процессор и тем быстрее он остывает

Слайд 44Цоколевка процессора Core i7

Группа сигналов тактовой частоты отвечает за определение частоты

Группа диагностических сигналов предназначена для тестирования и отладки систем согласно стандарту IEEE 1149.1 JTAG.

Группа сигналов инициализации обслуживает загрузку (запуск) системы.

Сигнал СК используется процессором для генерирования различных тактовых импульсов с частотой, кратной или дробной по отношению к частоте системного генератора. Для этого применяется устройство, называемое системой автоподстройки по задержке, или DLL (Delay-Locked Loop)

Слайд 45Конвейерный режим шины памяти DDR3 процессора Core i7

Запросы к памяти состоят

Фаза активизации (ACT) памяти «открывает» строку динамической памяти, делая ее готовой для последующих обращений.

2. В фазе чтения (READ) или записи (WRITE) могут происходить обращения к отдельным словам открытой строки динамической памяти или к последовательным словам текущей строки динамической памяти с использованием пакетного режима.

3. Фаза предзаряда (PCHRG) «закрывает» текущую строку динамической памяти и готовит память к следующей команде активизации.

Слайд 46Конвейерный режим шины памяти DDR3 процессора Core i7

Идея работы:

Динамическая память

Банк представляет собой блок динамической памяти, к которому процессор может обращаться параллельно с другими банками, даже находящимися на той же микросхеме.

Слайд 47Конвейерный режим шины памяти DDR3 процессора Core i7

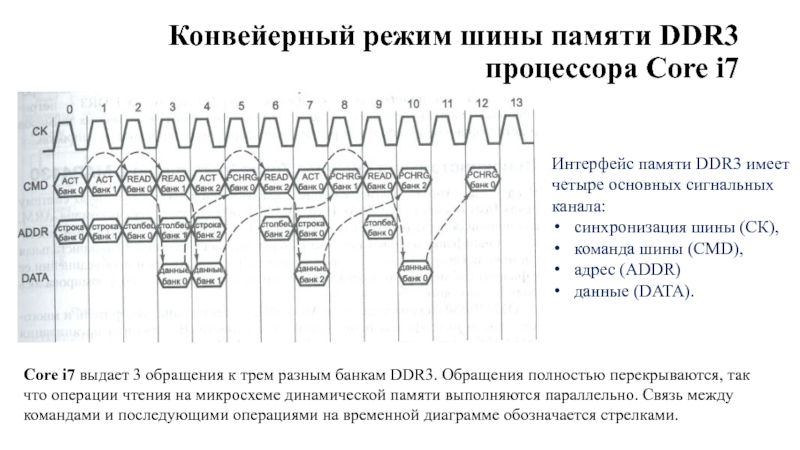

Core i7 выдает 3

Интерфейс памяти DDR3 имеет четыре основных сигнальных канала:

синхронизация шины (СК),

команда шины (CMD),

адрес (ADDR)

данные (DATA).

Слайд 48Конвейерный режим шины памяти DDR3 процессора Core i7

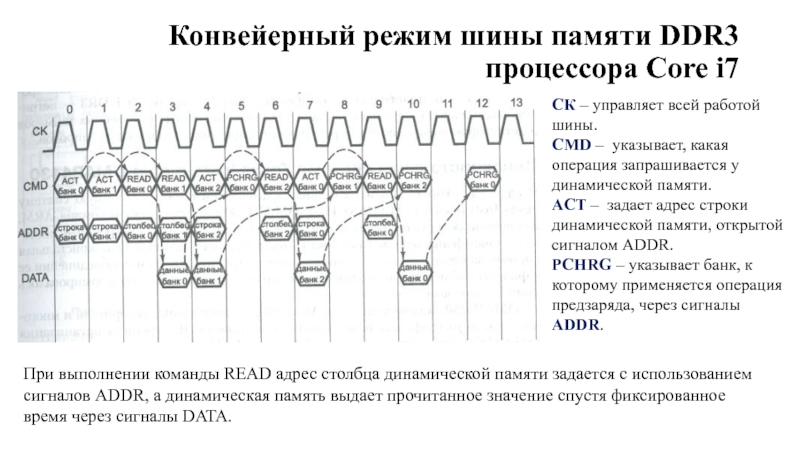

СК – управляет всей

CMD – указывает, какая операция запрашивается у динамической памяти.

ACT – задает адрес строки динамической памяти, открытой сигналом ADDR.

PCHRG – указывает банк, к которому применяется операция предзаряда, через сигналы ADDR.

При выполнении команды READ адрес столбца динамической памяти задается с использованием сигналов ADDR, а динамическая память выдает прочитанное значение спустя фиксированное время через сигналы DATA.

Слайд 49Конвейерный режим шины памяти DDR3 процессора Core i7

В нашем примере:

=> команда

=> параллелизм запросов памяти проявляется в перекрытии запросов READ к разным банкам динамической памяти. Первые два обращения READ к банкам 0 и 1 полностью перекрываются, производя результаты в циклах шины 3 и 4 соответственно. Обращение к банку 2 частично перекрывается с первым обращением к банку 1, и наконец, второе чтение из банка 0 частично перекрывается с обращением к банку 2.

Слайд 50Шина PCI

PCI (Peripheral Component Interconnect — взаимодействие периферийных компонентов),

[1990 г, компания

Шина PCI несовместима со всеми старыми платами ISA => Intel решила разрабатывать компьютеры с тремя и более шипами

Архитектура типичной системы первых поколений Pentium. [толщина линий шины обозначает ее пропускную способность =>

чем толще линия, тем выше пропускная способность]

ISA – 16,7 Мбайт/с

EISA – 33,3 Мбайт/с

PCI –133 Мбайт/с =>528 Мбайт/с

Слайд 51Шина PCI

Платы PCI отличаются:

потребляемой мощностью

[cтарые компьютеры обычно используют напряжение 5

разрядностью [32-разрядные платы содержат 120 выводов; 64-разрядные платы содержат те же 120 выводов плюс 64 дополнительных вывода]

синхронизацией [могут работать на частоте либо 33 МГц, либо 66 МГц, контакты идентичны, один из выводов связывается либо с источником питания, либо с землей]

Слайд 52Шина PCI

Структура шин в современной системе Core i7

Р67 предоставляет интерфейс к

Микросхема ICН10 обеспечивает поддержку интерфейсов старых устройств [PCI, 1G Ethernet, порты USB ports и старые версии PCI Express и SATA]

В новых системах ICH10 микросхема может отсутствовать.

Слайд 53Работа шины PCI

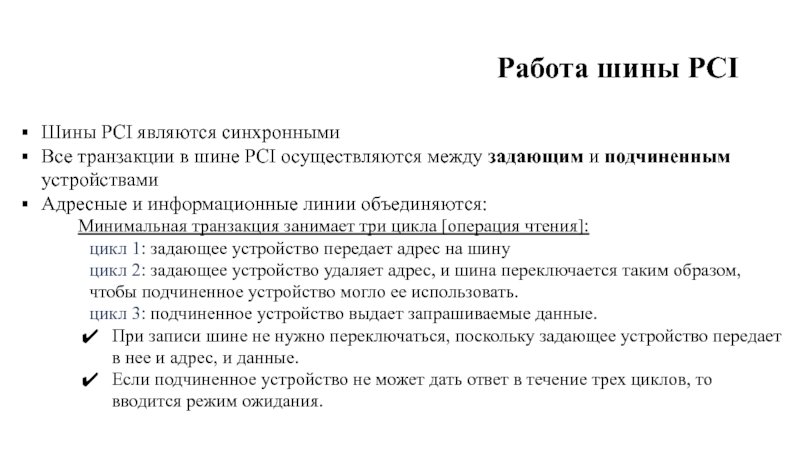

Шины PCI являются синхронными

Все транзакции в шине PCI осуществляются

Адресные и информационные линии объединяются:

Минимальная транзакция занимает три цикла [операция чтения]:

цикл 1: задающее устройство передает адрес на шину

цикл 2: задающее устройство удаляет адрес, и шина переключается таким образом, чтобы подчиненное устройство могло ее использовать.

цикл 3: подчиненное устройство выдает запрашиваемые данные.

При записи шине не нужно переключаться, поскольку задающее устройство передает в нее и адрес, и данные.

Если подчиненное устройство не может дать ответ в течение трех циклов, то вводится режим ожидания.

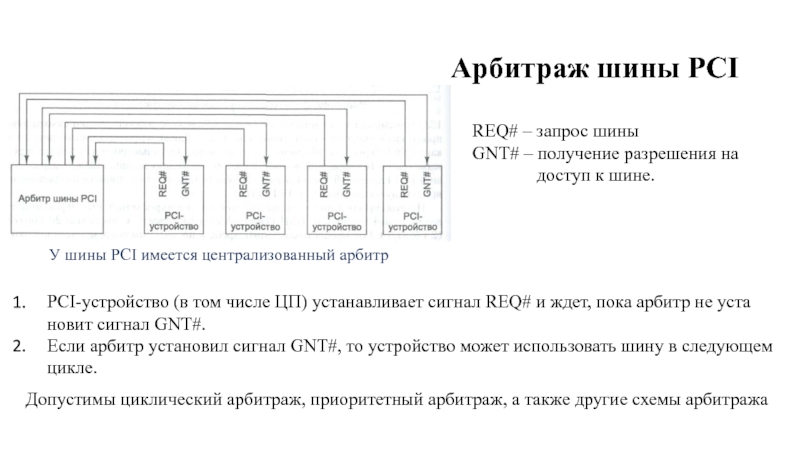

Слайд 54Арбитраж шины PCI

REQ# – запрос шины

GNT# – получение разрешения на доступ

У шины PCI имеется централизованный арбитр

PCI-устройство (в том числе ЦП) устанавливает сигнал REQ# и ждет, пока арбитр не установит сигнал GNT#.

Если арбитр установил сигнал GNT#, то устройство может использовать шину в следующем цикле.

Допустимы циклический арбитраж, приоритетный арбитраж, а также другие схемы арбитража

Слайд 55Арбитраж шины PCI

Транзакции:

шина предоставляется для одной транзакции

[продолжительность транзакции теоретически не ограничена]

между транзакциями требуется вставлять пустой цикл [при отсутствии конкуренции на доступ к шине устройство может совершать последовательные транзакции без пустых циклов между ними]

если задающее устройство выполняет очень длительную передачу, а какое-нибудь другое устройство выдало запрос на доступ к шине, арбитр может сбросить сигнал на линии GNT# [задающее устройство следит за линией GNT#, и при сбросе сигнала устройство должно освободить шину в следующем цикле]

Слайд 60Транзакции на шине PCI

Примеры 32-разрядных транзакций на шине PCI.

Во время

Цикл Т1 :

сигнала задающее устройство помещает адрес на линии AD и команду на линии С/ВЕ#.

задающее устройство устанавливает сигнал FRAME#, чтобы начать транзакцию.

Цикл Т2 :

задающее устройство переключает шину, чтобы подчиненное устройство могло воспользоваться ею во время цикла Т3

задающее устройство изменяет сигнал С/ВЕ#, чтобы указать, какие байты в слове ему нужно считать

Слайд 61Транзакции на шине PCI

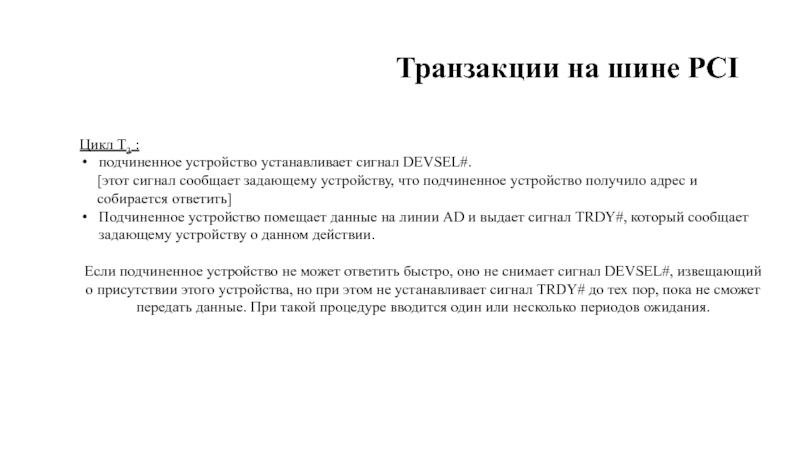

Цикл Т3 :

подчиненное устройство устанавливает сигнал DEVSEL#.

[этот

Подчиненное устройство помещает данные на линии AD и выдает сигнал TRDY#, который сообщает задающему устройству о данном действии.

Если подчиненное устройство не может ответить быстро, оно не снимает сигнал DEVSEL#, извещающий о присутствии этого устройства, но при этом не устанавливает сигнал TRDY# до тех пор, пока не сможет передать данные. При такой процедуре вводится один или несколько периодов ожидания.

![Арбитраж шиныЧто происходит, когда задающим устройством шины становятся два или более устройств одновременно?[микросхемы вода-вывода, cопроцессоры]](/img/tmb/3/283284/688ec95ce2406fed61b389c9a8232282-800x.jpg)

![Шина PCIPCI (Peripheral Component Interconnect — взаимодействие периферийных компонентов),[1990 г, компания Intel]Шина PCI несовместима со](/img/tmb/3/283284/a3b91b46aa9b59e2ec2caa02def81932-800x.jpg)

![Арбитраж шины PCIТранзакции:шина предоставляется для одной транзакции [продолжительность транзакции теоретически не ограничена] между транзакциями требуется](/img/tmb/3/283284/6e81f099cbc7748e49ec9940d2e6e300-800x.jpg)