- Главная

- Разное

- Дизайн

- Бизнес и предпринимательство

- Аналитика

- Образование

- Развлечения

- Красота и здоровье

- Финансы

- Государство

- Путешествия

- Спорт

- Недвижимость

- Армия

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Классификация параллельных процессоров. Архитектура и функционирование суперскалярних процессоров. (Тема 1.2) презентация

Содержание

- 1. Классификация параллельных процессоров. Архитектура и функционирование суперскалярних процессоров. (Тема 1.2)

- 2. Первый вопрос.

- 5. Фон Неймановская архитектура Машина состоит из

- 6. 3 основных признака фон Неймановской архитектуры (Принстонская):

- 7. Гарвардская архитектура Гарвардской архитектуре присущ один

- 8. Архитектура системы команд. Классификация процессоров (CISC и RISC)

- 9. Наиболее распространенными из систем, класса: один поток

- 10. Структура матричной вычислительной системы "SOLOMON" Система

- 11. Идея многомодальности заключается в

- 12. ПРИМЕРЫ МАТРИЧНЫХ ПРОЦЕССОРОВ

- 13. ПРОЦЕССОР С КОНВЕЙЕРИЗАЦИЕЙ КОМАНД ПРОЦЕССОР С КОНВЕЙЕРИЗАЦИЕЙ ОПЕРАЦИЙ

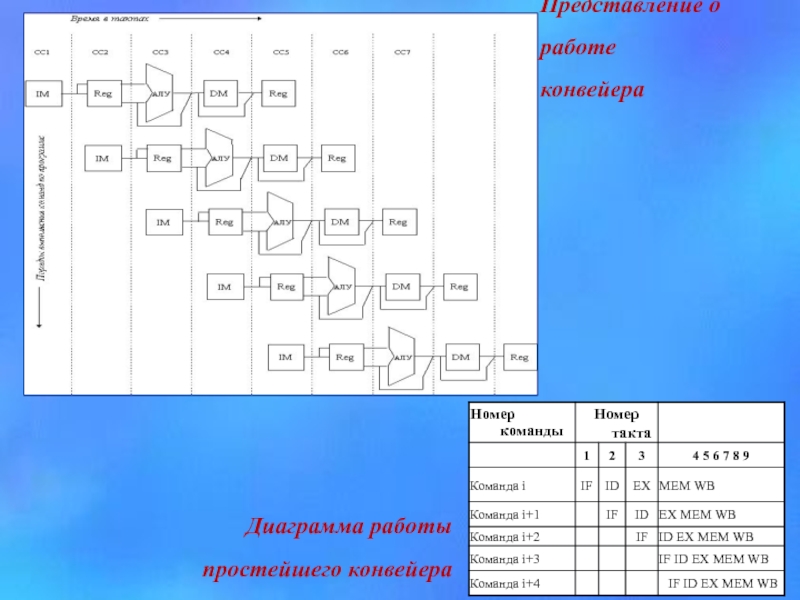

- 14. Представление о работе конвейера Диаграмма работы простейшего конвейера

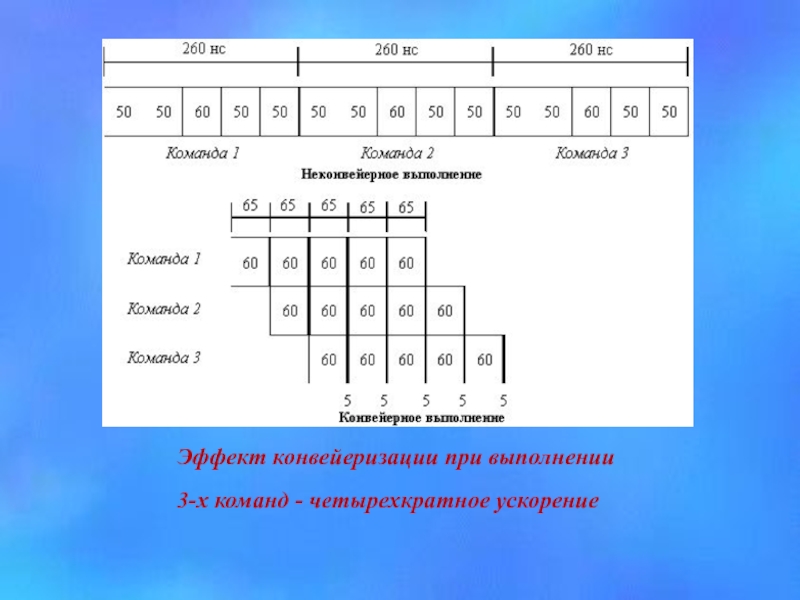

- 15. Эффект конвейеризации при выполнении 3-х команд - четырехкратное ускорение

- 16. Второй вопрос.

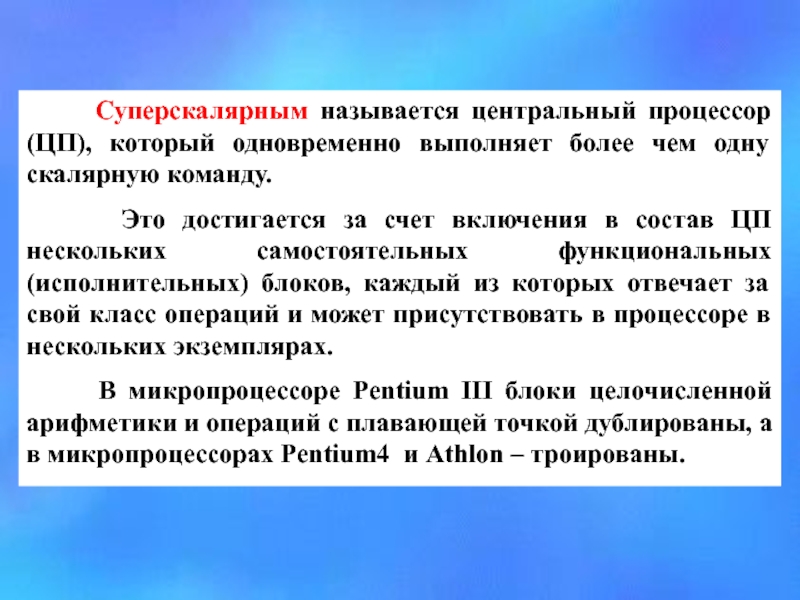

- 17. Суперскалярным называется центральный процессор

- 18. Архитектура суперскалярного процессора

- 19. Блок выборки команд извлекает команды из основной

- 20. Очереди диспетчеризации и распределения В дополнение к

- 21. . Упрощенная блок схема

- 23. Особенности суперскалярных процессоров

- 24. . Преимущества суперскалярной машины по

- 25. Структурная схема суперскалярного процесcора HP PA–RISC 8000

- 26. Литература: 1. Степанов А.Н. Архитектура вычислительных систем

Слайд 1ТЕМА 1. АРХИТЕКТУРА И ФУНКЦИОНИРОВАНИЕ СОВРЕМЕННЫХ ПАРАЛЛЕЛЬНЫХ ПРОЦЕССОРОВ.

Лекция 2. Классификация параллельных

Архитектура и функционирование суперскалярних процессоров.

Слайд 2Первый вопрос.

Архитектура Фон Неймановская архитектура Гарвардская архитектура Архитектура системы команд

Слайд 5

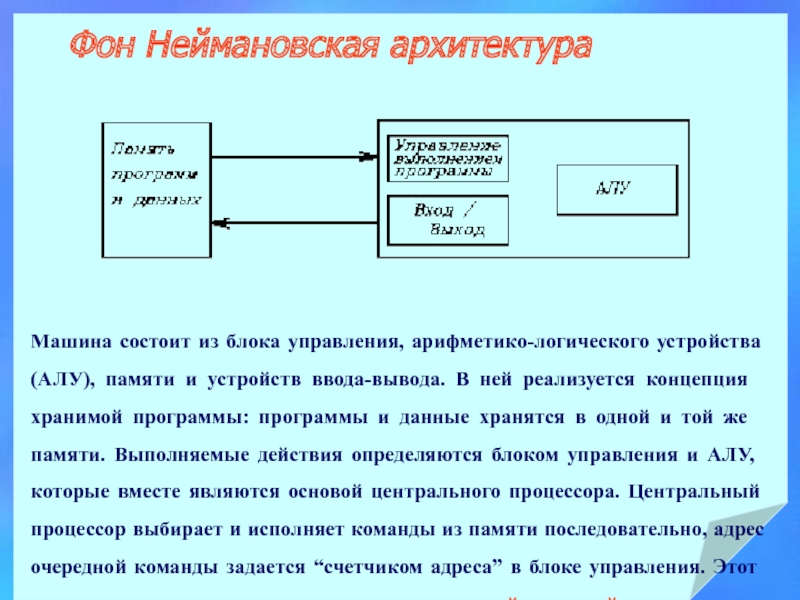

Фон Неймановская архитектура

Машина состоит из блока управления, арифметико-логического устройства (АЛУ), памяти

Слайд 63 основных признака фон Неймановской архитектуры (Принстонская):

память состоит из последовательности ячеек

хранение команд программы и обрабатываемых ими данных - на одинаковых принципах (с точки зрения обработки сообщений);

программа выполняется покомандно, в соответствии с их порядком. УУ – централизовано.

Почему ФН уже не удовлетворяет?

Первое – это скорость, сейчас в усредненной задачи от скорости работы CPU зависит не так уж много – важнее скорость работы памяти и других передач данных. Узкое место – единый тракт.

АЛЬТЕРНАТИВА – параллельная обработка, совмещение операций.

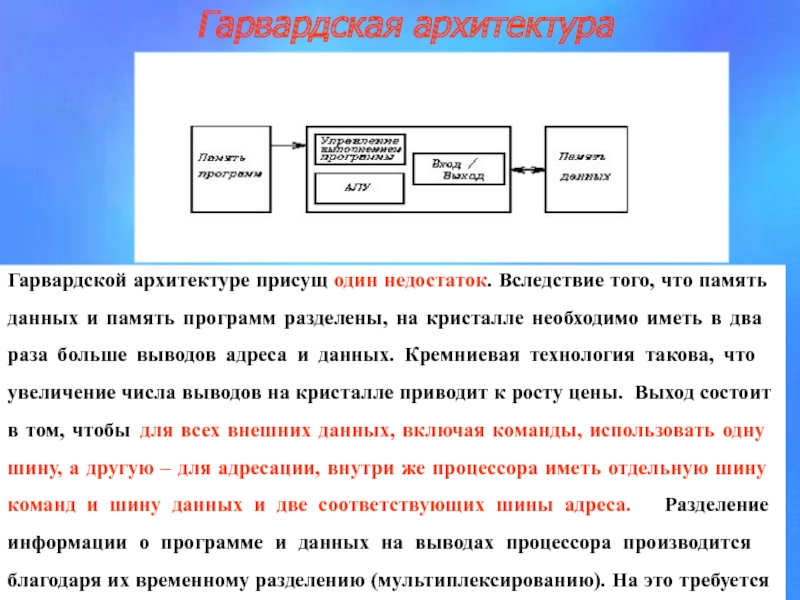

Слайд 7Гарвардская архитектура

Гарвардской архитектуре присущ один недостаток. Вследствие того, что память данных

Слайд 9Наиболее распространенными из систем, класса: один поток команд - множество -

Матричный процессор

Слайд 10

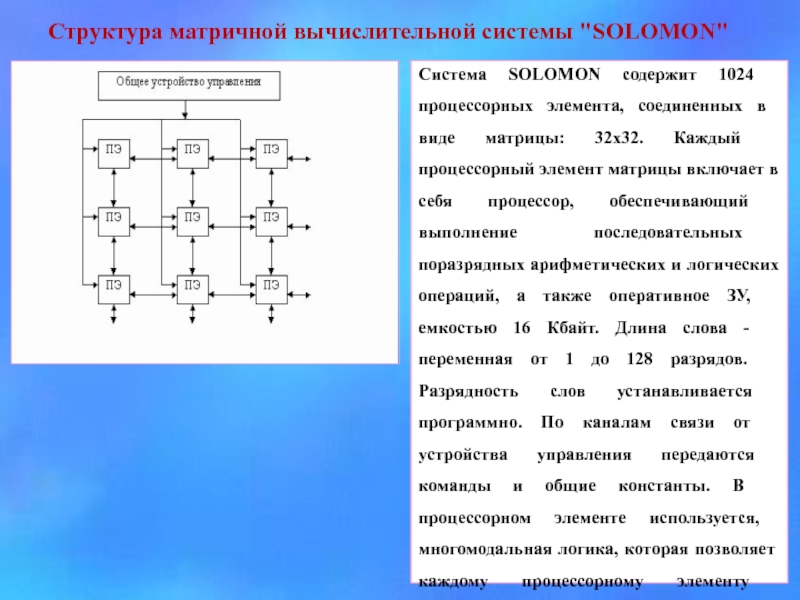

Структура матричной вычислительной системы "SOLOMON"

Система SОLOМОN содержит 1024 процессорных элемента, соединенных

Слайд 11 Идея многомодальности заключается в том, что в каждом

Мода (модальность) заносится в этот регистр от устройства управления.

При выполнении последовательности команд модальность передается в коде операции и сравнивается с содержимом регистра моды. Если есть совпадения, то операция выполняется.

В других случаях процессорный элемент не выполняет операцию, но может, в зависимости от кода, пересылать свои операнды соседнему процессорному элементу. Такой механизм позволяет выделить строку или столбец процессорных элементов, что очень полезно при операциях над матрицами. Взаимодействуют процессорные элементы с периферийным оборудованием через внешний процессор.

Слайд 17 Суперскалярным называется центральный процессор (ЦП), который одновременно выполняет

Это достигается за счет включения в состав ЦП нескольких самостоятельных функциональных (исполнительных) блоков, каждый из которых отвечает за свой класс операций и может присутствовать в процессоре в нескольких экземплярах.

В микропроцессоре Pentium III блоки целочисленной арифметики и операций с плавающей точкой дублированы, а в микропроцессорах Pentium4 и Athlon – троированы.

Слайд 19Блок выборки команд извлекает команды из основной памяти через кэш-память команд.

Блок декодирования расшифровывает код операции, содержащейся в извлеченных из кэш-памяти командах. В некоторых скалярных процессорах, например в микропроцессорах фирмы Intel, блоки выборки и декодирования совмещены.

Блоки диспетчеризации и распределения взаимодействуют между собой и в совокупности играют в суперскалярном процессоре роль конроллера трафика. Оба блока хранят очереди декодированных команд.

Очередь блока распределения часто рассредотачивается по нескольким самостоятельным буферам – накопителям команд или схемам резервирования,- предназначенным для хранения команд, которые уже декодированы, но еще не выполнены. Каждый накопитель команд связан со своим функциональным блоком (ФБ), поэтому число накопителей обычно равно числу ФБ, но если в процессоре используется несколько однотипных ФБ, то им придается общий накопитель.

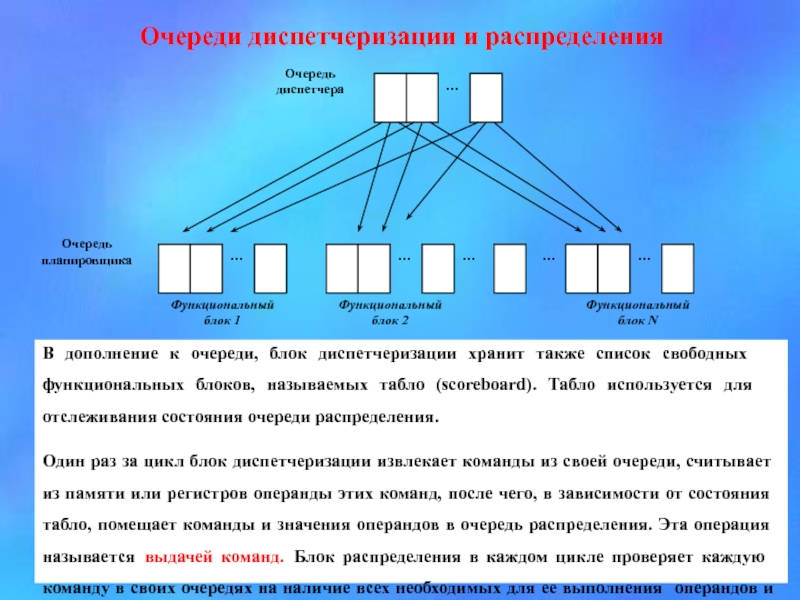

Слайд 20Очереди диспетчеризации и распределения

В дополнение к очереди, блок диспетчеризации хранит также

Один раз за цикл блок диспетчеризации извлекает команды из своей очереди, считывает из памяти или регистров операнды этих команд, после чего, в зависимости от состояния табло, помещает команды и значения операндов в очередь распределения. Эта операция называется выдачей команд. Блок распределения в каждом цикле проверяет каждую команду в своих очередях на наличие всех необходимых для ее выполнения операндов и при положительном ответе начинает выполнение таких команд в соответствующем функциональном блоке.

Слайд 21

.

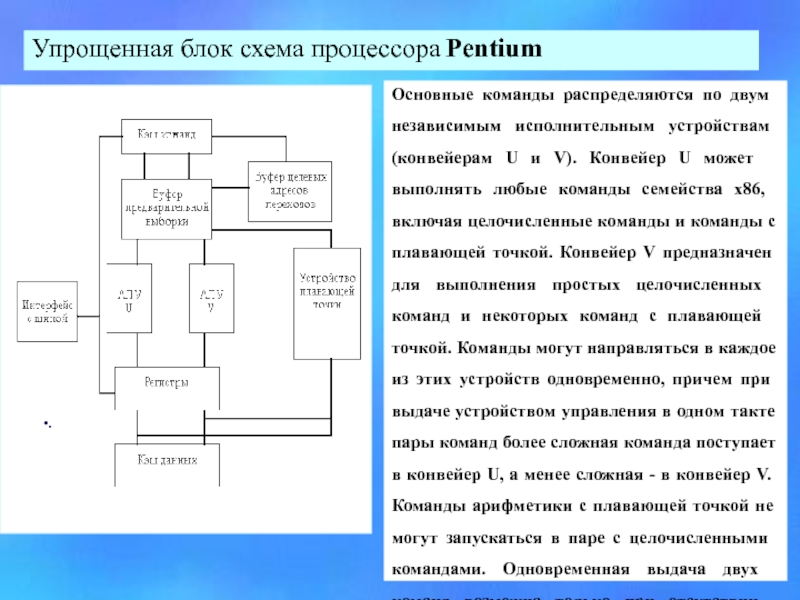

Упрощенная блок схема процессора Pentium

Основные команды распределяются по двум независимым исполнительным

Слайд 23

Особенности суперскалярных процессоров [ 1,2 ]:

1. Суперскалярные процессоры

2. Используются жесткие (аппаратно реализованные) многоступенчатые конвейеры обработки (без использования микропрограмм).

3. Большинство команд выполняются за один такт и лишь немногие – в течение нескольких или нескольких десятков тактов.

4. Все команды обработки данных взаимодействуют только с содержимым регистров, обращение к более медленной оперативной памяти осуществляется с помощью отдельных инструкций (загрузить в регистр/записать в память).

Слайд 24

.

Преимущества суперскалярной машины по сравнению с VLIW-машиной:

во-первых, малое воздействие на

во-вторых, на таких машинах могут работать неоптимизированные программы, или программы, откомпилированные в расчете на более старую реализацию.

Архитектура машин с очень длинным командным словом (VLIW Very - Long Instruction Word) позволяет сократить объем оборудования, требуемого для реализации параллельной выдачи нескольких команд, и потенциально чем большее количество команд выдается параллельно, тем больше эта экономия.

Слайд 26Литература:

1. Степанов А.Н. Архитектура вычислительных систем и компьютерных сетей. – СПб.:

2. Воеводин В.В., Воеводин Вл.В. Параллельные вычисления. - СПб.: БХВ-Петербург, 2002.- 608 с.

3. Лацис А. Как построить и использовать суперкомпьютер.- М.: Бестселлер, 2003.-240с.

4. wwwwww.www.parallelwww.parallel.www.parallel.rbwww.parallel.rb.www.parallel.rb.ru

![Особенности суперскалярных процессоров [ 1,2 ]: 1. Суперскалярные процессоры обрабатывают несколько команд одновременно в](/img/tmb/4/322044/373a3c4b8bd3eebf059e03126f51f91b-800x.jpg)